Предлагаемое изобретение относится к радиотехнике и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов (ШПС) в условиях интенсивных помех.

Известно аналогичное устройство синхронизации ШПС, например, а.с. СССР №613512, осуществляющее параллельный многоканальный поиск сигнала по задержке, а также устройство синхронизации, содержащее квадратурные каналы обработки, каждый из которых состоит из перемножителя, интегратора и аналого-цифрового преобразователя (АЦП), блок сумматоров с памятью и блок свертки, выход которого подключен к входам первого и второго цифроаналоговых преобразователей (ЦАП), выходы которых через соответствующие квадраторы подключены к входам сумматора, выход которого подключен к решающему блоку.

Недостатком указанных аналогов является их сравнительно невысокое быстродействие.

Наиболее близким к предлагаемому устройству по техническому решению (т.е. прототипом) является схема обработки ШПС с неизвестной задержкой, описанная в статье М.Л.Гарибяна "Определение целесообразности усложнения цифровых согласованных фильтров на интегральных структурах". Радиотехника, 1975 г., т.30, №10, стр.25 рис.1, структурная электрическая схема которой приведена на фиг.1.

Схема содержит два канала, каждый из которых состоит из последовательно соединенных перемножителя 1, фильтра 2, каскада совпадения 3, квантизатора 4 и 2Z параллельных регистров 5÷(2Z+4), 4Z сумматоров-дешифраторов (2Z+5)÷(6Z+4) и 4Z делителя (6Z+5)÷(10Z+4), а также сумматоров (10Z+5), (10Z+6) и квадраторов (10Z+7), (10Z+8), кроме того, выходы квадраторов (10Z+7) и (10Z+8) соединены со входами соответствующих блоков объединения квадратурных составляющих (10Z+9), (10Z+10), выходы которых соединены с входами вычитающего устройства (10Z+11), а выход генератора тактовых импульсов (10Z+12) соединен с вторыми входами каскадов совпадения 3 и тактовыми входами регистров 5÷(2Z+4).

Схема работает следующим образом.

Аддитивная смесь сигнала и помехи разделяется в перемножителях 1 на квадратурные составляющие, которые с выходом фильтров 2, оптимальных для элемента фазоманапулированного (ФМ) сигнала, через каскады совпадений 3 в дискретные моменты времени поступают на входы квантизаторов 4, у которых число выходов равно количеству уровней квантования 2Z. Информация с выходов квантизаторов 4 записывается в регистры 5÷(2Z+4) и сравнивается с кодовыми символами S1 и S2 с помощью сумматоров-дешифраторов (2Z+5)÷(6Z+4), отклики которых через делители (6Z+5)÷(10Z+4) с весовыми множителями δ±R подаются на сумматоры (10Z+5) и (10Z+6). Напряжение с выхода этих сумматоров, т.е. V1c, V1s, V2c, и V2s, через устройства, выполняющие операции

подаются на вычитающее устройство (10Z+11), в котором в момент окончания действия ШПС принимается решение о переданном сигнале.

Недостатком прототипа является его чрезмерная громоздкость и недостаточно высокая эффективность.

Целью предлагаемого изобретения является повышение эффективности и упрощение устройства.

Указанная цель достигается тем, что в известное устройство введены последовательно соединенные блок накопления информации, блок быстрого корреляционного преобразования, блок усреднения, блок нормировки, блок накопления корреляционных функций, схема выбора максимума, решающая схема, первый адресный генератор и второй адресный генератор, а также блок управления, при этом выход схемы накопления, выборки и запоминания каждого канала соединен с соответствующим входом блока накопления информации, выход блока быстрого корреляционного преобразования соединен с вторым входом блока нормировки, второй выход схемы выбора максимума соединен с вторым входом первого адресного генератора, выход второго адресного генератора соединен с третьим входом блока накопления информации, второй выход решающей схемы соединен с вторым входом блока накопления корреляционных функций, а выход блока управления соединен с входами управления схем накопления, выборки и запоминания, блока накопления информации, блока быстрого корреляционного преобразования, блока усреднения, блока накопления корреляционных функций, схемы выбора максимума и первого и второго адресных генераторов.

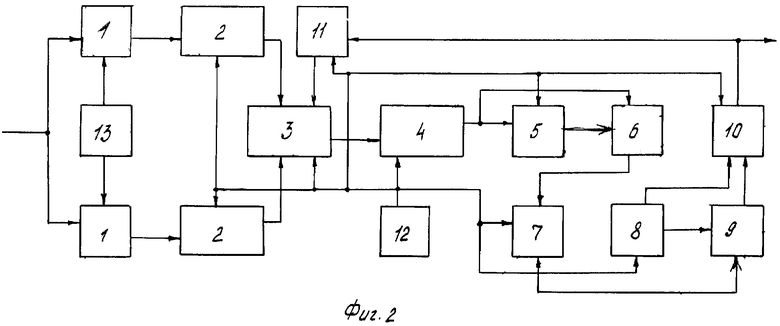

На фиг.2 изображена структурная электрическая схема предложенного устройства.

Устройство содержит два канала, каждый из которых состоит из последовательно соединенных перемножителя 1 и схемы накопления, выборки и запоминания 2, последовательно соединенные блок накопления информации 3, блок быстрого корреляционного преобразования 4, блок усреднения 5, блок нормировки 6, блок накопления корреляционных функций 7, схему выбора максимума 8, решающую схему 9, первый адресный генератор 10 и второй адресный генератор 11, а также блок управления 12 и генератор опорного напряжения 13, при этом выход схемы накопления, выборки и запоминания 2 каждого канала соединен о соответствующим входом блока накопления информации 3, выход блока быстрого корреляционного преобразования 4 соединен с вторым входом блока нормировки 6, второй выход схемы выбора максимума 8 соединен с вторым входом первого адресного генератора 10, выход второго адресного генератора 11 соединен с третьим входом блока накопления информации 3, второй выход решающей схема 9 соединен с вторым входом блока накопления корреляционных функций 7, выход блока управления 12 соединен с входами управления схем накопления, выборки и запоминания 2, блока накопления информации 3, блока быстрого корреляционного преобразования 4, блока усреднения 5, блока накопления корреляционных функций 7, схемы выбора максимума 8 и первого и второго адресных генераторов 10,11, а каждый из двух выходов генератора опорного напряжения 13 соединен с вторым входом перемножителя 1 соответствующего канала.

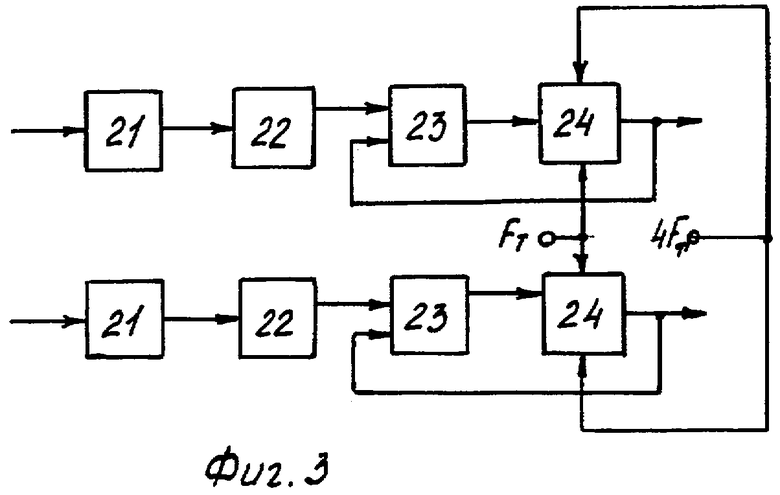

Предложенное устройство работает следующим образом. На входы перемножителей 1 каждого квадратурного канала поступает аддитивная смесь синхросигнала (представляющего собой М-последовательность длины N=2k-1) и помехи. На вторые входы перемножителей 1 поступают два сигнала с генератора опорного напряжения 13, сдвинутых по фазе относительно друг друга на 90°. Информация с выхода перемножителей 1 поступает далее в схему накопления, выборки и запоминания 2, где осуществляется ее фильтрация, интегрирование на отрезке, равном длительности элементарной посылки М-последовательности, и дискретизация сигнала по времени и уровню. При этом схема накопления, выборки и запоминания 2 может быть, в частности, выполнена, как это показано на фиг.3 (21 - фильтр низких частот, 22- аналого-цифровой компаратор, 23 - сумматор, 24 - регистр). Ее особенность состоит в том, что интегрирование сигнала в течение элементарной посылки синхропоследовательности происходит в цифровом виде.

Информация с выходов регистров 24 поступает затем в блок накопления информации 3, в котором происходит когерентное накопление синхронизирующей М-последовательности, а именно сложение отсчетов одного периода ШПС с соответствующими отсчетами последующего периода ШПС. Т.о. в Конечном итоге в блоке накопления информации 3 в каждом квадратурном канале хранится N отсчетов синхропоследовательности, а число циклов накопления определяется стабильностью тактовой частоты в передатчике и средним временем вхождения в синхронизм. Один из возможных вариантов построения блока накопления 3 представлен на фиг.4, где 31 - первый коммутатор, 32 - сумматор, 33 - оперативное запоминающее устройство (ОЗУ), 34 - регистр, 35 - второй коммутатор, 36 - третий коммутатор, 37 - четвертый коммутатор, 38 - пятый коммутатор, 39 - инвертор.

Существенно, что при записи информации в ОЗУ 33 происходит одновременно перестановка поступающих отсчетов синхронизирующей М-последовательности с целью преобразования синхропоследовательности к одной из функций Уолша, упорядоченной по Адамару. Закон перестановки отсчетов М-последовательности описан в статье Лосева В.В., Дворникова В.Д. "Способ многоканальной обработки симплексных кодов", Известия вузов - Радиоэлектроника, 1976 г., №12, стр.89, a технически может быть реализован с помощью генератора ПСН со встроенными сумматорами, роль которого выполняет второй адресный генератор 11. При этом выходы разрядов второго адресного генератора 11 определяют двоичный код номера ячейки ОЗУ 33, в которую записывается очередной отсчет синхропоследовательности. Начальное состояние второго адресного генератора 11 1000...0. Обработка информации в ОЗУ 33 осуществляется в двухтактном режиме с частотой, равной тактовой частоте FТ М-последовательности, так что в каждом ОЗУ записываются N отсчетов одной и N отсчетов другой квадратурной составляющей ШПС. Считывание же информации в блок быстрого корреляционного преобразования 4 происходит в быстром темпе.

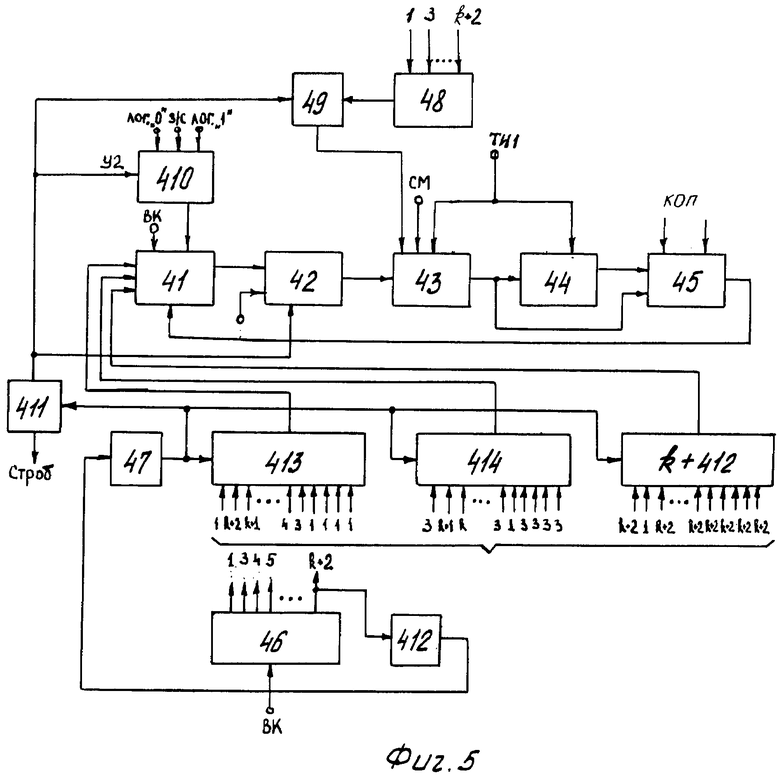

Суть обработки информации в блоке быстрого корреляционного преобразования 4 состоит в выполнении алгоритма быстрого преобразования Уолша (БПУ) и объединении квадратурных составляющих. Структурная схема одного из вариантов выполнения блока быстрого корреляционного преобразования 4 представлена на фиг.5, на которой.введены следующие обозначения: 41 - ОЗУ, 42 - первый коммутатор, 43 - первый регистр, 44 - второй регистр, 45 - арифметически-логическое устройство (АЛУ), 46 - адресный счетчик, 47 - счетчик управления, 48 - первый дешифратор, 49-схема И, 410 - второй коммутатор, 411 - второй дешифратор, 412 - инвертор, 413-(k+412) - адресные коммутаторы. Информация с выходов ОЗУ 33 блока накопления информации 3 перезаписывается в ОЗУ 41 через первый коммутатор 42 и первый и второй регистры 43,44 по адресам, определяемым номером поступающего отсчета. При этом в нулевую ячейку ОЗУ 41 принудительно записывается нуль путем обнуления в соответствующий момент времени первого регистра 43 (с помощью первого и второго дешифратора 48, 411 и схемы И 49).

После этого осуществляется процесс непосредственной реализации алгоритма БПУ, при котором необходимо выполнять сложную перегруппировку адресов ОЗУ 41. При этом легко показать, что на первом этапе преобразования для выполнения базовой операции "бабочки" достаточно инвертировать порядок следования разрядов адресного счетчика 46 для получения соответствующего адреса ячейки ОЗУ 41. На втором этапе преобразования необходимо осуществить инверсию только первых (k-1)-x разрядов адресного счетчика 46, не меняя положения k-го разряда адресного счетчика 46. На третьем этапе инвертируются только первые (k-2)-х разряда адресного счетчика 46 без изменения положения двух последних старших разрядов счетчика и т.д. Т.о. на k -ом этапе преобразования порядок следования разрядов адресного счетчика 46 окажется первоначальным (как при записи входной информации). Считываемые в определенном порядке отсчеты входного сигнала поступают парами с выхода ОЗУ 41 через первый коммутатор 42 в регистры 43,44 и далее в АЛУ 45. Результаты вычисления после выполнения очередной базовой операции БПУ записываются в те же ячейки ОЗУ 41, из которых была считана соответствующая пара отсчетов. С этой целью сигнал второго разряда адресного счетчика 46 вообще не используется при формировании адресов ОЗУ 41.

Описанная перегруппировка адресов ОЗУ 41 на каждом этапе БПУ происходит с помощью адресных коммутаторов 413÷(k+412). При этом управление переключением входных сигналов этих коммутаторов осуществляется счетчиком управления 47 с частотой, равной частоте сигнала старшего разряда адресного счетчика 46.

После выполнения алгоритма БПУ над обеими квадратурными составляющими сигнала регистры 43, 44 и АЛУ 45 используются для нахождения огибающей процесса по приближенной формуле

X=|I1|+|I2|,

где I1 и I2 - квадратурные составляющие процесса после выполнения БПУ.

При этом операция взятия модуля выполняется путем инвертирования кода регистра 43 (сигнал "взятия модуля", СМ). Отметим, что второй коммутатор 410 обеспечивает последовательное подключение сигналов "запись-считывание" (з/с), соответствующих трем режимам: записи информации в ОЗУ 41, выполнения БПУ и объединения квадратур, и считывания информации в блок усреднения 5 и блок нормировки 6.

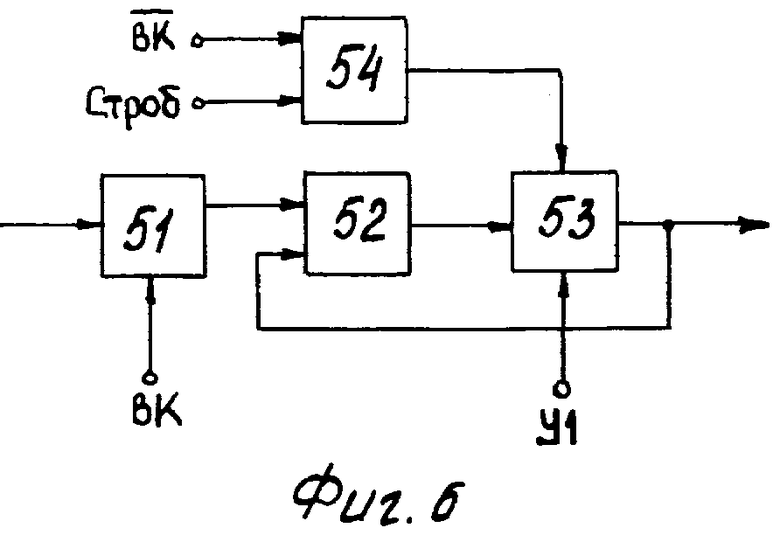

Полученная таким образом свертка входного сигнала поступает с выхода ОЗУ 41 в блок усреднения 5, который вычисляет приближенную оценку мощности процесса на выходе блока быстрого корреляционного преобразования 4. Конкретная реализация блока усреднения 5 приведена на фиг.6, на которой обозначено: 51 - первый регистр, 52 - сумматор, 53 - второй регистр, 54 - схема И.

Вычисленная оценка мощности процесса на выходе блока быстрого корреляционного преобразования 4 используется затем для нормировки отсчетов свертки входного сигнала в блоке нормировки 6. Отметим, что блок нормировки 6 представляет собой цифровой многоразрядный делитель, на входы которого одновременно поступают двоичный код оценки мощности процесса и код отсчетов свертки входного сигнала (см., например, Л.Рабинер, Б.Гоулд. Теория и применение цифровой обработки сигналов. Мир, 1978, стр.584, рис.8.37).

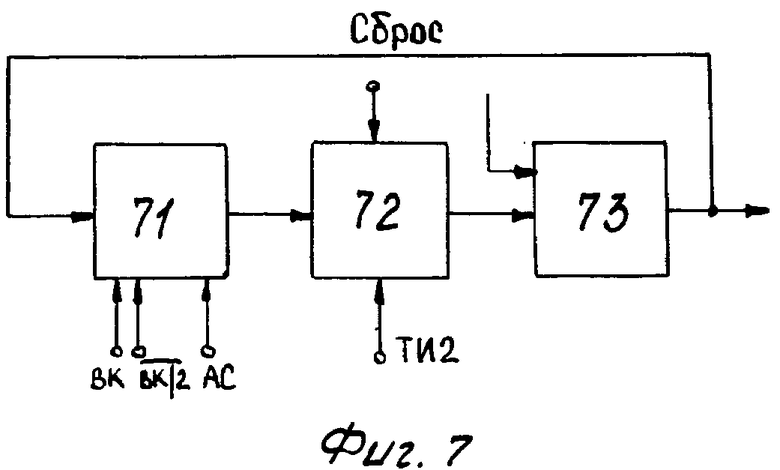

Блок накопления корреляционных функций 7 служит для последетекторного накопления отнормированной свертки входного сигнала, причем число периодов накопления ограничено средним временем вхождения в синхронизм.

Структурная схема блока накопления корреляционных функций 7 изображена на фиг.7, где 71 - ОЗУ, 72 - регистр, 73 - сумматор.

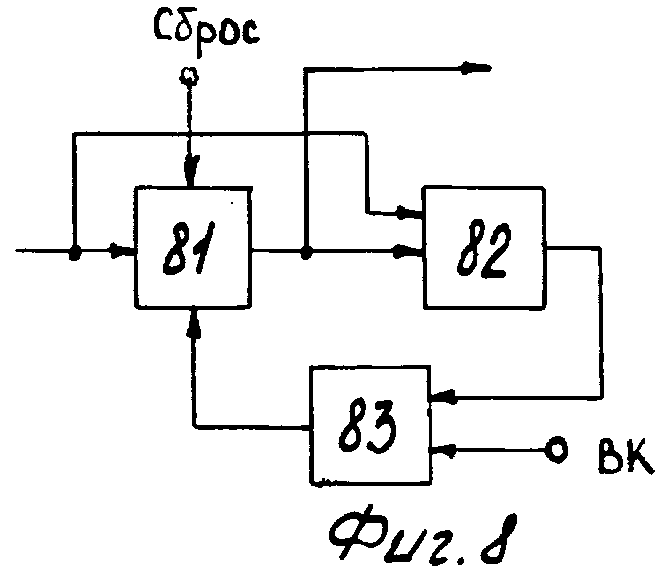

Дальнейшая обработка информации состоит в нахождении максимального пика корреляционной функции на выходе блока 7. Эта задача решается с помощью схемы выбора максимума 8, структурная схема которой представлена на фиг.8 (81 - регистр, 82 - компаратор, 83 - схема И). Схема работает таким образом, что если число на входе регистра 81 больше числа, хранящегося в этом регистре, то на тактовый вход регистра 81 проходит импульс записи.

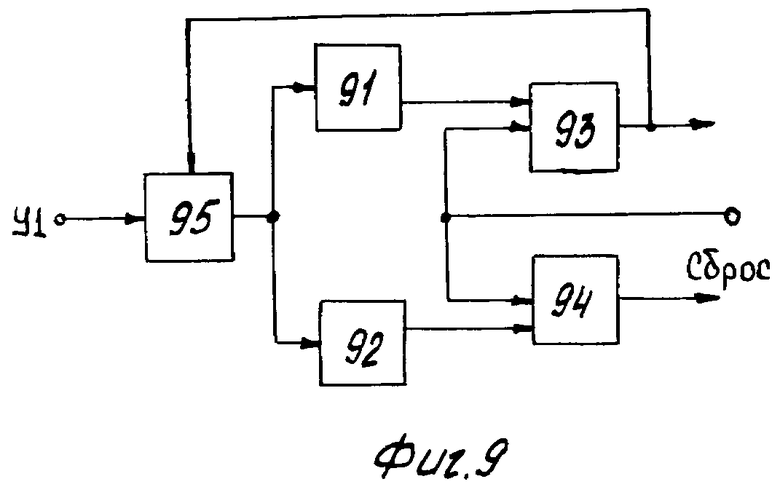

Найденный максимум корреляционной функции проверяется затем по критерию Вальда в решающей схеме 9, структура которой приведена на фиг.9, где обозначено: 91 - первое постоянное запоминающее устройство (ПЗУ), 92 - второе ПЗУ, 93 - первый компаратор, 94 - второй компаратор, 95 - счетчик числа периодов накопления. В соответствии с критерием Вальда максимум корреляционной функции сравнивается с верхним и нижним порогами обнаружения в компараторах 93 и 94 на каждом очередном цикле накопления. При этом, если максимум окажется больше верхнего порога обнаружения, принимается решение о выдаче импульса синхронизации с выхода первого адресного генератора 10. Если максимум будет меньше нижнего порога, выносится решение об отсутствии синхросигнала и в блок накопления корреляционных функций 7 поступает команда "сброс", которая обнуляет регистр 72. Если же величина максимума скажется между значениями верхнего и нижнего порогов, происходит очередной цикл накопления корреляционных функций. Значения верхнего и нижнего порогов обнаружения для каждого цикла накопления хранятся соответственно в первом и втором ПЗУ 91, 92 и считываются в соответствии с кодом на выходе счетчика числа периодов накопления 95. Пороги рассчитываются заранее исходя из заданных вероятностей ложной синхронизации и пропуска сигнала и являются постоянными для каждого цикла накопления, поскольку свертка входного сигнала нормируется в блоке нормировки 6.

При превышении максимума корреляционной функции верхнего порога обнаружения первый адресный генератор 10 устанавливается в начальное состояние, которое определяется кодом номера позиции этого максимума, и запускается. Поскольку первый адресный генератор 10 представляет собой генератор ПСП с нанесенным сумматором и позволяет переставить отсчеты корреляционной функции в порядке следования задержек входного сигнала, то момент перехода первого адресного генератора 10 в "нулевое" состояние и определяет искомый момент синхронизации. Импульс синхронизации одновременно производит установку в начальное состояние 1000...0 второго адресного генератора 11. Это позволяет на очередном этапе обработки произвести перепроверку синхронизации. В этом случае максимум корреляционной функции должен оказаться в первой ячейке ОЗУ 71 блока накопления корреляционных функций 7. Если не при повторном поиске максимум корреляционной функции в первой ячейке ОЗУ 71 не обнаружен, то первый импульс синхронизации считается ложным. Отметим, что первый и второй адресные генераторы 10 и 11 строятся на основе обычных триггеров и сумматоров, аналогично тому, как это сделано, например, в книге Диксона Р.К. «Широкополостные системы», Связь, стр.266-267, приложение №1.

Синхронизация работы всего устройства в целом осуществляется с помощью блока управления 12, структурная схема которого изображена на фиг.10, где введены следующие обозначения: 121 - опорный генератор, 122-125 - первый, второй, третий и четвертый делители на два, 126-129 - первый, второй, третий и четвертый инверторы, 1210 - коммутатор, 1211 - блок делителей, 1212 - триггер, 1213, 1214 - первая и вторая схемы И, 1215 - счетчик периода синхропоследовательности.

В этом блоке формируются основные сигналы управления, а именно тактовая частота FТ, сигналы «выбор кристалла» (ВК) и «запись-считывание» (з/с), для управления ОЗУ, тактовые импульсы регистров (ТИ1, ТИ2), сигнал «взятие модуля» (СМ), код операции для АЛУ (КОП), импульсы обнуления регистров.

Т.о. предложенное устройство, по сравнению с выбранным прототипом, обладает повышенной помехозащищенностью за счет накопления информации по входу и накопления корреляционных сверток. Так, если число периодов синхропоследовательности, накапливаемых по входу, равно шестнадцати, то помехозащищенность поиска возрастет, очевидно, на 12 дБ. Накопление корреляционных функций при процедуре Вальда дает дополнительный выигрыш 5-6 дБ. При этом время поиска сигнала в предложенному устройстве примерно в два раза меньше (чем в прототипе) за счет использования алгоритма быстрого преобразования Уолша.

В качестве базового образца может быть выбрана аппаратура "Кулон-Ш". При базе сигнала N=1023, числе корреляторов n=10 и времени накоплении сигнала ТН=0,2 сек время поиска сигнала в приемниках такого типа составит

Время поиска в предлагаемом устройстве составляет

т.е. в 10 раз меньше.

Помехозащищенность же поиска за счет накопления корреляционных сверток повышается на 5-6 дБ.

Отметим, что предложенное устройство может быть легко реализовано на базе цифровых интегральных микросхем, например, 564 и 537 серий. В настоящее время разработаны функциональные и электрические принципиальные схемы устройства, изготавливается его макетный образец.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ СЛОЖНЫХ СИГНАЛОВ | 1987 |

|

SU1840228A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| ВОКОДЕРНАЯ ИНТЕГРАЛЬНАЯ СХЕМА ПРИКЛАДНОЙ ОРИЕНТАЦИИ | 1995 |

|

RU2183034C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Способ обнаружения и оценивания характеристик широкополосных сигналов и устройство для его реализации | 2023 |

|

RU2814220C1 |

Изобретение относится к области радиотехники и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов (ШПС) в условиях интенсивных помех. Технический результат - повышение помехоустойчивости и сокращение времени поиска. Сущность изобретения состоит в том, что в устройство синхронизации М-последовательности, содержащее два канала, каждый из которых состоит из последовательно соединенных перемножителя и блока накопления, выборки и запоминания, а также генератор опорного напряжения, каждый из двух выходов которого соединен со вторым входом перемножителя соответствующего канала, согласно изобретению введены последовательно соединенные блок накопления информации, блок быстрого корреляционного преобразования, блок усреднения, блок нормировки, блок накопления корреляционных функций, решающий блок, первый адресный генератор и второй адресный генератор, а также блок управления, причем выход блока накопления, выборки и запоминания каждого канала соединен с соответствующим входом блока накопления информации, выход блока быстрого корреляционного преобразования соединен со вторым входом блока нормировки, второй выход блока выбора максимума соединен со вторым входом первого адресного генератора, выход второго адресного генератора соединен с третьим входом блока накопления информации, второй выход решающего блока соединен со вторым входом блока накопления корреляционных функций, а выход блока управления соединен с водами управления блоков накопления, выборки и запоминания, блока накопления информации, блока быстрого корреляционного преобразования, блока усреднения, блока накопления корреляционных функций, блока выбора максимума и первого и второго адресных генераторов. 10 ил.

Устройство синхронизации М-последовательности, содержащее два канала, каждый из которых состоит из последовательно соединенных перемножителя и блока накопления, выборки и запоминания, а также генератор опорного напряжения, каждый из двух выходов которого соединен со вторым входом перемножителя соответствующего канала, отличающееся тем, что, с целью повышения помехоустойчивости и сокращения времени поиска, введены последовательно соединенные блок накопления информации, блок быстрого корреляционного преобразования, блок усреднения, блок нормировки, блок накопления корреляционных функций, решающий блок, первый адресный генератор и второй адресный генератор, а также блок управления, причем выход блока накопления, выборки и запоминания каждого канала соединен с соответствующим входом блока накопления информации, выход блока быстрого корреляционного преобразования соединен со вторым входом блока нормировки, второй выход блока выбора максимума соединен со вторым входом первого адресного генератора, выход второго адресного генератора соединен с третьим входом блока накопления информации, второй выход решающего блока соединен со вторым входом блока накопления корреляционных функций, а выход блока управления соединен с входами управления блоков накопления, выборки и запоминания, блока накопления информации, блока быстрого корреляционного преобразования, блока усреднения, блока накопления корреляционных функций, блока выбора максимума и первого и второго адресных генераторов.

| Гарибян М.Л | |||

| Определение целесообразного усложнения цифровых согласованных фильтров на интегральных структурах, Радиотехника, 1975, т.30, №10. |

Авторы

Даты

2006-08-10—Публикация

1983-06-21—Подача