Предлагаемое изобретение относится к радиотехнике и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов (ШПС) в условиях интенсивных помех. Известно аналогичное устройство синхронизации ШПС, например, устройство синхронизации содержащее квадратурные каналы обработки, каждый из которых состоит из перемножителя, интегратора и аналого-цифрового преобразователя (АЦП), блок сумматоров с памятью и блок свертки, выход которого подключен к входам первого и второго цифроаналоговых преобразователей (ЦАП), выходы которых через соответствующие квадраторы подключены к входам сумматора, выход которого подключен к решающему блоку. Известна также аналогичная схема обработки ШПС с неизвестной задержкой, описанная в статье М.Л.Гариоян. Определение целесообразности усложнения циановых согласованных фильтров на интегральных структурах, Радиотехника, 1975, т.30, №10. Недостатком указанных аналогов является их сравнительно невысокое быстродействие и чрезмерная громоздкость, большое время поиска.

Прототипом предлагаемого устройства является устройство синхронизации М-последовательностей (авт.св. СССР №1840196 от 26 марта 1984 г.), структурная электрическая схема которого приведена на фиг.1.

Схема содержит два канала, каждый из которых состоит из последовательно соединенных перемножителя 1 и схемы накопления, выборки и запоминания 2, последовательно соединенные блок накопления информации 3, блок быстрого корреляционного преобразования 4, блок усреднения 5, блок нормировки 6, блок накопления корреляционных функций 7, схему выбора максимума 8, решающую схему 9, первый адресный генератор 10 и второй адресный генератор 11, а также блок управления 12 и генератор опорного напряжения 13, при этом выход схемы накопления, выборки и запоминания 2 каждого канала соединен с соответствующим входом блока накопления информации 3, выход блока быстрого корреляционного преобразования 4 соединен с вторым входом блока нормировки 6, второй выход схемы выбора максимума 8 соединен с вторым входом первого адресного генератора 10, выход второго адресного генератора 11 соединен с третьим входом блока накопления информации 3, второй выход решающей схемы 9 соединен с вторым входом блока накопления корреляционных функций 7, выход блока управления 12 соединен с входами управления схем накопления, выборки и запоминания 2, блока накопления информации 3, блока быстрого корреляционного преобразования 4, блока усреднения 5, блока накопления корреляционных функций 7, схемы выбора максимума 8, первого и второго адресных генераторов 10, 11, а каждый из двух выходов генератора опорного напряжения 13 соединен с вторым входом перемножителя 1 соответствующего канала.

Прототип работает следующим образом. На входы перемножителей 1 каждого квадратурного канала поступает аддитивная смесь синхросигнала (представляющего собой М-последовательность длины N=2K-1) и помехи. На вторые входы перемножителей 1 поступают сигналы генератора опорного напряжения 13, сдвинутые по фазе относительно друг друга на 90°. Информация с выхода перемножителей 1 поступает далее в схему накопления, выборки и запоминания 2, где осуществляется ее фильтрация, интегрирование на отрезке, равном длительности элементарной посылки М-последовательности и дискретизации сигнала по времени и уровню.

Затем информация поступает в блок накопления информации 3, в котором происходит когерентное накопление синхронизирующей М-последовательности, а именно сложение отсчетов одного периода ШПС с соответствующими отсчетами последующего периода ШПС.

После этого осуществляется считывание информации в блок быстрого корреляционного преобразования 4, в котором происходит выполнение алгоритма быстрого преобразования Уолта (БПУ) и объединение квадратурных составляющих.

Свертка выходного сигнала поступает в блок усреднения 5, который вычисляет приближенную оценку мощности процесса на выходе блока быстрого корреляционного преобразования 4.

Вычисленная оценка мощности процесса на выходе блока 4 используется затем для нормировки отсчетов входного сигнала в блоке нормировки 6.

Блок накопления корреляционных функций 7 служит для последетекторного накопления сформированной свертки входного сигнала. Дальнейшая обработка информации состоит в нахождении максимального пика корреляционной функции на выходе блока 7. Эта задача решается с помощью схемы выбора максимума 8.

Найденный максимум корреляционной функции проверяется затем по критерию Вальда в решающей схеме 9.

Синхронизация работы всего устройства в целом осуществляется с помощью блока управления 12.

Недостатком прототипа является невозможность поиска сигналов, отличающихся по структуре от М-последовательной.

Целью предлагаемого изобретения является обеспечение поиска ансамблей сигналов произвольной структуры, включая и М-последовательности.

Указанная цель достигается тем, что в данное устройство введены последовательно соединенные генератор опорного сигнала, блок формирования матрицы опорного сигнала и кодирующий блок, выход и второй вход которого соединены соответственно с входом блока теоретико-числовых преобразований и выходом блока накопления информации, а также третий адресный генератор, перемножитель и декодирующий блок, причем выход третьего адресного генератора соединен с вторым входом блока формирования матрицы опорного сигнала, выход и вход а перемножителя соединены соответственно с вторым входом и первым выходом блока теоретико-числовых преобразований, выход декодирующего блока соединен с входом блока усреднения и вторым входом блока нормировки, а вход декодирующего блока соединен с вторым выходом блока теоретико-числовых преобразований, кроме того, выход блока управления соединен с соответствующими входами управления перемножителя, генератора опорного сигнала, третьего адресного генератора и блока формирования матрицы опорного сигнала.

При дополнительном поиске, проведенном авторами в соответствии с п.52 ЭЗ-1-74, не обнаружены объекты со сходными признаками отличительной части. Учитывая это, авторы считают, что предлагаемое решение отвечает критерию "существенные отличия".

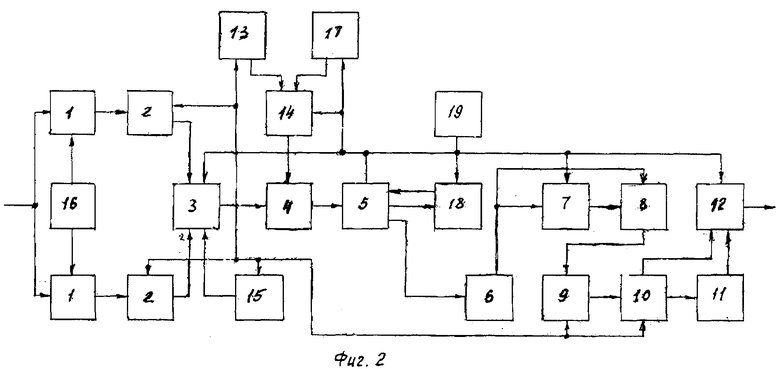

Структурная электрическая схема предлагаемого устройства приведена на фиг.2.

Схема содержит два канала, каждый из которых состоит из последовательно соединенных перемножителя 1 и схемы накопления, выборки и запоминания 2, последовательно соединенные блок накопления информации 3, кодирующий блок 4, блок теоретико-числовых преобразований 5, декодирующий блок 6, блок усреднения 7, блок нормировки 8, схему накопления корреляционных функций 9, схему выбора максимума 10, решающую схему 11 и второй адресный генератор 12, а также последовательно соединенные генератор опорного сигнала 13 и блок формирования матрицы опорного сигнала 14, кроме того, первый адресный генератор 15, генератор опорного напряжения 16, третий адресный генератор 17, перемножитель 18, блок управления 19, при этом выход схемы накопления, выборки и запоминания 2 каждого канала соединен с соответствующим входом блока накопления информации 3, выход декодирующего блока 6 соединен с вторым входом блока нормировки 8, второй выход схемы выбора максимума 10 соединен с вторым входом второго адресного генератора 12, выход первого адресного генератора 15 соединен с третьим входом блока накопления информации 3, выход третьего адресного генератора 17 соединен с вторым входом блока формирования матрицы опорного сигнала 14, выход и вход перемножителя 18 соединены соответственно с вторым входом и вторым выходом блока теоретико-числовых преобразований 5, выход блока управления 19 соединен с соответствующими входами управления схемы накопления, выборки и запоминания 2 каждого канала, блока накопления информации 3, первого адресного генератора 15, генератора опорного сигнала 13, третьего адресного генератора 17, блока формирования матрицы опорного сигнала 14, блока теоретико-числовых преобразований 5, перемножителя 18, блока усреднения 7, схемы накопления корреляционных функции 9, схемы выбора максимума 10, второго адресного генератора 12, а каждый из двух выходов генератора опорного напряжения 16 соединен с вторым входом перемножителя 1 соответствующего канала.

Предлагаемое устройство работает следующим образом.

На входы перемножителей 1 каждого квадратурного канала поступает смесь синхросигнала (представляющего собой последовательность произвольной структуры) и помехи. На вторые входы перемножителей 1 поступают сигналы генератора опорного напряжения 16, сдвинутые по фазе относительно друг друга на 90°. Информация с выхода перемножителей 1 поступает далее в схему накопления, выборки и запоминания 2, где осуществляется ее фильтрация, интегрирование на отрезке, равном длительности элементарной посылки синхропоследовательности, и дискретизация сигнала по времени и уровню.

Затем информация поступает в блок накопления информации 3, в котором происходит когерентное накопление синхронизирующей последовательности, а именно сложение отсчетов одного периода с соответствующими отсчетами последующего периода,

При этом схема накопления выборки и запоминания 2 и блок накопления информации 3 могут быть выполнены как это показано в описании изобретения по авт.св. СССР №1840196 на фиг.3 и фиг.4 соответственно.

Существенно, что при записи информации в ОЗУ происходит одновременно перестановка поступающих отсчетов синхронизирующей последовательности в соответствии с правилом, описанным в [1]. В результате которой формируется матрица входного сигнала для проведения двумерного теоретико-числового преобразования, необходимость которого определяется длиной преобразований и, как следствие, величиной аппаратурных затрат. Технически перестановка может быть осуществлена с помощью генератора, роль которого выполняет первый адресный генератор 15. При этом выходы разрядов первого адресного генератора 15 определяют двоичный код номера ячейки ОЗУ, в которую записывается очередной отсчет синхропоследовательности. Один из возможных вариантов построения первого адресного генератора 15 показан на фиг.3, где 151-адресный счетчик, 152-постоянное запоминающее устройство (ПЗУ), 153 - регистр. Таким образом в конечном итоге в блоке накопления информации 3 хранится N (где N - длина синхропоследовательности) отсчетов синхропоследовательности в каждом квадратурном канале. Считывание информации в кодирующий блок 4 происходит в быстром темпе.

За время накопления информации в блоке накопления информации 3 генератор опорного сигнала 13 формирует сигнал, совпадающий по структуре с синхропоследовательностью. Генератор опорного сигнала 13 (в зависимости от типа синхропоследовательности) может представлять собой генератор М-последовательности, последовательности Гоулда и т.п.

Далее опорный сигнал поступает в блок формирования матрицы опорного сигнала 14, представляющий собой ОЗУ, на адресный вход которого поступают разряды третьего адресного генератора 17. Закон перестановок отсчетов опорного сигнала описан в [1]. B результате перестановок формируется матрица опорного сигнала для проведения двумерного преобразования. Практически третий адресный генератор 17 может быть выполнен аналогично первому адресному генератору 15, схема которого приведена на фиг.3, единственным отличием является программа, заложенная в ПЗУ.

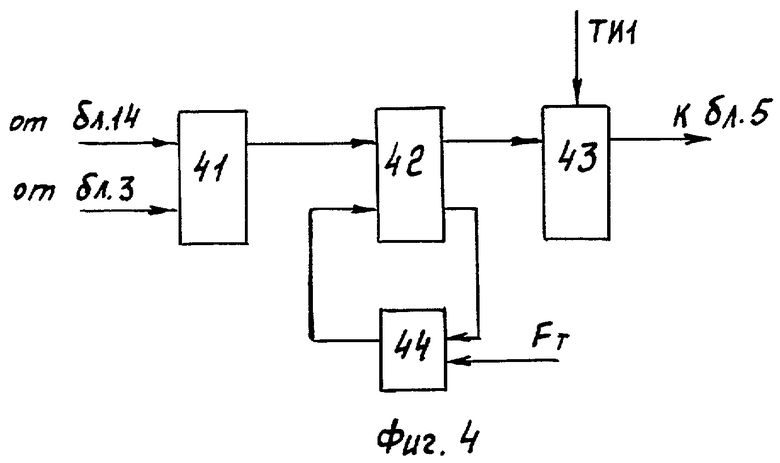

Информация из блока формирования матрицы опорного сигнала 14 поступает в кодирующий блок 4, в котором происходит кодирование данных в соответствии с двоичной арифметикой, описанной в [1]. Необходимость кодирования объясняется тем, что преобразования в блоке теоретико-числовых преобразований 5 производятся в кольце чисел по модулю числа Ферма, которое выбирается из соображений разрядности входных отсчетов и базы синхропоследовательности. Описанное правило кодирования в [1] позволяет значительно уменьшить затраты на выполнение теоретико-числовых преобразований. Один из вариантов построения кодирующего блока 4 приведен на фиг.4, где 41 - мультиплексор 2:1, 42 - арифметико-логическое устройство (АЛУ), 43 - регистр, 44 - триггер.

Далее опорный сигнал, закодированный соответствующим образом, поступает на вход блока теоретико-числовых преобразований 5. Суть обработки информации в блоке теоретико-числовых преобразований 5 сводится к выполнению алгоритма, описанного в [1]. На этом этапе преобразования аналогичны прямым преобразованиям Фурье, т.е. в результате получается спектр опорного сигнала в базисе теоретико-числовых преобразовании Ферма, вычисленный быстрыми числовыми методами. Коэффициенты преобразований каждого этапа поступают из блока управления 19. После обработки опорного сигнала на вход блока теоретико-числовых преобразований 5 поступает закодированная входная последовательность и вычисляется спектр входной информации, фактически повторяются вышеописанные преобразования.

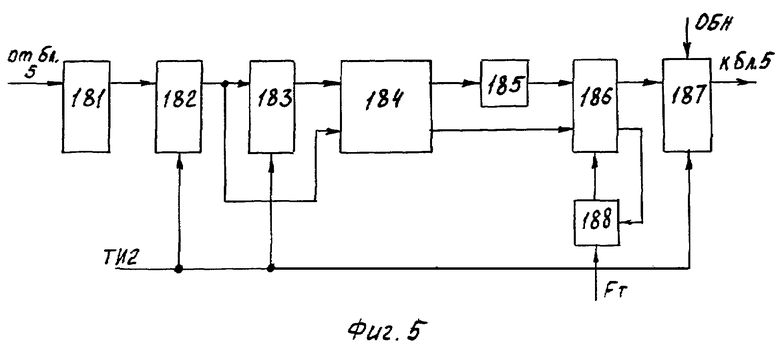

Затем производится перемножение полученных спектров входного сигнала и опорного в перемножителе 18. Перемножение осуществляется в упрощенной двоичной арифметике, описанной в [1]. Один из вариантов построения перемножителя 18 приведен на фир.5, где 181 - сумматор, 182, 183 - регистры, 184 - обычный двоичный перемножитель, 185 - инвертор, 186 - сумматор, 187 - регистр, 188 - триггер.

Результат перемножения поступает в блок теоретико-числовых преобразований 5, для выполнения обратных преобразований, которые отличаются от прямых только значениями коэффициентов, поступающих из блока управления 19. Реализация блока теоретико-числовых преобразований подробно описана в [1].

В результате преобразований формируется свертка синхропоследовательности и опорного сигнала.

После проведения вышеуказанных преобразований над информацией каждого квадратурного канала, производится объединение квадратур. Эта процедура и ее практическая реализация приведена в описании изобретения по авт.св. СССР №1840196.

Полученная таким образом свертка входного сигнала поступает с выхода блока теоретико-числовых преобразований в декодирующий блок 6, который может быть выполнен аналогично кодирующему блоку 4, схема которого приведена на фиг.4, за исключением входного мультиплексора 2:1 - 41. В декодирующем блоке осуществляется перевод информации из кода арифметико-числовых преобразований Ферма в обычный двоичный код.

Далее информация поступает в блок усреднения 7, который вычисляет приближенную оценку мощности процесса на выходе декодирующего блока 6.

Вычисленная оценка мощности процесса на выходе декодирующего блока 6 используется затем для нормировки отсчетов свертки входного сигнала в блоке нормировки 8.

Блок накопления корреляционных функций 9 служит для последетекторного накопления отнормированной свертки входного сигнала, причем число периодов накопления ограничено средним временем вхождения в синхронизм.

Дальнейшая обработка информации состоит в нахождении максимального пика корреляционной функции на выходе блока 9. Эта задача решается с помощью схемы выбора максимума 10.

Найденный максимум корреляционной функции проверяетсяпо критерию Вальда в решающей схеме 11.

Проверенный максимум поступает на второй адресный генератор 12, который вырабатывает информацию о моменте синхронизации для управления устройствами выделения информации.

Реализация блока усреднения 7, блока нормировки 8, блока накопления корреляционных функций 9, схемы выбора максимума 10, решающей схемы 11 приведена в описании изобретения по авт.св. СССР №1840196.

Второй адресный генератор 12 фактически соответствует генератору опорного сигнала, но в некоторых случаях его роль может выполнять обычный двоичный счетчик, который устанавливается импульсом, вырабатываемым решающей схемой 11, в состояние, соответствующее коду позиции корреляционного пика, определяемой схемой выбора максимума 10. После чего осуществляется счет до нулевого состояния и количество тактовых импульсов несет информацию о начале блока синхропоследовательности.

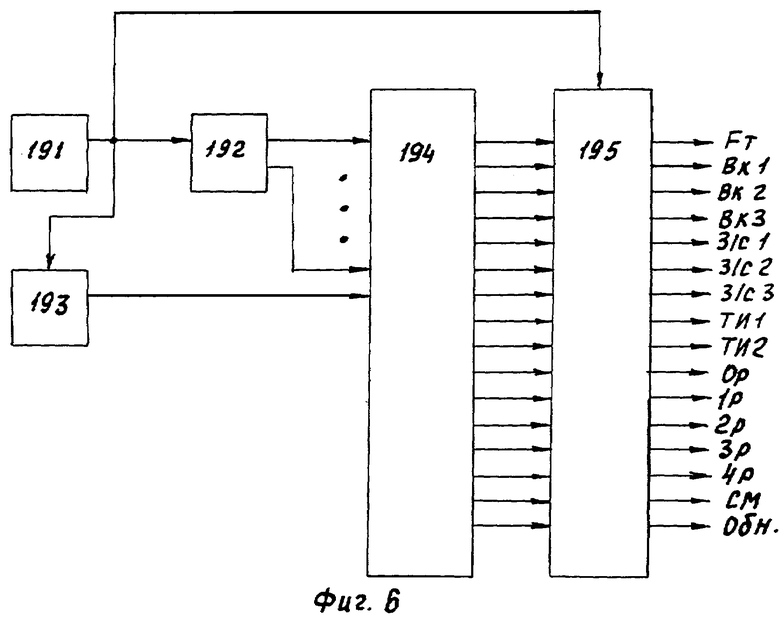

Синхронизация работы всего устройства в целом осуществляется с помощью блока управления 19, структурная схема которого изображена на фиг.6, где введены следующие обозначения: 191 - генератор опорной частоты, 192 - времязадающий счетчик, 193 - счетчик периода синхропоследовательности, 194 - блок ПЗУ, 195 - блок регистров.

В этом блоке формируются основные сигналы управления, а именно: тактовая частота Fт, сигналы "выбор кристалла" (BK1, ВК2, ВК3) и "запись-считывание" (З/С 1, З/С 2, З/С 3), для управления ОЗУ; тактовые импульсы регистров (ТИ1, ТИ2), сигналов коэффициентов преобразований (0р, 1р, 2р, 3р, 4р), сигнал "взятие модуля" (СМ), импульсы обнуления регистров.

Таким образом, предложенное устройство, по сравнению с выбранным прототипом, обладает возможностью поиска синхросигналов произвольной структуры.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| СПОСОБ ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ АДАПТИВНОЙ АНТЕННОЙ РЕШЕТКИ БАЗОВОЙ СТАНЦИИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2002 |

|

RU2237379C2 |

| Ретранслятор | 1989 |

|

SU1707772A1 |

| Приёмное устройство широкополосных сигналов | 2018 |

|

RU2691731C1 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2002 |

|

RU2229156C2 |

| Способ обнаружения, оценки параметров и подавления имитационных помех и навигационный приемник с устройством обнаружения, оценки параметров и подавления имитационных помех | 2020 |

|

RU2737948C1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| Способ обнаружения и оценивания характеристик широкополосных сигналов и устройство для его реализации | 2023 |

|

RU2814220C1 |

Изобретение относится к области радиотехники и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов (ШПС) в условиях интенсивных помех. Технический результат - обеспечение поиска ансамблей сигналов произвольной структуры, включая и М-последовательности. Достигается тем, что в данное устройство введены последовательно соединенные генератор опорного сигнала, блок формирования матрицы опорного сигнала и кодирующий блок, выход и второй вход которого соединены соответственно с входом блока теоретико-числовых преобразований и выходом блока накопления информации, а также третий адресный генератор, перемножитель и декодирующий блок, причем выход третьего адресного генератора соединен с вторым входом блока формирования матрицы опорного сигнала, выход и вход перемножителя соединены соответственно с вторым входом и первым выходом блока теоретико-числовых преобразований, выход декодирующего блока соединен с входом блока усреднения и вторым входом блока нормировки, а вход декодирующего блока соединен с вторым выходом блока теоретико-числовых преобразований, кроме того, выход блока управления соединен с соответствующими входами управления перемножителя, генератора опорного сигнала, третьего адресного генератора и блока формирования матрицы опорного сигнала. 6 ил.

Устройство синхронизации сложных сигналов, содержащее два канала, каждый из которых содержит последовательно соединенные перемножитель и узел выборки и запоминания, выходы которых подключены соответственно к первому и второму входам блока накопления информации, последовательно соединенные блок усреднения, блок нормировки, узел накопления корреляционных функций, узел выбора максимума, решающий узел, второй адресный генератор, выход которого является выходом устройства, а также первый адресный генератор, выход которого соединен с третьим входом блока накопления информации, генератор опорного напряжения, блок быстрого корреляционного преобразования (БКП), блок управления, выход которого соединен с соответствующими входами управления узлов выборки и запоминания, блока накопления информации, первого и второго адресных генераторов, блока БКП, узла накопления корреляционных функций, узла выбора максимума, выход которого соединен со вторым входом второго адресного генератора, при этом второй вход блока нормировки соединен с входом блока усреднения, первые входы перемножителей каждого канала объединены и соединены с входом устройства, выходы опорного генератора соединены соответственно со вторыми входами перемножителей каждого канала, отличающееся тем, что, с целью обеспечения поиска сигналов произвольной структуры, введены последовательно соединенные генератор опорного сигнала, блок формирования матрицы опорного сигнала, кодирующий блок, выход которого соединен с первым входом блока БКП, а так же третий адресный генератор, выход которого соединен со вторым входом блока формирования матрицы опорного сигнала, третий перемножитель, выход которого соединен со вторым входом блока БКП, первый выход которого соединен с входом третьего перемножителя, декодирующий блок, вход которого соединен со вторым выходом блока БКП, а выход подключен к входу блока усреднения, при этом второй вход кодирующего блока соединен с выходом блока накопления информации, выход блока управления соединен с соответствующими входами управления третьего перемножителя, блока формирования матрицы опорного сигнала, третьего адресного генератора.

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

Авторы

Даты

2006-08-20—Публикация

1987-05-04—Подача