Предлагаемое изобретение относится к радиотехнике и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов (ШПС).

Известны устройства обработки ШПС с неизвестной задержкой, описанные, например, в статье М.Л.Гарибян "Определение целесообразности усложнения цифровых согласованных фильтров на интегральных структурах" [1]. Недостатком указанного аналога является невысокое быстродействие и чрезмерная громоздкость.

Известно также устройство, недостатком которого является большое время поиска по ансамблю М-последовательностей.

Прототипом предлагаемого устройства является устройство синхронизации М-последовательности (авт.св. № 1810075).

Блок-схема устройства-прототипа приведена на фиг.1, где обозначено:

1 - перемножитель,

2 - схема накопления, выборки и запоминания,

3 - блок накопления информации,

4 - блок быстрого корреляционного преобразования,

5 - блок усреднения,

6 - блок нормировки,

7 - блок накопления корреляционных функций,

8 - схема выбора максимума,

9 - решающая схема,

10 - инвертор,

11 - схема И,

12 - адресный счетчик,

13 - постоянное запоминающее устройство (ПЗУ),

14 - второй адресный генератор,

15 - первый адресный генератор,

16 - блок управления,

17 - генератор опорного напряжения.

Устройство состоит из двух каналов последовательно соединенных блоков 1 и 2, первые входы блока 1 соединены между собой и являются входом устройства, вторые входы блока 1 соединены с соответствующими выходами блока 17, а выходы блока 2 соединены с входами блока 3, выход которого соединен с первым входом блока 4, первый выход которого соединен с первыми входами блоков 5 и 6, а второй выход с первым входом блока 11, выход блока 5 последовательно соединен с блоками 6, 7, 8 и 9, второй выход блока 8 соединен с первым входом блока 15, а первый выход блока 9 соединен со вторым входом блока 7, второй выход блока 9 соединен со вторым входом блока 15 и последовательно соединен с блоками 10, 11, 12, 13, 14, 4, причем выход блока 13 соединен с третьим входом блока 15, кроме этого выход блока 16 соединен с соответствующими входами блоков 2, 3, 4, 5, 7, 8, 14, 15.

Устройство-прототип работает следующим образом.

На входы перемножителей 1 каждого канала поступает аддитивная смесь синхросигнала (М-последовательность длины №2к-1) и помехи. На вторые входы перемножителей 1 поступают сигналы генератора опорного напряжения 17, сдвинутые по фазе относительно друг друга на 90°.

Информация с выхода перемножителей 1 поступает далее на схему накопления, выборки и запоминания 2, где осуществляется ее фильтрация и интегрирование на отрезке, равном длительности элементарной посылки М-последовательности, и дискретизация сигнала по времени и уровню. После такого преобразования информация поступает в блок накопления информации 3, в котором происходит когерентное накопление синхронизирующей М-последовательности, а именно сложение отсчетов одного периода ШПС с соответствующими отсчетами последующего периода ШПС. Т.о. в конечном итоге в блоке накопления информации 3 в каждом квадратурном канале хранится N отсчетов синхропоследовательности. При этом число циклов накопления определяется из требуемого среднего времени вхождения в синхронизм. После окончания накопления информация из блока накопления 3 переписывается в блок быстрого корреляционного преобразования 4.

Суть обработки информации в блоке быстрого корреляционного преобразования 4 состоит в выполнении алгоритма быстрого преобразования Уолша (БПУ) и объединении квадратурных составляющих.

Существенно, что при перезаписи информации из блока накопления 3 в блок быстрого корреляционного преобразования 4 происходит перестановка отсчетов синхронизирующей М-последовательности с целью преобразования этой последовательности в одну из функций Уолша, упорядоченную по Адамару. Закон перестановки отсчетов М-последовательности описан в [2], а технически может быть реализован с помощью генератора ПСП со встроенными сумматорами по модулю два, роль которого выполняет второй адресный генератор 14, начальное состояние которого -10...00. После этого осуществляется непосредственная реализация алгоритма БПУ, заключающаяся в многократном выполнении операции "бабочка". После выполнения БПУ по квадратурным составляющим сигнала вычисляется огибающая по приближенной формуле

X=|I1|+|I2|,

где I1 и I2 - квадратурные составляющие процесса после выполнение БПУ.

Полученная таким образом свертка входного сигнала поступает в блок усреднения 5, который вычисляет приближенную оценку мощности процесса на выходе блока корреляционного преобразования 4. Вычисленная оценка мощности процесса используется затем для нормировки отсчетов свертки входного сигнала в блоке нормировки 6.

Блок накопления корреляционных функций 7 служит для последетекторного накопления нормированной свертки входного сигнала. Дальнейшая обработка информации состоит в нахождении максимального пика корреляционной функции на выходе блока 7. Эта задача решается с помощью схемы выбора максимума 8. Найденный максимум корреляционной функции проверяется затем по критерию Вальда в решающей схеме 9, где максимум корреляционной функции сравнивается с верхним и нижним порогами. При этом, если максимум окажется больше верхнего порога, принимается решение о наличии синхросигнала, если максимум будет меньше нижнего порога, выносится решение об отсутствии синхросигнала, если же величина максимума окажется между значениями верхнего и нижнего порогов, происходит очередной цикл накопления корреляционных функций.

При превышении максимума корреляционной функции верхнего порога первый адресный генератор 15 устанавливается в начальное состояние, которое определяется кодом номера позиции этого максимума и запускается в момент перехода второго адресного генератора 14 через состояние 1000...0, после чего генератор 15 оказывается сфазированным с входным синхросигналом.

Если за все время последетекторного накопления верхний порог не будет превышен, то нулевой уровень на выходе решающей схемы инвертируется в блоке 10 в разрешает прохождение импульса с выхода блока быстрого корреляционного преобразования 4 через блок 11. Этот импульс изменяет состояние адресного счетчика 12, который управляет ПЗУ 13, где хранятся номера обратных связей первого и второго адресных генераторов 14 и 15. После этого устройство начинает вычислять свертку входного сигнала, но уже с другой М-последовательностью. Ансамбль, по которому устройство может вести поиск, определяется периодом синхросигнала и временем обработки в устройстве, чем больше их отношение, тем больше ансамбль, по которому устройство успеет вести поиск.

Недостатком данного устройства является то, что оно может работать только при низких тактовых частотах М-последовательности, т.е. когда период последовательности значительно больше времени обработки. Например, при базе сигнала N=211-1, частоте обработки fт=1 МГц и тактовой частоте F=1 кГц период М-последовательности равен

а время обработки сигнала

Таким образом, устройство успевает вести поиск ансамбля из

М-последовательностей.

При тактовой частоте F=20 кГц устройство будет успевать обрабатывать только одну М-последовательность.

Кроме этого, при больших тактовых частотах, когда Тоб>Т, последетекторное накопление становится неэффективным, во-первых, из-за влияния нестабильности тактовых частот. Например, при тактовой частоте F=1 МГц и нестабильности генераторов δ=3·10-6 разница тактовых частот приемника и передатчика может достигать

Δf=2·δ·F=2·3·10-6·106=6 Гц.

Это означает, что за время

приемник и передатчик расходятся на один символ М-последовательности, следовательно, время накопления в блоке 3 и время обработки должны быть меньше величины t. Для Тоб=80 мсек при последетекторном накоплении М-последовательности приемника и передатчика могут разойтись больше чем на один символ, что недопустимо. Во-вторых, при Тоб>Т последетекторное накопление вообще нельзя применять при обработке сигнала в реальном масштабе времени.

Цель изобретения - сокращение времени поиска ансамбля М-последовательностей при больших частотах следования символов этих последовательностей.

Поставленная цель достигается тем, что в устройство синхронизации М-последовательности, содержащее два канала последовательно соединенных перемножителя и схемы накопления, выборки и запоминания, в котором входы перемножителей соединены между собой и являются входом устройства, а вторые входы перемножителей соединены с соответствующими выходами генератора опорного напряжения, выходы схемы накопления, выборки и запоминания соединены с входами блока накопления информации, выход которого соединен с первым входом блока быстрого корреляционного преобразования, выход постоянного запоминающего устройства соединен с первыми входами первого адресного генератора и второго адресного генератора, выход которого соединен с вторым входом блока быстрого корреляционного преобразования, первый выход схемы выбора максимума соединен с вторым входом первого адресного генератора, а второй выход с первым входом решающей схемы, второй вход которой соединен с выходом блока усреднения, а выход с третьим входом первого адресного генератора, выход блока управления соединен с входами схемы накопления, выборки и запоминания, блока накопления информации, блока быстрого корреляционного преобразования, блока усреднения, схемы выбора максимума, первого и второго адресного генераторов, введены k вычислителей быстрого корреляционного преобразования, первый и второй коммутаторы и регистр, причем первые входы вычислителей быстрого корреляционного преобразования соединены с выходом блока накопления информации, а вторые входы - с первым выходом блока быстрого корреляционного преобразования, второй выход которого и выходы вычислителей быстрого корреляционного преобразования соединены с соответствующими входами первого коммутатора, выход которого соединен с входом схемы выбора максимума и входом блока усреднения, выход адресного счетчика соединен с входами блока быстрого корреляционного преобразования, первого и второго коммутатора и информационными входами регистра, тактовый вход которого соединен с первым выходом схемы выбора максимума, а выход - с вторым входом второго коммутатора, выход которого соединен с входом постоянного запоминающего устройства, управляющий вход второго коммутатора и вход адресного счетчика соединены с выходом блока управления и второй выход блока быстрого корреляционного преобразования соединен со вторым входом адресного счетчика.

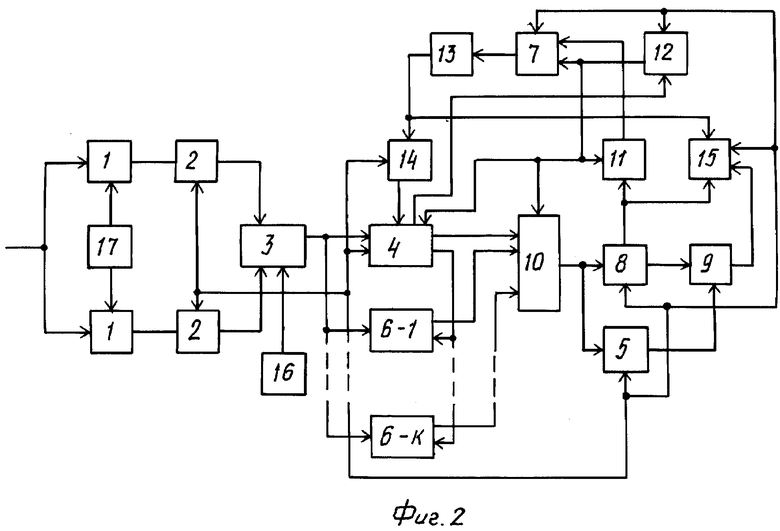

Блок-схема предлагаемого устройства приведена на фиг.2, где обозначено:

1 - перемножитель,

2 - схема накопления, выборки и запоминания,

3 - блок накопления информации,

4 - блок быстрого корреляционного преобразования,

5 - блок усреднения,

6-1...6-к - вычислители быстрого корреляционного преобразования,

7 - второй коммутатор,

8 - схема выбора максимума,

9 - решающая схема,

10 - первый коммутатор,

11 - регистр,

12 - адресный счетчик,

13 - постоянное запоминающее устройство,

14 - второй адресный генератор,

15 - первый адресный генератор,

16 - блок управления,

17 - генератор опорного напряжения.

Предлагаемое устройство работает следующим образом. На первые входы перемножителей 1 поступает аддитивная смесь синхросигнала и помехи, на вторые входы которых поступают сигналы от генератора опорного напряжения 17, сдвинутые по фазе относительно друг друга на 90°.

Информация с выходов перемножителей 1 поступает далее на схему накопления, выборки и запоминания 2, где осуществляется ее фильтрация и интегрирование на отрезке, равном длительности элементарной посылки М-последовательности и дискретизация сигнала по времени и уровню. После такого преобразования информация поступает в блок накопления информации 3, в котором происходит когерентное накопление синхронизирующей М-последовательности, а именно сложение отсчетов одного периода ШПС с соответствующими отсчетами последующего периода ШПС. Таким образом, в конечном итоге в блоке накопления информации 3 в каждом квадратурном канале хранится N отсчетов синхропоследовательности. При этом число циклов накопления определяет помехозащищенность устройства.

После окончания накопления информация из блока накопления 3 последовательно переписывается в блок быстрого корреляционного преобразования 4 и в k вычислителей быстрого корреляционного преобразования 6. Существенно, что при перезаписи информации происходит перестановка отсчетов синхропоследовательности с целью преобразования этой последовательности в одну из функций Уолша, упорядоченную по Адамару. Причем в цикле перезаписи на второй коммутатор 7 из блока управления 16 поступает команда, по которой он пропускает на выход сигналы от адресного счетчика 12. В начале цикла перезаписи счетчик 12 импульсом, поступающим с блока управления 16, устанавливается в нулевое состояние, поступающее на ПЗУ, которое из своей нулевой ячейки подает на выход код обратных связей, соответствующий первой М-последовательности. Таким образом, при перезаписи информации из блока накопления информации 3 в блок быстрого корреляционного преобразования 4 закон перестановки отсчетов синхропоследовательности задается генератором ПСП 14 со встроенными сумматорами по модулю два, которые включены в соответствии с кодом, поступающим с ПЗУ с нулевой ячейки. После перезаписи 2N отсчетов из блока быстрого корреляционного преобразования 4 на адресный счетчик 12 поступает импульс, переводя его в 1-е состояние, при этом на выход ПЗУ будет поступать код из 1-й ячейки, соответствующий второй М-последовательности. После этого начинается перезапись информации из блока накопления 3 в первый вычислитель быстрого корреляционного преобразования 6-1, но закон перестановки будет соответствовать уже второй М-последовательности. В каждый последующий i-й вычислитель информация переписывается с перестановками, соответствующими i-й М-последовательности.

После окончания перезаписи начинается непосредственная реализация БПУ, заключающаяся в многократном выполнении операции "бабочка". Причем в блоке быстрого корреляционного преобразования и вычислителях быстрого корреляционного преобразования эти операции осуществляются синхронно. После выполнения БПУ по квадратурным составляющим сигнала вычисляется огибающая по приближенной формуле

где I1 и I2 - квадратурные составляющие процесса после выполнения БПУ. Эта операция в блоке быстрого корреляционного преобразования и вычислителях также осуществляется синхронно.

Дальнейшая обработка заключается в нахождении максимальной свертки, по которой определяется входная М-последовательность и ее фаза. Для этого из блока управления поступает импульс на адресный счетчик 12 и устанавливает его в нулевое состояние. Этот код поступает на первый коммутатор 10, который пропускает на свой выход отсчеты с блока быстрого корреляционного преобразования 4. Эти отсчеты суммируются в блоке усреднения 5 и среди них выбирается максимальное значение. Причем номер позиции максимального отсчета запоминается в первом адресном генераторе 15, а в регистре 11 запоминается нулевой код, соответствующий 1-й М-последовательности. После того как будут просмотрены N отчетов с блока быстрого корреляционного преобразования, с этого же блока на адресный счетчик 12 поступает импульс и переводит его в 1-е состояние, код счетчика поступает на первый коммутатор 10, который на этом этапе будет пропускать на выход отсчеты с 1-го вычислителя быстрого корреляционного преобразования. Если на этом этапе будет найден отсчет больше, чем на предыдущем этапе, то в первом адресном генераторе 15 запоминается номер позиции максимального сигнала, а в регистре 11 запоминается код 00...1, соответствующий 2-й М-последовательности. Аналогично анализируются отсчеты остальных вычислителей. В конце анализа в регистре 11 будет храниться номер М-последовательности, давшей максимальную свертку с входной синхропоследовательностью, а в первом адресном генераторе 15 будет хранится номер позиции максимального отсчета.

После окончания анализа с блока управления 16 поступает команда на второй коммутатор 7, по которой на его выход проходит код с регистра 11, в результате на выходе ПЗУ появляется код обратных связей адресных генераторов 14 и 15, соответствующих той М-последовательности, которая дала максимальную свертку с входной синхропоследовательностью. В решающей схеме 9 происходит сравнение максимального отсчета, хранящегося в схеме выбора максимального сигнала, с приближенной оценкой мощности шума, полученной в блоке усреднения 5. Если сигнал превысит порог, то с решающей схемы 0 на первый адресный генератор 15 поступит команда, которая запустит этот генератор в момент, когда второй адресный генератор 14 будет находиться в состоянии 1000...0. С этого момента времени М-последовательность на выходе генератора 15 будет синфазна входной синхропоследовательности. Если порог не будет превышен, то весь процесс поиска повторяется.

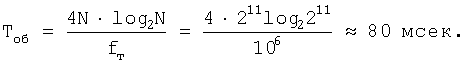

Возможная схема реализации блока быстрого корреляционного преобразования 4 представлена на фиг.3, где обозначено:

41 - ОЗУ,

42 - первый коммутатор,

43 - первый регистр,

44 - второй регистр,

45 - арифметическо-логическое устройство (АЛУ),

46 - адресный счетчик,

47 - счетчик управления,

48 - первый дешифратор,

49 - схема И,

410 - второй коммутатор,

411 - второй дешифратор,

412 - инвертор,

413...к+412 - адресные коммутаторы,

50 - третий коммутатор,

51 - дешифратор со стробированием,

52 - элемент ИЛИ,

53 - ключ.

Информация с блока накопления 3 перезаписывается в ОЗУ 41 через первый коммутатор 42 и первый в второй регистры 43, 44. Существенно, что при записи информации в ОЗУ 41 происходит перестановка поступающих отсчетов с целью преобразования входной последовательности в одну из функций Уолша, упорядоченную по Адамару. Закон перестановки отсчетов М-последовательности описан в [2]. Технически это реализуется с помощью генератора ПСП со встроенными сумматорами по модулю два, роль которого выполняет второй адресный генератор 14, при этом выходы его разрядов через третий коммутатор 50 подаются на адресные входы ОЗУ 41. Начальное состояние второго адресного генератора 14-1000...0. При перезаписи информации в нулевую ячейку ОЗУ 41 принудительно записывается нуль путем обнуления в соответствующий момент времени первого регистра 43 с помощью первого и второго дешифратора 48, 411 и схемы И 49. После этого начинается реализация алгоритма БПУ, который для выполнения операции "бабочка" требует сложной перегруппировки адресов ОЗУ 41. Осуществляется это с помощью адресных коммутаторов 413...k+412, на которые подается код с адресного счетчика 46 через третий коммутатор 50, и управление коммутаторами осуществляется счетчиком управления 47. Считываемые в определенном порядке отсчеты поступают парами с выхода ОЗУ 41 через первый коммутатор 42 в регистры 43, 44 и далее в АЛУ 45. Результаты вычисления после выполнения очередной операции "бабочка" записываются в те же ячейки ОЗУ 41, из которых была считана информация. После выполнения алгоритма БПУ над обеими квадратурными составляющими сигнала регистры 43, 44 и АЛУ 45 используются для нахождения огибающей по формуле (1). При этом операция взятия модуля выполняются путем инвертирования кода регистра 43 (сигнал "взятие модуля", СМ). Второй коммутатор 410 обеспечивает последовательное подключение сигналов "запись-считывание" (з/с), соответствующих трем режимам: записи информации в ОЗУ 41, выполнению БПУ и объединению квадратур, а также считывания информации для определения максимальной свертки. Отметим, что описанная реализация блока быстрого корреляционного преобразования 4 не отличается от реализации, предложенной в устройстве-прототипе, за исключением введения дешифратора со стробированием 51, который распределяет импульсы ВК (выбор кристалла), ключа 53 и элемента ИЛИ 52. Благодаря этому осуществляется последовательная запись информации в блок быстрого корреляционного преобразования и вычислители быстрого корреляционного преобразования, а после выполнения БПУ - считывание. При вычислении БПУ и огибающей импульсы ВК поступают одновременно на все ОЗУ, для чего от блока управления 16 на ключ 53 поступает команда, открывающая этот ключ, в результате импульс ВК будет проходить на все элементы ИЛИ.

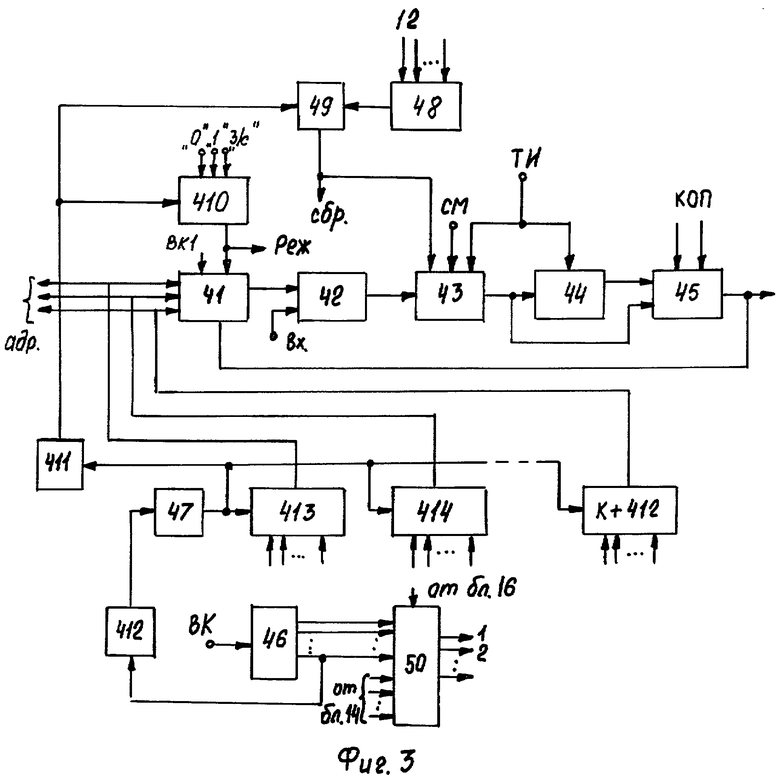

Реализация вычислителя быстрого корреляционного преобразования 6 представлена на фиг.4, из которой видно, что она отличается от реализации блока быстрого корреляционного преобразования отсутствием схем, формирующих управляющие сигналы, так как эти сигналы являются общими. Таким образом, вычислитель требует значительно меньших аппаратурных затрат, чем блок быстрого корреляционного преобразования.

Например, при использовании в вычислителе 16 разрядных чисел и применении микросхем 533ИР16 (универсальный регистр), 533 ИПЗ (АЛУ), 541РУ1 (ОЗУ), 533 КП11 (коммутатор) вычислитель будет состоять из 20 микросхем.

Таким образом, предлагаемое устройство за счет сравнительно небольших аппаратурных затрат позволяет параллельно веста поиск по ансамблю М-последовательностей, что значительно сокращает время поиска, особенно при высоких частотах следования символов ПСП, при которых последовательная обработка становится невозможной из-за ограниченного быстродействия существующей элементной базы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ СЛОЖНЫХ СИГНАЛОВ | 1987 |

|

SU1840228A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Ретранслятор | 1989 |

|

SU1707772A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к радиотехнике и может быть использовано в системах связи различного назначения для ускоренной синхронизации шумоподобных сигналов. Техническим результатом изобретения является сокращение времени поиска ансамбля М-последовательностей при больших частотах следования символов этих последовательностей. При перезаписи информации происходит перестановка отсчетов синхропоследовательности с целью преобразования этой последовательности в одну из функций Уоша, упорядоченную по Адамару. Причем в цикле перезаписи на второй коммутатор 7 из блока управления 16 поступает команда, по которой он пропускает на выход сигналы от адресного счетчика 12. Блок-схема устройства приведена на фиг.2. 4 фиг.

Устройство синхронизации М-последовательности, содержащее адресный счетчик и объединенные по первому входу два перемножителя, к вторым входам которых подключены выходы генератора опорного напряжения, а выходы первого и второго перемножителей подключены к первым входам соответственно первого и второго блоков накопления, выборки и хранения, выходы которых подключены к первому и второму входам накопителя информации, выход которого подключен к первому входу блока быстрого корреляционного преобразователя, при этом выход блока постоянной памяти подключен к первым входам первого и второго адресных генераторов, причем выход второго адресного генератора подключен к второму входу блока быстрого корреляционного преобразования, к третьему входу которого, а также к третьему входу накопителя информации, вторым входам блоков накопления, выборки и хранения, первым входам блока усреднения и блока выбора максимума и второму входу первого адресного генератора подключен выход блока управления, при этом первый и второй выходы блока выбора максимума подключены соответственно к третьему входу первого адресного генератора и первому входу решающего блока, выход которого подключен к четвертому входу первого адресного генератора, отличающееся, тем, что, с целью сокращения времени поиска ансамбля М-последовательностей при больших частотах следования символов М-последовательности, введены регистр, первый и второй коммутаторы и k вычислителей быстрого корреляционного преобразования, к первым входам которых подключен выход накопителя информации, при этом первый выход блока быстрого корреляционного преобразования подключен к вторым входам k вычислителей быстрого корреляционного преобразования, выходы которых, а также второй выход блока быстрого корреляционного преобразования подключены ко входам первого коммутатора, выход которого подключен к вторым входам блока выбора максимума и блока усреднения, выход которого подключен к второму входу решающего блока, а первый выход блока выбора максимума подключен к тактовому входу регистра, к информационному входу которого, а также к первому входу второго коммутатора, четвертому входу блока быстрого корреляционного преобразования и соответствующему входу первого коммутатора подключен выход адресного счетчика, к первому входу которого и управляющему входу второго коммутатора подключен выход блока управления, а к второму входу адресного счетчика подключен третий выход блока быстрого корреляционного преобразования, при этом выход регистра подключен к второму входу второго коммутатора, выход которого подключен ко входу блока постоянной памяти.

| Гарибян М.Л | |||

| Определение целесообразного усложнения цифровых согласованных фильтров на интегральных структурах | |||

| - Радиотехника, 1975, т.30, №10 | |||

| Авт | |||

| св | |||

| Ректификационная колонна | 1991 |

|

SU1810075A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

2006-07-20—Публикация

1985-06-21—Подача