Изобретение относится к области радиосвязи и может быть использовано в радиостанциях и на приемных центрах для автоматизации поиска приемных каналов, свободных от помех.

Известны устройства автоматического поиска каналов радиосвязи, содержащие приемник, коммутатор радиочастот, блоки предварительного и основного времени анализа; схему И, триггер, коммутатор порогов сравнения, схему сравнения, блок формирования эталонного сигнала, электронно-перестраиваемый аттенюатор, блок формирования времени анализа инверсного элемента, блок выбора помех наименее надежного элемента адресной кодограммы (Авторские свидетельства №464980 "Устройство контроля качества каналов связи" МКИ Н 04 J 3/04, G 01 Д 21/00 от 25.3.75 г., №362497 "Устройство автоматического поиска каналов связи" Н 04 В 1/10, Н 04 J 1/16 от 9.2.73 г.).

Однако эти устройства определяют канал связи путем сравнения некоторого напряжения, характеризующего качества канала связи, с одним или двумя порогами. С другой стороны возможны ситуации, когда в системе связи все каналы хуже некоторого порогового значения (т.е. на всех каналах уровень напряжения, характеризующего качество данного канала, больше порогового значения, формируемого коммутатором порогов). В этом случае приведенные устройства не обеспечивают выбор лучшего канала приема, так как считается, что все каналы непригодны для радиосвязи.

Для систем возможны связи как с дальних (предельных) расстояний, так и с близких, когда связь может обеспечиваться за счет энергетического превышения уровня полезного сигнала над помехой. В этом случае приведенные устройства не обеспечивают выбор канала с минимумом помех, т.е. канала, в котором наблюдается минимальное превышение помех над пороговым значением.

Кроме того, все приведенные устройства - аналоги обеспечивают выбор канала приема адресной кодограммы по значению помех в данный момент времени, совершенно не учитывая характер изменения уровня помех в канале по времени, отсюда возможен ошибочный выбор канала приема, вследствие того, что канал, хороший для связи в данный момент, в процессе вхождения в связь и информационного обмена может стать совершенно непригодным для этих целей из-за изменения уровня помех в канале, т.е. не оценивается качество канала связи на все время ведения связи с некоторой среднестатической длительностью. Последнее обстоятельство особенно важно для интенсивной помеховой обстановки, которая будет наблюдаться в подвижных адаптивных системах радиосвязи низового звена управления для современных информационных нагрузок.

Из известных устройств наиболее близким к предлагаемому устройству является устройство, принятое за прототип.

блок-схема которого приведена на фиг.1. Устройство состоит из следующих блоков:

1 - блок предварительного времени анализа;

2 - блок основного времени анализа;

3 - ключ;

4 - коммутатор порогов сравнения;

5 - блок формирования импульса "проба";

6 - ключ;

7 - схема сравнения;

8 - коммутатор радиочастот;

9 - триггер;

10 - приемник;

11 - схема И;

12 - линия задержки;

13 - блок формирования времени анализа инверсного элемента;

14 - блок выбора помех наименее надежного элемента адресной кодограммы;

15 - блок формирования эталонного сигнала;

16 - электронно-перестраиваемый аттенюатор;

17 - ключ эталонного сигнала.

Основные блоки устройства-прототипа связаны следующими функциональными связями:

Вход приемника 10 соединен через последовательно соединенные ключи эталонного сигнала 17, электронно-перестраиваемый аттенюатор 16 и блок формирования эталонного сигнала 15 с выходом блока формирования времени анализа инверсного элемента 13 и со входом блока выбора помех наименее надежного элемента адресной кодограммы 14, второй вход которого соединен с выходом приемника 10 и через ключ 3 с корпусом. Первый выход блока 14 соединен со вторым входом электронно-перестраиваемого аттенюатора 16, а второй выход соединен с первым входом схемы сравнения 7, второй вход которой соединен через ключ 6 с выходом коммутатора порогов сравнения 4, а выход соединен со входом триггера 9, входом блока 13 и через коммутатор радиочастот 8 со вторым входом приемника 10, второй выход которого соединен со вторым входом блока формирования эталонного сигнала 15, а третий выход соединен со входом схемы И 11, второй вход которой соединен с выходом блока 2 через последовательно соединенные триггер 9 и линию задержки 12, а выход схемы И 11 соединен со входами блоков 1 и 2, причем второй выход блока 2 соединен со вторым входом блока 13 и через блок формирования импульса "проба" 5 со вторым входом ключа 6, третий выход блока 2 соединен со входом ключа 3 и со входом ключа эталонного сигнала 17, а четвертый выход соединен со входом коммутатора порогов сравнения 4, второй вход которого соединен со вторым выходом блока формирования импульса "проба" 5, а третий вход соединен с выходом блока 1, второй выход которого соединен с первым входом блока 5, а второй вход блока 5 соединен со вторым выходом блока 13, третий вход блока 1 и третий вход блока 2 соединен со входом тактовых импульсов запуска.

Работа устройства - прототипа заключается в следующем. При поступлении импульса запуска ТИ, определяющего начало анализа, блоки 1 и 2 формируют импульсы напряжения, длительность которых определяет предварительное и основное время анализа. Эти импульсные напряжения поступают на ключ 3, коммутатор порогов сравнения 4, блок формирования импульса "проба" 5, на блок формирования времени анализа инверсного элемента 13 и ключ эталонного сигнала 17.

Ключ 3 закрывается, обеспечивая нарастание потенциала на выходе блока выбора помех наименее надежного элемента адресной кодограммы 14 за счет напряжения помех, поступающих с выхода приемника 10.

Блок формирования эталонного сигнала 15 при анализе любого из выбранных М частотных радиоканалов представляет собой неперестраиваемый генератор элементов адресной кодограммы и элементов инверсной (к адресной) кодограмме.

Адресная кодограмма подается в смеситель приемника 10 через электронно-перестраиваемый аттенюатор 16 и замкнувшийся ключ эталонного сигнала 17. Напряжение управления, подаваемое на электронно-перестраиваемый аттенюатор 16 с блока 14, пропорционально уровню воздействующих помех, т.е. чем больший уровень помех имеется на выходе приемника 10, тем больший уровень напряжения управления подается на аттенюатор 16 и тем меньше ослабление эталонного сигнала, подаваемого в приемник 10 от блока формирования эталонного сигнала 15.

При этом блок формирования времени анализа инверсного элемента 13 выдает сигнал о формировании "прямой" кодограммы ("прямой" элемент адресной кодограммы) на блок формирования эталонного сигнала 15 на базе опорной частоты с синтезатора частот приемника, подаваемой через дополнительный выход приемника 10. В блоке выбора помех наименее надежного элемента адресной кодограммы 14 осуществляется коммутация, необходимая для обработки этого сигнала и обеспечивающая нарастание потенциала на одном из входов схемы сравнения 7 за счет действия помех на сигнал "прямой" кодограммы.

На выходе коммутатора порогов сравнения 4 устанавливается пороговый потенциал сравнения, соответствующий принятому для предварительного анализа за счет действия импульса, поступающего на него с блока предварительного времени анализа 1, но выход которого пока отключен от схемы сравнения 7, так как ключ 6 закрыт потенциалом, поступающим на него с блока формирования импульса "проба" 5. Выход коммутатора 4 к схеме сравнения 7 подключается на короткое время, равное действию импульса "проба" на ключ 6, формирующегося блоком 5 в конце интервала времени предварительного анализа. Если за время предварительного анализа потенциал на выходе блока 14 окажется выше, чем пороговый потенциал сравнения, поступающий на схему сравнения 7 с коммутатора порогов сравнения 4, то схема сравнения 7 выдает на коммутатор радиочастот 8 сигнал о переключении приемника 10 на следующий канал.

Коммутатор радиочастот 8 переключает приемник 10 на новую частоту, после чего сигнал об окончании перестройки приемника 10 поступает через схему И 11, подготовленную триггером 9 на повторный запуск блоков 1 и 2.

Триггер 9 устанавливается в исходное состояние импульсом с блока основного времени анализа 2 через линию задержки 12. Начинается новый анализ на следующем канале.

Если на входе схемы сравнения 7, соединенного с выходом блока 14, за время предварительного анализа потенциал не превышает порогового потенциала сравнения, то схема сравнения 7 не выдает команду на перестройку приемника 10, ключ 6 закрывается и отключает выход коммутатора порогов сравнения 4, на котором устанавливается пороговый потенциал сравнения, принятый для основного времени анализа. При этом, если в период основного времени анализа пороговое напряжение не превышено, то блок 13 в результате воздействия импульса окончания основного времени анализа с одного из выходов блока 2 (при условии отсутствия импульса на выходе схемы сравнения 7) выдает импульс в блоки 1 и 2 на новый запуск схемы. Одновременно с этим выдаются сигналы смены кодограммы на инверсную в блок формирования эталонного сигнала 15 и в блок выбора помех наименее надежного элемента адресной кодограммы 14. После чего описанная выше процедура повторяется заново, но при этом происходит анализ помехоустойчивости приема инверсной кодограммы (элемента кодограммы).

Если же в результате накапливания помех в блоке 14 за время основного анализа потенциал основного анализа превышен, то схема сравнения 7 выдает сигнал о перестройке приемника 10 на следующий канал на коммутатор радиочастот 8 и одновременно этот же сигнал перебросит триггер 9, так что на выходе триггера 3 устанавливается логическая единица, после перестройки на следующий канал с выхода приемника 10 подается импульс окончания перестройки на схему И 11, которая пропускает этот импульс на блоки 1 и 2 для начала нового цикла анализа на следующем канале.

Из описания работы следует, что канал считается пригодным для качественного приема адресной кодограммы, если не будет превышено ни одно пороговое значение коммутатора порогов сравнения 4 (как для "прямой", так и для "инверсной" кодограммы) на данном канале.

Таким образом, из описания работы устройства-прототипа следует, что оно, как и все перечисленные аналоги, имеет низкую надежность выбора оптимального канала приема адресной кодограммы вызова.

Целью предлагаемого устройства является устранение отмеченного недостатка.

Эта цель достигается исключением из блок-схемы устройства-прототипа блока предварительного времени анализа, коммутатора порогов сравнения, ключа, блока формирования импульса "проба" и схемы сравнения и введением в блок-схему двух матриц памяти качества каналов, блока экстраполяции, М-1 схем разности, М-1 сумматоров, многовходовой схемы сравнения и шифратора.

При этом выбор оптимального канала производится следующим образом. С выхода блока выбора помех наименее надежного элемента адресной кодограммы напряжение, характеризующее качество канала за основное время анализа, поступает на матрицу памяти качества каналов, где происходит запоминание этой величины, затем таким же образом записывается напряжение, характеризующее качество канала за основное время анализа по инверсной кодограмме, причем из двух величин окончательно остается записанной большая величина (либо анализ по "прямой" кодограмме, либо по "инверсной" кодограмме), а меньшая величина стирается и теряется. Записанное напряжение характеризует помеховые условия на данном канале. Затем подобным же образом происходит анализ на следующем канале с последующим выбором большего напряжения и его записью в следующую ячейку памяти.

Описанная процедура повторяется на всех М радиоканалах. В результате чего в матрице памяти качества каналов окажется записанным столбец значений результатов анализа на М каналах, после чего происходит новый цикл анализа с записью его результатов в новый столбец матрицы памяти качества каналов и так далее.

В блоке экстраполяции происходит вычисление возможных результатов анализа за время, равное некоторой среднестатистической длительности переговора между абонентами в системе связи, т.е. осуществляется предсказание будущих результатов анализа за определенное время по результатам анализа качества каналов, записанных в первой матрице памяти качества каналов. Результаты этой экстраполяции записываются во вторую матрицу памяти качества каналов, после чего выбирается канал, результаты предсказания в котором оптимальные, т.е. в нем помехи будут иметь меньшую величину, чем в оставшихся (М-1) каналах.

Причем результаты экстраполяции выдаются сразу после одного цикла анализа по всем М каналам, а затем происходит более точная экстраполяция по мере заполнения столбцов первой матрицы памяти качества каналов.

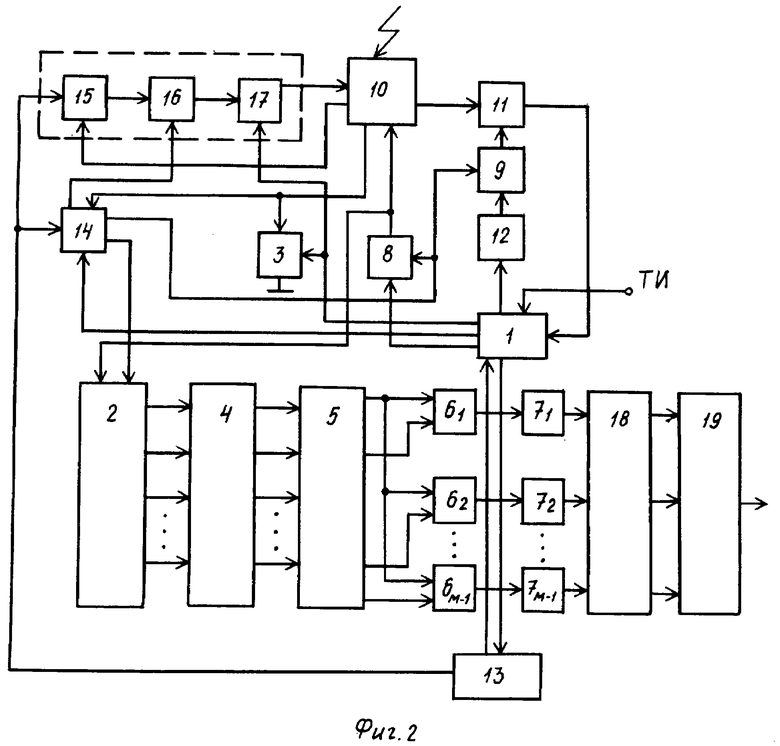

Блок-схема предлагаемого устройства изображена на фиг.2. На схеме использованы следующие обозначения:

1 - блок основного времени анализа;

2, 5 - матрицы памяти качества каналов;

3 - ключ;

4 - блок экстраполяции;

61, 62...6м-1 - схема разности;

71, 72...7м-1 - сумматор;

8 - коммутатор радиочастот;

9 - триггер;

10 - приемник;

11 - схема И;

12 - линия задержки;

13 - блок формирования времени анализа инверсного элемента;

14 - блок выбора помех наименее надежного элемента адресной кодограммы;

15 - блок формирования эталонного сигнала;

16 - электронно-перестраиваемый аттенюатор;

17 - ключ эталонного сигнала;

18 - многовходовая схема сравнения;

19 - шифратор.

Отдельные блоки предлагаемого устройства имеют следующие функциональные связи.

Вход приемника 10 подключен через последовательно соединенные ключ эталонного сигнала 17, электронно-перестраиваемый аттенюатор 16 и блок формирования эталонного сигнала 15 к выходу блока формирования времени анализа инверсного элемента 13 и со входом блока выбора помех наименее надежного элемента адресной кодограммы 14, второй вход которого соединен с выходом приемника 10 и через ключ 3 с корпусом, первый выход блока 14 соединен со вторым входом электронно-перестраиваемого аттенюатора 16, второй выход блока 14 соединен со входом коммутатора радиочастот 8 и со входом триггера 9, а третий выход соединен со входом матрицы памяти качества каналов 2, второй вход которого соединен со вторым входом приемника 10 и коммутатор радиочастот 8 с выходом блока основного времени анализа 1, второй выход которого подключен через последовательно соединенные линию задержки 12 и триггер 9 ко входу схемы И 11, второй вход которой соединен со вторым выходом приемника 10, третий выход которого соединен со вторым входом блока формирования эталонного сигнала 15, а выход схемы И 11 соединен со входом блока 1, второй вход которого соединен со вторым выходом блока 13, вход которого соединен со вторым выходом блока 1, третий вход которого соединен со входом тактовых импульсов ТИ, четвертый выход соединен со вторым входом ключа 3 и со вторым входом ключа эталонного сигнала 17, а пятый выход 1 соединен с третьи входом блока 14.

Выходы матрицы памяти качества каналов 2 соединены с соответствующими входами блока экстраполяции 4, выходы которого соединены с соответствующими входами второй матрицы памяти качества каналов 5, первый выход которого соединен с первыми входами схем разности 61, 62...6м-1, вторые входы которых соединены с соответствующими выходами второй матрицы памяти качества каналов 5, выходы схем разности 61, 62,...6м-1 соединены через сумматоры 71, 72,...7м-1 с соответствующими входами многовходовой схемы сравнения 18, выходы которой соединены с соответствующими входами шифратора 19.

Предлагаемое устройство, изображенное на фиг.2, работает следующим образом.

При поступлении импульса запуска ТИ, определяющего начало анализа, блок основного времени анализа 11 формирует импульсное напряжение, которое подается на коммутатор радиочастот 8. Под действием этой команды коммутатор радиочастот 8 перестраивает приемник 10 на первый выбранный канал для начала анализа. После перестройки приемника 10 сигнал об окончании перестройки с его выхода подается на вход схемы И 11, на второй вход которой подается логическая единица с выхода триггера 9, установленная на нем при включении. Сигнал окончания перестройки приемника 10 проходит через схему И и поступает на вход блока основного времени анализа 1. Под действием этого сигнала блок 1 вырабатывает импульсные напряжения, длительности которых обеспечивают работы схемы.

Эти импульсные напряжения поступают на ключ 3, ключ эталонного сигнала 17, на блок формирования времени анализа инверсного элемента 13, на линию задержки 12 и на блок выбора помех наименее надежного элемента адресной кодограммы 14. Ключ 17 замыкается и начинает пропускать эталонный сигнал с блока 15 через электронно-перестраиваемый аттенюатор 16 на соответствующий вход приемника 10, ключ 3 размыкается, обеспечивая нарастание помех и эталонного сигнала, прошедшего через приемник 10, на входе блока14.

Импульсное напряжение также подается на вход линии задержки, которое после задержки на время перестройки переведет триггер 9 в другое устойчивое состояние, когда на его выходе будет логический нуль, запрещающий через схему И 11 новый запуск блока 1 до окончания анализа на данном канале. Импульсное напряжение переводит блок формирования времени анализа инверсного элемента 13 в состояние, когда на его выходе формируется сигнал, переключающий блок 15 на генерирование "прямой" адресной кодограммы и переводящий блок 14 на обработку "прямой" адресной кодограммы, кроме того, в блок 14 подается с блока 1 напряжение, определяющее время анализа эталонного сигнала в этом блоке. В процессе анализа "прямой" адресной кодограммы с генератора эталонного сигнала 15, подаваемой через блок 16 и ключ эталонного сигнала 17 на вход приемника 10, напряжение управления, подаваемое на электронно-перестраиваемый аттенюатор 16 с блока 14, пропорционально уровню воздействующих помех на данном канале, т.е. чем больше уровень помех на выходе приемника 10 (на входе блока 14), тем больше уровень напряжения управления подается на аттенюатор 16 и тем меньше ослабление эталонного сигнала от блока 15, подаваемого на вход приемника 10. Конечный уровень управляющего напряжения, подаваемого на аттенюатор 16, будет таким, при котором декодирование эталонного сигнала в блоке 14 произойдет с заданной достоверностью. После этого в конце основного времени анализа "прямой" адресной кодограммы с блока выбора помех наименее надежного элемента адресной кодограммы 14 на вход матрицы памяти качества каналов 2 поступит сигнал, характеризующий качество анализируемого канала по "прямой" адресной кодограмме эталонного сигнала, который запишется в первую ячейку памяти матрицы 2.

После этого анализ качества по "прямой" адресной кодограмме заканчивается. С блока формирования времени анализа инверсного элемента 13 на вход блока формирования эталонного сигнала 15 и на вход блока 14 поступает команда смены кодограммы на "инверсную". По этой команде блок формирования эталонного сигнала 15 формирует "инверсную" адресную кодограмму, которая подается на вход приемника 10, одновременно эта команда переводит блок 14 на обработку "инверсной" адресной кодограммы. Начинается анализ качества по "инверсной" кодограмме, который осуществляется по описанной выше процедуре. После того, как произойдет декодирование "инверсной" адресной кодограммы в блоке 14 с заданной достоверностью в конце основного времени анализа, с блока 14 поступит напряжение, характеризующее качество анализируемого канала на вход матрицы памяти качества каналов 2. Если это напряжение больше уже записанного в первой ячейке напряжения, характеризующего качество анализа по "прямой" адресной кодограмме, то происходит перезапись большего напряжения в первую ячейку. Если же это напряжение меньше уже хранящегося в первой ячейке напряжения анализа по "прямой" адресной кодограмме, то перезаписи не будет, т.е. всегда в первой ячейке будет записано большее напряжение, характеризующее качество анализа (по "прямой" либо по "инверсной" адресной кодограмме) на данном канале, чем обеспечивается запись худшего результата анализа на данном канале.

Одновременно с этими действиями блок 14 выдает команду конца анализа на коммутатор радиочастот 8, который дает команду перестройки приемника 10 на следующий канал, и команду на вход триггера 9, устанавливая его в состояние, когда на его выходе - логическая единица, которая подает на вход схемы И 11. После окончания перестройки приемника 10 на следующий канал с его выхода поступает на вход схемы И 11 команда конца перестройки, которая проходит схему И и поступает на вход блока основного времени анализа 1, запуская его на формирование импульсов анализа на этом следующем канале. Описанная выше процедура анализа качества канала по "прямой" и "инверсной" адресной кодограмме полностью повторяется, также полностью повторяется и запись результатов анализа в матрицу памяти качества каналов 2 за исключением того, что под действием кода номера канала с коммутатора радиочастот 8, подаваемого на соответствующий вход матрицы памяти качества каналов 2, запись результатов анализа производится в следующую (вторую) ячейку памяти первого столбца ячеек матрицы памяти качества каналов 2.

Таким образом, описанная процедура последовательно повторяется на всех М выделенных для связи каналах, в результате чего первый столбец матрицы памяти качества каналов 2 будет хранить результат анализа на каналах за первый цикл анализа. После того как пройдет один цикл анализа на всех М каналах, и окажется записанным один столбец матрицы памяти качества каналов 2, производится считывание значений результатов анализа качества из ячеек первого столбца матрицы 2 в блок экстраполяции 4. В блоке 4 производится экстраполяция считываемых значений на время, равное среднестатической длительности переговора τ в данной группе для данных информационных нагрузок (эта величина является априорно заданной), т.е. по известному результату анализа качества канала в данный момент времени прогнозируется качество этого же канала на последующее время τ. Экстраполяция осуществляется следующим образом.

Пусть  - число точек экстраполяции,

- число точек экстраполяции,

где Е(х) - целая часть величины х,

ta - время цикла анализа всех М каналов, т.е. если в данный момент проанализировался некоторый канал, то через ta вновь будет анализироваться этот же канал.

Следовательно, на интервале прогнозирования укладывается К циклов анализа радиоканалов, и поэтому можно результаты прогнозирования запомнить в виде К значений ожидаемого состояния канала.

Количество исходных значений качества анализа в канале (число столбцов в матрице памяти качества 2), вообще говоря, произвольно, однако примем его равным К, т.е. по предыдущему качеству канала за время τ до настоящего момента, прогнозируется качество на последующее время τ за данным моментом.

Пусть y1, y2,...yk - результаты анализа качества некоторого i-го канала (они записаны в i строку матрицы памяти качества канала 2), т.е. это напряжения, характеризующие качество канала в различные моменты времени и получающиеся на выходе блока выбора помех наименее надежного элемента адресной кодограммы 14 после первого цикла анализа (величина y1), после второго цикла анализа (величины y2) и т.д., если в данном канале анализ не проводился, то все y1, y2,...yk равны нулю, если проводился один раз, то отличен от нуля только y1 и т.д.

По значениям y1, у2,...yk в блоке экстраполяции 4 осуществляется экстраполяция (прогнозирование) следующих K значений результатов анализа качества канала, эти напряжения обозначим как yk+1, yk+2,...y2k, которые и несут информацию о поведении помеховых условий данного канала на последующее время τ. Методов экстраполяции величин yk+1, yk+2,...y2k интерполяционными методами существует достаточного много (интерполяционная формула Лагранжа, интерполяционная формула Ньютона, итерационно-интерполяционный метод Эйткена и другие, так как для экстраполяции применимы все интерполяционные методы), конкретный выбор реализации блока экстраполяции 4 определяется требуемой точностью экстраполяции.

Примерный вариант блока экстраполяции 4 предлагается в следующем виде.

После одного цикла анализа качества каналов происходит считывание значений y1, y2,...yk (из которых только y1 отличен от нуля) из матрицы памяти качества каналов 2 в блок экстраполяции 4.

Так как экстраполяция по одному значению невозможна, то значение y1 записывается в соответствующую строку ячеек в матрице памяти качества каналов 5, следовательно, после первого цикла анализа  равны

равны

(верхний индекс указывает на номер цикла), т.е. считается, что качество канала будет неизменным за следующее время τ и равным y1. После второго цикла анализа произойдет новое считывание значений y1, y2,...yk (из которых уже отличны от нуля y1 и y2).

По величинам y1 и y2 в блоке экстраполяции 4 осуществляется экстраполяция значений

в следующем виде:

Эти значения поступают в соответствующую строку матрицу памяти качества каналов 5, где записывается, стирая прежние значения, т.е. экстраполяция значений анализа качества канала обновляется после каждого цикла, причем экстраполяционные значения уточняются в результате каждого цикла анализа. После третьего цикла анализа отличны от нуля значения y1, y2, y3.

По ним определяются следующие значения, но вначале определяются промежуточные значения:

Затем определяются экстраполяционные значения:

которые записываются в строку матрицы памяти качества каналов 5, стирая прежние значения в этой строке, т.е. экстраполяция станет более точной, чем после второго цикла.

Описанная процедура повторяется вплоть до K-цикла, в результате которого в матрицу памяти качества каналов 5 запишутся величины:

После этого цикла анализа в экстраполяции участвовали все y1, y2,...yk, так как они все отличны от нуля. После нового (k+1) цикла анализа в матрице памяти качества каналов 2 произойдет стирание y1, сдвиг величин y2, y3,...yk в строке влево на одну ячейку, так что К ячейка станет свободной, куда и запишется новое значение анализа после (k+1) цикла. Т.е. произойдет обновление величин y1, y2,...yk (здесь уже роль y1 выполняет старое значение y2 и т.д.).

После этого вновь произойдет считывание значений в блок экстраполяции 4 и определение значении  которые запишутся в матрицу памяти качества каналов 5.

которые запишутся в матрицу памяти качества каналов 5.

Таким образом, осуществляется экстраполяция помехового состояния канала на будущий интервал τ.

Можно показать, что описанная процедура при своей простоте достаточно эффективна, т.е. значения yk+1, yk+2,...y2k лежат возле истинной кривой помеховых условий от времени.

На следующем канале описанная процедура повторяется полностью, как и на всех М каналах, в результате чего прогнозируются помеховые условия всех М каналов на будущее время τ.

Реализация блока экстраполяции 4 в соответствии с описанной процедурой экстраполяции для случая k=4 изображена на фиг.3, где введены следующие обозначения:

1 - счетчик циклов;

3, 23 - распределители;

4 - датчик чисел;

6, 7, 8, 9 - ячейки памяти;

10, 11, 12 - схемы разности;

13, 14, 15 - умножители;

16, 17, 18, 19, 20 - сумматоры;

22, 21 - делители.

Основные блоки устройства, изображенного на фиг.3, имеют следующие функциональные связи.

Выход счетчика циклов 1 соединен со входами распределителей 3, 23. Выходы распределителя 3 соединены с соответствующими входами ячеек памяти 6, 7, 8, 9. Выход ячейки памяти 6 соединен со входом схемы разности 10, со входом сумматора 16 и со входом распределителя 23. Выход ячейки памяти 7 соединен со вторым входом схемы разности 10, со входом сумматора 17 и со входом схемы разности 11. Выход ячейки памяти 8 соединен со вторым входом схемы разности 11, со входом сумматора 18 и со входом схемы разности 12, второй вход которой соединен с выходом ячейки памяти 9.

Выход схемы разности 10 соединен со входом умножителя 13, второй вход которого соединен с выходом датчика чисел 4 и со входами умножителей 14 и 15, а выход соединен со вторым входом сумматора 16, входом которого соединен со вторым входом распределителя 23 и со входом сумматора 19. Выход схемы разности 11 соединен со вторым входом умножителя 14, выход которого соединен со вторым входом сумматора 19, выход которого через делитель 21 соединен с третьим входом распределителя 23 и со входом сумматора 20. Выход схемы разности 12 соединен со вторым входом умножителя 15, выход которого соединен со вторым входом сумматора 18, выход которого соединен со вторым входом сумматора 20, выход которого через делитель 22 соединен с четвертым входом распределителя 23. Для наглядности составлены связи блока с блоком 2, 5 в соответствии с фиг.2.

Схема работает следующим образом. После первого цикла анализа счетчик циклов 1 выдаст в распределители 3 и 23 управляющий сигнал, по которому распределитель 3 обеспечит считывание величины y1 из матрицы памяти 2 и запись ее в ячейку памяти 6, на остальных его входах будут нули, т.к. отлична от нуля только величина y1. Распределитель 23 обеспечивает запись величины y1 с выхода ячейки памяти 6 в строку матрицы памяти качества каналов 5, остальные блоки схемы на этом цикле не работают.

После второго цикла под действием сигналов счетчика циклов 1 распределитель 3 обеспечивает запись в ячейки памяти 6 и 7 величин y1 и y2, соответственно, распределитель 23 подключит выход сумматора 16 на вход матрицы памяти качества каналов 5. В схеме разности 10 произойдет вычитание y2-y1. Эта величина подается на вход умножителя 13, на второй вход которого последовательно подадутся числа k+1, k+2,...2k, т.е. в нашем случае 5, 6, 7, 8. На выходе умножителя 13 получим набор чисел 5 (y2-y1), 6 (y2-y1), 7 (y2-y1), 8 (y2-y1), которые подадутся на вход сумматора 16, где сложатся с величиной y1, т.е. на выходе сумматора имеем величины экстраполяции

которые через распределитель 23 запишутся в соответствующую строку матрицы памяти качества каналов 5. После третьего цикла анализа распределитель 3 обеспечит запись в ячейки памяти 6, 7, 8 величин y1, y2, y3. Распределитель 23 подключит выход делителя 21 на вход матрицы памяти качества каналов 5. По описанной выше методике на выходе сумматора 16 получатся значения

которые через распределитель 23 запишутся в соответствующую строку матрицы памяти качества каналов 5. После третьего цикла анализа распределитель 3 обеспечит запись в ячейки памяти 6, 7, 8 величин y1, y2, y3. Распределитель 23 подключит выход делителя 21 на вход матрицы памяти качества каналов 5. По описанной выше методике на выходе сумматора 16 получатся значения

На выходе схемы разности 11 получится величина y3-y2, а на выходе умножителя 14 получатся величины 5 (y3-y2), 6 (y3-y2), 7 (y3-y2), 8 (y3-y2), которые подаются на вход сумматора 17, где суммируются с величиной y2, т.е. на выходе сумматора 17 получаются величины

, которые суммируются с величинами

, которые суммируются с величинами

в сумматоре 19 и после деления на 2 в делителе 21 получаются величины

в сумматоре 19 и после деления на 2 в делителе 21 получаются величины

которые через распределитель 23 подадутся в матрицу памяти качества каналов 5. После четвертого цикла анализа распределитель 3 обеспечит запись величин y1, y2, y3, y4 в ячейки памяти 6, 7, 8, 9, соответственно. По описанной выше процедуре на выходе делителя 21 получаются значения

которые через распределитель 23 подадутся в матрицу памяти качества каналов 5. После четвертого цикла анализа распределитель 3 обеспечит запись величин y1, y2, y3, y4 в ячейки памяти 6, 7, 8, 9, соответственно. По описанной выше процедуре на выходе делителя 21 получаются значения

, которые подаются на вход сумматора 20. На выходе схемы разности 12 получится величина y4-y3, на выходе умножителя 15 получатся величины 5 (y4-y3), 6 (y4-y3), 7 (y4-y3), 8 (y4-y3), которые в сумматоре 18 просуммируются с величиной y3, подаваемой из ячейки памяти 8. На выходе сумматора 18, следовательно, получатся величины

, которые подаются на вход сумматора 20. На выходе схемы разности 12 получится величина y4-y3, на выходе умножителя 15 получатся величины 5 (y4-y3), 6 (y4-y3), 7 (y4-y3), 8 (y4-y3), которые в сумматоре 18 просуммируются с величиной y3, подаваемой из ячейки памяти 8. На выходе сумматора 18, следовательно, получатся величины

, которые затем суммируются с величинами

, которые затем суммируются с величинами

в сумматоре 20 и после деления на 2 в делителе 22 получатся величины

в сумматоре 20 и после деления на 2 в делителе 22 получатся величины

которые через распределитель 23 поступают в матрицу памяти качества каналов 5. После пятого цикла управляющие сигналы счетчика циклов 1 останутся неизменными, так как счетчик уже переполнен и больше состояние не меняет.

которые через распределитель 23 поступают в матрицу памяти качества каналов 5. После пятого цикла управляющие сигналы счетчика циклов 1 останутся неизменными, так как счетчик уже переполнен и больше состояние не меняет.

Следовательно, предыдущая процедура (после четвертого цикла) полностью повторяется, однако на вход распределителя 3 из матрицы памяти качества каналов 2 поступят сдвинутые на одно значение величины y2, y3, y4, y5, которые в схеме переобозначаются в новые значения y1, y2, y3, y4, после происходит экстраполяция описанным способом.

Как следует из описания работы блока экстраполяции 4 на фиг.3, в матрицу памяти качества каналов 5 после каждого цикла анализа на каждом канале происходит запись прогнозирования помеховых условий каналов на ближайшее время τ путем записи K чисел в строку матрицы.

После записи данных экстраполяции в матрицу памяти качества каналов 5 сразу же после первого и каждого последующего цикла анализа всех М каналов радиосвязи происходит выбор оптимального канала связи с учетом прогнозирования, который осуществляется следующим образом:

В системах разности 61, 62,...6m-1 последовательно вычисляются величины разности значений качества каждого канала относительно первого, т.е. на выходе схемы разности 61 имеем величины

где в скобках указаны каналы, на которых получены величины

На выходе схемы разности 62 имеем величины

На выходе схемы разности 62 имеем величины

и т.д.

и т.д.

Эти разности затем суммируются в сумматорах 71, 72,...7м-1, так, что на выходах сумматоров получаются величины суммарного отклонения качества соответствующего канала относительно первого. Чем больше величины напряжений на выходе сумматоров 71, 72...7м-1, тем хуже качество данных каналов относительно первого. Если на выходе какого-нибудь сумматора 7i-1 напряжение равно нулю, то это значит, что i канал имеет качество, равное первому каналу. Если же для i канала величина напряжения на выходе сумматора 7i-1 меньше нуля, то это означает, что качество i канала лучше, чем качество первого канала. В общем случае на выходах сумматоров 71, 72...7м-1 может быть часть напряжений меньше нуля, часть напряжений равны нулю, часть напряжений больше нуля. Эти напряжения подаются на соответствующие входы многовходовой схемы сравнения 18, которая осуществляет выбор наименьшего (с учетом знака) напряжения качества каналов. В результате сравнения всех напряжений в многовходовой схеме сравнения 18 на ее соответствующем выходе появится логическая единица, т.е. на выходе имеем десятичный код лучшего канала связи, который затем преобразуется в двоичный код лучшего канала в шифраторе 19. Таким образом, на выходе устройство имеет код номера лучшего канала связи. После каждого цикла анализа всех М каналов происходит обновление информации, и вновь по описанной процедуре выбирается лучший радиоканал. Код номера лучшего канала связи далее может быть использован по желанию для установки приемника 10 на этот канал путем подачи кода на коммутатор радиочастот 8, либо код может быть использован для установки на лучший канал связи любого другого приемо-передатчика.

Как следует из описания работы предлагаемого устройства, после одного цикла анализа всех М каналов осуществляется просто выбор лучшего из них в данное время, следовательно, если экстраполяция не нужна или изменения помех в каналах таковы, что экстраполяция не эффективна, то достаточно оставить счетчик циклов 1 блока экстраполяции 4 в состоянии "1" постоянно. В этом случае экстраполяция отключается. При включенной экстраполяции обновление и уточнение экстраполяции осуществляется после каждого цикла анализа всех М каналов.

Следует отметить, что если помеховая обстановка на радиоканалах стационарна во времени, то устройство выбирает лучший текущий радиоканал за один цикл анализа, так как во времени качество этого лучшего текущего канала будет неизменно. В общем случае, однако, лишь некоторую часть времени помеховая обстановка радиоканалов будет стационарной по сравнению с длительностью переговоров в системе радиосвязи, а в остальное время (значительно большее) помеховая обстановка каналов связи будет существенно нестационарной, что делает необходимым экстраполяцию помех в радиоканале при выборе лучшего канала приема.

Таким образом, достигается поставленная цель, а именно: повышается надежность выбора оптимального канала приема адресной кодограммы вызова.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1977 |

|

SU1840702A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1978 |

|

SU1840438A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1978 |

|

SU1840437A1 |

| СПОСОБ АДАПТАЦИИ КАНАЛОВ РАДИОСВЯЗИ С ИСПОЛЬЗОВАНИЕМ ИСКУССТВЕННОГО ИНТЕЛЛЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2405265C2 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ УГЛОВОЙ ОРИЕНТАЦИИ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2014 |

|

RU2553270C1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

Изобретение относится к области радиосвязи и может быть использовано в радиостанциях и на приемных центрах для автоматизации поиска приемных каналов, свободных от помех. Техническим результатом является повышение точности выбора оптимального канала. Устройство содержит приемник, коммутатор радиочастот, элемент И, линию задержки, триггер, блок основного времени анализа, блок формирования времени анализа инверсного элемента, блок выбора помех, блок формирования эталонного сигнала, аттенюатор, ключ, блок памяти качества каналов с экстраполятором, вычитатель, сумматор, блок сравнения и шифратор. Устройство может быть снабжено счетчиком циклов, датчиком чисел, двумя распределителями, умножителем, блоком памяти, вычитателем, сумматором и двумя делителями. После одного цикла анализа всех каналов осуществляется выбор лучшего из них в данное время. При включенной экстраполяции обновление и уточнение экстраполяции осуществляется после каждого цикла анализа всех каналов. 1 з.п. ф-лы, 3 ил.

Устройство автоматического поиска каналов радиосвязи для адаптивных адресных систем, содержащее приемник, вход которого соединен с выходом коммутатора радиочастот, а выход - с первым входом элемента И, второй вход которого соединен с выходом блока основного времени анализа через последовательно соединенные линию задержки и триггер, выход элемента И соединен с первым входом блока основного времени анализа, второй вход которого соединен с первым выходом блока формирования времени анализа инверсного элемента, второй выход которого соединен со входом блока выбора помех и через последовательно соединенные блок формирования эталонного сигнала, аттенюатор, второй вход которого соединен с выходом блока выбора помех, и ключ подключен ко второму входу приемника, второй выход которого соединен со вторым входом блока выбора помех, а третий - со вторым входом блока формирования эталонного сигнала, отличающееся тем, что, с целью повышения точности выбора оптимального канала, введены блок памяти качества каналов с экстраполятором, вычитатель, сумматор, блок сравнения и шифратор, причем второй выход блока выбора помех соединен со вторыми входами триггера и коммутатора радиочастот, а третий выход соединен с входом блока памяти качества каналов с экстраполятором, второй вход которого соединен с выходом коммутатора радиочастот, а выходы через вычитатель и сумматор подключены к блоку сравнения, выходы которого соединены с входами шифратора.

Авторы

Даты

2007-03-10—Публикация

1979-01-05—Подача