VI

О

ел

N СЬ

пределитель 8. Распределитель 8 обеспечивает считывание из блока 19 бит предыдущей кодограммы, который сравнивается с текущим битом с помощью элемента 20 сравнения, после чего текущий бит записывается в регистр 9. Регистр 9 накапливает код признака-маркера начала кодограммы, который декодируется дешифратором 18. Сигнал маркера с дешифратора 18 сбрасывает в нуль содержимое соответствующей

ячейки в блоке 10, который является многоканальным счетчиком бит и формирует адресную часть для блока 19 памяти. При совпадении бит предыдущей и последующей кодограмм в блоке 11 накапливается число совпавших кодограмм и при достижении порогового числа выдается сигнал совпадения на выход 24 устройства. 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для индикации | 1989 |

|

SU1686474A1 |

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Устройство для приема информации | 1988 |

|

SU1562950A1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| Устройство для фиксации сбоев | 1987 |

|

SU1462320A1 |

Изобретение относится к вычислительной технике и может быть использовано в многоканальных резервированных системах обработки информации в последовательных кодах. Цель изобретения - повышение производительности за счет сравнения кодов всех каналов с различной информацией в одном цикле. Устройство содержит генератор 3 импульсов, счетчик 4, элементы НЕ 5, 6, 7, распределитель 8 импульсов, регистр 9, блоки 10, 11 суммирования, триггеры 12, 13, элемент ИЛИ-НЕ 14, элементы И 15, 16, ИЛИ 17, дешифратор 18, блок 19 памяти, элемент 20 сравнения. Счетчик 4 через блоки 1, 2 опрашивает цепи запросов и информации каналов. При обнаружении запроса от канала счетчик 4 адресует этот канал, выбирает соответствующие ячейки в блоках 10, 11 суммирования и включает рас

Изобретение относится к вычислительной технике и может быть использовано в многоканальных системах обработки информации для выделения достоверной информации путем кодового голосования.

Целью изобретения является повышение производительности за счет сравнения кодов всех каналов с различной информацией в одном цикле.

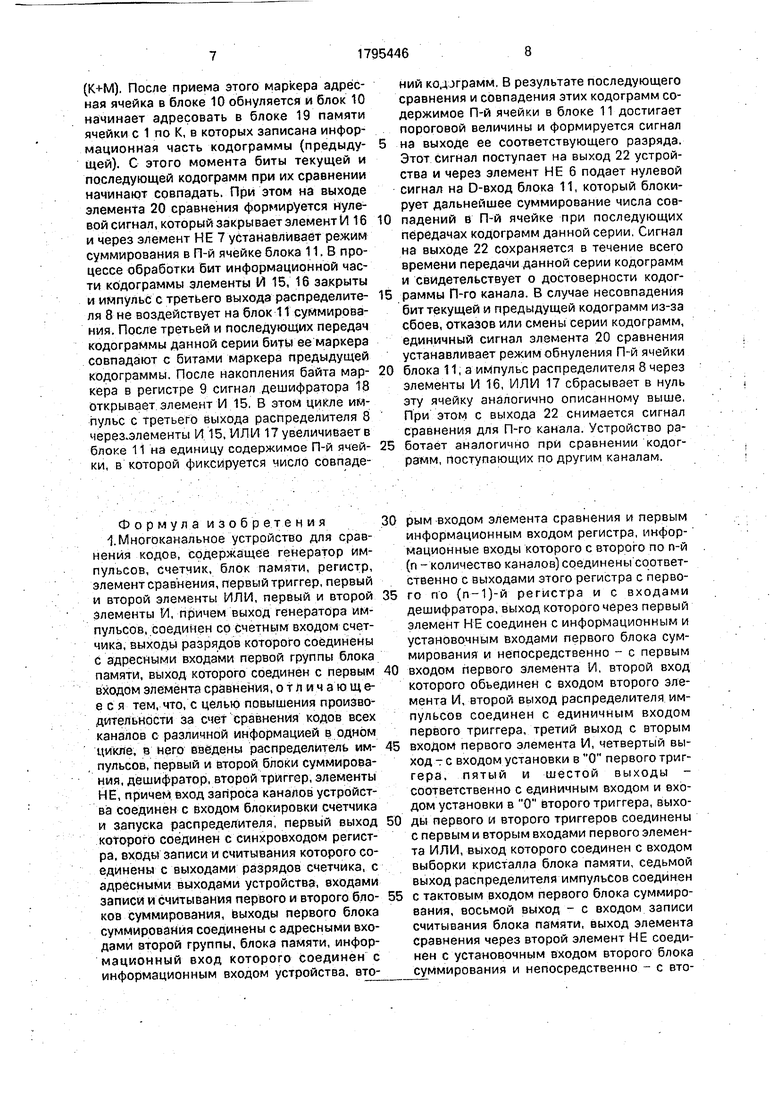

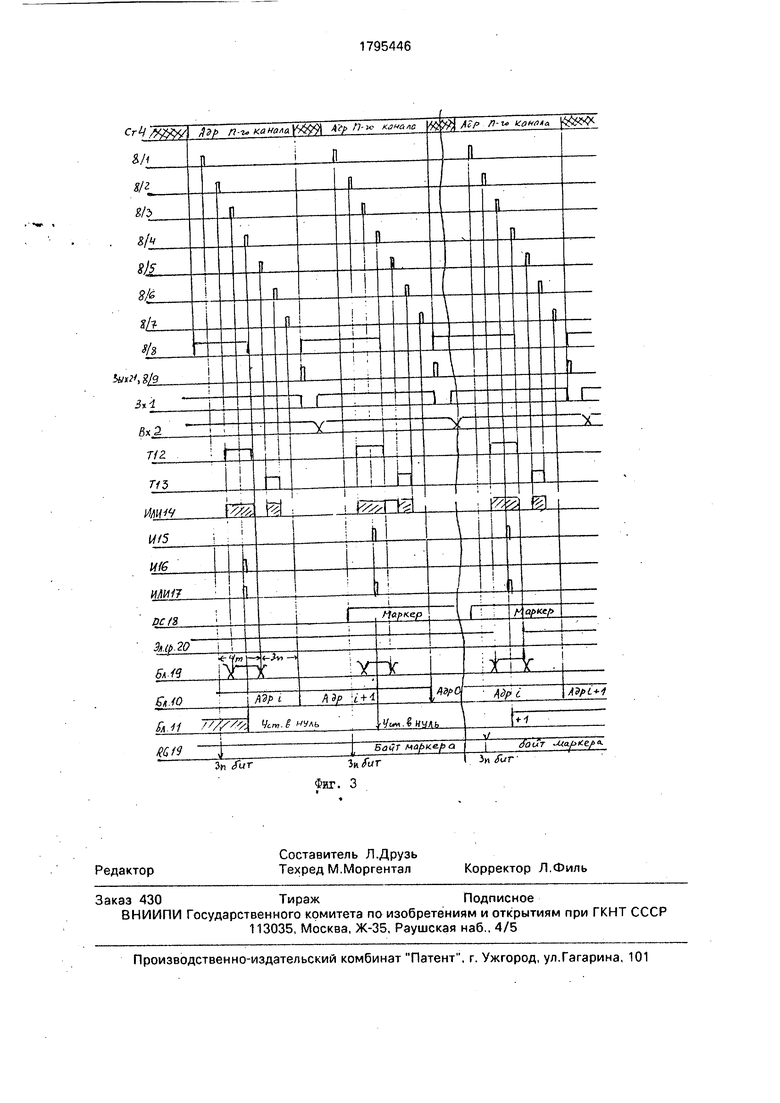

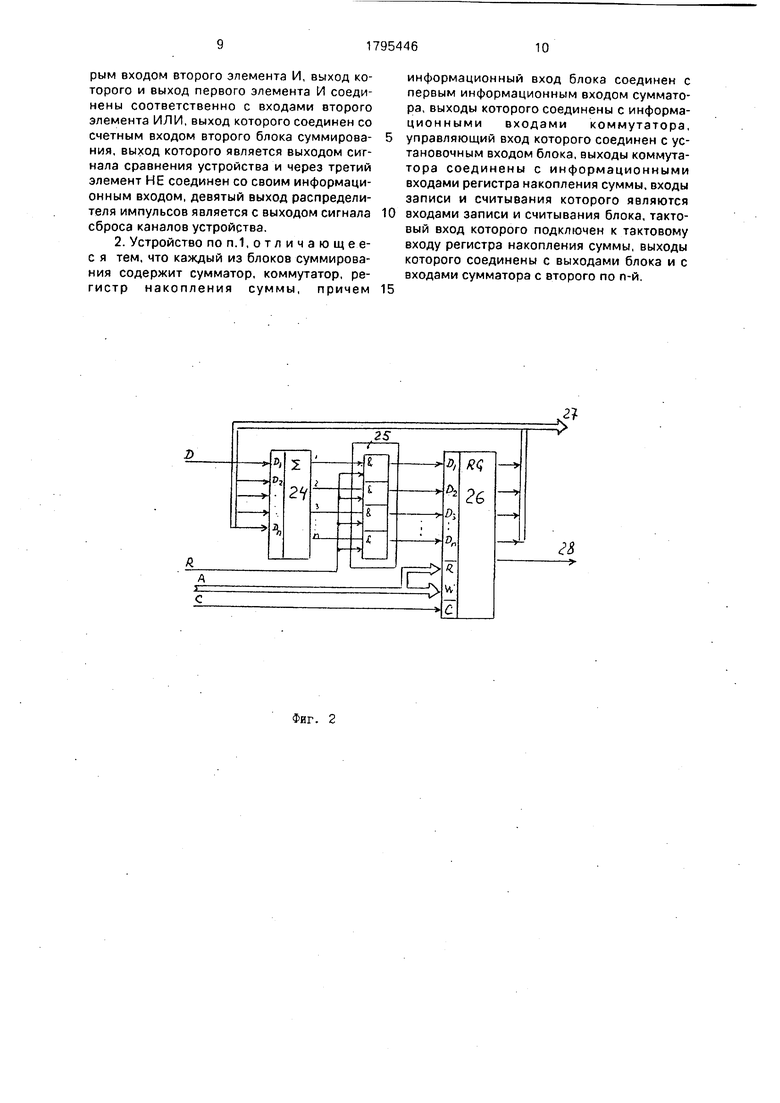

Функциональная схема устройства приведена на фиг, 1, схема выполнения блоков суммирования - на фиг. 2, временная диаграмма работы устройства - на фиг. 3.

Устройство содержит вход 1 запросов каналов, вход 2 информации каналов, генератор 3 импульсов, счетчик 4, элементы НЕ 5, 6,7, распределитель 8 импульсов, регистр 9, блоки 10, 11 суммирования, триггеры 12, 13, элемент ИЛИ 14, элементы И 15, 16, элемент ИЛИ 17, дешифратор 18, блок 19 памяти, элемент 20 сравнения (ИСКЛЮЧАЮЩЕЕ ИЛИ), выход 21 сброса каналов, выход 22 сигнала сравнения, выходы 23 адресов каналов. Блоки 10, 11 суммирования содержат сумматор 24, коммутатор 25, регистр 26 накопления сумм, выходы 27 номера бита, выход 28 порогового значения суммы..

Устройство работает следующим образом.

В исходном положении триггеры 12, 13, счетчик 4 установлены в нулевое положение. На входе 1 установлен единичный сигнал, который удерживает в нулевом положении распределитель 8 и подает сигнал разрешения счета на управляющий вход счетчика 4. После включения генератора 3 счетчик 4 начинает циклический счет тактовых импульсов и формирует на выходах 23 последовательность адресов каналов, обслуживаемых устройством. Канал, опрашиваемый счетчиком 4, выставляет запрос на обслуживание по входу 1 устройства в виде

сигнала низкого уровня, который блокирует счетчик 4 и снимает сигнал сброса с входа пуска распределителя 8. На выходах счетчика 4 устанавливается адрес П-го канала, требующего обслуживания. Информация П-го канала подается по входу 2 устройства, в последовательном коде, бит за битом, в виде кодограмм, содержащих признак начала кодограмм - маркер и информационную

часть, Для достоверности передача одной и той же кодограммы по данному каналу многократно повторяется в виде серии некоторое пороговое число раз до передачи следующей кодограммы другого содержания. Формат кодограмм разных серий может быть разным, максимальная длина серии определяет разрядность элементов устройства. Счетчик 4 адресует в регистре 9 ячейку П-го канала, в которой содержится

информация, принятая по П-му каналу в предыдущих циклах обслуживания канала, За счет обратной связи с выходов регистра 9 на группу его входов, сдвинутых на один разряд, обеспечивается преобразование

последовательного кода в параллельный. При этом текущий бит записывается на место первого разряда данной ячейки, а все предыдущие биты записываются в следующие разряды этой ячейки, и происходит

сдвиг кода по разрядам ячейки в каждом цикле опроса данного канала. Накапливаемый параллельный код подается с выходов регистра 9 на дешифратор 18 маркера. Если код в П-й ячейке регистра 9 не является

маркером кодограммы, то на выходе дешифратора 18 сигнал не формируется. При этом элемент И 15 закрыт и через элемент НЕ 5 на входы D, R блока 10 суммирования подается единичный сигнал, обеспечивающий

режим суммирования числа принимаемых бит поданному каналу. В блоках 10, 11 счетчик 4 также адресует ячейки П-го канала. Блок 10 предназначен для суммирования

числа бит, поступающих по каждому из П каналов, формирует адрес-номер бит и выполняет функции многоканального счетчика бит. Блок 11 предназначен для суммирования числа маркеров совпавших кодограмм при их сравнении, поступающих по П-му каналу, выполняет функции многоканального счетчика совпадающих кодограмм и формирует сигнал сравнения по пороговому критерию для каждого канала. Суммирование сигналов в блоках 10, 11 производится следующим образом. В регистре 26 блоков 10,11 каждому каналу соответствует ячейка, адресуемая по входам запись/чтение счетчиком 4 устройства. При подаче П-го адреса на вход R регистра 26 на выходах последнего формируется код, предыдущий и содержащийся в П-й ячейке регистра. Этот код подается на группу входов сумматора 24, где суммируется с единицей, подаваемой на D-вход сумматора 24. При подаче единичного сигнала на вход R блоков 10. 11 открывается коммутатор 25 и последующий код суммы сигналов с выходов сумматора 24 поступает на D-входы регистра 26 в ячейку, адресуемую по входам W, R счетчиком 4; Запись суммы в эту ячейку производится импульсным сигналом, подаваемым на вход С регистра 26. Для установки в нуль содержимого ячейки П-ro канала по входу R блоков 10, 11 подается нулевой сигнал, коммутатор 25 закрывается, на D-входы регистра 26 подаются нулевые сигналы и в ячейку, адресуемую по входам запись/чтение записывается нулевой код, импульс записи подается на С-вход регистра 26. После запуска распределитель 8 выполняет один цикл обработки бита информации П-ro канала, В начале цикла на восьмом выходе распределителя 8 установлен единичный сигнал, который задает режим чтения на входе запись/чтение блока 19 памяти. На адресные входы блока 19 памяти поступают со счетчика 4 - адрес П-ro канала, с выходов блока 10 суммирования - адрес бита, принятого для данного канала в предыдущем цикле. Импульс с первого выхода распределителя 8 производит запись текущего бита с входа 2 в ячейку регистра 9, адресуемую счетчиком 4. Импульс со второго выхода распределителя 8 включает триггер 12, который через элемент ИЛИ 14 подает сигнал выборки кристалла на вход CS блока 19 памяти. Из блока 19 по указанному адресу считывается бит идентичной кодограммы, принятый для данного канала в предыдущем цикле передачи этой кодограммы. Этот бит подается на элемент 20 сравнения, на другой вход которого поступает текущий бит с входа 2 и производится сравнение бит

предыдущей и последующей кодограммы. При передаче по П-му каналу кодограммы в первый раз ее биты не совпадают с битами, хранящимися в ячейках блока 19 памяти. 5 При несовпадении бит на входах элемента сравнения 20 на его выходе формируется единичный сигнал, который открывает элемент И 16 и через элемент НЕ 7 устанавливает режим обнуления ячейки данного

0 канала в блоке 11 суммирования. Импульс с третьего выхода распределителя 8 через элементы И 16, ИЛИ 17 записывает нулевой код, т.е. сбрасывает в нуль ячейку блока 11, адресуемую счетчиком 4. Импульс с четвер5 того выхода распределителя 8 сбрасывает в. нуль триггер 12.

При этом на восьмом выходе распределителя 8 устанавливается нулевой потенциальный сигнал, соответствующий режиму

0 записи информации на входе запись/чтение блока 19 памяти. Импульс с пятого выхода распределителя 8 включает триггер 13, который через элемент ИЛИ 14 подает сигнал выборки на блок 19 памяти. В блоке 19

5 на место бита предыдущей кодограммы записывается текущий бит последующей кодограммы в ячейку, адресуемую счетчиком 4 и блоком 10 суммирования. Импульс с шестого выхода распределителя 8 сбрасывает в

0 нуль триггер 13. Импульс с седьмого выхода распределителя 8 увеличивает на единицу содержимое ячейки в блоке 10, импульс с девятого выхода-через выход 21 сбрасывает сигнал запроса П-го канала. На этом цикл

5 обработки бита П-го канала заканчивается. После, снятия сигнала запроса П-ro канала на входе 1 снова формируется единичный сигнал, который сбрасывает в нуль распределитель 8 и включает счетчик 4 в режим

0 опроса каналов. При обнаружении запроса другого или П-го канала организуется обработка запроса данного канала аналогично описанному выше. После накопления в регистре 9 байта маркера кодограммы П-го

5 канала на выходе дешифратора 18 формируется единичный сигнал, который через элемент НЕ 5 устанавливает в блоке 10 суммирования режим сброса в нуль ячейки П-го канала. 8 текущем цикле распредели0 тель 8 импульсом с седьмого выхода устанавливает в нуль П-ю ячейку, после чего в ней начинается счет бит информационной части кодограммы П-го канала. После первой передачи информационной части кодог5 раммы, содержащей К бит, в блоке 10 фиксируется адрес К и соответственно в блоке 19 памяти эта информация запишется в ячейках с 1 по К. Во время второй передачи кодограммы ее маркер, содержащий М бит, разместится в блоке 19 в ячейках с (К+1) по

(К+М). После приема этого маркера адресная ячейка в блоке 10 обнуляется и блок 10 начинает адресовать в блоке 19 памяти ячейки с 1 по К, в которых записана информационная часть кодограммы (предыдущей). С этого момента биты текущей и последующей кодограмм при их сравнении начинают совпадать. При этом на выходе элемента 20 сравнения формируется нулевой сигнал, который закрывает элемент И 16 и через элемент НЕ 7 устанавливает режим суммирования в П-й ячейке блока 11. В процессе обработки бит информационной части кодограммы элементы И 15, 16 закрыты и импульс с третьего выхода распределителя 8 не воздействует на блок 11 суммирования. После третьей и последующих передач кодограммы данной серии биты ее маркера совпадают с битами маркера предыдущей кодограммы. После накопления байта маркера в регистре 9 сигнал дешифратора 18 открывает элемент И 15, В этом цикле импульс с третьего выхода распределителя 8 через.элементы И 15, ИЛИ 17 увеличивает в блоке 11 на единицу содержимое П-й ячейки, в которой фиксируется число совпадеФормула и з о б р е.т.е н и я 1.Многоканальное устройство для сравнения кодов, содержащее генератор импульсов, счетчик, блок памяти, регистр, элемент сравнения, первый триггер, первый и второй элементы ИЛИ, первый и второй Элементы И, причем выход генератора импульсов, соединен со счетным входом счетчика, выходы разрядов которого соединены с адресными входами первой группы блока памяти, выход которого соединен с первым входом элемента сравнения, о f л и ч а ю щ е- е с я тем, что, с целью повышения производительности за счет сравнения кодов всех каналов с различной информацией в одном цикле, в негр введены распределитель импульсов, первый и второй блоки суммирования, дешифратор, второй триггер, элементы НЕ, причем вход запроса каналов устройства соединен с входом блокировки счетчика и запуска распределителя, первый выход которого соединен с синхровходом регистра, входы записи и считывания которого соединены с выходами разрядов счетчика, с адресными выходами устройства, входами записи и считывания первого и второго блоков суммирования, выходы первого блока суммирования соединены с адресными входами второй группы, блока памяти, информационный вход которого соединён с информационным входом устройства, втоний кодограмм, В результате последующего сравнения и совпадения этих кодограмм содержимое П-й ячейки в блоке 11 достигает пороговой величины и формируется сигнал

на выходе ее соответствующего разряда. Этот сигнал поступает на выход 22 устройства и через элемент НЕ 6 подает нулевой сигнал на D-вход блока 11, который блокирует дальнейшее суммирование числа соападений в П-й ячейке при последующих передачах кодограмм данной серии. Сигнал на выходе 22 сохраняется в течение всего времени передачи данной серии кодограмм и свидетельствует о достоверности кодограммы П-го канала. В случае несовпадения бит текущей и предыдущей кодограмм из-за сбоев, отказов или смены серии кодограмм, единичный сигнал элемента 20 сравнения устанавливает режим обнуления П-й ячейки

блока 11, а импульс распределителя 8 через элементы И 16, ИЛИ 17 сбрасывает в нуль эту ячейку аналогично описанному выше. При этом с выхода 22 снимается сигнал сравнения для П-ro канала. Устройство работаёт аналогично при сравнении кодограмм, поступающих по другим каналам.

рым входом элемента сравнения и первым информационным входом регистра, информационные входы которого с второго по п-й (п-количествоканалов)соединены соответственно с выходами этого регистра с первого по (п-1)-й регистра и с входами дешифратора, выход которого через первый элемент НЕ соединен с информационным и установочным входами первого блока суммирования и непосредственно - с первым

входом первого элемента И, второй вход которого объединен с входом второго элемента И, второй выход распределителя импульсов соединен с единичным входом первого триггера, третий выход с вторым

входом первого элемента И, четвертый выход - с входом установки в О первого триггера, пятый и шестой выходы - соответственно с единичным входом и входом установки в О второго триггера, аыходы первого и второго триггеров соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом выборки кристалла блока памяти, седьмой выход распределителя импульсов соединен

с тактовым входом первого блока суммирования, восьмой выход - с входом записи считывания блока памяти, выход элемента сравнения через второй элемент НЕ соединен с установочным входом второго блока суммирования и непосредственно - с вторым входом второго элемента И, выход которого и выход первого элемента И соединены соответственно с входами второго элемента ИЛИ, выход которого соединен со счетным входом второго блока суммирования, выход которого является выходом сигнала сравнения устройства и через третий элемент НЕ соединен со своим информационным входом, девятый выход распределителя импульсов является с выходом сигнала сброса каналов устройства.

Фиг. 2

0

5

информационный вход блока соединен с первым информационным входом сумматора, выходы которого соединены с информа- ционными входами коммутатора, управляющий вход которого соединен с установочным входом блока, выходы коммутатора соединены с информационными входами регистра накопления суммы, входы записи и считывания которого являются входами записи и считывания блока, тактовый вход которого подключен к тактовому входу регистра накопления суммы, выходы которого соединены с выходами блока и с входами сумматора с второго по п-й.

| Устройство для сравнения кодов | 1984 |

|

SU1171778A1 |

| Устройство для сравнения кодов | 1988 |

|

SU1509869A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-02-15—Публикация

1990-11-01—Подача