Изобретение относится к области вычислительной техники и может быть использовано в вычислительном устройстве управления лучом фазированных антенных решеток (ФАР).

К современным ФАР предъявляются высокие требования по разрешающей способности, скорости переключения луча в пространстве с одного направления на другое, числу рабочих частот, надежности работы, простоте конструкции и технологичности изготовления.

Степень удовлетворения ФАР этим требованиям в значительной мере зависит от параметров и характеристик вычислительного устройства распределения фаз по элементам ФАР, которое должно управлять большим числом элементов ФАР, иметь высокое быстродействие, обеспечивать надежную работу ФАР в формировании диаграммы направленности при простой конструкции и высокой степени унификации устройств.

Известно обладающее высоким быстродействием вычислительное устройство (ВУ) с табличным хранением кодов управления в запоминающих устройствах (ЗУ), описанное в статье В.И. Лебедя "Некоторые способы построения управляющей машины для сканирования луча антенны типа "фазированная решетка". Вопросы специальной радиоэлектроники, серия XII общетехническая, выпуск 5, I966 г., выполненное следующим образом. Раскрыв антенны разбивается на подрешетки. ЗУ управляют всеми излучателями лишь одной подрешетки, которую называют основной. После суммирования информации из ЗУ отклонения луча по азимуту и ЗУ отклонения луча по углу места в сумматорах основной подрешетки, полученные суммы переписываются в соответствующие сумматоры всех остальных подрешеток. Для фазирования подрешеток между собой на сумматоры каждой подрешетки из специальных ЗУ фазирования подрешеток по азимуту и углу места заносятся соответствующие коды. В результате получается распределение фаз по всему раскрыву, соответствующее выбранному направлению луча в пространстве.

К недостаткам этого ВУ следует отнести зависимость объема ЗУ от дискретности перемещения луча и сектора обзора. При работе ФАР в диапазоне частот каждой частоте должно соответствовать свое ЗУ, что увеличивает объем оборудования ВУ в целом. Существенным недостатком также является большое число проводов между подрешетками, что значительно усложняет конструкцию ФАР и технологию ее изготовления, а также низкая надежность работы ФАР с таким ВУ, т.к. при любом отказе в ЗУ одновременно на большое число фазовращателей поступит неверное значение кодов управления, что приведет к отклонению луча ФАР от выбранного направления.

Наиболее близким по технической сущности является ВУ, описанное в статье Д.М. Зарезнова "Некоторые способы построения цифровых вычислительных устройств для управления лучом антенны типа "фазированная решетка" в РЛС", Вопросы специальной радиоэлектроники, серия общетехническая, выпуск 21, 1968 г., обеспечивающее вычисление кодов управления элементами ФАР по каждой из координат (азимут, угол места) путем логического суммирования кодов, полученных непосредственно из кода целеуказания. ВУ содержит вычислитель кодов управления, подключенный своим входом к выходу вычислителя дифференциального фазового сдвига, а соответствующие выходы которого являются выходами устройства по одной из координат. При необходимости управления по двум координатам применяется два таких ВУ с последующим суммированием соответствующих кодов в сумматорах каждого из элементов ФАР.

В вычислителе кодов управления вычисляются коды для управления нечетными элементами путем суммирования кодов, получаемых из кода целеуказания. Для первого элемента код не вычисляется, а используется код целеуказания соответствующей разрядности. Для получения кода для второго элемента вычисления не требуются, а код получается путем монтажного сдвига кода целеуказания на один разряд в сторону старших разрядов. Аналогично получаются коды для элементов с номером 2n путем сдвига кода целеуказания на n разрядов в сторону старших разрядов. Код для третьего, пятого и девятого элементов получается путем суммирования кода первого элемента соответственно с кодом второго, четвертого и восьмого элементов. Для шестого элемента код получается путем сдвига на один разряд в сторону старших разрядов кода третьего элемента, а для седьмого - путем суммирования кодов первого и шестого элементов. Аналогично вычисляются коды управления остальными элементами ФАР.

Описанное ВУ имеет ряд существенных недостатков. Устройства, входящие в вычислитель кодов управления, не могут быть унифицированы без большого избытка оборудования, т.к. этот вычислитель не имеет повторяющейся структуры, а тот факт, что многие коды управления получаются из кодов управления другими элементами, существенно снижает надежность работы ФАР, т.к. ошибка в одном коде приводит к неверному управлению несколькими элементами, а так как коды управления в ФАР подаются одновременно на столбцы или строки элементов ФАР, то такая ошибка в одном коде приводит к неверному управлению большим числом элементов ФАР, а это ведет к отклонению луча от заданного направления. Существенно усложняет конструкцию ФАР и усложняет технологию изготовления необходимость подводки кодов управления к элементам ФАР при двухкоординатном управлении во взаимно перпендикулярных направлениях.

Целью настоящего изобретения является устранение перечисленных недостатков, а именно упрощение конструкции и повышение надежности работы ФАР путем независимого вычисления кодов управления элементами подрешеток, на которые разбит раскрыв антенны.

Для достижения указанной цели введены для первой подрешетки первый датчик кода номера подрешетки и первый вычислительный блок кодов управления элементами подрешетки, в котором к упомянутому вычислителю кодов управления подключены множительное устройство и группа сумматоров, при этом первый вход множительного устройства соединен с выходом вычислителя дифференциального фазового сдвига, второй - с выходом датчика кода номера подрешетки, а выход - с первыми входами группы сумматоров, вторые входы которых соединены с соответствующими выходами вычислителя кодов управления, а выход множительного устройства совместно с выходами группы сумматоров являются выходами вычислительного блока кодов управления элементами подрешетки, а для второй, третьей и n-й подрешеток к выходу соответствующего датчика кода номера подрешетки и выходу упомянутого вычислителя дифференциального фазового сдвига подключен второй, третий и n-й вычислительный блок кодов управления элементами подрешеток, выполненный аналогично первому, а выходом устройства являются выходы всех вычислительных блоков кодов управления элементами подрешеток.

Применение предлагаемого вычислительного устройства позволяет унифицировать аппаратуру подрешеток ФАР, значительно сократить количество проводов между подрешетками до числа, равного суммарной разрядности двух дифференциальных фазовых сдвигов при двухкоординатном управлении, и тем самым существенно упростить конструкцию и повысить технологичность изготовления ФАР, а также в связи с независимым вычислением кодов управления для элементов подрешеток повысить надежность работы ФАР по управлению лучом.

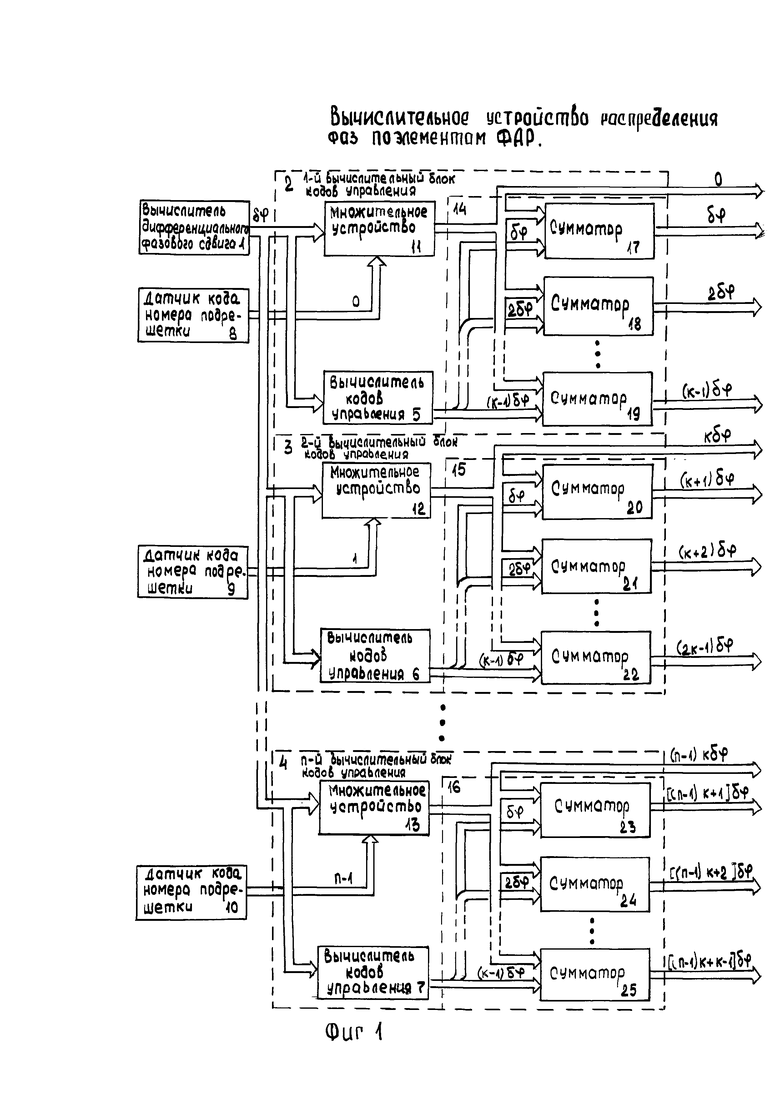

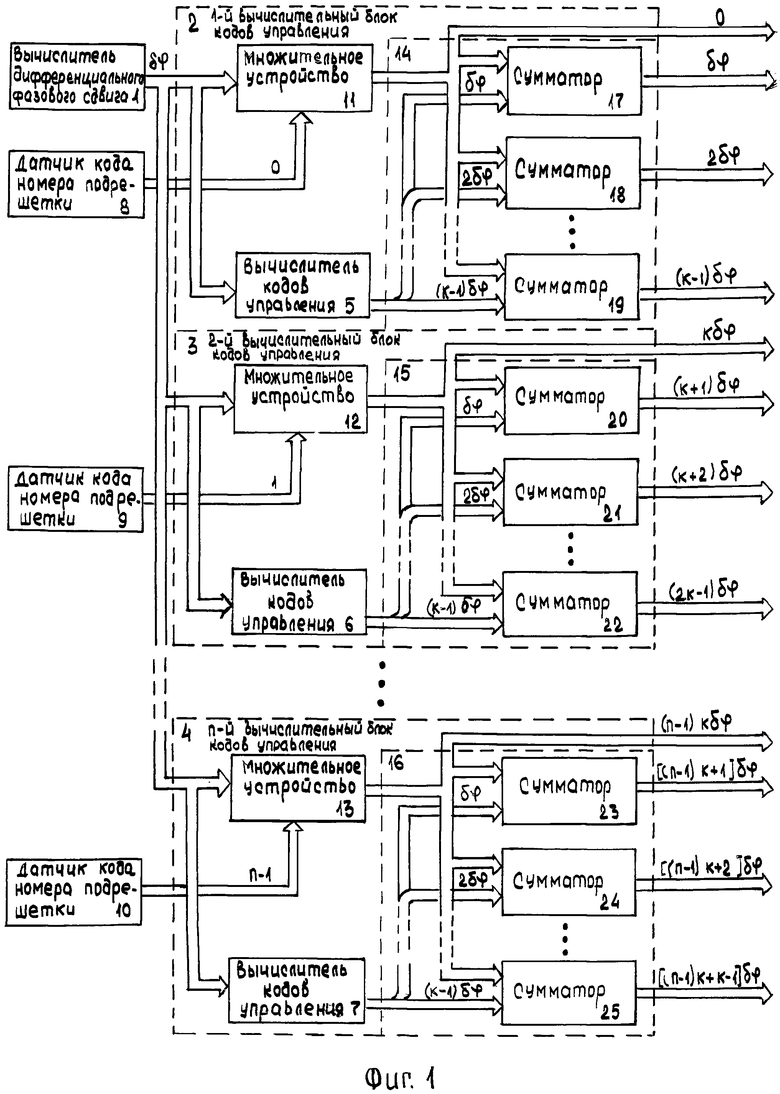

Сущность изобретения иллюстрируется фиг. 1, на которой представлен пример структурной схемы вычислительного устройства распределения фаз по элементам ФАР для одного ряда n подрешеток, управляющего их к элементами по одной координате.

Предлагаемое вычислительное устройство содержит вычислитель дифференциального фазового сдвига 1, вычислительные блоки кодов управления элементами подрешеток 2, 3 и 4, вычислители кодов управления 5, 6 и 7, датчики кодов номеров подрешеток 8, 9 и 10, множительные устройства 11, 12 и 13, группы сумматоров 14, 15 и 16 с сумматорами 17÷25.

Выход вычислителя дифференциального фазового сдвига 1 подключен параллельно к первым входам множительных устройств 11, 12 и 13 и входам вычислителей кодов управления 5, 6 и 7, вторые входы множительных устройств подключены к выходам соответствующих датчиков кода номера подрешетки 8, 9 и 10, выходы множительных устройств 11, 12 и 13 параллельно подключены к первым входам сумматоров 17÷25 соответствующих групп сумматоров 14, 15 и 16, вторые входы этих сумматоров подключены к соответствующим выходам вычислителей кодов управления 5, 6 и 7. Выходами устройства являются выходы множительных устройств 11, 12 и 13 и выходы сумматоров 17÷25.

Предлагаемое вычислительное устройство для ФАР, содержащей восемь элементов в строке (столбце) подрешетки работает следующим образом. Код с выхода вычислителя дифференциального фазового сдвига 1 поступает параллельно на входы вычислительных блоков кодов управления элементами подрешеток 2, 3 и 4, в которых они поступают на входы множительных устройств 11, 12 и 13 и вычислителей кодов управления 5, 6 и 7. С выхода каждого из датчиков кода номера подрешетки 8, 9 и 10 код номера подрешетки поступает на второй вход множительного устройства 11, 12, 13 соответствующего вычислительного блока кодов управления элементами подрешеток 2, 3 и 4.

Вычислитель кодов управления 5, 6 и 7 вычисляет семь кодов управления согласно выражению φi=δφ·i, где

i=1, 2, … 7, т.е. 1δφ, 2δφ, 3δφ, 4δφ, 5δφ, 6δφ, и 7δφ.

Очевидно, что код 1δφ не требует вычисления, т.к. это входной код. Коды 2δφ и 4δφ получаются сдвигом входного кода соответственно на один и два разряда в сторону старших разрядов и могут быть выполнены не аппаратурно, а при монтаже, т.к. этот сдвиг постоянный. Вычисление кодов 3δφ и 5δφ выполняется при помощи сумматоров в соответствии с выражениями:

3δφ=1δφ+2δφ;

5δφ=1δφ+4δφ.

Код 6δφ получается сдвигом кода 3δφ на один разряд в сторону старших разрядов, а 7δφ вычисляется при помощи сумматоров согласно выражению 7δφ=1δφ+6δφ.

Как видно из примера, каждый из вычислителей кодов управления 5, 6 и 7 вычислил идентичные коды 1δφ, 2δφ … 7δφ, а для управления элементами строки (столбца) ФАР требуется вычислять коды 0,1δφ, 2δφ, … 7δφ, 8δφ, …,(j-1)δφ, где j - число элементов в строке (столбце) ФАР. Фазирование вычислительных блоков кодов управления элементами подрешеток 2, 3 и 4 между собой обеспечивается при помощи множительных устройств 11, 12 и 13 групп сумматоров 14, 15 и 16 и датчиков кодов номеров подрешеток 8, 9 и 10.

В качестве датчиков кода номера подрешетки 8, 9 и 10 могут использоваться соответствующим образом распаянные выводы ответных разъемов вычислительных блоков кодов управления элементами подрешеток, на которые заведены логические сигналы "0" и "1".

Множительные устройства 11, 12 и 13 вычисляют код фазирования согласно выражению

φф=8·n·δφ,

где 8 - число элементов в строке (столбце) подрешетки;

n=0, 1, 2 … - код номера подрешетки;

δφ - код дифФеренциального фазового сдвига между элементами строки (столбца) ФАР.

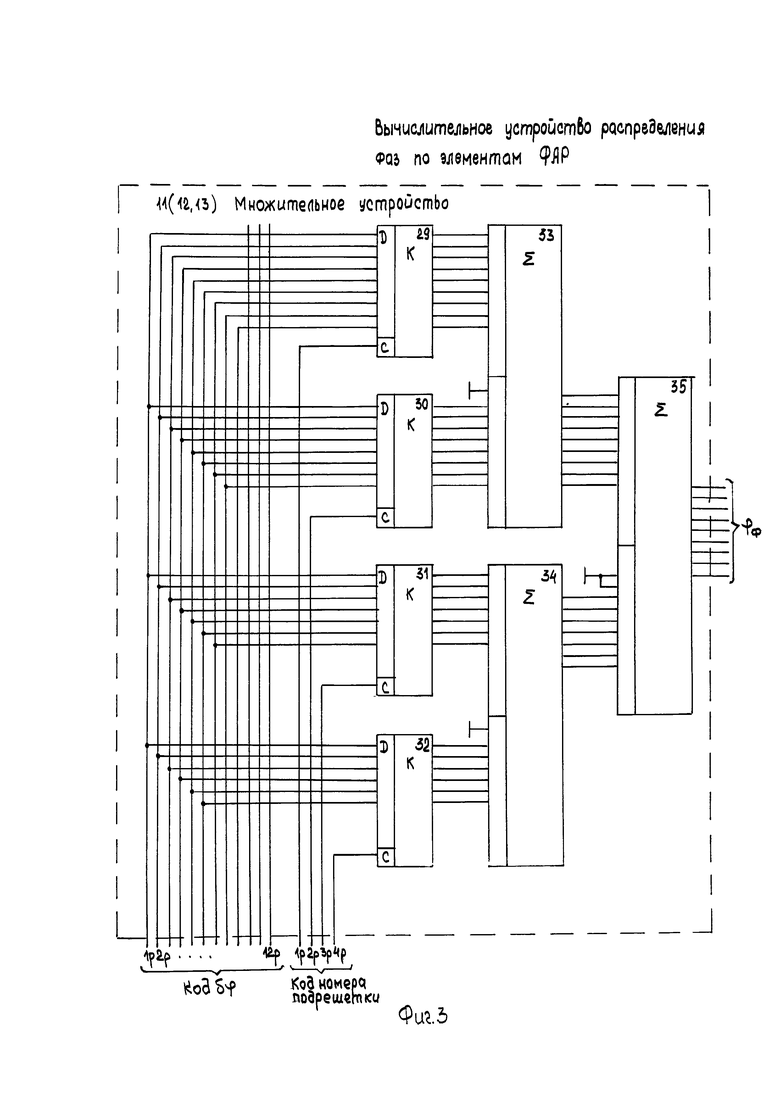

Выполнение операции умножения кода δφ на восемь осуществляется путем сдвига кода δφ на три разряда в сторону старших разрядов при монтаже, т.к. операция умножения на восемь выполняется в каждом из вычислительных блоков кодов управления элементами подрешеток 2, 3 и 4 в каждом цикле вычислений. Выполнение операции умножения кода 8δφ на код номера подрешетки n может выполняться множительным устройством любого типа, но для увеличения быстродействия выполнения этой операции лучше применять матричного типа, в котором результат получается за один такт.

Таким образом, множительные устройства вычисляют следующие коды 0δφ, 8δφ, 16δφ, 24δφ,…,(n-1)8δφ.

Эти коды являются кодами управления нулевыми элементами соответствующих подрешеток и кодами фазирования вычислительных блоков кодов управления элементами подрешеток 2, 3 и 4 между собой. Они с выходов множительных устройств поступают параллельно на первые входы сумматоров 17÷25 соответствующих групп сумматоров 14, 15 и 16, а на вторые входы этих сумматоров - соответствующие коды с выходов вычислителей кодов управления 5, 6 и 7, каждый из сумматоров 17÷25 выполняет операцию суммирования поступивших на его входы кодов.

В результате выполнения вычислений таким образом, как описано выше, на соответствующих выходах вычислительного блока кодов управления элементами подрешетки 2 будут получены следующие коды управления элементами ФАР: 0δφ, 1δφ, …, 7δφ, на соответствующих выходах вычислителя кодов управления элементами подрешетки 3 - коды: 8δφ, 9δφ, …,15δφ, на выходах n-го вычислительного блока кодов управления элементами подрешеток 4 - коды (n-1)8δφ, (n-1)9δφ, (n-1)10δφ,…,(n-1)15δφ.

Как видно из рассмотренного примера, вычислительное устройство распределения фаз по элементам ФАР обеспечивает расчет кодов управления элементами ФАР по одной из координат. Для расчета кодов управления элементами ФАР по второй координате требуется применение второго такого устройства с последующим суммированием кодов управления сумматорами, расположенными возле элементов ФАР.

Использование предлагаемого вычислительного устройства распределения фаз по элементам ФАР упрощает конструкцию и технологию изготовления последней в связи с унификацией вычислительных блоков кодов управления элементами подрешеток и уменьшением числа проводов в ФАР, повышает надежность ее работы по сравнению с той, которую имела бы при применении вычислительного устройства, описанного в статье Д.М. Зарезнова "Некоторые способы построения цифровых вычислительных устройств для управления лучом антенны типа "фазированная решетка" в РЛС" (Вопросы специальной радиоэлектроники, выпуск 21, 1968 г.) в 7÷8 раз.

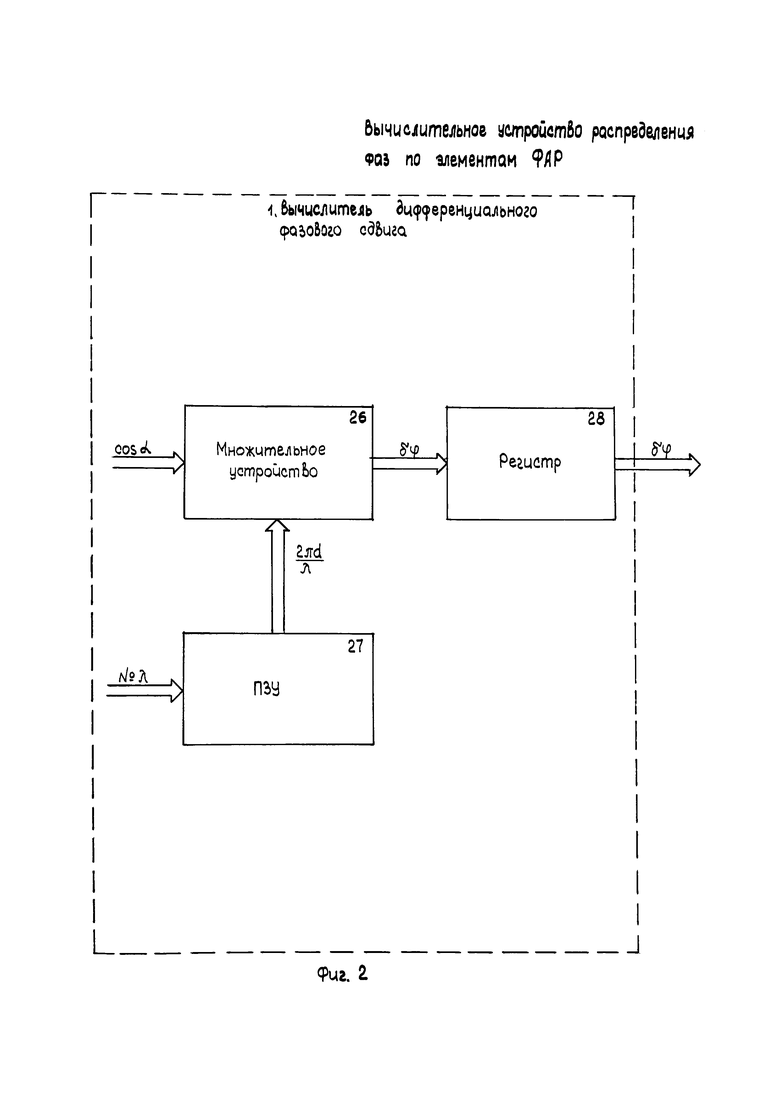

Вычислитель дифференциального фазового сдвига 1 производит вычисление кода δφ (пропорционального разнице фаз СВЧ-сигнала излучаемого или принимаемого соседними излучателями строки (столбца) элементов ФАР для отклонения луча от нормали к плоскости ФАР на угол α при работе ФАР на частоте с длиной волны λ и расстоянии между соседними излучателями d согласно выражению δφ= cosα.

cosα.

В качестве этого вычислителя может применяться вычислитель, содержащий множительное устройство, на один вход которого из постоянного запоминающего устройства поступает, в зависимости от рабочей частоты ФАР, код  , а на второй вход с ЦВМ целеуказаний поступает код cosα.

, а на второй вход с ЦВМ целеуказаний поступает код cosα.

Вычислители кодов управления 5, 6 и 7, например, для ФАР с подрешетками, содержащими восемь элементов по одной из координат, состоят из трех комбинационных сумматоров общеизвестного типа для вычисления кодов 3δφ, 5δφ, и 7δφ, а остальные коды получают монтажным сдвигом кода δφ или кода, полученного на выходах сумматоров. Принцип построения такого вычислителя описан в прототипе.

Множительное устройство 11, 12 и 13 может быть построено по любой из общеизвестных схем, например, блок умножения с аппаратным способом ускорения второго порядка (Самофалов К.Г. и др. Электронные цифровые вычислительные машины. К., Вища школа, 1976 г., стр. 315, 316).

Сумматоры 17÷25 являются комбинационными сумматорами общеизвестного типа, например на элементах 134 ИМ4.

Вычислительный блок кодов управления элементами подрешеток 2, 3 и 4 состоит из устройств (множительное устройство, вычислитель кодов управления и группа сумматоров), принцип построения которых описан выше, а конструктивно может быть выполнен на элементах серий 133, 134 в виде одной кассеты размером 130×140×15 мм3.

Согласно заявляемому изобретению на предприятии разработаны электрические схемы устройства, выполнено конструирование, изготовлены и проведены испытания опытной партии вычислительных блоков управления элементами подрешеток. Полученные результаты испытаний подтвердили правильность заложенных технических решений, упрощение конструкции и технологии изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841199A1 |

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841222A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ СХЕМЫ РАЗВЕДЕНИЯ ПЕЛЕНГАЦИОННЫХ ЛУЧЕЙ | 1989 |

|

SU1841118A1 |

| ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА С УПРАВЛЯЕМОЙ ШИРИНОЙ ДИАГРАММЫ НАПРАВЛЕННОСТИ | 2012 |

|

RU2507647C1 |

| Устройство управления ферритовыми фазовращателями модульной фазированной антенной решетки | 2018 |

|

RU2698957C1 |

| СПОСОБ ФОРМИРОВАНИЯ ПРИЕМНЫХ ПАРЦИАЛЬНЫХ ЛУЧЕЙ ДЛЯ ПАРАЛЛЕЛЬНОГО ОБЗОРА ПРОСТРАНСТВА | 2018 |

|

RU2701460C1 |

| Способ формирования остронаправленных сканирующих компенсационных диаграмм направленности в плоской фазированной антенной решетке с пространственным возбуждением | 2020 |

|

RU2755642C1 |

| Двухдиапазонная приемо-передающая активная фазированная антенная решетка | 2018 |

|

RU2688836C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА УСИЛЕНИЯ АКТИВНЫХ ФАР | 1989 |

|

SU1841122A1 |

| ПРИЕМО-ПЕРЕДАЮЩАЯ АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2014 |

|

RU2583336C1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных устройствах управления лучом ФАР. Технический результат - повышение точности устройства. Устройство содержит вычислитель дифференциального фазового сдвига, выходы которого подключены ко входам формирователей управляющих кодов, а также дополнительные формирователи управляющих кодов и блоки умножения, блоки сумматоров и шифраторы, выходы которых подключены к первым входам соответствующих блоков умножения, к вторым входам которых и входам дополнительных формирователей управляющих кодов подсоединены выходы вычислителя дифференциального фазового сдвига, выходы блоков умножения и формирователей управляющих кодов подключены ко входам соответствующих блоков сумматоров, выходы которых и выходы блоков умножения являются выходами устройства. 2 з.п. ф-лы, 4 ил.

1. Вычислительное устройство для управления лучом антенны, содержащее вычислитель дифференциального фазового сдвига, выходы которого подключены ко входам формирователей управляющих кодов, отличающееся тем, что, с целью повышения точности устройства, в него введены дополнительные формирователи управляющих кодов и блоки умножения, блоки сумматоров и шифраторы, выходы которых подключены к первым входам соответствующих блоков умножения, вторые входы которых соединены с выходами вычислителя дифференциального фазового сдвига и входами дополнительных формирователей управляющих кодов, выходы блоков умножения и формирователей управляющих кодов подключены ко входам соответствующих блоков сумматоров, выходы блоков сумматоров и блоков умножения являются выходами устройства.

2. Устройство по п. 1, отличающееся тем, что блок дифференциального фазового сдвига содержит последовательно соединенные узел постоянной памяти, узел умножения и регистр, выходы которого являются выходами блока.

3. Устройство по п. 1, отличающееся тем, что формирователь кодов управления содержит три сумматора, входы которых являются входами формирователя, при этом выходы первого сумматора подключены ко входам третьего сумматора и являются одними из выходов формирователя, другими выходами которого являются выходы второго и третьего сумматоров.

| Патент США № 3682532, кл | |||

| ДВУХМАССОВЫЙ ВИБРОЛОТОК | 0 |

|

SU364520A1 |

| "Вопросы специальной радиоэлектроники", вып | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

2016-09-20—Публикация

1981-05-25—Подача