Изобретение относится к области вычислительной техники и может быть использовано для управления лучом фазированной антенной решетки /ФАР/.

Вычислительные устройства для управления лучом современных ФАР обладают большой сложностью и дороговизной.

Построение больших ФАР на базе взаимозаменяемых модулей упрощает конструирование, изготовление, эксплуатацию, обслуживание и ремонт аппаратуры.

Известно вычислительное устройство /ВУ/, описанное в статье Д.М. Зарезнова "Некоторые способы построения цифровых вычислительных устройств для управления лучом антенны типа "фазированная решетка" в РЛС", Вопросы специальной радиоэлектроники, серия общетехническая, выпуск 21, 1968 г., обеспечивающее вычисление кодов управления элементами ФАР по каждой из координат /угол места, азимут/ путем логического суммирования кодов, полученных непосредственно из кода целеуказания.

ВУ содержит вычислитель кодов управления, подключенный своим входом к выходу регистра, а выходы указанного вычислителя являются выходами устройства по одной из координат. Для управления по двум координатам применяются два таких ВУ с последующим суммированием соответствующих кодов управления в сумматорах каждого из элементов ФАР, расположенных в узлах пересечения ортогональных строк и столбцов.

В известном ВУ вычисляются коды для управления элементами нечетных строк /столбцов/ путем суммирования кодов, получаемых из кода целеуказания. Так, для элементов первой строки код не вычисляется, а используется код целеуказания соответствующей разрядности. Для получения кода для элементов второй строки вычисления не требуется, а код получается путем монтажного сдвига кода целеуказания на один разряд в сторону старших разрядов, что эквивалентно умножению кода целеуказания на два. Аналогично получаются коды для элементов строк с номером 2n путем сдвига кода целеуказания на n разрядов в сторону старших разрядов. Код для элементов третьей, пятой и девятой строк получается путем суммирования кода для элементов первой строки соответственно с кодами для элементов второй, четвертой и восьмой строк. Для элементов шестой строки код получается путем монтажного сдвига на один разряд в сторону старших разрядов кода управления для элементов третьей строки, а для элементов седьмое строки - путем суммирования кодов управления для элементов первой и шестой строк.

При операциях сдвига и суммирования старшие разряды в полученных кодах управления отбрасываются, т.к. вес этих разрядов кратен фазе 360°. Аналогично вычисляются коды управления элементами остальных строк /столбцов/ ФАР.

Описанное ВУ имеет следующие недостатки. Устройство не может быть выполнено в виде взаимозаменяемых модулей без большого избытка аппаратуры, т.к. этот вычислитель не имеет повторяющейся структуры. Многие коды управления получаются из кодов управления другими элементами, что снижает надежность работы ФАР, т.к. ошибка в одном коде приводит к неверному управлению элементами одной строки /столбца/ или элементами нескольких строк /столбцов/ одновременно, что отклоняет луч от заданного направления. Существенно усложняет конструкцию больших ФАР и снижает технологичность их изготовления необходимость подводки кодов управления к элементам ФАР во взаимоперпендикулярных направлениях при двухкоординатном управлении.

Наиболее близким по технической сущности является вычислительный модуль ВУ для управления лучом антенны, описанный в авт. свид. № 1841181 по заявке №3019172 от 25 мая 1981 года /прототип/.

Вычислительный модуль содержит шифратор, формирователь управляющих кодов, блоки сумматоров и блок умножения, первые входы которого подключены к выходам шифратора, а вторые входы - ко входам формирователя управляющих кодов, выходы блока умножения и формирователя управляющих кодов подключены ко входам соответствующих блоков сумматоров, выходы блоков сумматоров и блоков умножения являются выходами устройства.

Вычислительный модуль обеспечивает независимое вычисление кодов управления элементами одной подрешетки ФАР по одной из координат /угол места, азимут/.

Код дифференциального фазового сдвига /код целеуказания/ поступает параллельно на первые входы блока умножения и на входы формирователя управляющих кодов. На вторые входы блока умножения с выхода шифратора поступает код номера подрешетки. Коды, получаемые на выходах формирователя управляющих кодов, вычисляются аналогично кодам управления ВУ. Коды с выходов формирователя управляющих кодов поступают на первые входы соответствующих блоков сумматоров, на вторые входы которых поступает код с выходов блока умножения. Коды на выходах блока умножения и блоков сумматоров являются кодами управления элементами подрешетки ФАР по одной координате. Аналогично вычисляются коды управления по другой координате.

Недостатком описанного вычислительного модуля является большой объем аппаратуры. Так, в вычислительном модуле, выполненном на микросхемах серий 133 или 134, управляющем подрешеткой с восьмью элементами в строке /столбце/ при 12-разрядном коде дифференциального фазового сдвига, только для выполнения формирователя управляющих кодов и блоков сумматоров требуется применение 30 штук микросхем 133 ИМ3 или 134 ИМ4.

Целью настоящего изобретения является сокращение объема аппаратуры вычислительного модуля.

Поставленная цель достигается тем, что в вычислительном модуле, содержащем регистр, блок умножения, шифратор и /2n-1/ сумматоров, где n - целое число, равное или большее числа два, первые входы первого и второго сумматоров подключены к выходам блока умножения, первые входы которого подключены к выходам шифратора, а вторые - к выходам регистра и вторым входам первого и второго сумматоров, входы регистра являются входами, а выходы блока умножения и каждого из сумматоров - выходами устройства, введены следующие связи, первые входы третьего и всех следующих по номеру сумматоров подключены к выходам регистра, а вторые входы сумматора с номером i подключены к выходам сумматора с номером j=i-2(m-1) так, чтобы выполнялось условие i≤2m, где m - целое число, а 2m должно быть ближайшим большим или равным числу i.

Такое выполнение вычислительного модуля позволяет, по сравнению с устройством /прототипом/, сократить аппаратурные затраты за счет параллельно-последовательного вычисления кодов управления, что позволило исключить из структурной схемы устройства /прототипа/ формирователь управляющих кодов.

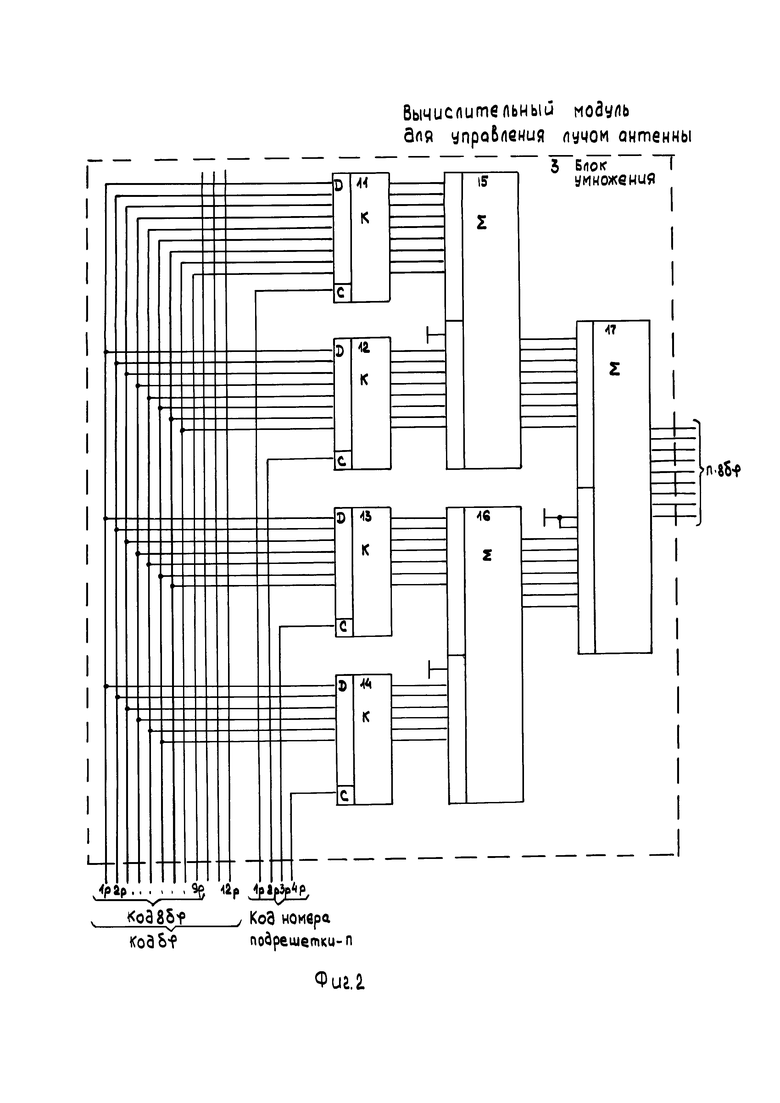

На фиг.1 представлена структурная схема вычислительного модуля; на фиг.2 - схема блока умножения.

Предлагаемый вычислительный модуль /фиг.1/ содержит регистр 1, шифратор 2, блок умножения 3 и сумматоры 4-10.

Выходы блока умножения 3 подключены к первым входам сумматоров 4 и 5, выходы которых подключены соответственно к первым входам сумматоров 6, 8 и 7, 9. Первые входы сумматора 10 с номером i должны быть подключены к выходам сумматора с номером j=i-2(m-1) так, чтобы выполнялось условие i≤2m, где m - целое число, а 2m должно быть ближайшим большим или равным числу i. Выходы шифратора 2 подключены к первым входам блока умножения 3, вторые входы которого подключены к выходам регистра 1 и ко вторым входам сумматоров 4-10. Входы регистра 1 являются входами, а выходы блока умножения 3 и сумматоров 4-10 - выходами устройства.

Блок умножения 3, представленный на фиг.2, содержит коммутаторы 11-14 и сумматоры 15-17.

Первые и вторые входы сумматора 17 подключены соответственно к выходам сумматоров 15 и 16. Первые и вторые входы сумматора 15 подключены соответственно к выходам коммутаторов 11 и 12, а первые и вторые входы сумматора 16 - к выходам коммутаторов 13 и 14. Управляющие входы коммутаторов 11-14 являются первыми входами, а информационные входы, соединенные между собой, - вторыми входами блока умножения 3. Выходы сумматора 17 являются выходами блока умножения 3.

Блоки, входящие в вычислительный модуль, могут быть выполнены на микросхемах серий 133 или 134.

Регистр 1 конструктивно может быть выполнен на микросхемах 133ИР1 или 134ИР1.

В качестве шифратора 2 могут использоваться соответствующим образом распаянные выводы ответного разъема вычислительного модуля, на которые подаются сигналы логического нуля и единицы, которые являются разрядами кода номера подрешетки.

Коммутаторы 11-14 могут быть выполнены на элементах 2И /133ЛИ1/, на первый вход /Д/ каждого из которых подаются соответствующие разряды одного кода, а на вторые входы /С/, объединенные между собой, - разряд другого кода.

Сумматоры 4-10 и 15-17 могут быть выполнены на микросхемах 133ИМ3 или 134ИМ4.

Рассмотрим работу вычислительного модуля на примере вычисления кодов управления элементами подрешетки, содержащей восемь /к равно 8/ строк /столбцов/.

Код дифференциального фазового сдвига δφ на время вычисления кодов управления запоминается в регистре 1.

На первые входы блока умножения 3 с выходов шифратора 2 поступает код номера подрешетки n по соответствующей координате ФАР, который может принимать значения от 0 до N-1, где N - количество подрешеток в ФАР по рассматриваемой координате управления.

С выходов регистра 1 на вторые входы блока умножения 3 поступает код кδφ, равный 8δφ. Для образования кода 8δφ используется код δφ без трех старших разрядов, веса которых после умножения кода δφ на восемь /23/ стали кратными 360° фазы СВЧ-сигнала и поэтому могут не использоваться, и старшим разрядом кода 8δφ стал 9-й разряд 12-разрядного кода δφ.

На фиг.2 представлена схема блока умножения 3, который работает следующим образом.

Из кода 8δφ образуются коды 16δφ, 32δφ и 64δφ, соответственно без одного, двух и трех старших разрядов кода 8δφ.

Коды 8δφ, 16δφ, 32δφ и 64δφ поступают соответственно на Д-входы коммутаторов 11, 12, 13 и 14. На С-вход коммутатора 11 поступает первый /младший/ разряд кода номера подрешетки, а на С-входы коммутаторов 12, 13 и 14 поступают соответственно 2-й, 3-й и 4-й разряды кода номера подрешетки.

При единичном значении разряда кода номера подрешетки поступивший код на Д-вход соответствующего коммутатора передается на его выход, а при нулевом - на выходе соответствующего коммутатора устанавливается нулевое значение кода.

Коды с выходов коммутаторов 11 и 12 поступают на соответствующие входы сумматора 15, а коды с выходов коммутаторов 13 и 14 - на соответствующие входы сумматора 16.

Коды, полученные на выходах сумматоров 15 и 16, поступают на входы сумматора 17. В сумматорах 15, 16 и 17 разряды кодов с одинаковыми весами суммируются между собой, а в случае "недостачи" младших разрядов одного из кодов на соответствующие входы сумматоров подаются сигналы логического нуля.

Код n·8δφ, полученный на выходе сумматора 17, является кодом управления элементами первой строки /столбца/ n-й подрешетки ФАР.

Например, в вычислительных модулях, подключенных в местах расположения подрешеток ФАР с их номерами 0, 1, 2, …, 15, блоками умножения 3 вычисляются соответственно коды управления 0δφ, 8δφ, 16δφ, …, 120δφ.

Вычисление кодов управления элементами остальных строк /столбцов/ каждой из подрешеток ФАР производится сумматорами 4-10.

На первые входы сумматоров 4 и 5 поступает код n·8δφ, а на вторые входы - соответственно коды δφ и 2δφ. Код 2δφ получен путем монтажного сдвига кода δφ на один разряд в сторону старших разрядов. Сумматорами 4 и 5 вычисляются коды управления элементами второй и третьей строки /столбца/, соответственно /n·8+1/δφ и /n·8+2/δφ. Код /n·8+1/δφ с выходов сумматора 4 поступает на первые входы сумматоров 6 и 8, на вторые входы которых поступают соответственно коды 2δφ и 4δφ, полученные путем монтажного сдвига. Код /n·8+2/δφ с выходов сумматора 5 поступает на первые входы сумматоров 7 и 9, на вторые входы которых поступают соответственно коды 2δφ и 4δφ. Сумматорами 6-9 вычисляются коды управления элементами четвертой, пятой, шестой и седьмой строк, соответственно /n·8+3/δφ, /n·8+4/δφ, /n·8+5/δφ и /n·8+6/δφ. Код /n·8+3/δφ с выходов сумматора 6 должен поступать на первые входы сумматора 10, на вторые входы которого должен поступать код 4δφ. Сумматором 10 вычисляются коды управления элементами восьмой строки /столбца/ в соответствии с выражением /n·8+7/δφ.

Например, в вычислительных модулях, вычисляющих коды управления для подрешеток ФАР с порядковыми номерами 0, 1, 2, … 15, сумматорами 4-10 вычисляются соответственно коды управления: 1-я подрешетка /n=0/ - δφ, 2δφ, 3δφ, 4δφ, 5δφ, 6δφ, 7δφ; 2-я подрешетка /n=1/ - 9δφ, 10δφ, 11δφ, 12δφ, 13δφ, 14δφ, 15δφ; 3-я подрешетка /n=2/ - 17δφ, 18δφ, 19δφ, 20δφ, 21δφ, 22δφ, 23δφ, …; 16-я подрешетка /n=15/ - 121δφ, 122δφ, 123δφ, 124δφ, 125δφ, 126δφ, 127δφ.

Из структурной схемы /фиг.1/ видно, что возможны другие варианты выполнения вычислительного модуля, заключающиеся в изменении количества выходов устройства к. Сокращение объема аппаратуры вычислительного модуля по сравнению с прототипом достигается при к, равном или больше числа четыре.

Наиболее целесообразно количество выходов вычислительного модуля K выбирать равным целой степени числа два, т.е. 4, 8, 16 и т.д., что позволяет формировать на входе блока умножения коды, кратные коду к, путем монтажного сдвига.

Применение предлагаемого вычислительного модуля по сравнению с базовым объектом, который является прототипом, позволяет сократить объем аппаратуры. Для описанного устройства, выполненного на элементах 133 или 134 серий, уменьшение объема аппаратуры составляет примерно 20% в пределах одной подрешетки, что при 12-разрядном коде дифференциального фазового сдвига позволяет экономить 18 микросхем 133ИМ3 или 134ИМ4. Сокращение объема аппаратуры вычислительного модуля позволяет уменьшить стоимость и массогабаритные характеристики, упростить конструкцию и повысить технологичность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841222A1 |

| Вычислительное устройство для управления лучом антенны | 1981 |

|

SU1841181A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1988 |

|

SU1580393A1 |

| Антенная система с фазовым управлением | 1988 |

|

SU1597987A1 |

Изобретение относится к области вычислительной техники и может быть использовано для управления лучом фазированной антенной решетки (ФАР). Технический результат - упрощение устройства. Вычислитель положения луча ФАР содержит регистр, вход которого является первым входом вычислителя, а выход подключен к первому входу умножителя и первым входам первого и второго сумматоров группы, вторые входы которых соединены с выходом умножителя, второй вход умножителя подключен к выходу шифратора, вход которого является вторым входом вычислителя, а выходы умножителя и сумматоров группы являются выходами вычислителя, при этом первые входы сумматоров группы, начиная с третьего, подключены к выходу регистра, а второй вход каждого сумматора, начиная с третьего, соединен с выходом соответствующих сумматоров. 2 ил.

Вычислитель положения луча фазированной антенной решетки, содержащий регистр, вход которого является первым входом вычислителя, а выход подключен к первому входу умножителя и первым входам первого и второго сумматоров группы, вторые входы которых соединены с выходом умножителя, второй вход умножителя подключен к выходу шифратора, вход которого является вторым входом вычислителя, а выходы умножителя и сумматоров группы являются выходами вычислителя, отличающийся тем, что, с целью упрощения устройства, первые входы сумматоров группы, начиная с третьего, подключены к выходу регистра, а второй вход каждого сумматора, начиная с третьего, соединен с выходом соответствующих сумматоров.

| Зарезнов Д.М | |||

| "Некоторые способы построения цифровых вычислительных устройств для управления лучом антенны типа "фазированная решетка" в РЛС", "Вопросы специальной радиоэлектроники", сер | |||

| общетехническая, вып | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Вычислительное устройство для управления лучом антенны | 1981 |

|

SU1841181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2016-10-10—Публикация

1982-06-28—Подача