Изобретение относится к области вычислительной техники и может быть использовано для управления лучом фазированной антенной решетки /ФАР/ с гексагональной структурой расположения элементов /излучателей/.

ФАР с гексагональной структурой расположения элементов обладает преимуществами, по сравнению с ФАР с прямоугольной структурой расположения элементов /см. "Антенны" /Современное состояние и проблемы/, под ред. чл.-кор. АН СССР Л.Д. Бахраха и проф. Д.И. Воскресенского; "Советское радио", 1979 г., стр. 43-47/, заключающимися в увеличении расстояния между излучателями и уменьшении их общего количества. Однако при этом усложняется аппаратурная реализация вычислительного устройства для управления лучом антенны.

При создании ФАР одной из основных задач является упрощение конструкции, снижение трудоемкости их изготовления, обслуживания и ремонта. Решение этой задачи существенно упрощается при построении ФАР на базе взаимозаменяемых модулей. Данное изобретение направлено на создание одного из таких модулей - вычислительного модуля управления лучом антенны.

Известно вычислительное устройство /ВУ/, описанное в статье Д.М. Зарезнова "Некоторые способы построения цифровых вычислительных устройств для управления лучом антенны типа "фазированная решетка" в РЛС", Вопросы специальной радиоэлектроники, серия общетехническая; выпуск 21, 1968 г., обеспечивающее вычисление кодов управления элементами ФАР по каждой из координат /угол места, азимут/ путем логического суммирования кодов, полученных непосредственно из кода целеуказания. ВУ содержит вычислитель кодов управления, подключенный своим входом к выходу регистра, а соответствующие выходы которого являются выходами устройства по одной из координат. При управлении по двум координатам применяются два таких ВУ с последующим суммированием соответствующих кодов в сумматорах, расположенных в узлах пересечения ортогональных строк и столбцов, каждого из элементов ФАР.

Б вычислителе кодов управления вычисляются коды для управления элементами нечетных строк /столбцов/ путем суммирования кодов, получаемых из кода целеуказания. Так, для элементов первой строки код не вычисляется, а используется код целеуказания соответствующей разрядности. Для получения кода для элементов второй строки вычисление не требуется, а код получается путем монтажного сдвига кода целеуказания на один разряд в сторону старших разрядов, что эквивалентно умножению на два. Аналогично получаются коды для элементов строк с номером 2n путем сдвига кода целеуказания на n разрядов в сторону старших разрядов.

Код для элементов третьей, пятой и девятой строк получается путем суммирования кода для элементов первой строки соответственно с кодами для элементов второй, четвертой и восьмой строк. Для элементов шестой строки код получается путем сдвига кода для элементов третьей строки на один разряд в сторону старших разрядов, а для элементов седьмой строки - путем суммирования кодов для элементов первой и шестой строк. Аналогично вычисляются коды управления остальными элементами строк /столбцов/ ФАР.

Так как в кодах δφ /целеуказаний/ вес старшего разряда кратен 180° фазы СВЧ сигнала, то появляющиеся в процессе выполнения операции сдвига или суммирования более старшие разряды, как кратные 360° фазы /или 0°/ СВЧ сигнала, в последующих вычислениях могут не учитываться.

Описанное ВУ не может быть выполнено в виде взаимозаменяемых модулей без большого избытка аппаратуры, т.к. этот вычислитель не имеет повторяющейся структуры.

Наиболее близким по технической сущности является вычислительный модуль, описанный в авт. свид. № 1841199, заявка 3045162, от 28.06.82 г.

Вычислительный модуль содержит регистр, блок умножения, шифратор и 2n-1 сумматоров, где n - целое число большее единицы. Первые входы блока умножения подключены к выходам шифратора, а вторые - к выходам регистра и ко вторым входам каждого из сумматоров, первые входы третьего и всех последующих сумматоров с номером i подключены к выходам сумматора с номером j=i-2(m-1) так, чтобы выполнялось условие i≤2m, где m - целое число, а 2m должно быть ближайшим большим или равным числу i, входы регистра являются входами, а выходы блока умножения и каждого из сумматоров - выходами устройства.

В вычислительном модуле код дифференциального фазового сдвига δφ /целеуказания/ на время вычисления кодов управления запоминается в регистре. На первые входы блока умножения поступает код κ·δφ, где κ - количество выходов в вычислительном модуле, равное числу два в целой степени, а на вторые входы - код номера подрешетки n /номер вычислительного модуля в столбце /строке/ вычислительных модулей ФАР/.

На вторые входы 2n-1 сумматоров поступают коды: на первый сумматор - δφ, на второй, третий, четвертый - 2δφ, на пятый, шестой, седьмой и восьмой - 4δφ и т.д.

На выходах вычислительного модуля получаются коды соответственно n·κδφ, (n·κ+1)δφ, (n·κ+2)δφ, …, [n·κ+(κ-1)]δφ.

Нижеупомянутые 2n-1 сумматоров и связи между ними будем называть формирователем кодов управления, на первый вход которого поступает код n·κδφ, на второй - δφ, на третий - 2δφ.

При необходимости управления лучом ФАР по двум координатам требуется применение в каждой подрешетке еще одного такого вычислительного модуля, вычисляющего коды управления элементами подрешетки по второй координате.

На входы вычислительных модулей поступают соответствующие коды дифференциальных фазовых сдвигов между соседними элементами столбцов и строк ФАР.

Коды, вычисленные каждым из вычислительных модулей, поступают, соответственно, на входы сумматоров, расположенных в узлах пересечения строк и столбцов элементов подрешеток ФАР в цепях управления фазовращателями.

В зависимости от расположения излучателей в ФАР, в прямоугольной или гексагональной сети, сумматоры, суммирующие коды управления для элементов подрешетки при двухкоординатном управлении лучом и связи между ними будем называть соответственно прямоугольной или гексагональной суммирующей матрицей.

При сопоставлении прямоугольной с гексагональной суммирующей матрицей видно, что при одинаковом числе элементов подрешетки гексагональная суммирующая матрица имеет по одной из координат в два раза большее число входов. Это обстоятельство вызывает необходимость вычисления вычислительным модулем этой координаты удвоенного числа кодов управления, а значит - существенного увеличения аппаратурных затрат за счет увеличения числа сумматоров в формирователе кодов управления.

Целью настоящего изобретения является сокращение аппаратурных затрат в вычислительном модуле при управлении лучом в ФАР с гексагональной сетью расположения излучателей.

Поставленная цель достигается тем, что в вычислительном модуле, содержащем первый и второй регистры, первый и второй шифраторы, первый и второй блоки умножения, первый и второй формирователь кодов управления и суммирующую матрицу с гексагональной структурой расположения сумматоров /ниже суммирующая матрица/, в которой первые входы сумматоров каждой из строк соединены между собой и являются строчными входами суммирующей матрицы, а вторые входы сумматоров каждого из столбцов соединены между собой и являются столбцовыми входами этой матрицы, выходы первого блока умножения и первого формирователя кодов управления подключены соответственно к строчным нечетным входам суммирующей матрицы, выходы второго блока умножения и второго формирователя кодов управления подключены соответственно к столбцовым входам суммирующей матрицы, первые входы первого и второго формирователей кодов управления подключены соответственно к выходам первого и второго блоков умножения, выходы первого регистра подключены ко вторым и третьим входам первого формирователя кодов управления и к первым входам первого блока умножения, вторые входы которого подключены к выходам первого шифратора, выходы второго регистра подключены к третьим входам второго формирователя кодов управления и к первым входам второго блока умножения, вторые входы которого подключены к выходам второго шифратора, входы первого и второго регистров являются входами, а выходы сумматоров суммирующей матрицы - выходами устройства, - введен сумматор, выходы которого подключены ко вторым входам второго формирователя кодов управления, а первые и вторые входы - соответственно к выходам первого и второго регистров, строчные нечетные и последующие четные входы суммирующей матрицы попарно соединены между собой.

Сущность изобретения заключается в следующем. Первым блоком умножения и первым формирователем кодов управления вычисляются коды управления только для нечетных строк /строчных входов суммирующей матрицы/, а подаются эти коды на объединенные строчные входы нечетных с последующими четными входами этой матрицы. Однако коды управления для четных строчных входов суммирующей матрицы должны отличаться от предшествующих нечетных на 0,5δφy /половину величины кода дифференциального фазового сдвига между соседними элементами в столбце излучателей ФАР/. Учитывая, что сумматоры четных строк в суммирующей матрице одновременно принадлежат четным столбцам, код 0,5δφy с помощью введенного сумматора суммируется с кодом δφx и в составе кодов управления четными столбцами, вычисленными вторым формирователем кодов управления, поступает на сумматоры четных столбцов, а это равнозначно подаче кода 0,5δφy в сумматоры четных строк.

Таким образом, попарное объединение строчных входов суммирующей матрицы и введение дополнительного сумматора позволяет сократить вдвое число вычисляемых кодов управления строками, а значит, существенно уменьшить объем аппаратуры и число связей в вычислительном модуле.

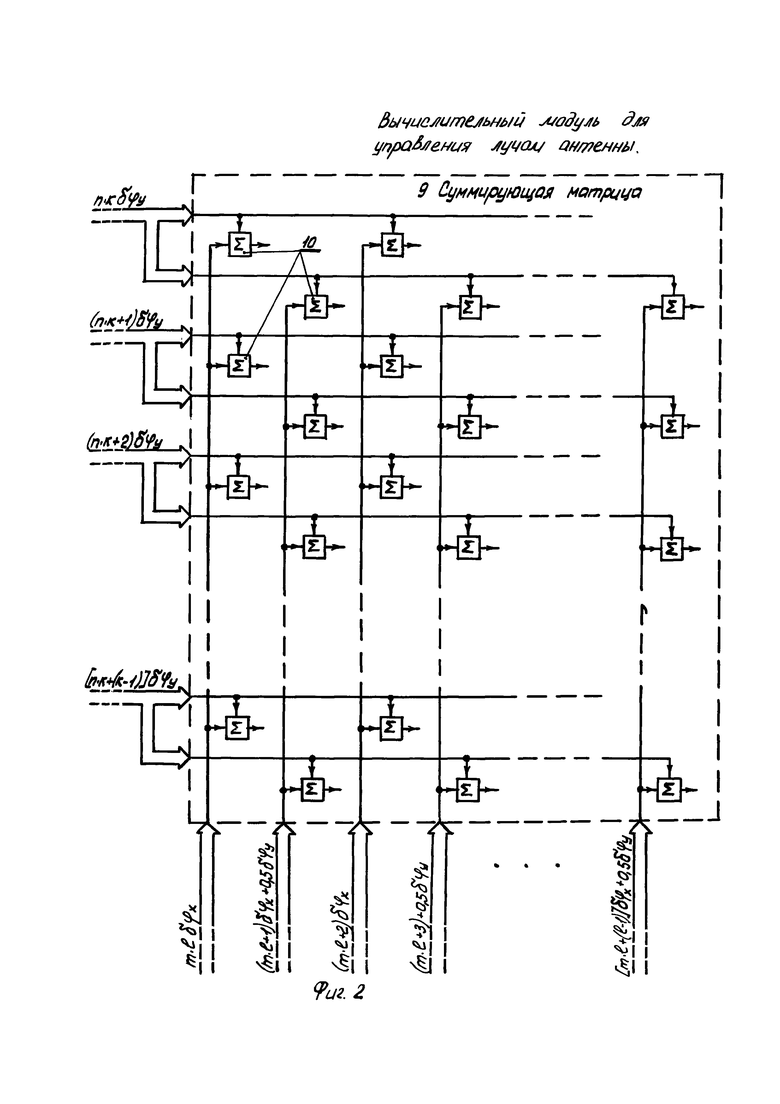

На фиг. 1, 2 представлена структурная схема вычислительного модуля для управления лучом антенны; на фиг. 3 - схема блока умножения, на фиг. 4 - схема формирователя кодов управления.

Предлагаемый вычислительный модуль /фиг. 1, 2/ содержит регистры 1 и 2, шифраторы 3 и 4, блоки умножения 5 и 6, формирователи кодов управления 7 и 8, суммирующую матрицу 9 с сумматорами 10 и сумматор 11.

В суммирующей матрице 9 /фиг. 2/ первые входы сумматоров 10 каждой из строк сумматоров соединены между собой и являются строчными входами суммирующей матрицы 9, а вторые входы сумматоров 10 каждого из столбцов соединены между собой и являются столбцовыми входами суммирующей матрицы 9.

Выходы блока умножения 5 и формирователя кодов управления 7 подключены соответственно к строчным нечетным и последующим четным входам суммирующей матрицы 9. Выходы блока умножения 6 и формирователя кодов управления 8 подключены соответственно к столбцовым входам суммирующей матрицы 9.

Выходы блоков умножения 5 и 6 подключены соответственно к первым входам формирователей кодов управления 7 и 8. Выходы регистра 1 подключены ко вторым и третьим входам формирователя кодов управления 7, к первым входам сумматора 11 и к первым входам блока умножения 5, вторые входы которого подключены к выходам шифратора 3. Выходы регистра 2 подключены к третьим входам формирователя кодов управления 8, ко вторым входам сумматора 11 и к первым входам блока умножения 6, вторые входы которого подключены к выходам шифратора 4. Выходы сумматора 11 подключены ко вторым входам формирователя кодов управления 8. Входы регистров 1 и 2 являются входами, а выходы сумматоров 10 в суммирующей матрице 9 - выходами устройства.

Блок умножения 5 /6/ /фиг. 3/ содержит коммутаторы 12-15 и сумматоры 16-18. Первые и вторые входы сумматора 18 подключены соответственно к выходам сумматоров 16 и 17. Первые и вторые входы сумматора 16 подключены соответственно к выходам коммутаторов 12 и 13, а первые и вторые входы сумматора 17 - к выходам коммутаторов 14 и 15. Управляющие входы коммутаторов 12-15 являются первыми входами, а информационные входы, соединенные между собой, - вторыми входами блока умножения 5 /6/. Выходы сумматора 18 являются выходами блока умножения 5 /6/.

В предлагаемом устройстве формирователи кодов управления 7 и 8 /фиг. 1/ выполняются на базе комбинационных сумматоров. При применении суммирующей матрицы 9 с разным числом сумматоров 10 и различным их взаимным соединением /прямоугольная или гексагональная сеть/ требуются соответственно формирователи кодов управления 7 и 8 с разным числом сумматоров и соответствующим числом выходов.

Так, в вычислительном модуле с суммирующей матрицей 9 /фиг. 2/ и с сумматорами 10, расположенными в восемь строчек и четыре столбца, формирователи кодов управления 7 /8/ /фиг. 4/ содержат сумматоры 19-21. Выходы сумматора 19 подключены к первым входам сумматора 21. Первые входы сумматоров 19 и 20 соединены между собой и являются первыми входами формирователя кодов управления 7 /8/. Вторые входы сумматора 19 являются вторыми входами, а вторые входы сумматоров 20 и 21, соединенные между собой, - третьими входами формирователя. Выходы сумматоров 19, 20 и 21 являются выходами формирователей кодов управления 7 и 8.

Блоки, входящие в вычислительный модуль, могут быть выполнены на соответствующих серийно выпускаемых микросхемах, например, серий 133 или 134. Регистры 1 и 2 могут быть выполнены на микросхемах 133 ИР1 или 134 ИР1.

В качестве шифраторов 3 и 4 могут использоваться соответствующим образом распаянные выводы ответного разъема вычислительного модуля, на который подаются сигналы логического нуля и единицы.

Коммутаторы 12-15 могут быть выполнены на элементах 2И (133ЛИ1), на первый вход /Д/ каждого из которых подаются соответствующие разряды одного кода, а на вторые входы /С/, объединенные между собой - разряд второго кода.

Сумматоры 10, 11, 16-21 могут быть выполнены на микросхемах 133ИМ3 или 134ИМ4.

Рассмотрим работу вычислительного модуля /фиг. 1, 2/ на примере вычисления кодов управления излучателями подрешетки с 16 излучателями с гексагональной сетью размещения в восьми строках и четырех столбцах.

Код дифференциального фазового сдвига между соседними элементами в столбце δφy /управление по углу места/ запоминается в регистре 1, с выходов которого поступает на первые входы блока умножения 5. С выходов шифратора 3 на вторые входы блока умножения 5 поступает код номера подрешетки n, который может принимать значения от 0 до N-1 где N - максимальное количество подрешеток в вертикальных рядах подрешеток в ФАР.

В блоке умножения 5 /фиг. 3/ на информационные Д-входы коммутаторов 12, 13, 14 и 15 поступают соответственно коды 4δφy, 8δφy, 16δφy, 32δφy, полученные путем монтажного сдвига кода δφy соответственно на два, три, четыре и пять разрядов в сторону старших разрядов. На С-вход коммутатора 12 поступает 1-й /младший/ разряд кода номера подрешетки - n, а на С-входы коммутаторов 13, 14 и 15 соответственно 2-й, 3-й и 4-й разряды кода номера подрешетки n.

При единичном значении разряда кода номера подрешетки поступивший код на Д-вход соответствующего коммутатора передается на его выход, а при нулевом - на выходе соответствующего коммутатора устанавливается нулевое значение кода.

Коды с выходов коммутаторов 12 и 13 поступают на соответствующие входы сумматора 14, а коды с выходов коммутаторов 14 и 15 - на соответствующие входы сумматора 17. Коды, полученные на выходах сумматоров 16 и 17, поступают на входы сумматора 18.

В сумматорах 16, 17 и 18 разряды кодов с одинаковыми весами суммируются между собой, а в случае "недостачи" младших разрядов одного из кодов на соответствующие входы сумматоров подаются сигналы логического нуля.

Код n·4δφy, полученный на выходе сумматора 18, является выходным кодом блока умножения 5.

На первые входы формирователя кодов управления 7 (фиг. 1) подступает код n·4δφy, на вторые входы - код δφy, а на третьи входы - 2δφy. В результате выполнения операции суммирования этих кодов в сумматорах 19-21 (фиг. 4) на их выходах соответственно будут значения кодов (n·4+1)δφy, (n·4+2)δφy, (n·4+3)δφy.

Вычисленные соответствующие значения кодов управления поступают попарно на нечетные и последующие четные строки сумматоров 10 суммирующей матрицы 9 (фиг. 2).

Код дифференциального фазового сдвига δφx (управление по азимуту) запоминается в регистре 2, с выходов которого поступает на первые входы блока умножения 6. С выходов шифратора 4 на вторые входы блока умножения 6 поступает код номера подрешетки m, который может принимать значения от 0 до М-1, где М - максимальное количество подрешеток в горизонтальных рядах подрешеток в ФАР.

Блоком умножения 6 вычисляется код m·lδφx, где l - количество кодов управления столбцами суммирующей матрицы 9 (в нашем примере l=4). С выхода блока умножения 6 (фиг. 3) код поступает на первые входы формирователя кодов управления 8 (фиг. 1). На второй вход формирователя кодов управления 8 поступает код с выхода сумматора 11. На первый вход сумматора 11 поступает код 0,5δφy с выхода регистра 1, а на второй вход этого сумматора - код δφx.

На третьи входы формирователя кодов управления 8 поступает код 2δφx с выходов регистра 2.

В соответствии со схемой (фиг. 4) сумматорами 18, 19 и 20 вычисляются соответственно коды управления (m·4+1)δφx+0,5δφy; (m·4+2)δφx и (m·4+3)δφx+0,5δφy.

Вычисленные коды управления с выходов блока умножения 6 и формирователя кодов управления 8 (фиг. 1) поступают на столбцовые входы суммирующей матрицы 9 (фиг. 2), в которой они поступают на вторые входы сумматоров 10.

Сумматорами 10 вычисляются коды управления фазовращателями, находящимися в цепях управления излучателями ФАР.

Коды дифференциальных фазовых сдвигов δφy и δφx могут быть вычислены с помощью ЦВМ или вычислителя дифференциальных фазовых сдвигов (на фиг. 1 условно не показана) согласно выражениям:

;

;

,

,

где dx - расстояние между соседними столбцами элементов ФАР;

dy - расстояние между соседними элементами в столбце ФАР;

λ - длина волны СВЧ сигнала;

Cosαx, Cosαy - косинусы угла между направлением максимума диаграммы направленности ФАР и плоскостью ФАР соответственно в горизонтальной и вертикальной плоскостях.

Применение предлагаемого вычислительного модуля для управления лучом ФАР с гексагональной сетью расположения элементов позволяет сократить по сравнению с базовым объектом, являющимся прототипом, в два раза число вычисляемых кодов управления, существенное уменьшение числа связей и примерно на 10% число элементов (микросхемы 133ИМ3 или 134ИМ4).

Согласно заявляемому изобретению, на предприятии и в рамках объявленного конкурса по снижению массо-габаритных характеристик ФАР, были разработаны схемы устройства.

Конструктивно вычислительный модуль в ФАР с подрешетками на 64 элемента состоит из 4 кассет одного типа с размерами 130×140 мм2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841199A1 |

| Вычислительное устройство для управления лучом антенны | 1981 |

|

SU1841181A1 |

| Устройство для умножения | 1988 |

|

SU1571574A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Устройство управления ферритовыми фазовращателями модульной фазированной антенной решетки | 2018 |

|

RU2698957C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для моделирования сетевых графов | 1982 |

|

SU1065858A1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных схем | 1980 |

|

SU980084A1 |

| Устройство поиска экстремального пути в графе | 1986 |

|

SU1341647A1 |

Изобретение относится к области вычислительной техники. Технический результат - упрощение вычислителя. Устройство содержит сумматор, первый регистр, выход которого соединен с входами формирователя кодов строк и первого умножителя, через который выход первого шифратора соединен с входом формирователя кодов строк, матрицу сумматоров, второй регистр, выход которого соединен с входами формирователя кодов столбцов и второго умножителя, через который выход второго шифратора соединен с входом формирователя кодов столбцов, выходы формирователя кодов строк и первого умножителя соединены с входами сумматоров соответствующих нечетных строк матрицы сумматоров, выходы второго умножителя и формирователя кодов столбцов соединены с входами сумматоров, соответствующих столбцов матрицы сумматоров, при этом выходы первого и второго регистров через сумматор соединены с входом формирователя кодов столбцов, а выходы сумматоров нечетных строк матрицы сумматоров объединены с входами сумматоров последующих строк матрицы сумматоров последующих четных строк матрицы сумматоров. 4 ил.

Вычислитель положения луча фазированной антенной решетки, содержащий первый регистр, выход которого соединен с входами формирователя кодов строк и первого умножителя, через который выход первого шифратора соединен с входом формирователя кодов строк, матрицу сумматоров, второй регистр, выход которого соединен с входами формирователя кодов столбцов и второго умножителя, через который выход второго шифратора соединен с входом формирователя кодов столбцов, выходы формирователя кодов строк и первого умножителя соединены с входами сумматоров соответствующих нечетных строк матрицы, выходы второго умножителя и формирователя кодов столбцов соединены с входами сумматоров, соответствующих столбцов матрицы, отличающийся тем, что, с целью упрощения вычислителя, в него введен сумматор, через который выходы первого и второго регистров соединены с входом формирователя кодов столбцов, а входы сумматоров нечетных строк матрицы объединены с входами сумматоров последующих четных строк матрицы.

| Вычислительное устройство для управления лучом антенны | 1981 |

|

SU1841181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841199A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2016-11-20—Публикация

1982-10-04—Подача