Известиы преобразователи кода, обеспечивающие преобразование исходного к-разрядного кода в «-разрядный код, образуемый всеми п 2, л: 22 3 линейными комбинациями элементов исходного кода, и состоящий из двух стунеией, первая из которых содержит сумматоры по модулю два для получения всех С двучленных линейных комбинаций.

Предложенный преобразователь отличается от известных тем, что вторая ступень выполнена в виде переключателя с разделением нагрузки, входы которого соединены со всеми сумматорами первой ступени, а выходы объединены с помощью диодпых собирательных

схем для получения остальных - к - 1 линейных комбинаций исходного кода. Это noBbiuiaeT помехоустойчивость по отнощению к отказам отдельных элементов.

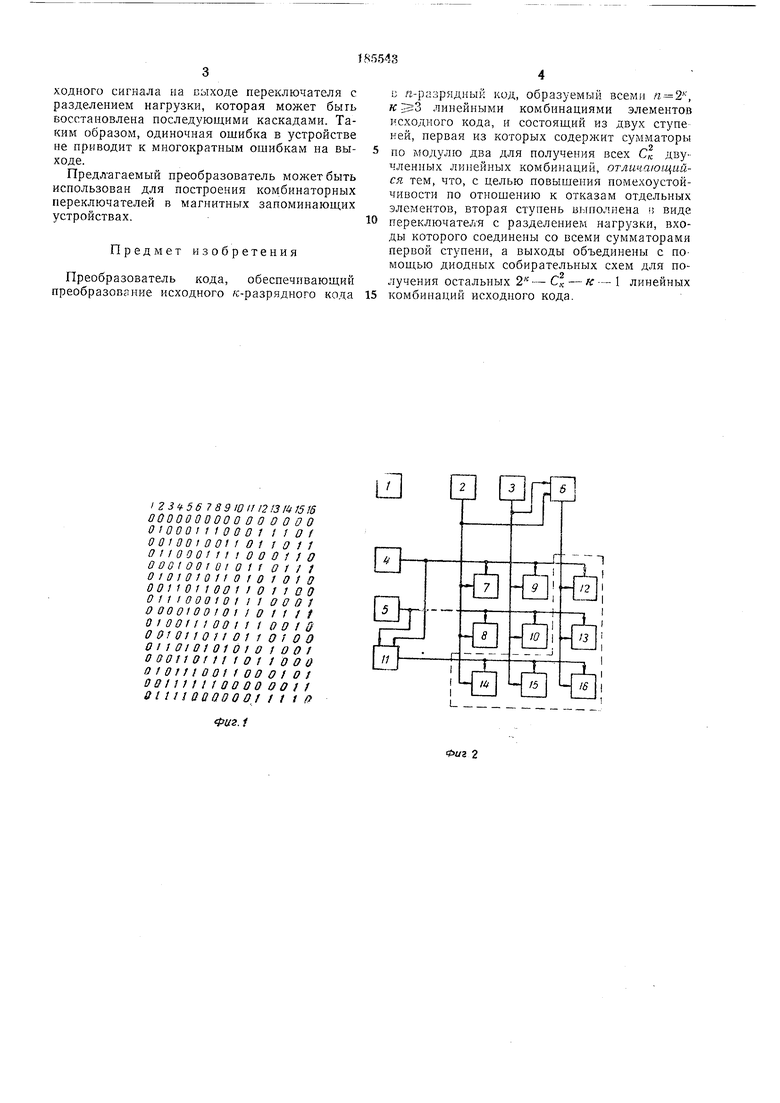

На фиг. 1 представлена таблица из всех линейных комбинаций исходного четырехразрядного двоичного кода. Если исходный код записать в виде вектора Х(Х-„ Xz, Х, , то записанный в таблице код У может быть представлен в виде Y (О, X-i, Xz, Х, Х, X -j-}-Х-2, Xi +XQ, , Xj-j-Xs, , , X,+X,+X,, Ji+Xa+X, X,+X,+X,, X,,+ -i-X, Xi4-.X2-f Xo-j-X), где сложение производится по модулю два.

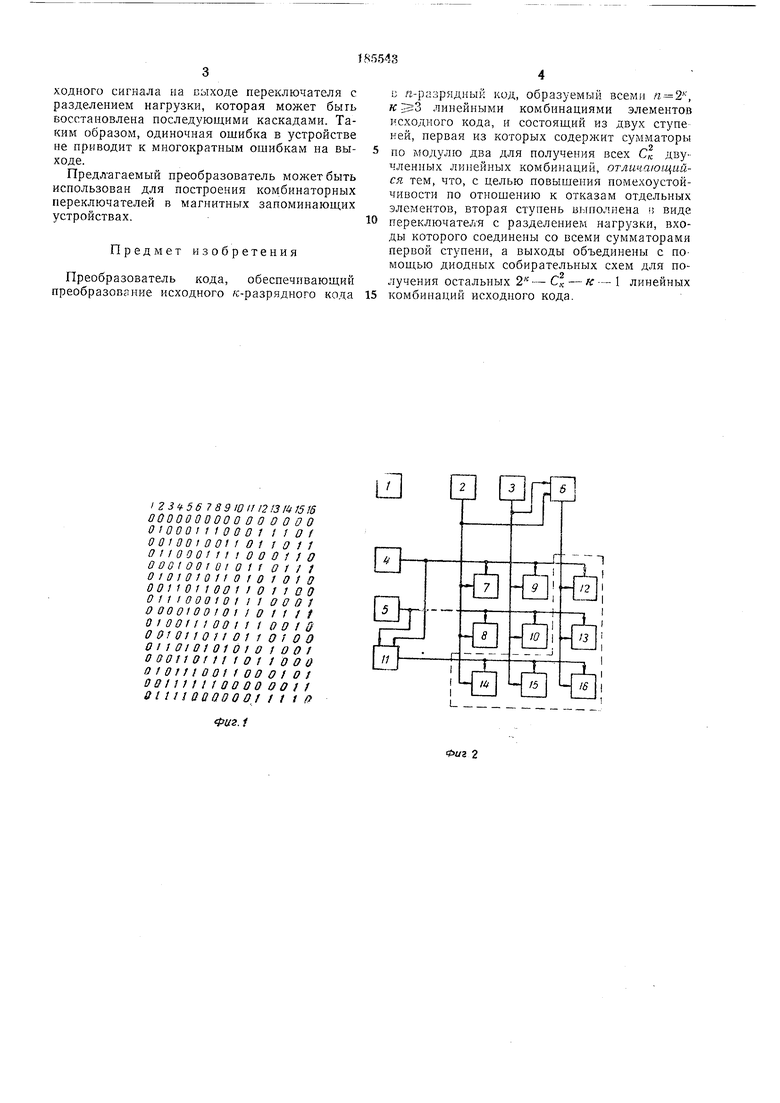

На фиг. 2 изображено устройство, в котором преобразование осундествляется с помощью сумматоров, образующих две ступени. В первой ступени (сумматоры /-11) образуются все двучленные линейиые комбинации исходного кода, а во второй ступени (сумматоры 12-16) - все остальные линейные комбинации.

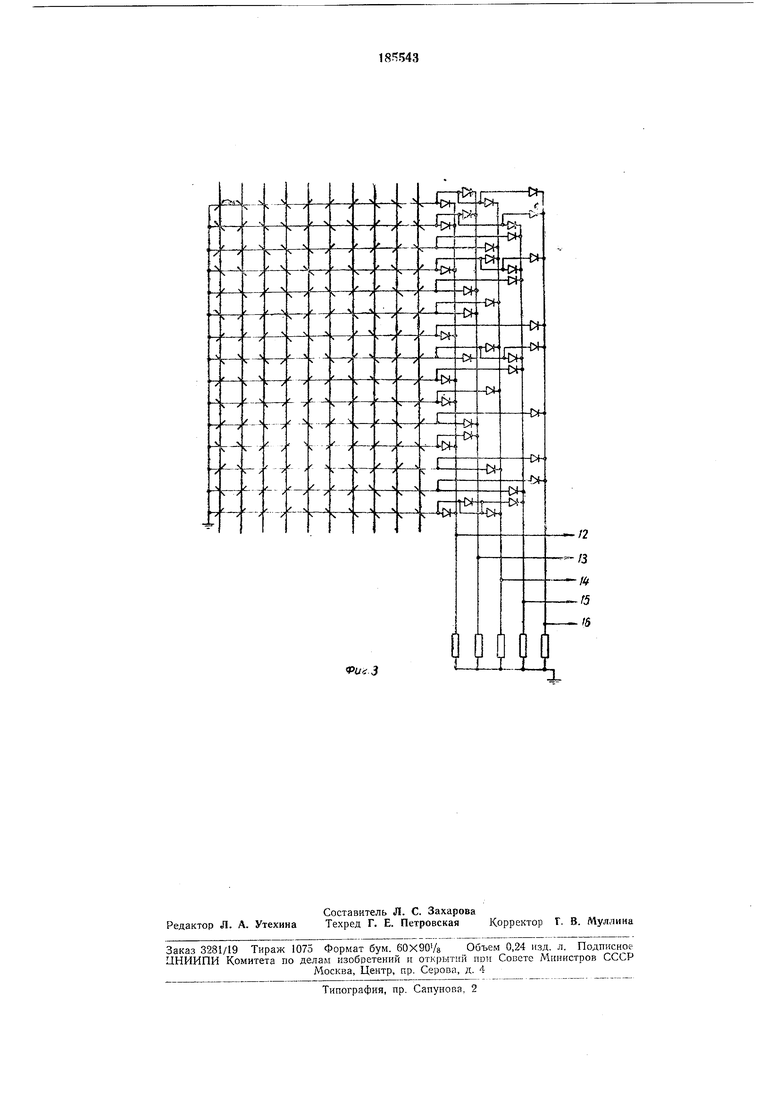

На фиг. 3 изображен переключатель с раздеоТением нагрузки, заменяющий в предложенном устройстве сумматоры второй ступени.

На фиг. 3 жирными вертикальными линиями изображены ферритовые сердечники, тонкими горизонтальными линиями - щины считывания. Короткие диагональные линни указывают направлепие прошивки. Выходные обмотки сердечников (на чертеже не указаиы) подключаются к выходам сумматоров первой ступени. Входы диодных собирательных схем подключены к тем щинам матрицы, иа которых появляется сигнал при поступлении на входы матрицы кодовой комбинации, у которой в столбце матрицы фиг. 1, соответствующем данному разряду преобразованного кода, стоит единица.

ходного сигнала на выходе переключателя с разделением нагрузки, которая может быть восстановлена последующими каскадами. Таким образом, одиночная ошибка в устройстве не приводит к многократным ошибкам на выходе.

Предлагаемый преобразователь может быть использован для построения комбинаторных переключателей в магнитных запоминающих устройствах.

Предмет изобретения

Преобразователь кода, обеспечивающий преобразование исходного к-разрядного кода

ц /г-разрядный код, образуемый всеми л 2, к 53 линейными комбинациями элементов исходного кода, и состоящий из двух ступе ней, первая из которых содержит сумматоры по модулю два для получения всех Ск двучленных линейных комбинаций, отличающийся тем, что, с целью повыщения помехоустойчивости по отношению к отказам отдельных элеглентов, вторая ступень выполнена п виде

переключателя с разделением нагрузки, входы которого соединены со всеми сумматорами первой ступени, а выходы объединены с помощью диодных собирательных схем для получения остальных С, -- к - 1 линейных

комбинаций исходного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодирующее устройство | 1983 |

|

SU1239868A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство для моделирования двоичного канала связи | 1986 |

|

SU1397932A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Преобразователь код-вероятность | 1973 |

|

SU450153A1 |

| Устройство формирования укороченного псевдослучайного @ -разрядного кода | 1982 |

|

SU1200424A1 |

| Последовательный одноразрядный двоичный сумматор | 1989 |

|

SU1615703A1 |

| Способ и ассоциативное матричное устройство параллельного поиска образца по его префиксам | 2021 |

|

RU2760628C1 |

I 2 89Ю1 I213IU1515 000000000000 0000 О О 00 f t О О О } I О ( OOtOOtOOIIOiJOf} OllOOO }t OOOf/0 OOOlOOtOlOtfOI/}

otoiotonotoioio

00 n on 00 1 t о j 1 D о 0 t I 0 00 I 0 I I 0001 о 00 0 t 0 t I 0 1 t t f OlOOIllOOlflOO/l} 00 On011011OiOO о I 1 01 01 01 0 I о i 0 0 000110 1} 1 о } 1 0 о 0 OfO IOOIlOffOffff

0 0 in n 1 a 0 Q 0 о о 11 SI inaaooo0,1 / / / /

Фиг.1

fPUi 3

Даты

1966-01-01—Публикация