I 1

Изобретение отндсится к вычислительной технике и может быть использовано в вычислительных машинах и системах для формирования контрольных кодовых комбинаций, предназнаенных для обнаружения ошибок в инормации, хранимой во внешней цамя- ти ЭВМ, а также в технике связи для помехоустойчивого кодирования инфор- ации в каналах связи с использованием циклических кодов.

Цель изобретения - повышение быстродействия кодирующего устройства путем последовательно-параллельной обработки информации.

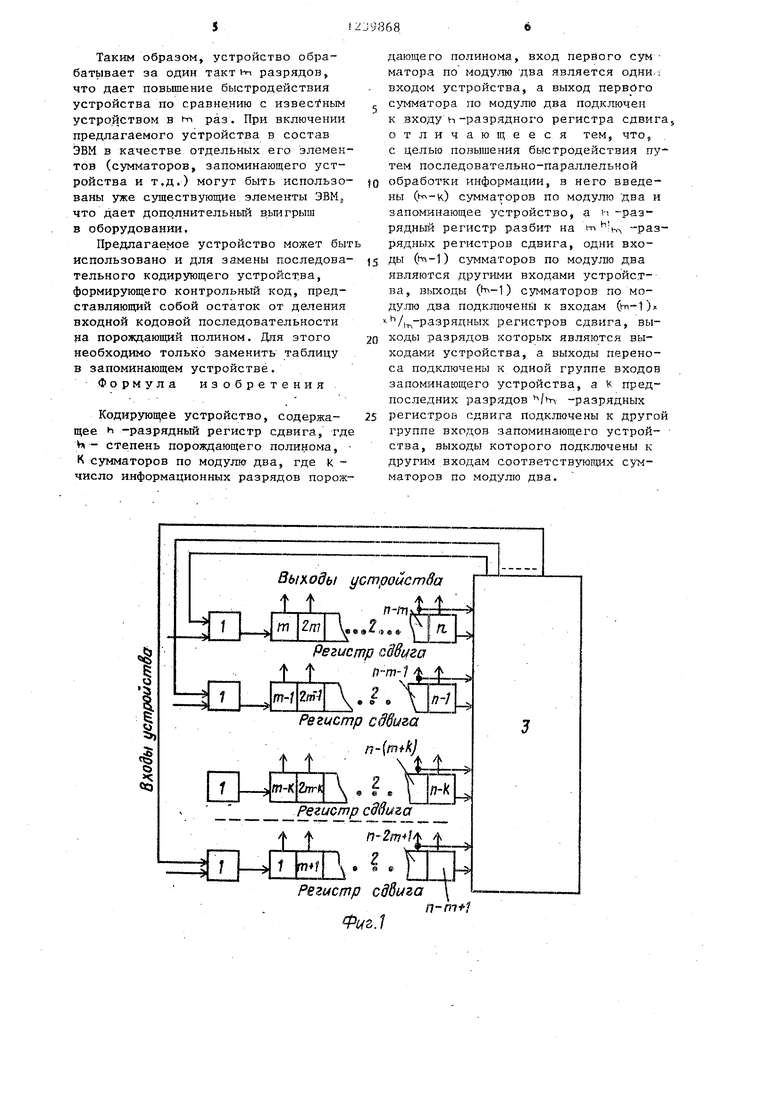

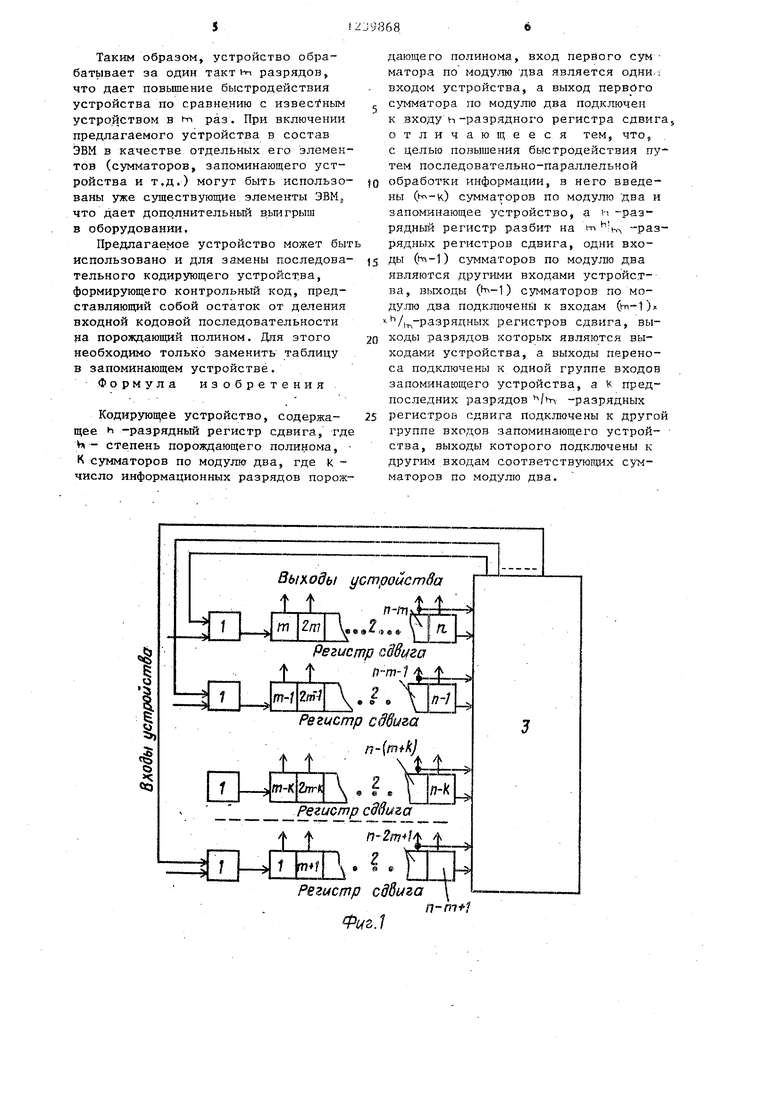

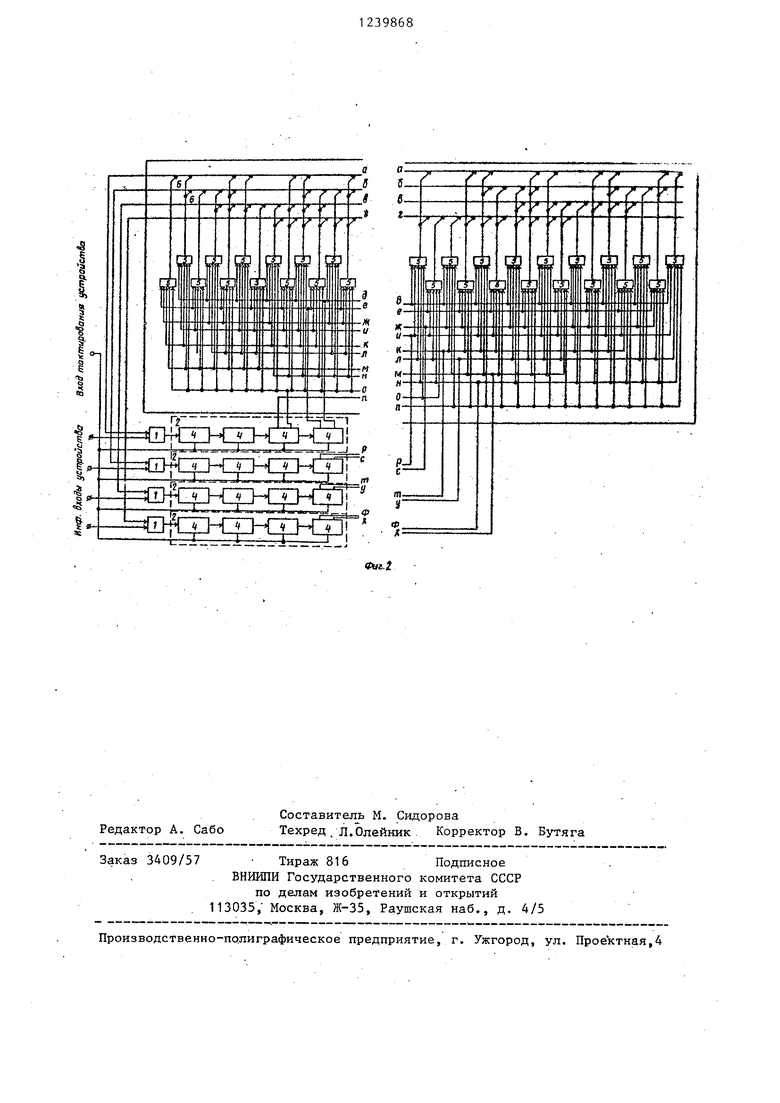

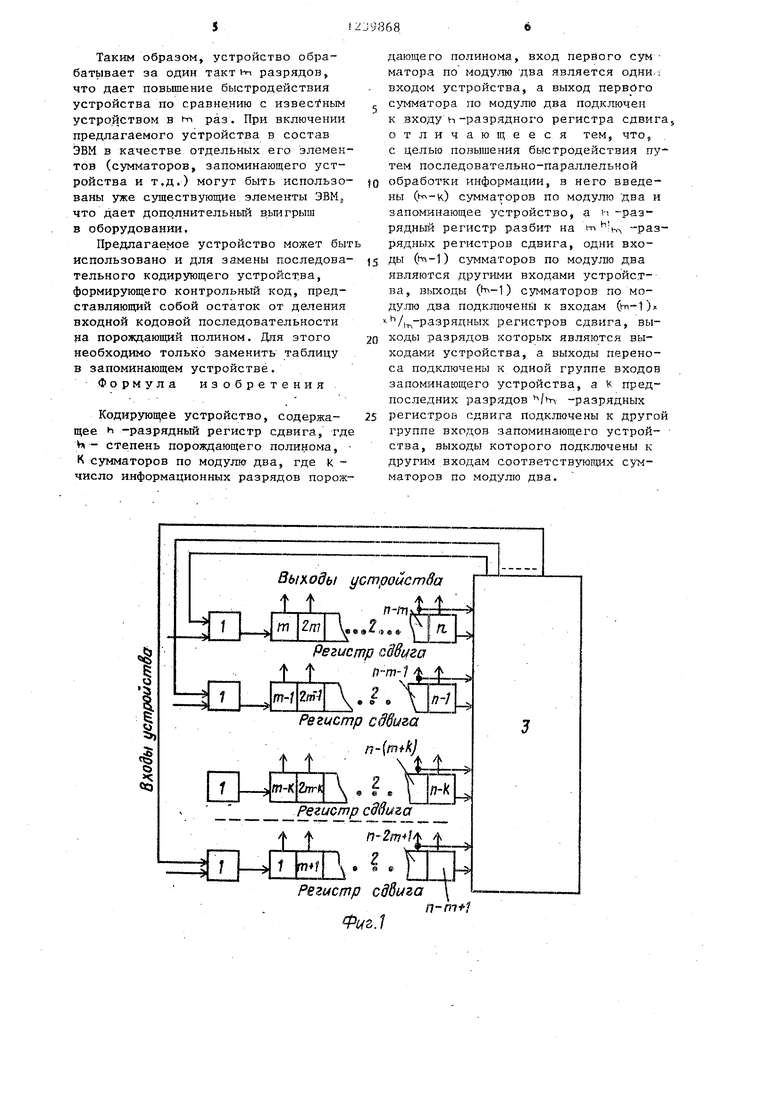

На фиг.1 приведена блок-схема коирующего устройства, предназначенного для формирования проверочных разрядов, циклического кода, образуемого полиномом вида ... на фиг.2 - принципиальная схема устройства, предназначенного для форми-, рования проверочных разрядов циклического кода, образуемого полиномом вида х - - х + 1 .

. Устройство содержит к су {маторов 1 по модулю два, t-r i/h-,-разрядных ре- гистров 2 сдвига, запоминающее уст- pOiiCTBo 3 (ЗУ выполнено в виде программируемой логической матрицы, фиг.2), триггеры 4, элементы ИЗ, диодные сборки 6 (элемент ИЛИ).,

Устройство работает следующим образом.

На вход устройства параллельно группам по 1-п бит 1:;рдается кодовая последовательность, для которой требуется сформировать проверочный код. Одновременно с подачей на вход очередной кодовой группы производится сдвиг информации по всех регистрах на один разряд и считьшание информации из запоминающего устройства по адресу, код которого представляет собой совокупность битов, содержащихся в последних разрядах всех, регистров сдвига и в К предьздущих разрядах регистров сдвига, При этом информация, считанная из запоминающего устройства, поступает на вторые входы сумматоров и суммируется по модулю два с информацией, поступившей: на вход устройства. Полученная сумма поступает в первые разряды регистров сдвига. Затем на вход

10

15

398682

устройства подается следующая кодовая группа и все повторяется.

В результате обработки m разрядов входной последовательности в первые

5 разрядов регистра сдвига помещена поразрядная сумма по модулю два Ьл битов входной последовательности с соответствующими битами, поступающими из цепи обратной связи, которые являются функцией h-i к последних битов регистра сдвига. В устройстве зта ,функция определяется за один такт с помощью таблицы, хранимой в запоминающем устройстве.

В запоминающем устройстве 3,которое может быть как оперативньм, так и постоянным, так как в нем постоянно хранится одна и та же информация, помещается таблица, сос20 тоящая из строк, каждая из которых представляет собой ,ьп -разрядный кодовый вектор, после г, тактов его работы, если перед началом его работы в последние (+к разрядов известного устройства был помещен адрес (аргумент) данной строки таблицы. Значение строки таблицы с адресом z.| , ,.-. , , может быть определено по формуле m 4. k:

Y,-I, a,.,,,(v-odi),

25

30

где

V - значение координаты

5

0

7

h-J + 1

вектора-строки таблицы,

-значение координаты вектора-адреса (аргумента) строки;.

-значение коэффициента порозкдающего полинома.

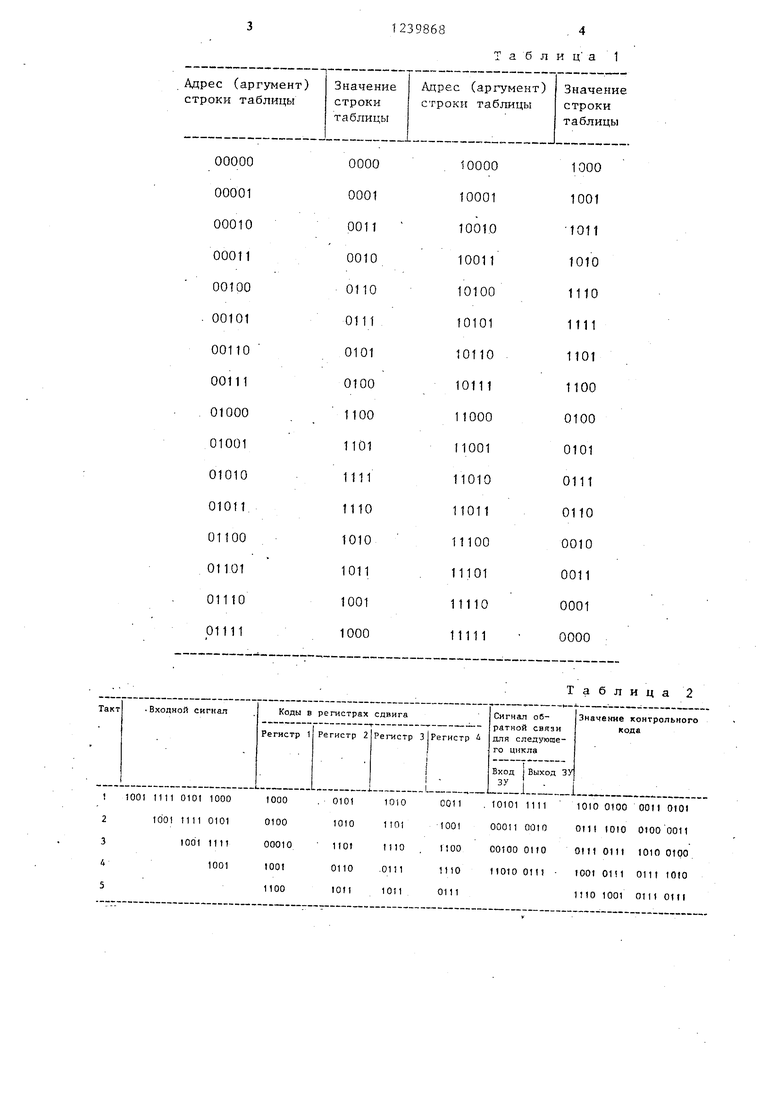

В качестве примера приведена табл., 1, соотв ;тству1ощая порождающему полиному X -I- X -i- 1 при tn 4.

В табл.2 приведена временная последовательность кодов, получаемая в различных цепях предлагаемого устройства в процессе формирования контрольного кода при значении входного сигнала: 1001 1111 0101 1000 и при следующих исходных значениях кода в регистрах сдвига:

Регистр 1 - 1000

Регистр 2 --0101

Регистр 3 - 1010

Регистр 4 - 0011

Т а б л и ц а 1

Таблица 2

Таким образом, устройство обрабатывает за один такт t-n разрядов, что дает повьипение быстродействия устройства по сравнению с извес ным устройством в ьл раз. При включении предлагаемого устройства в состав ЭВМ в качестве отдельных его элементов (сумматоров, запоминающего устройства и т.д.) могут быть использованы уже существующие элементы ЭВМ, .что дает дополнительный вьшгрыш в оборудовании.

Предлагаемое устройство может быт использовано и для замены последовательного кодирующего устройства, формирующего контрольный код, представляющий собой остаток от дапения входной кодовой последовательности на порождающий полином. Для этого необходимо только заменить таблицу в запоминающем устройстве.

Формула изобретения

Кодирующее устройство, содержащее и -разрядный регистр сдвига, гд Ц- степень порождающего полинома, К сумматоров по модулнг два, где К - число информационных разрядов порождающего полинома, вход пербого сумматора по модулю два является одни.-г входом устройства, а выход первого сумматора по модулю два подключен к входу h-разрядного регистра сдвига, отличающееся тем, что . с целью повышения быстродействия путем последовательно-параллельной

обработки информации, в него введены (N4-к) сумматоров по модулю два и запоминающее устройство, а i-, -разрядный регистр разбит на : -разрядных регистров сдвига, одни входы () сумматоров по модулю два являются другими входами устройства, выходы (Ьл-1) сумматоров по модулю два подкшочень к входам (ш-) /,-разрядных регистров сдвига, выходы разрядов которьгх являются выходами устройства, а выходы переноса подключены к одной группе входов запоминающего устройства, а К предпоследних разрядов -разрядных

регистров сдвига подключены к другой группе входов запоминающего устрой- ства, выходы которого подключены к другим входам соответствующих сумматоров по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ двоичных ЦИКЛИЧЕСКИХ кодов | 1972 |

|

SU335691A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Устройство для кодирования циклических кодов | 1982 |

|

SU1083385A1 |

| Единый генератор псевдослучайных последовательностей (ПСП) приемника сигналов Глобальных Навигационных Спутниковых Систем (ГНСС) | 2022 |

|

RU2789320C1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Оперативное запоминающее устройство с коррекцией информации | 1983 |

|

SU1111206A1 |

| Декодер укороченного кода Хэмминга | 1983 |

|

SU1109924A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах для формирования контрольных кодовых комбинаций,предназначенных для обнаружения ошибок в информации, хранимой во внешней памяти ЭВМ, а также в технике связи для помехоустойчивого кодирова- ния информации в каналах связи с использованием циклических кодов, С целью повышения быстродействия кодирующего устройства путем последовательно-параллельной обработки информации в кодирующее устройство, содержащее h -разрядный регистр сдвига, где - степень порождающего полинома, Ц сумматоров по модулю два, где К - число информационных разрядов порождающего полинома, введены () сумматоров по модулю два и запоминающее устройс тво, а ь -разрядный регистр разбит на rr vifvn -разрядных регистров сдвига. На вход устройства параллельно группам и по n-v бит подается кодовая последовательность, для которой необходимо сформировать проверочный код. Одно- . вреь-генно с подачей на вход очередной кодовой группы производится сдвиг информации во всех регистрах на 1 разряд и считывание информации из запоминающего устройства по адресу, код которого представляет собой совокупность битов, содержащихся в последних разрядах всех регистров сдвига и в К. предьщущих разрядах регистров сдвига. Информация, считанная из запоминающего устройства, суммируется с входной в сумматорах по модулю два. 2 ил, 2 табл. to оо () 00 а 00

Выводы устройства tn-n Л т

Zm

(deft

-J-- -- -- fceMeJ

Регистр сЗвига

t t f f 7; / 4 V dii:-Л. nj

,,-f-, - - ,ifc,

Регистр сдвига /7.( t tVl-4: регистр сдвмга

Регистр сдвига .1

/7-2w-f/4 A

I

0 e

n-m-t-l

Редактор А. Сабо

Составитель М. Сидорова

Техред/л.Олейник . Корректор В. Бутяга

3409/57

Тираж 816 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Питерсон У., Уэлдон Э | |||

| Коды, исправляющие ошибки | |||

| М.: Мир, с | |||

| Способ исправления пайкой сломанных алюминиевых предметов | 1921 |

|

SU223A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-06-23—Публикация

1983-10-18—Подача