Двухканальный аналого-цифровой преобразователь поразрядного уравновешивания, основанный на использовании в зависимых каналах разных двоично-десятичных кодов, известен. Однако он имеет такие недостатки, как малая надежность и помехозащищенность, влияние канала на канал, обусловленное конечными входными сопротивлениями каналов, относительно низкое быстродействие, увеличение которого ограничено переходными процессами в преобразователе, значительными динамическими ошибками, возникающими при измерении изменяющихся напряжений.

Предлагаемый преобразователь отличается от известных тем, что для новыщения достоверности результатов измерения, в каждом канале к входам триггеров реверсивного счетчика-сумматора канала подключены логические схемы совпадения и запрета; один вход схем совпадения присоединен к распределителю синхропотенциалов, второй вход - к выходу устройства сравнения другого канала; вход схем запрета ирисоединен к выходам логических схем совпадения, объединяющих выходы триггеров счетчика в каждом канале.

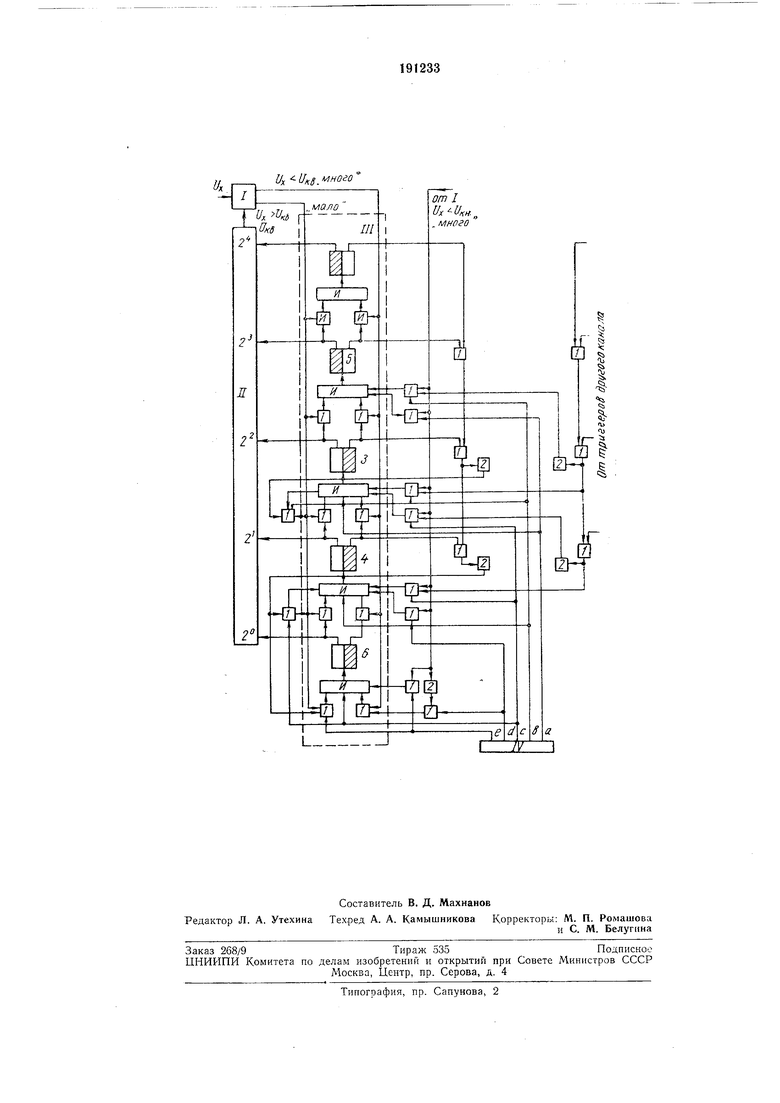

На чертеже представлена функциональная схема одного из каналов преобразователя.

иряжения, реверсивный счетчик-сумматор ///, управляющий ключами блока /, направление счета в котором определяется выходным сигналом устройства / сравнения, группы логических схем совпадения 1 и запрета 2 и общий для двух каналов распределитель синхропотенциалов /V.

Устройство работает следующим образом.

В исходном состоянии в реверсивном счетчике П1 набрано в двоичном коде число 24 (в реверсивноК счетчике другого канала -- число 8), ц блок // выдает напряжение в 24 единицы.

измеряемое напряжение L.v 10,5 единиц. Тогда от устройства сравнения / верхнего канала ноступит сигнал «много (t/v ке), а от устройства сравнения нижнего канала сигнал «мало (L.,.e). Реверсивный счетчик верхнего канала при этом включается на 5ычитание, и импульс с щины а распределителя спнхропотенциалов перебрасывает триггер 3 счетчика /// в другое положение, после чего в счетчике оказывается число, равное 20 (в реверсивном счетчике нил него канала к этому моменту будет число 12).

Устройство сравнения верхнего и нижнего каналов по-прежнему выдает сигнал «много (счетчик верхнего канала включен на вычитание). Импульс с щины b распределителя синхропотенциалов перебрасывает триггер 4

и через логические схемы / и схему 2, управляемую от трех старших триггеров второго канала, также перебрасывает триггер 5. В результате в счетчике /// образуется число 10, и устройства сравиения обоих каналов дают сигнал «мало, вследствие чего счетчик /// включается на суммирование.

Импульс с шины с распределителя иеребра. сывает триггер 6 и через логические схемы /, объединяющие триггеры верхнего канала, схемы 2 и схему /, управляемую с шины «мало устройства сравнения /, триггер 3. В результате в счетчике набирается число 13. Устройство сравнения обоих каналов дает сигнал «много. Связи счетчика переключаются на вычитание.

Импульс с шины d распределителя проходит через схему 1, управляемую с шины «много устройства сравнения нижнего канала, и уменьшает содержимое счетчика на 2 единицы.

Компенсационное напряжение верхнего канала 6«в становится равно И единицам, и реверсивный счетчик переключается на вычитание. При этом импульс с шины е распределителя не попадает на триггеры счетчика и не изменяет его состояния, так как схемы /, на которые подается импульс с этой шины, закрыты.

Таким образом при 7.1- 10,5 единицам компенсационное напряжение верхнего канала равно 11 единицам, а нижнего - 10. По окончании измерения и считывания результата измерения с реверсивного счетчика любого из каналов на триггеры счетчиков подается импульс «сброс (не показан на чертеже), иереводяш,ий счетчик в исходное состояние.

Чтобы исключить переполнение реверсивного счетчика, в схеме преобразователя предусмотрены логические схемы 1, объединяющие выходы триггеров реверсивного счетчика. Импульсы с распределителя синхропотенциалов подаются через эти схемы так, что если триггеры находятся в состоянии «1, и тем самым сущее 1вует возможность иереиолнения счетчнка, то схема оказывается закрытой и не пропускает на счетчик импульс, который может переполнить его.

Предмет изобретения

Двухканальный аналого-цифровой преобразователь поразрядного уравновешивания, содержащий устройства сравнения измеряемого и компенсационного напряжения, блоки формирования компенсационного напряжения, реверсивные счетчики-сумматоры, управляющие ключами блоков формирования компенсационного напряжения, распределитель синхропотепциалоБ с группой оюгических схем, отличающийся тем, что, с целью повышения достоверности результата измерения, в каждом канале к входам триггеров реверсивного счетчика-сумматора канала подключены логические схемы совпадения и запрета; один вход схем

совпадения присоединен к распределителю синхропотенциалов, второй вход - к выходу устройства сравнения другого канала; вход схем запрета присоединен к выходам логических схем совпадения, объединяющих выходы триггеров счетчика в каждом канале.

Uf,s. ного

и.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ— КОД». | 1968 |

|

SU209086A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГОНАПРЯЖЕНИЯ | 1966 |

|

SU188587A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД | 1972 |

|

SU340078A1 |

| В. И. Патерикин Институт автоматики и электрометрии СО АН СССР | 1967 |

|

SU200882A1 |

| Калибратор фазы звуковых и инфразвуковых частот | 1975 |

|

SU570852A1 |

| Устройство для управления многоканальным импульсным регулятором мощности переменного тока с @ -нагрузками | 1987 |

|

SU1545306A1 |

| Многоканальный преобразователь угол-код | 1972 |

|

SU451116A1 |

| Многоточечный сигнализатор уровня | 1982 |

|

SU1114889A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО СЧЕТА ПОДВИЖНЫХ ЕДИНИЦ | 1973 |

|

SU407776A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

Авторы

Даты

1967-01-01—Публикация