Изюйретеиие относится к имиульсиой ,ке и мюжет быть Ис;п1ольз10 ва1но для п.реобразавания аналогового сигнала в код.

Из1ве|СТ1НЫ преобразователи яаиряжеииякод, содержащие блок формирования компен,са1цио,нно1го напряжения, блок сравнания измеряемото и К0мпен1сацио но1го иапряжаний, рав роииный счетчи:к-су|М,мат:0|р, у1пра1вляк щий блакОМ фор|Мир:01вания К(ОМ1пен,са1ЦИО|Нето|По иапряжаНИя, распределитель оинлроиотанциаЛОВ и два блока в1реме;нн1ой задержки.

Од1на1ко известные шрео бразователи не выделяют величину изманання натряженил сигнала, проходящего в промежутке между измере1Нвя1МИ.

С целью получения в процессе преобразования т/очного значания разности межд|у кодами д1В|ух смежных п|рео1бразо|ваний предлагаемый нреобраэователь -напряжение-код содержит регистр раз-ности, триггар siHaiKa раэности и логический блок выделения разности, причем ВЫХ10Д ра)определителя iCHHXipoпоте1Н1Циало1В и выходы блоков враман1НОЙ задержки подключены к сигналынькм входам логического блока выделения разности, выходы триггеров раварсивного счетчика-сумматора, выхюд блока -сравнения и выходы триггера знака разности подключены к управля1Ю1иД|И1М входам логичаокото блока выделения раэности, выходы которотО соединены со

входами триггеров регистра разности и входам триггара знака разно|сти, а выходы реварсивнОГо счетчи1ка-1сум1матара под1К1ЛЮчены к у|ста1новочнЫ(М входам т1рИ1ггеров реверсивного 1счетчи1ка-|а 1мматора.

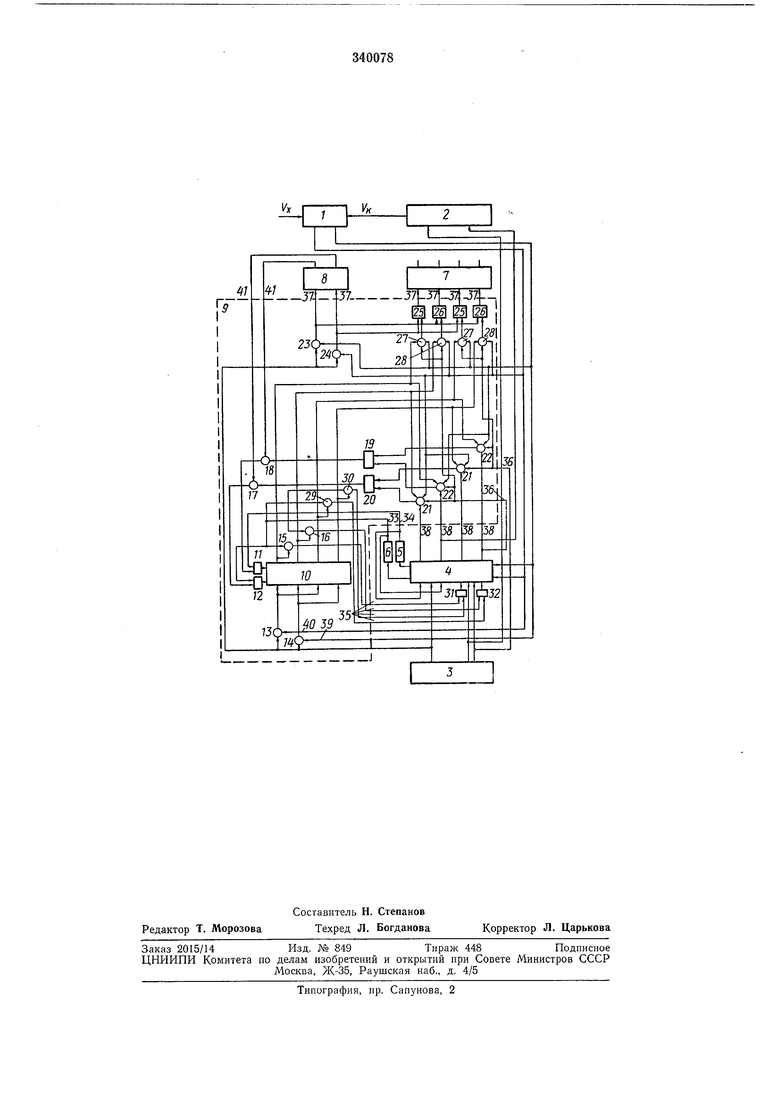

На чертеже приведена блюк-схема оредлаraeMOino устройства.

Преобр.азо1ва;тель состоит из блока 1 сравнения измеряемого « «омпейсадиоаного напряжений, (блока 2 |фор.ми|р01Бания ко.м нансациоиного напряжения, распределителя 3 синх|р101п оте1НЦиал0(в, peiBapiCHBiHOno счетчика-сумматора 4, управляющего блоком 2 формирования комиенсационнош напряжения, блокскв

5 и 6 .В|рем-ен1ной задержки, регистра 7 разности, триггера 8 знака раз(ности и ло1ГИ1чеСКО1ГО блока 9 выделения разности.

Люгичеакий блок 9 выделения разности состоит из реверси1В1НО1го счетчика 10 сигналов

переполнения счетчика-юуММ а тор а 4, схем «ИЛИ /У и 12, схем «И , схам «ИЛИ :}9 и 20, схем «И 21-24, схе.м «ИЛИ 25 и 26, 1схем «И 27-30 и схам «ИЛИ и 32.

|Выхощы блоков 5 и 5 в|ременной задержки соединены через сишналыные входы 33 и 34 блока 9 со схемами «И 15, 16, 29 и 30, управшяемых выходам-и трИГгеров счетчика iO, со входами схем «ИЛИ // и 12 и с устаряда счетчика-юу-мматора 4. Выхюды схам «И 15, 16, 29 и 30, 1соста1вля1ощие выходы 35 блока 9 выделения (разиойти, подключены через схе.мы «ИЛИ 3,1 и 32 « установочным входам трипгерО1В .младших разрядOIB счетчика-су мкм а то pa 4. Распределитель 5 синхропотенциалав Овоими 1вых,одами сое,ди.не1Н со сч;ет1НЫ1ми 1вх1ода ми триггеров счетчик а-с|у1М,мат;ор;а 4 Е с сипнальпыми входзми 36 бложа 9 выделения разности. Скпнальные входы 36 блока 9 выделения рЯзности, соедине1нные с первЫМ выходом распределителя 3 синхропотенциалов, подключены ко входам схем «И 13 и 14, выходы которых соединены с установочными входами счетчика 10, и ко вх1одам схем «И 23 и 24, выходы последних соединены со BxioaaiMH схем «ИЛИ 25 и 26. того, выходы схем «И 23 и 24 через выxioды 37 сигналов разности бло.ка 9 выделения разНЮ1СТИ пО|Д1ключе1ны к устано1воч1ным 1ВХ|Ода1м триггера 8 знака разности, а схемы «ИЛИ 25 и 26 через те же выходы блока 9 выделения разности-IK устано1воч1НЫ1М вх10дам триггеров регистра 7 разности. Сигналыные входы 55 блока 9 выделения разиости, соединенные с остальны1ми выходами распределителя 3 синхронотенпиалов, подключены кю входа1М схе.м «И 2,1 и 22. Выходы (юржмы е и инверсные) триггеров роверсивного счетчи1ка-1сум1матора 4 подключены через управляющие входы 38 блока 9 выделения разности ко входаа схем блока 2 фо р М ИР ов аи и я KiOMin енс ацио нного и ал р яж е ни;я, его выход соединен со входом блока 1 сравнения, на вход которого подается преобразуемое напряжение. Выходы блока / сравнения подключены к упра1вляю1щи.м входам реверсивиого счетчика-сум|матора 4 и через управляющее входы 39 и 40 блока 9 выделения разности - -ко входам схем «И 13, 14, 21, 24, 27 и 28. Выходы триггер.а 5 знажа разности нодключены через управляющие входы 41 блока 9 выделение разности ко входам схем «И 27 и 28. Выходы трИ|Ггер|01В счетчика 10 соединены со входами схем «И 27 и 28, выходы которых под1ключе1ны ко входам схем «ИЛИ 25 и , а также со в;хода1ми схем «И 21, 22, выходы которых через схемы «ИЛИ 19 и 20, cxeiMbi «И 17 и Ш соединены со входами схем «ИЛИ 1,1 и 12. Преобразователь работает след|уЮЩИ1м образом. На in epiBOM сиахропотенщиале, 1ностунающ.ем с .первого выхода .распределителя 3 синхропотенциалов на счетный вход триггера старшего разряда раверсивного счетчика-сумматора 4 в зависимости от состояния блока 1 сравме.ния, к код.у счетчи|ка-юум.матора 4 прибавляет1ся лжбо вычитается «е.ди1ни1ца, соответСтвующая весу этого разряда. На этом синхронотеициале, нрощедшем через схаму ли1вается «нулевое ли.бо «единичное сО|Стояние. TaiKHM образом, определяется разности, так как иачалыное состояние блока Jf сравнания свидетельствует о зиаке рааности t/x - UK, где (7х - «апряЖепие выходного сигиала, UK - ко1М1Пенсациоиное напряжение,, соот1вет ст1вующ,ее коду реверсивного счетчнкасумматора 4. На блок / 1Сра1В(неиия накладывается условие ееизменности состояния во врСмени пере ходных процассов в ревер1си1вном счетчи1ке-сум|маторе 4. С дно1В ре1ме1ННо сигнал с выхода схемы «И 23 (или 24) проходит через схе;му «ИЛИ 25 (или 26) соответютветиш. устана1влн1В.ает в начальное «1Нулевое или «единичное состояние триггеры ре,ги1стра 7 разности. Код разиости, формируемый на следующих тактах на триггерах ре1гистра 7 раз|ности, нолучается прямым при одиом знаке разности и обратным при другом, такж-е в зависимости от состо.яНЕя блока 1 cpaiBнания (Первый синхропотенциал, пройдя через схаму «И 13 (или 14) устанавливает в начальное «нулевое или «единичное состоя1ние триггеры счетчика 10 блока 9 выделения разности. На счетчике-сумматоре 4 цифровой эквив алент .преобразуемого напряжения всегда фиксируется в нрямо1м коде. В случае, если старше го раэряда счетчика-сумматора 4 находится в «единичном состоянии, а блок 1 сравнения дает разрешение на .шнне «)больше, что о.31начает для счетчик а-сумматора 4 режим «суммирования, то этот триггер пе|ребра1СываеТся на первом синхронотенцнале в «нулевое состояние, но на выходе блока 5 задержки поя1вляется си|Рнал переполнения, восстанавливающий «единич|ное состояние этого триггера. Этот же сишал с выхода блока 5 В)рвман;ной з аде|рж1ки noiCTyпает на блок 9 выделания разности и, пройдя через схем|у «ИЛИ 1,1, прибавляет «единид|у к началыному «.нулевому ко.ду счетчика 10, который служит для подсчета количества си1гнало1в переполнения счетчика-ciyMматора 4 и сигналов имитации его паренолнения. Си1гналы имитации переполнения счетчик а-сумматора 4 формируются толыко на следую1щих синхронотеяциалах с помощью элементов логического блока выделания разности схем «И 21, 22, 17 и /5 н схем «ИЛИ 19 и 20. В случае, если три1гге р старшего разряда счетчика-суммато|ра 4 находится в «1Н;улеаом состоянии при разрешении на шине «/.меныше блока / сравнения, то на выходе блока 6 времен1ной задержки поя|вляется сигнал переполнени:я, воостанавливающий «iHiyлевое состояние этого триггера, и в блоке 9 выделения разности, .пройдя схему «ИЛИ 12, он просчитается в счетчике 10. В этом сл|учае начальное состояние т|ритгеров счетчи1ка Ю «единичное, и ситнал с вых|0да схамы «ИЛИ 12 уменьшит содержимое счетчика на «единицу его младшего разряда. На второ.м синхронотенциале со следующе5лов к коду реверсивного счетчика-суаьматора 4 прибавляется или вычитается «единица соОТ1БетствуюЩ;его разряда. На этоМ же синх|р|0цо:те|нциале з аалсъшает1СЯ состоя1иие триюгера старшего разряда5 ючетчика-оумматора 4 в старший разряд регистра 7 разйости в случае, если ва преиыд|ущем такте происходит иамеиение состояния этого триггера, не вызывающее измеиание состояция блс1ка / сравнения, при это1м вто-Ю рой синх|р01поте1нциал проходит через схему «И 27 (или 28), затбм схему «ИЛИ 25 (или 26) и поступает на один из установочны.х входов старшего триггера регистра 7 разяости. Схемы «И 27 и 28 управляются15 выхода1ми триггеров счетчика 10 и выходами блока 1 сравнения. Синхропотенциал прох;0дит схему «И 27 тольвд в случае, если И1меет1ся разрешение на данном такте на шине «больше блока 1 сра1вне1ния и не происходит20 пе|реполнение счетчика-сумматора 4 на nipeдыдуш,ем такте. В cxeMiy «И 28 синх1ронотенциал пройдет голыко в том случае, если и.меется разрешение на шине «(меньше и перед этим отсутствует перепол;нение счетчн-25 ка-сумматора 4. Часть логического блока 9 выделения разности, состоящая из схем «И 2(1, 22, 17 и 18 и схем «ИЛИ 19 и 20, служит для имитации сигналов переполнения счетчика-сумматора 4,30 в последнем, сигналы переполнения формирую1тся на то.м же такте, на котором происходит его переполнение, проходят как на вход счетчика 10, так и на уста1нов1041ные входы триггеров счетчи1ка-сумматора 4. Если35 б очегчик-сумматор 4 переполняется на произвольпом такте, то имитации переполнения счетчика-сум|Мато,ра 4 проходят только «а вход Счетчика 10 и служат для обеслечения правильной работы схемы, П.р е д ,м е т изобретения .Преобразователь натряжение-код, содержаЩ,ий блок формирова-ния Ko MineiHcauHOiHiHoro напряжения, блок С(ра1В1нани1Я из.Ме|ряамого и компенсационного напряжений, реверсивный счетчик-сумматор, управляющий блоком формиров а ния компенсационного напряжения, распределитель сипхропотенциалов и два блюка враменной задержки, отличающийся тем, что, с целью получения в процессе преобразования точного значения разности между кодами двух смежных преобразований, он содержит регистр разности, триггер знака разности и ло:гичес1кий блок выделения разности, причем выход распределителя синхропотенциалов и выходы блоков временной задержки подключены к сигнальным входам логического блока выделения разности, выходы триггеров реверсивного счетчи1ка-сум матора, выход блока сравнения и выходы тришгара знака разности -водключены к ушравляющим входам логического блока выделения разности, выходы которого соединены со ВХ1ода|МИ трипгеров регистра разности и входо1м триггера знака разности, а выходы реверсивного счетчикансумматора подключены к уста1новочны:м входам трнггеров реверси1вного счетчика-сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ— КОД». | 1968 |

|

SU209086A1 |

| Преобразователь напряжения в двоичный код | 1972 |

|

SU482005A1 |

| УО:;СОЮЗНАЯ | 1973 |

|

SU363202A1 |

| ДВУХКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1967 |

|

SU191233A1 |

| Преобразователь напряжение-код | 1977 |

|

SU622201A2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГОНАПРЯЖЕНИЯ | 1966 |

|

SU188587A1 |

| Устройство для преобразования двоичных кодов приращения функции | 1975 |

|

SU550657A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

Даты

1972-01-01—Публикация