Извеетиы преобразователи напряжения в цифровой код гюразрядного ураВ110веи ива1Г Ш, содержаи1,ие устройство сравнения преобразуемого и компенсационного сигналов, преобразователь кода в напряжение, связанный с триггерами памяти, логическое устройство, распределитель сиихропотенциалоз и генератор тактовых импульсов.

Предложенное устройство отличается тем, что оно еодержит два пороговых устройства с двумя схемами «ИДИ, схему антисовпадения, переключатель преобразуемого сигнала и схе.му запрета тактового и.мпульса, причем входные цепи пороговых устройств вклЕочены параллельно 1-1 ниверсно ;по отношению друг к другу. Выходы одного из этих устройств и устройства сравнения соедшшны через одну схе.гу «ИДИ с логичееким устройством, выходы нороговых элементо;:; через другую схему «ИДИ и схему антисовпадения - с переключателем преобразуемого сигпала. В цепь запуска распределителя синхропотепциалов жлючеиа схема запрета тактового импульса, соединенная с выходо.м генератора тактовых имнульсов и выходом переключателя преобразуемого еигиала. Это позволяет снизить пеperpysKii устройства сравнения и увеличить быстродействие преобразователя.

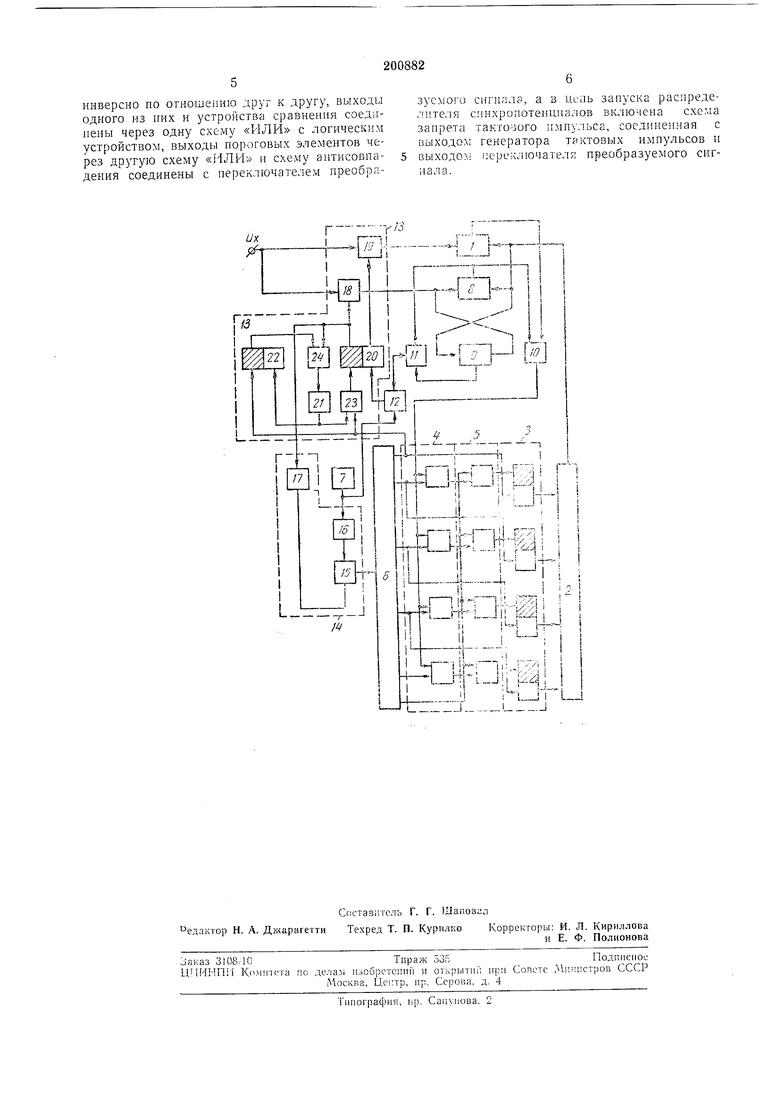

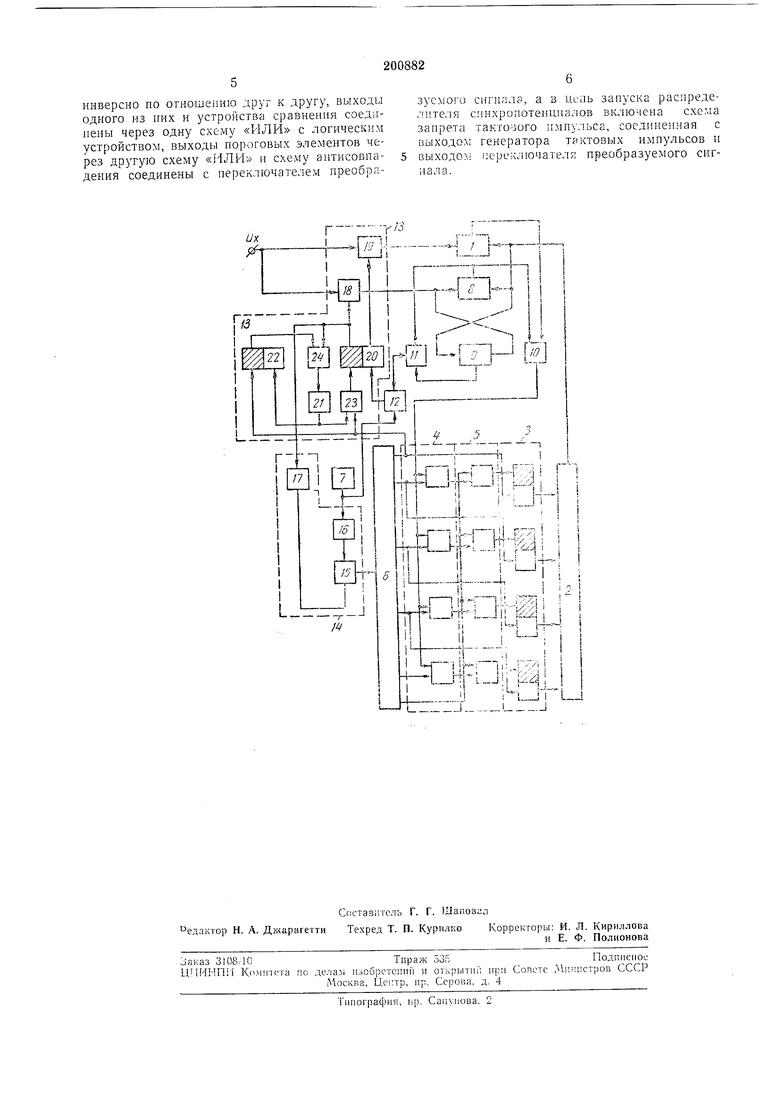

Он содержит

устройство / сравнения преoбpaзye гoгo и компенсационного сигиалоз, 2 кода в напряжение, тригпреобразовательгеры памяти 3, управляюшие преобразователем кода в папряжеиие логические схемы «И 4 «ИДИ 5, с помощью которого производится соответствуюна,ее переключение триггеров памяти в процессе уравновешивания, распределитель синхропотенцпалов 6 и генератор тактовых импульсов 7. Кроме того, преобразователь содержит два пороговых элемента 8 и 9, входные цепи которых включеиы параллельно и инверсио по отношению друг к другу. Выходы порогового эле.мепта 8 и устройства сравнения соединены через схему МЛИ 10 с логическим устройство.м 4, а выходы пороговых элементов 8 и 9 - через схему «ИДРЬ // и схему аптисовпадения 12 с переключателем 13 нреобразуемого сигнала во входных цепях нороговых эле.ментов и устройства сравнения. В цепь запуска распредел1ггеля синхропотенциалов включена схема запрета тактового импульеа 14, которая сод(ржит cxeNiy антисовпадения /5, элемеит задержки тактовых импульсов 16 i одновибратор 17. Один вход схемы антисовиадеиия 15 соединен с эле.меитом 16 задержки тактовых и.мпульсов, а другой - с выходом однов братора 17. Цепь запуска этого одновнбратора соединена с одним из выходов переключателя

13. Последний содержит ключ 18 во входной цепи порогозых элементов и ключ 19 во входнон цепи устройства сравнения, триггер 20, управляющий ключами 18 и 19, одповибратор 21 и триггер 22 - элемент памяти числа переключения ключей. Цепь запуска триггера 2(9 соединена с выходом схемы антисовпадения 12, а цепь сброса соединена через схему «ИЛИ 23 с нервой выходной шиной распределителя синхропотенциалоз и е выходом одновибратора 21. Его цепь запуска соединена с ВЫХОДОМ схемы «И 24. Один ее вход соединен с выходом левого плеча триггера 20, с KOTopbtM соединена цепь управления ключа 18, а другой - с выходом левого плеча триггера 22. Цепь запуска последнего соединена с выходом одиоБибратора 21, а цепь сброса - с первой выходной шиной распределителя синхропотенциалов.

Цифро-аналоговый преобразователь работает следуюилим образом. РЬшульсом, -снимаемым с первой выходной шины распределителя синхроиоте;-1циалов, триггеры 20 и 22 будут установлены в такое состояние, в котором с выходоз левых нлечей будет сниматься сигнал «единицы. Ма выходе устройства формирования компенсационного сигнала будет сформировано напряжение, величина которого соотЕетствует «весу -старшего разряда кода, а ключ 18 во входных цепях пороговых элементов будет замкнут. Если значение преобразуемого напряжения будет отличаться от компенсационного в ту или другую сторону больше, чем па величину порога срабатывания элементов 6 и 9, один из них перейдет из нулевого состояния в состояние «единицы.

Предположим, что пороговый элемент 8 переходит Б Состояние «единица, когда значение напряжения компенсации превышает на величину порога срабатывания зиачение преобразуемого напряжения, тогда пороговый элемент 9 будет находиться в нулевом состоянии, и наоборот. Состоянию «единица какого-либо из пороговых элементов соответствует отсутствие сигнала на выходе схемы антисовпадения 12, в результате чего триггер 20 ие изменяет свое состояние и, следовательно, ключ 18 замкнут, а ключ J9 разомкнут. Процесс преобразования производится с иомощью ныходного сигнала порогового элемента 8 до тех пор, пока в один из тактов сравиеиия нн один КЗ пороговых элементов не срабатывает. Тогда в следующий такт выходным сигналом схемы аитисовпадения 12 триггер 20 будет переброшен в новое состояние, ключ /6 разомкнется и замкнется ключ 19.

Р1зменеиие состояния триггера 20 вызовет .запуск одновибратора 17, что вызовет запрещение прохождения импульса такта на вход распределителен еинхро110тснциалов. Состояиие триггера памяти 3 ие изменяется и остается неизлшниым значением напряжения компенсации иа выходе устройства формирования. В это время сравнение величин преобразуемого компенсациоиного напряжений производится с помощью устройства сравнения, выход которого, так же как и порогового 5леме та 5, соединен через -схему «ИЛИ 10 с логическими схемами «И 4 и «ИЛИ 5.

Одновременно с изменением состояния триггера 20 и включеиием ключа 19 вместо 18 происходит залуск одновибратора 21, длительность выходного импульса которого должна быть liOMHorHM более длительности такта сравнения.

Задним фронтом выходного импульса этого одиовибратора триггер 21 будет переброшен в первоначальное состояние, а триггер 22 - в иовое, при ЭТОЛ1 ключ 18 будет вновь замкнут, а ключ 19 разомкнут - пороговые элементы будут подключены к источнику преобразуемого сигнала, а устройство сравнения выключено.

Включение пороговых элементов непосредственно после первого включения устройства сравнения необходимо вследствие того, что уже в самом начале преобразования сигнал разности может стать достаточно малым, например, когда преобразуемое напряжение окалсется приблизительно равным «весу одного старшего или сумме «весов двух-трех и т. д. старших разрядов кода. В таком случае пороговые элементы будут выключены и включится устройство сравнения, но в следующем такте сигнал разности может быть снова большим, поэтому иеобходимо повторное включение пороговых элементов.

Уравновешивание производится с помощью порогового элемента 8 до тех пор, пока в каком-то такте ни один из иорогОВых элемеитов не сработает, тогда триггер 20 измеиит свое состояние, включится устройство сравнения, будет зацрещено ирохождение соответствующего импульса такта и последующее иреобразоваиие будет производиться с помощью устройства сравнения. Если же при повторном включении пороговых элемеитов они в следующем такте ие сработают, триггер 20 изменит свое состояние и включит устройство сравнения до конца преобразования, так как схема И 24 не пропустит имиульс на запуск одповибратора 18.

Предмет изобретения

Преобразователь напряжения в цифровой код поразрядного уравиовещивания, содержащий устройство сравнения преобразуемого и компенсационного сигналов, преобразователь кода в напряжение, связанный с триггерами памяти, логическое устройство, распределитель снпхропотеициалов и генератор тактовых импульсов, отличающийся тем, что, с целью снижения перегрузки устройства сравнения и увеличения быстродействия, оно содержит две пороговых устройства с двумя схемами «ИЛИ, схему антисоВПадения, переключатель преобразуемого сигнала и схему запрета тактового импульса, причем входные цеии лороговых устройств включены параллельно ц инверсно по отношелию друг к другу, выходы одного из них и устройства сравнения соединены через одну схему «ИЛИ с логическим устройством, выходы тороговых элементов че рез другую схему «ИЛИ и схему антнсовпадения соединены с переключателем преобразусмоги сигнала, а з цель запуска распреде.(ителя синхропотенциалов включена схема запрета такто ого импульса, соединенная с выходов; генератора тактовых импульсов и выходом 1;ереключателя преобразуемого сиг--

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1967 |

|

SU191233A1 |

| Преобразователь напряжения в двоичный код | 1972 |

|

SU482005A1 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Двухканальный аналого-цифровой преобразователь | 1973 |

|

SU517997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД | 1972 |

|

SU340078A1 |

| Цифровой интегрирующий вольтметр | 1972 |

|

SU496500A1 |

Даты

1967-01-01—Публикация