Известны устройства контроля исправности оборудования блоков управления цифровых вычислительных машин, содержащие запоминающую матрицу для формирования контрольных последовательностей, узел анализа контрольных последовательностей, узел установки устройства в исходное состояние и узел выделения контрольных последовательностей.

Предлагаемое устройство отличается от известных тем, что в нем отдельные входные обмотки матрицы каждой контролируемой последовательности включены между рабочими выходами контролируемого устройства и через разделительные диоды клапанами, другие входы которых связаны с контролируемым устройством. Выходы матрицы соединены с единичными и нулевыми выходами триггеров узла анализа контрольных последовательностей и с клапанами формирования сигнала сбой. Другие выходы контролируемого устройства соединены через собирательные схемы с первыми входами клапанов, вторые входы которых подсоединены к соответствующей группе выходов контролируемого устройства. Выходы клапанов подключены к собирательной схеме формирования сигнала сбой. Это позволяет выделить ошибки любой кратности параллельно с вычислительным процессом.

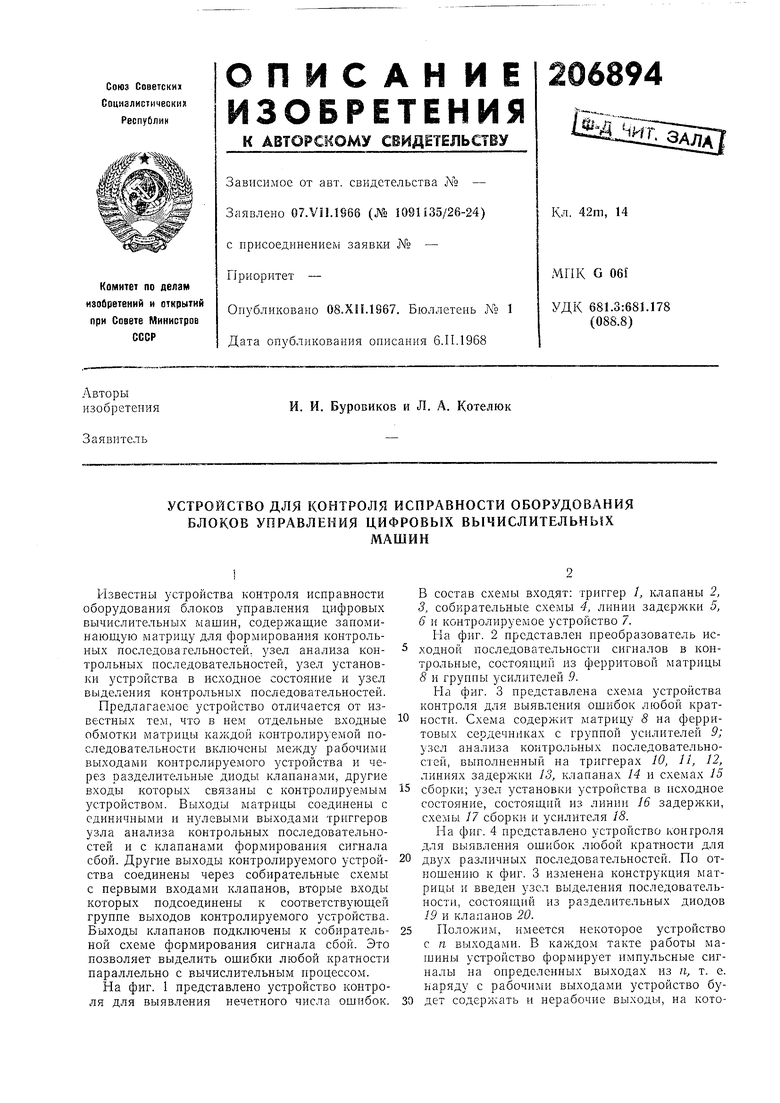

В состав схемы входят: триггер 1, клапаны 2, 3, собирательные схемы 4, линии задержки 5, 6 и контролируемое устройство 7.

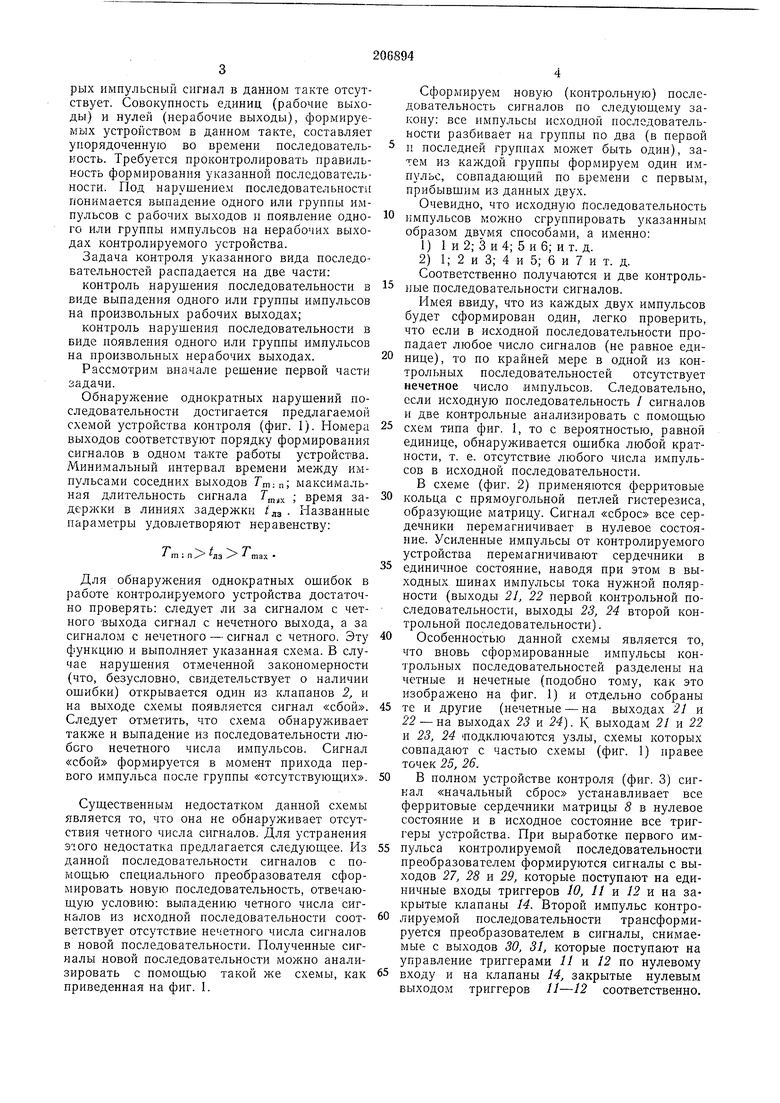

Па фиг. 2 представлен преобразователь исходной последовательности сигналов в контрольные, состоящий из ферритовой матрицы 8 и группы усилителей 9.

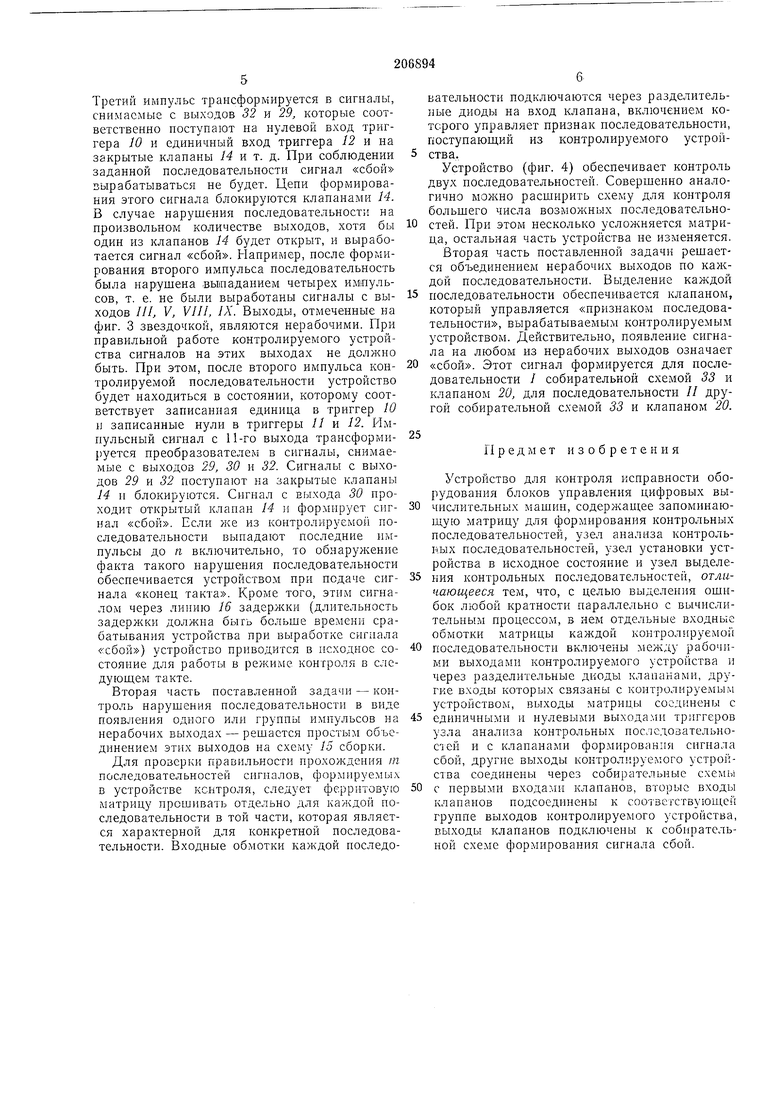

Па фиг. 3 представлена схема устройства контроля для выявления ошибок любой кратности. Схема содержит матрицу 8 на ферритовых сердечниках с группой усилителей 9; узел анализа контрольных последовательностей, выполненный па триггерах 10, 11, 12, линиях задерл ки 13, клапапах 14 и схемах 15

сборки; узел установки устройства в исходное состояние, состоящий из линии 16 задержки, схемы 17 сборки и усилителя 18.

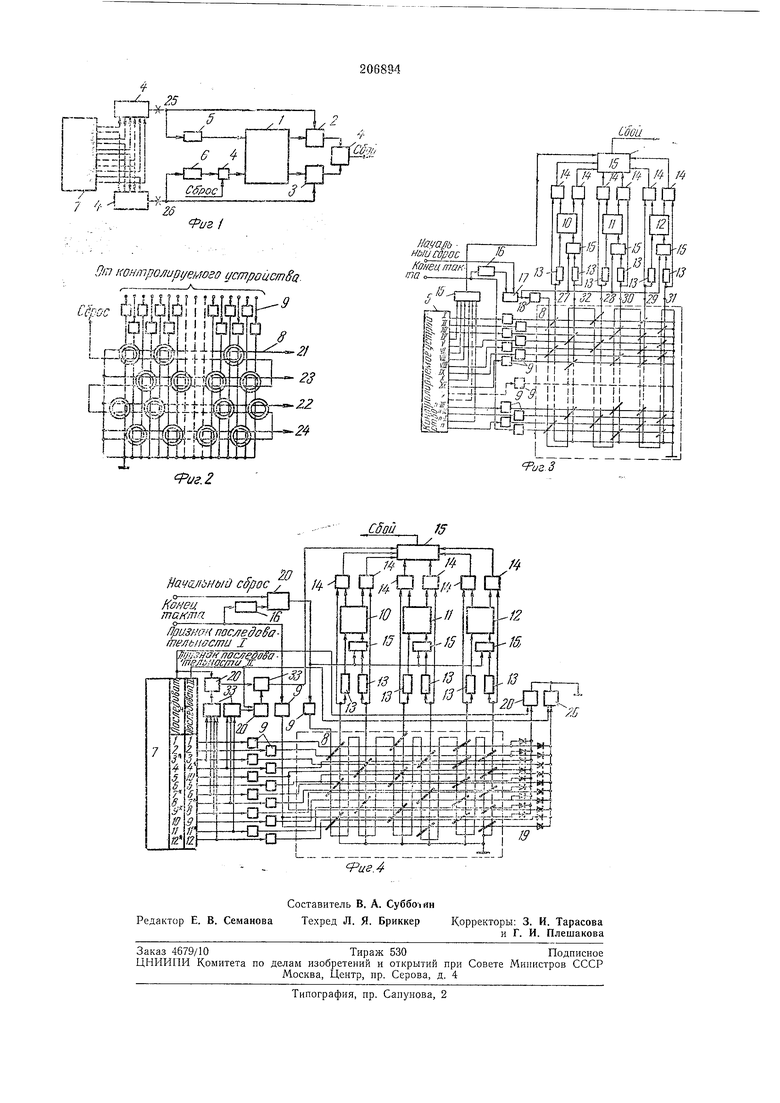

Па фиг. 4 представлено устройство контроля для выявления ошибок любой кратности для

двух различных последовательностей. По отношению к фиг. 3 изменена конструкция матрицы и введен узел выделения последовательности, состоящий из разделительных диодов 19 и клапанов 20.

Положим, имеется некоторое устройство с п выходами. В каждом такте работы машины устройство формирует импульсные сигналы па определенных выходах из п, т. е. наряду с рабочими выходами устройство бурых импульсный сигнал в данном такте отсутствует. Совокупность единиц (рабочие выходы) и нулей (нерабочие выходы), формируемых устройством в данном такте, составляет упорядоченную во времени последователььюсть. Требуется проконтролировать правильность формирования указанной последовательности. Под нарушением последовательности понимается выпадение одного или группы импульсов с рабочих выходов и появление одного или группы импульсов на нерабочих выходах контролируемого устройства. Задача контроля указанного вида последовательностей распадается на две части: контроль нарушения последовательности в виде выпадения одного или группы импульсов на произвольных рабочих выходах; контроль нарушения последовательности в виде появления одного или группы импульсов на произвольных нерабочих выходах. Рассмотрим вначале решение первой части задачи. Обнаружение однократных нарушений последовательности достигается предлагаемой схемой устройства контроля (фиг. 1). Номера выходов соответствуют порядку формирования сигналов в одном такте работы устройства. Минимальный интервал времени между импульсами соседних выходов 7m;n; максимальная длительность сигнала „„ ; время задержки в линиях задержки /дз Названные параметры удовлетворяют неравенству: m : п лз max Для обнаружения однократных ошибок в работе контролируемого устройства достаточно проверять: следует ли за сигналом с четного выхода сигнал с нечетного выхода, а за сигналом с нечетного - сигнал с четного. Эту функцию и выполняет указанная схема. В случае нарушения отмеченной закономерности (что, безусловно, свидетельствует о наличии ошибки) открывается один из клапанов 2, и на выходе схемы появляется сигнал «сбой. Следует отметить, что схема обнаруживает также и выпадение из последовательности любого нечетного числа импульсов. Сигнал «сбой формируется в момент прихода первого импульса после группы «отсутствующих. Существенным недостатком данной схемы является то, что она не обнаруживает отсутствия четного числа сигналов. Для устранения эюго недостатка предлагается следующее. Из данной последовательности сигналов с помощью специального преобразователя сформировать новую последовательность, отвечающую условию: выпадению четного числа сигналов из исходной последовательности соответствует отсутствие нечетного числа сигналов в новой последовательности. Полученные сигналы новой последовательности можно анализировать с помощью такой же схемы, как приведенная на фиг. 1. Сформируем новую (контрольную) последовательность сигналов по следующему закону: все импульсы исходной последовательности разбивает на группы по два (в первой п последней группах может быть один), затем из каждой группы формируем один импульс, совпадающий по времени с первым, прибывшим из данных двух. Очевидно, что исходную Последовательность импульсов можно сгруппировать указанным образом двумя способами, а именно: 1)1 и 2; 3 и 4; 5 и 6; и т. д. 2)1; 2 и 3; 4 и 5; 6 и 7 и т. д. Соответственно получаются и две контрольные последовательности сигналов. Имея ввиду, что из каждых двух импульсов будег сформирован один, легко проверить, что если в исходной последовательности пропадает любое число сигналов (не равное единице), то по крайней мере в одной из контрольных последовательностей отсутствует нечетное число импульсов. Следовательно, если исходную последовательность / сигналов и две контрольные анализировать с помощью схем типа фиг. I, то с вероятностью, равной единице, обнаруживается ошибка любой кратности, т. е. отсутствие любого числа импульсов в исходной последовательности. В схеме (фиг. 2) применяются ферритовые кольца с прямоугольной петлей гистерезиса, образующие матрицу. Сигнал «сброс все сердечники перемагничивает в нулевое состояние. Усиленные импульсы от контролируемого устройства перемагничивают сердечники в единичное состояние, наводя при этом в выходных шинах импульсы тока нужной полярности (выходы 21, 22 первой контрольной последовательности, выходы 23, 24 второй контрольной последовательности). Особенностью данной схемы является то, что вновь сформированные импульсы контрольных последовательностей разделены на четные и нечетные (подобно тому, как это изображено на фиг. 1) и отдельно собраны те и другие (нечетные - на выходах 21 и 22 - на выходах 23 и 24. К выхода.м 21 и 22 и 23, 24 «подключаются узлы, схемы которых совпадают с частью схемы (фиг. 1) правее точек 25, 26. В полном устройстве контроля (фиг. 3) сигнал «начальный сброс устанавливает все ферритовые сердечники матрицы 8 в нулевое состояние и в исходное состояние все триггеры устройства. При выработке первого импульса контролируемой последовательности преобразователем формируются сигналы с выходов 27, 28 и 29, которые поступают на единичные входы триггеров 10, 11 и 12 vi на закрытые клапаны 14. Второй импульс контролируемой последовательности трансформируется преобразователем в сигналы, снимаемые с выходов 30, 31, которые поступают на управление триггерами 11 и 12 по нулевому входу и на клапаны 14, закрытые нулевым выходом триггеров //-12 соответственно.

Третий импульс трансформируется в сигналы, снимаемые с выходов 32 и 29, которые соответственно поступают на нулевой вход триггера 10 и единичный вход триггера 12 и на закрытые клапаны 14 и т. д. При соблюдении заданной последовательности сигнал «сбой вырабатываться не будет. Цепи формирования этого сигнала блокируются клапанами 14. В случае нарушения последовательности на произвольном количестве выходов, хотя бы один из клапанов 14 будет открыт, и выработается сигнал «сбой. Например, после формирования второго импульса последовательность была нарушена выпаданием четырех импульсов, т. е. не были выработаны сигналы с выходов 111, V, V11I, IX. Выходы, отмеченные на фиг. 3 звездочкой, являются нерабочими. При правильной работе контролируемого устройства сигналов на этих выходах не должно быть. При этом, после второго импульса контролируемой последовательности устройство будет находиться в состоянии, которому соответствует записанная единица в триггер 10 и записанные нули в триггеры // и 12. Импульсный сигнал с 11-го выхода трансформируется преобразователем в сигналы, снимаемые с выходов 29, 30 и 32. Сигналы с выходов 29 и 32 поступают на закрытые клапаны 14 и блокируются. Сигнал с выхода 30 проходит открытый кланан 14 и формирует сигнал «сбой. Если же из контролируемой последовательности выпадают последние имнульсы до п включительно, то обнаружение факта такого нарушения последовательности обеспечивается устройством при подаче сигнала «конец такта. Кроме того, этим сигналом через линию 16 задержки {длительность задерл ки должна быть больше времени срабатывания устройства при выработке сигнала «сбой) устройство приводится в исходное состояние для работы в режиме контроля в следующем такте.

Вторая часть поставленной задачи - контроль нарушения последовательности в виде появления одного или группы импульсов на нерабочих выходах - решается простым объединением этих выходов на схему 15 сборки.

Для проверки правильности прохождения т последовательностей сигналов, формируемых в устройстве кснтроля, следует ферритовую матрицу прошивать отдельно для каждой последовательности в той части, которая является характерной для конкретной последовательности. Входные обмотки каждой последовательности подключаются через разделительные диоды на вход клапана, включением которого управляет признак последовательности, поступающий из контролируемого устройства.

Устройство (фиг. 4) обеспечивает контроль двух последовательностей. Совершенно аналогично можно расширить схему для контроля большего числа возможных иоследовательностей. При этом несколько усложняется матрица, остальная часть устройства не изменяется. Вторая часть поставленной задачи решается объединением нерабочих выходов по каждой последовательности. Выделение каждой

последовательности обеспечивается клапаном, который управляется «признаком последовательности, вырабатываемым контролируемым устройством. Действительно, появление сигнала на любом из нерабочих выходов означает

«сбой. Этот сигнал формируется для последовательности / собирательной схемой 33 и клапаном 20, для последовательности // другой собирательной схемой 33 и клапаном 20.

25

Предмет изобретения

Устройство для контроля исправности оборудования блоков управления цифровых вычислительных машин, содержащее запоминающую матрицу для формирования контрольных последовательностей, узел анализа контрольных последовательностей, узел установки устройства в исходное состояние и узел выделеыия контрольных последовательностей, отличающееся тем, что, с целью выделения ошибок любой кратности параллельно с вычислительным процессом, в нем отдельные входные обмотки матрицы каждой контролируемой

последовательности включены между рабочими выходами контролируемого устройства и через разделительные диоды клапанами, другие входы которых связаны с контролируемым устройством, выходы матрицы соединены е

единичными и нулевыми выхода.ми триггеров узла анализа контрольных последозательносчей и с клапанами формирования сигнала сбой, другие выходы контролируемого устройС1ва соединены через собирательные схемы

с первыми входами клапанов, вторые входы клапанов подсоединены к соответствующей группе выходов контролируемого устройства, выходы клапанов подключены к собирательной схеме формирования сигнала сбой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности чередования импульсов | 1986 |

|

SU1406757A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1793441A2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ С КОНТРОЛЕМ | 1992 |

|

RU2084015C1 |

| Способ контроля магнитных накопителей | 1982 |

|

SU1095232A1 |

| Устройство для контроля Р-кодов Фибоначчи | 1988 |

|

SU1533007A1 |

| СПОСОБ КОДИРОВАНИЯ | 2003 |

|

RU2256951C2 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для контроля матриц памяти | 1982 |

|

SU1027780A2 |

| Устройство для контроля информации по модулю три | 1976 |

|

SU634282A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ КОНТРОЛЬНОГО РАЗРЯДА ИНФОРМАЦИОННОГО СЛОВА ПРИ ИЗМЕНЕНИИ | 1969 |

|

SU235400A1 |

Даты

1968-01-01—Публикация