(61)1206785

(21)4725122/24

(22)28.07.89

(46)07.02,9.3. Бюл. № 5: ; , (72) В.0.Канцлер, Г.А.Никитин и В.Ф.Сватов -:; . . (56) Авторское свидетельство СССР Ms 1206785, кл. G 06 F 11/26, 1986. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ ... - / ; (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве встроенной системы контроля цифровых блоков в процессе экс- плуатаци и. Цель изобретения - повышение достоверности контроля. Достоверность повышена за счет расширения информативности контроля, что достигнуто введением в устройство, содержащее блок управления, генератор тестов, три регистра, два счетчика, дешифратор, генератор импульсов и элемент задержки, четвертого регистра, группы элементов НЕ и группы элементов ИЛИ. 2 ил.7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1679487A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для тестового контроля электромеханических блоков | 1982 |

|

SU1151973A1 |

| Устройство для контроля цифровых систем | 1983 |

|

SU1130871A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

Изобретение относится к автоматике и вычислительной технике и может .быть использовано в качестве встроенной системы контроля цифровых блоков в процессе эксплуатации.. . .... . ; /. . .

Известно устройство для контроля цифровых блоков, содержащее блок управления, генератор тестов, .блок предварительной обработки информации, элемент ИЛИ, счетчик и Дешифратор. Контроль осуществляется методом счета единичных импульсов на выходе контролируемого блока за интервал времени контроля с последующим сравнением подсчитанного суммарного числа импульсов с заранее известным для данного исправного цифрового блока.. .. . .

Недостатком устройства является снижение достоверности результатов контроля в случае наличия в выходных наборах импульсов сбоев.

Известны средства обнаружения одиночных ошибок путём подсчета числа единиц в принимаемых группах (выходных

наборах) при условии кодирования этих наборов по коду 2 из 5 или в общем случае с добавлением контрольного бита четности 6 последующим анализом выходных наборов (контроль по модулю 2).

Недостаток этих схем - они реагируют на любое нечетное количество ошибок и не реагируют, если количество ошибок четное, или наоборот, если правило контроля принято противоположным; Вследствие этого кратные сбои могут быть не зафиксированы, что снижает достоверность контроля. С увеличением модуля непропорционально возрастает количество дрполнйтельно- го:оборудования и значительно возрастает количество дополнительного оборудова- ,ния и значительно усложняются схемы контроля.

Известны устройства контроля, фиксирующие сбои в выходных наборах путем анализа нестабильности результатов контроля, при этом каждый результат предшествующего цикла опроса должен быть запомнен и сохранен до окончания текущеел

с

ч ю ы

4 4

Ю

го цикла контроля с последующим их сравнением (двойной счет).

Недостатком этих устройств является необходимость повторного полного цикла контроля и, как следствие, невозможность обнаружения систематических сбоев.

Наиболее близким к предлагаемому является устройство для контроля цифровых блоков, содержащее блок управления, генератор тестов, три регистра, два счетчика, -дешифратор, генератор импульсов и элемент задержки. Контроль осуществляется методом счета единичных импульсов с. последующим сравнением их суммарного числа с заранее известным, определяемым функцией, реализуемой правильно функционирующим контролируемым блоком. Ранее указанный недостаток частично устраняется благодаря введению в устройство контроля схемы регистрации сбоев, что расширяет информативность результатов контроля за счет уточнения причин изменения состояния контролируемого блока. Анализ таблицы и схемы устройства показывает, что достоверное решение о состоянии контролируемого цифрового блока :будет принято только в первом и во втором случаях, когда в результате контроля будет получен сигнал Исправно или Неисправно и сигнал Сбой отсутствует. Во всех других случаях достоверность принятого ре- . шения снижается из-за -ограниченной информационной глубины контроля.

Под информационной глубиной контроля будем понимать способность регистрировать такие типы ошибок, как одиночные и групповые сбои, причем различной структуры: ошибки типа Ложный 0 (1 - 0), Ложная 1 (0 1) ил.и оба типа ошибок ().

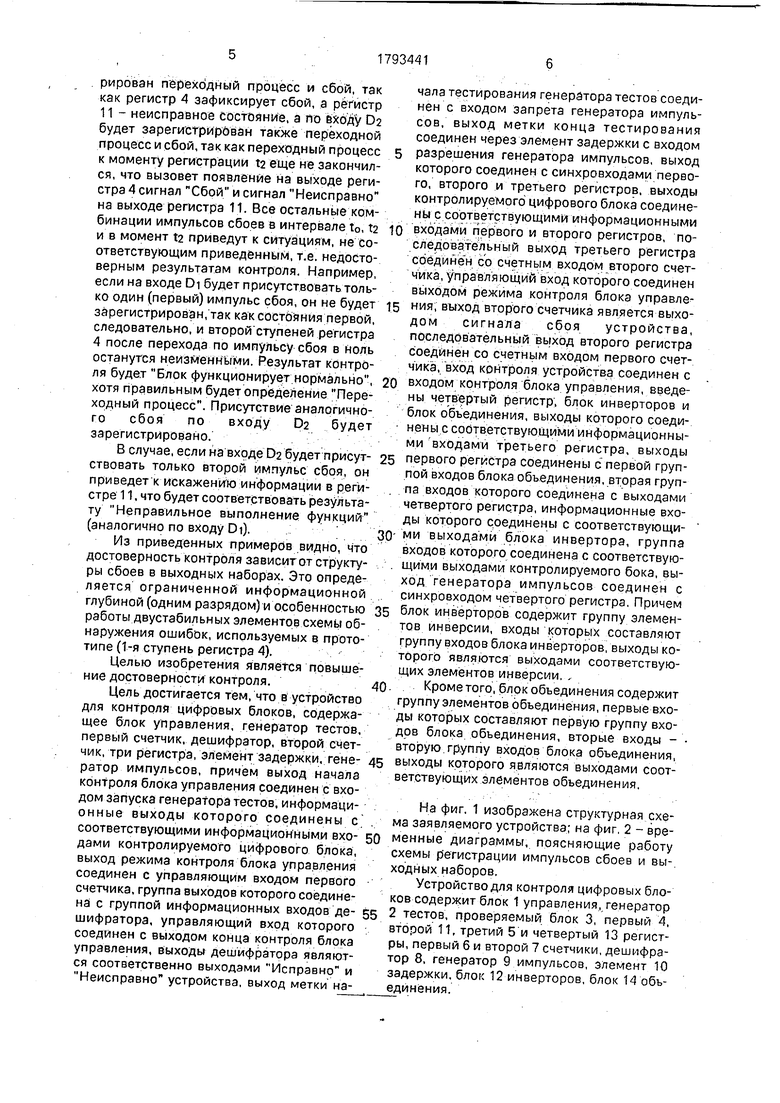

Анализ схемы устройства показывает, что сообразно логике работы в качестве регистров 4, 5 и 11 (фиг. 1) могут быть применены регистры следующих типов. В качестве регистра 11 применен сдвигающий регистр с динамическим управлением режимами: параллельной записью выходных наборов и последовательным их считыванием по перепаду каждого синхроимпульса с выхода генератора 9 импульсов.

Схема регистрации сбоев включает регистры 4 и 5 и представляет набор трехступенчатых триггеров в каждом разряде, причем регистр 4 хранения выполнен на двухступенчатой MS-структуре, а последо- вательно- параллельный регистр 5 выполняет функций синхронного фиксатора. Особенность прототипа в том, что первая ступень МЗ-триггеря представляет собой статический D-триггер, тактируемый синхроимпульсами от генератора 9 (триггер - защелку), вторая ступень - динамический D-триггер хранения, тактируемый теми же импульсами. Синхронный фиксатор. - регистр 5 аналогичен регистру 11.

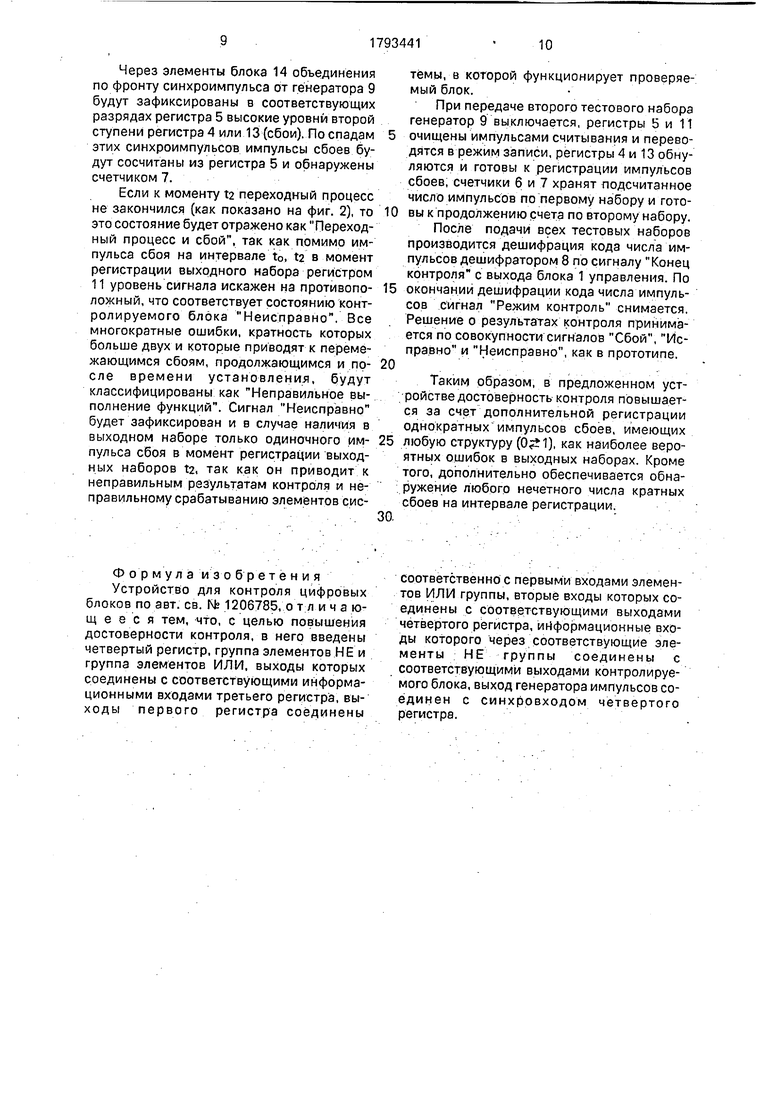

На фиг. 2 представлены временные ди- .аграммы, поясняющие логику работы схемы обнаружения ошибок в выходных наборах для двух возможных случаев - когда в рассматриваемрм такте контроля происходит смена уровней с низкого на высокий (Di) и наоборот (О2). Смена уровней происходит в интервале to, ti, определяемом временем формирования входных наборов. Интервал

ti, ta определяется временем установления переходных процессов. С началом формирования входных наборов регистр 4 предварительно обнуляется и на выходах первой и второй ступеней ((Нет и Qa ст) устанавливается высокий уровень. При смене уровней на информационных входах D регистров 4 и 11 могут возникать импульсы сбоев, образующихся в результате переходных процессов. Если переходные процессы не

закончились моменту регистрации выходных наборов 12, это рассматривается как неисправное состояние блока. Рассмотрим их влияние на достоверность контроля, условившись, что срабатывание первой ступени регистра 4 происходит по

отрицательным перепадам в интервале to,

ta; перенос .последнего состояния первой

ступени во вторую регистра 4 с фиксацией

этого состояния в регистре 5, а также запись

выходных наборов в регистр 11 происходят по переднему фронту синхроимпульсов от генератора 9 (момент t2); считывание информации из регистров 5 и 11 происходит по заднему фронту этих синхроимпульсов (моменты ta).

Из рассмотрения временных диаграмм видно, что регистрация импульсов сбоев (изменение состояния второй ступени регистра 4) происходит всякий раз, когда

независимо от их структуры количество отрицательных перепадов на интервале to, ta будет четное, т.е. 2,4,6,.,., что и указывается в прототипе как необходимое условие реги-. страции. При этом если искажения имеют

0 характер разрывов в высоком уровне (1 0), сбой будет зарегистрирован, если их количество составляет любое четное число. Если искажения имеют характер иголок на низком уровне (0- ), регистрация

5 возможна лишь в случае, если будет нечетное число сбоев, так как первая ступень регистра 4 отследит также переход состояния из высокого в низкое по тест-набору (Da). Поэтому по входу DI будет зарегистрирован переходный процесс и сбой, так как регистр А зафиксирует сбой, а регистр 11 - неисправное состояние, а по входу D2 будет зарегистрирован также переходной процесс и сбой, так как переходный процесс к моменту регистрации t2 еще не закончился, что вызовет появление на выходе регистра 4 сигнал Сбой и сигнал Неисправно на выходе регистра 11. Все остальные комбинации импульсов сбоев в интервале t0, t2 и в момент t2 приведут к ситуациям, не соответствующим приведенным, т.е. недостоверным результатам контроля. Например, если на входе DI будет присутствовать только один (первый) импульс сбоя, он не будет зарегистрирован/так как состояния первой, следовательно, и второй ступеней регистра 4 после перехода по импульсу сбоя в ноль останутся неизменными. Результат контроля будет Блок функционирует.нормально, хотя правильным будет определение Переходный процесс. Присутствие аналогичного сбоя по входу D2 будет зарегистрировано.

В случае, если на входе D2 будет присут- ствовать только второй импульс сбоя, он приведет к искажению информации в регистре 11, что будет соответствовать результату Неправильное выполнение функций (аналогично по входу DI). .

Из приведенных примеров видно, что достоверность контроля зависитот структуры сбоев в выходных наборах. Это определяется ограниченной информационной глубиной (одним разрядом) и особенностью работы двустабильных элементов схемы обнаружения ошибок, используемых в прототипе (1-я ступень регистра 4).

Целью изобретения является повышение достоверности контроля.

Цель достигается тем, что в устройство для контроля цифровых блоков, содержащее блок управления, генератор тестов, первый счетчик, дешифратор, второй счетчик, три регистра, элемент задержки, гене- ратор импульсов, причем выход начала контроля блока управления соединен с входом запуска генератора тестов, информаци- онные выходы которого соединены с соответствующими информационными вхо- дами контролируемого цифрового блока, выход режима контроля блока управления соединен с управляющим входом первого счетчика, группа выходов которого соединена с группой информационных входов де- шифратора, управляющий вход которого соединен с выходом конца контроля блока управления, выходы дешифратора являются соответственно выходами Исправно и Неисправно устройства, выход метки начала тестирования генератора тестов соединен с входом запрета генератора импульсов, выход метки конца тестирования соединен через элемент задержки с входом разрешения генератора импульсов, выход которого соединен с синхровходами первого, второго и третьего регистров, выходы контролируемого цифрового блока соединены с соответствующими информационными входами первого и второго регистров, последовательный выход третьего регистра соединен со счетным входом второго счетчика, управляющий вход которого соединен выходом режима контроля блока управле ния, выход второго счетчика является выходом сигнала сбоя устройства, последовательный выход второго регистра соединен со счетным входом первого счетчика, вход контроля устройства соединен с входом контроля блока управления, введены четвертый регистр;, блок инверторов и блок объединения, выходы которого соединены с соответствующими информационными входами третьего регистра, выходы первого регистра соединены с первой группой входов блока объединения, вторая группа входов которого соединена с выходами четвертого регистра, информационные входы которого соединены с соответствующими выходами блока инвертора, группа входов которого соединена с соответствующими выходами контролируемого бока, выход генератора импульсов соединен с синхровходом четвертого регистра, Причем блок инверторов содержит группу элементов инверсии, входы которых составляют группу входов блока инверторов, выходы которого являются выходами соответствующих элементов инверсии.,

Кроме того, блок объединения содержит группу элементов объединения, первые входы которых составляют первую группу входов блока объединения, вторые входы - вторую.группу входов блока объединения, выходы которого являются выходами соответствующих элементов объединения.

На фиг. 1 изображена структурная схема заявляемого устройства; на фиг, 2 - временные диаграммы, поясняющие работу схемы регистрации импульсов сбоев и вы-, ходных наборов.

Устройство для контроля цифровых блоков содержит блок 1 управления,генератор 2 тестов, проверяемый блок 3, первый 4, второй 11, третий 5 и четвертый 13 регистры, первый 6 и второй 7 счетчики, дешифратор 8, генератор 9 импульсов, элемент 10 задержки, блок 12 инверторов, блок 14 объединения.

Блок 1 управления выполнен как в прототипе. Блок 12 инверторов содержит п элементов инверсии НЕ, где п - число выходов в контролируемом блоке. Блок 14 объединения содержит также п двухвходовых элементов объединения ИЛИ.

Первый выход 15 генератора 2 тестов является выходом метки начала тестирования t0, совпадающей с началом контроля и определяющей момент выключения генера-тора 9 импульсов. Второй выход 16 генератора 2 тестов - это выход метки конца тестирования ti, определяющей момент окончания формирования наборов генератором 2 тестов. Выход 17 элементов 10 задержки - это выход метки включения генератора 9 импульсов t2. Выход 18 генератора 9 импульсов - выход импульсов, по которым осуществляется динамическое управление регистрами: по фронту первого импульса в момент t2 осуществляется считывание из регистров 4 и 13 с одновременной записью в регистры 5 и 11, а по спадам импульсов - синхронный сдвиг информации в регистрах 5 и 11 (тз), начиная со старшего разряда.

Устройство работает следующим образом.

При включении контролируемого цифрового блока 3 и устройства все элементы в них устанавливаются в исходное состояние (цепи установки в исходное состояние не показаны). После этого на вход блока 1 управления поступает сигнал Контроль, после чего на его третьем выходе на все время контроля появляется сигнал Режим контроль, который разрешает работу счетчиков 6 и 7. Одновременно на первом выходе блока 1 управления появляется сигнал Начало контроля, который поступает на вход генератора 2 тестов (момент времени to, фиг. 2). По этому сигналу генератор 2 начинает последовательно вырабатывать наборы сигналов; число которых заранее определено для контролируемого блока. По началу каждого тестового набора с второго выхода генератора 2 тестов появляется сигнал выключения генератора 9 импульсов (метка 15 в момент t0, фиг, 1,2). По окончании передачи каждого тестового набора в момент времени ti на первом выходе генератора 2 появляется сигнал 16 (метка конца тестирования), который через элемент 10 задержки в момент времени т.2 включает генератор 9 импульсов.

По каждому тестовому набору в интервале тестирования (to, ti) на выходах контро--лируемого блока 3 появляются соответствующие им выходные наборы, размерность каждого из которых опрёдел яется числом контролируемых выходов п. Регистрация .и анализ выходных наборов производятся по окончании их формирования к моменту времени ti и с учетом времени установления переходных процессов(tyCr) элементом задержки, т.е. начиная с момента времени t2, В моменты t2 генератор 9 начинает вырабатывать серии из п импульсов, по фронту которых осуществляется запись выходных наборов в регистр 11, а по спаду каждого импульса - последовательное считывание из регистра 11 и подсчет числа импульсов счетчиком 6 и дешифрация этого числа дешифратором 8.

Регистрация импульсов сбоев производится следующим образом. Анализ возможных информационных сигналов (выходных наборов) на входах DI и D2 регистра 4 (фиг. 2) показывает, что потери информации о

сбоях в схеме прототипа отсутствуют, если на интервале регистрации импульсов сбоев (to, t2) будет четное число отрицательных перепадов логических уровней. В то же время сигналы на входах DI и D2 взаимно

инверсны (Di 02), а их структура отражает все возможные комбинации сбоев ня интервале регистрации (случаи, кратные приведенным, приводят к тем же результатам). Это обстоятельство позволяет сделать вывод о том, что если дополнить любой сигнал выходного набора его инверсией, то становится возможным обнаружить сбой любой .структуры (), так как нечетное число отрицательных перепадов дополняется до

четного. Таким образом, сформировав пара- фазный сигнал выходного набора и проанализировав его в дополнительном канале, аналогичном основному каналу прототипа, можно обеспечить регистрацию сбоев без

потери информации. Результаты контроля обоих каналов целесообразно объединить на входах общего фиксатора состояний каналов для последующего анализа,

Дополнительный канал, аналогичный основному, реализован на регистре 13, на информационные входы которого подаются инверсии выходных наборов через блок 12 ; инверторов. Поэтому в соответствии с рассмотренными временными диаграммами на одновременных выходах регистров 4 и 13 в моменты t2 из второй ступени регистров считываются пары сигналов с уровнями 0,1 для нечетного числа импульсов сбоев на ин5 тервале t0, t2 и структуре сбоев 1 0 или с уровнями 1,0 для четного числа импульсов сбоев. При смене структуры сбоев на 0 1 пары сигналов будут 1,0 или 0,1 соответственно.

Через элементы блока 14 объединения по фронту синхроимпульса от генератора 9 будут зафиксированы в соответствующих разрядах регистра 5 высокие уровни второй ступени регистра 4 или 13 (сбои). По спадам этих синхроимпульсов импульсы сбоев будут сосчитаны из регистра 5 и обнаружены счетчиком 7.

Если к моменту t2 переходный процесс не закончился (как показано на фиг. 2), то это состояние будет отражено как Переходный процесс и сбой, так как помимо импульса сбоя на интервале to, t2 в момент регистрации выходного набора регистром 11 уровень сигнала искажен на противоположный, что соответствует состоянию контролируемого блока Неисправно. Все многократные ошибки, кратность которых больше двух и которые приводят к перемежающимся сбоям, продолжающимся и после времени установления, будут классифицированы как Неправильное выполнение функций. Сигнал Неисправно будет зафиксирован и в случае наличия в выходном наборе только одиночного импульса сбоя в момент регистрации выходных наборов t2, так как он приводит к неправильным результатам контроля и неправильному срабатыванию элементов сисФ о р м у л а и з о б р ет е н и я Устройство для контроля цифровых блоков по авт. св. № 1206785, о тли ч а ю- щ е е с я тем, что, с целью повышения достоверности контроля, в него введены четвертый регистр, группа элементов НЕ и группа элементов ИЛИ, выходы которых соединены с соответствующими информационными входами третьего регистра, выходы первого регистра соединены

темы, в которой функционирует проверяемый блок.

При передаче второго тестового набора генератор 9 выключается, регистры 5 и 11

очищены импульсами считывания и переводятся в режим записи, регистры 4 и 13 обнуляются и готовы к регистрации импульсов сбоев, счетчики 6 и 7 хранят подсчитанное число импульсов по первому набору и готовы к продолжению счета по второму набору. После подачи всех тестовых наборов производится дешифрация кода числа импульсов дешифратором 8 по сигналу Конец контроля с выхода блока 1 управления. По

окончаний дешифрации кода числа импульсов сигнал Режим контроль снимается. Решение о результатах контроля принимается по совокупности сигналов Сбой, Исправно и Неисправно, как в прототипе.

. . . :

Таким образом, в предложенном устройстве достоверность контроля повышается за счет дополнительной регистрации однократных импульсов сбоев, имеющих

любую структуру (), как наиболее вероятных ошибок в выходных наборах. Кроме того, дополнительно обеспечивается обнаружение любого нечетного числа кратных сбоев на интервале регистрации.

соответственно с первыми входами элементов ИЛИ группы, вторые входы которых соединены с соответствующими выходами четвертого регистра, информационные входы которого через соответствующие элементы НЕ группы соединены с соответствующими выходами контролируемого блока, выход генератора импульсов со- ёдинен с синхррвходом четвертого регистра.

16

1793441

flour 9l i e

i;

п.

. фиг. 1 i 2 ..

j u--fe..---ЛШ--. 1П ,t

п.

П

Авторы

Даты

1993-02-07—Публикация

1989-07-28—Подача