| Изобретение относится к вычислитель- | ной технике и может быть использовано при (построении отказоустойчивых многопро- цессорных вычислительных систем (ВС). i Цель изобретения - повышение досто- |верности контроля функционирования системы путем организации приоритетного контроля наименее надежных процессоров.

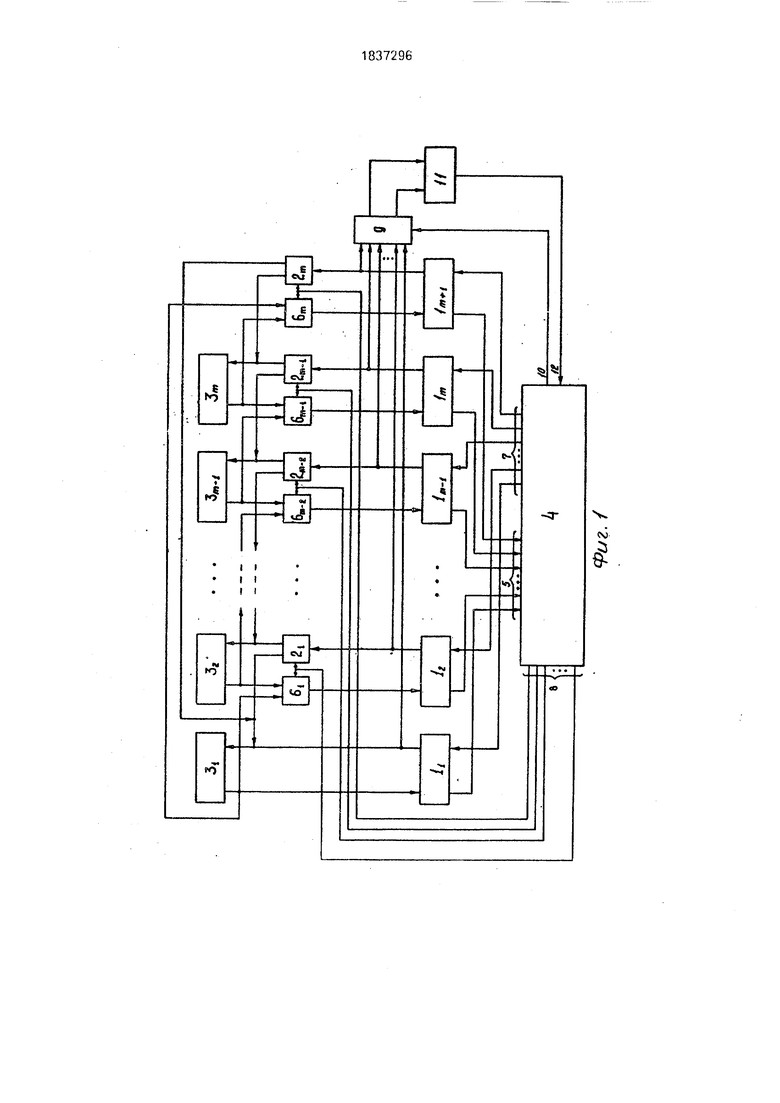

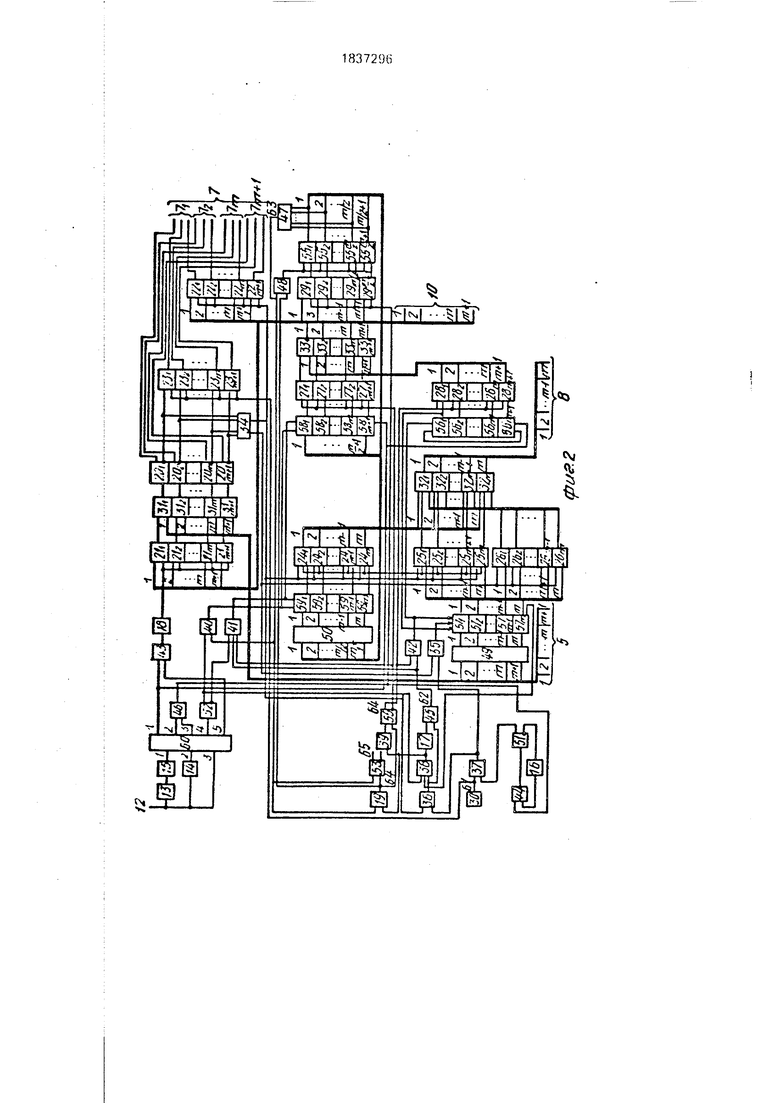

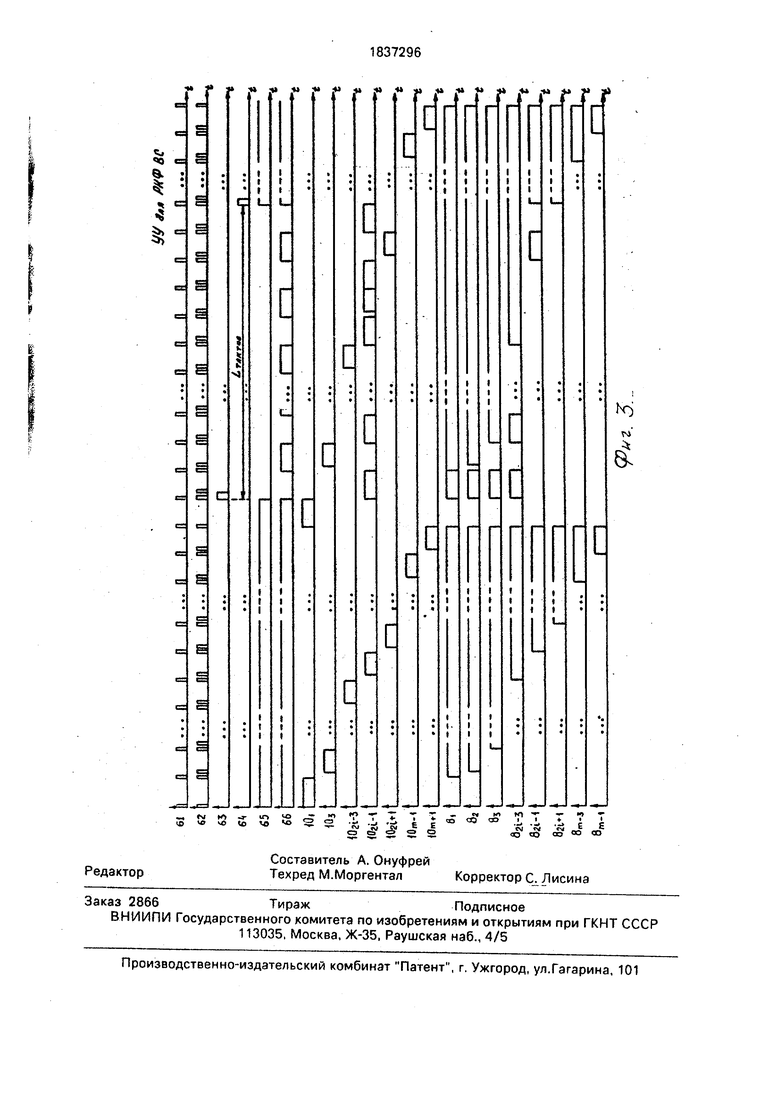

На фиг.1 представлена схема резервированной вычислительной системы; на фиг.2 - схема устройства управления; на фиг.З - временные диаграммы работы устройства управления.

Резервированная ВС (фиг.1) содержит ;1i, .... 1m, lm-и резервируемые процессоры, коммутаторы 2i 2m вывода информации, модули памяти 3i,.... 3m, устройство 4

управления, первая группа 5i5m, 5т+1

информационных входов устройства управления, коммутаторы 6i, ..., 6m ввода информации, первая группа 7i7m, 7m+i и

(вторая группа 8i, ..., 8m выходов устройства управления, коммутатор 9, выход 10 элементов третьей 33 группы ИЛИ, схему сравнения 11, выход 12 схемы сравнения.

Устройство управления (фиг.2) содержит первый 13, второй 14, третий 15, четвертый 16, пятый 17, шестой 18 элементы задержки, счетчик 19 тактов, регистр 20 готовности процессоров, первую 21121m,

21m+i, вторую 22i 22m, 22т+1, третью

23i23m, 23т+1, четвертую 24i24m,

пятую 25i 25m, шестую 26i 26m,

седьмую 27i, .... 27m, 27m+i, восьмую 28i,

.... 28m, 28nvM, девятую 29i 29m/2,

29m/2+i группы элементов И, генератор 30

тактовых импульсов, первую 311 31m,

31m+i, вторую 32i 32m, третью 33i

33m, ЗЗт+1 группы элементов ИЛИ, первый 34, второй 35. третий 36, четвертый 37, пятый 38, шестой 39, седьмой 40, восьмой 41, девятый 42 элементы И, первый 43, второй 44, третий 45, четвертый 46, пятый 47, шестой 48 элементы ИЛИ, первый 49 и второй 50 шифраторы согласования, первый 51, второй 52, третий 53 и четвертый 54 триггеры, группу 55i55m/2, 55т/2+1 счетчиков, перin

00

вый 56, второй 57, третий 58 и четвертый 59 регистры сдвига, дешифратор 60.

На временных диаграммах (фиг.З) обозначено: 61 - сигнал на выходе генератора 30, 62 - сигнал на выходе третьего 45 элемента ИЛИ, 63 - сигнал на выходе пятого 47 элемента ИЛИ, 64 - сигнал на выходе переполнения счетчика 19 тактов, 65 - сигнал на прямом выходе третьего 53 триггера, 66 - сигнал на прямом выходе четвертого 54

триггера, 10i, Юз1021-3, 1021-1, 1021+1, ..,.,

10m-i, tOm+1 - сигналы управления коммутатором 9, 8i, 82, 83 821-3, 821-3, 821+1, ....

8m-3, 8m-i - сигналы управления соответствующими коммутаторами ввода 2 и коммутаторами вывода 6 информации.

Общий принцип функционирования вычислительной системы состоит в следующем. Каждый резервируемый процессор через соответствующие коммутаторы ввода и вывода подключается к одному из модулей памяти. В исходном состоянии все процессоры исправны. Организован внешний контроль работы процессоров - в каждом такте назначается пара проверяемых процессоров, которые подключаются к одному модулю памяти и выполняют одни и те же инструкции над одинаковыми исходными данными.

Результаты работы назначений пары процессоров сравниваются. Если произошло совпадение результатов работы проверяемых процессоров, то на следующий такт назначается новая пара процессоров. Если произошло несравнение результатов работы пары проверяемых процессоров, то на следующий такт для проверки назначается эта же пара процессоров. Если при повторном счете произошло совпадение результатов работы, то принимается решение, что в предыдущем такте произошел сбой и на следующий такт назначается новая пара процессоров.

Если при повторном счете опять произошло несравнение результатов работы пары проверяемых процессоров, принимается решение о неисправности одного из процессоров и на основе анализа работы процессоров в следующем такте выявляется неисправный процессор.

Выбор пары процессоров для внешнего контроля происходит с учетом надежности работы процессоров: для каждой пары параллельно работающих процессоров подсчитывается количество сбоев, при достижении числа сбоев заданного порога К за определенное количество L тактов работы ВС, назначается приоритетный контроль той пары процессоров, число сбоев

которой первым достигло порогового значения.

Если ВС работает без сбоев, не превышен порог К за L тактов работы, то происхо- 5 дит последовательное (неприоритетное) назначение пар процессоров для внешнего контроля за цикл работы ВС, равный, в данном случае, (т/2+1) тактам, каждый процессор будет один раз проверен внешним

Ю контролем.

Если назначен приоритетный контроль, то выбранная пара процессоров назначается для внешнего контроля, через каждый такт работы ВС, в оставшихся тактах осуице15 ствляется последовательный контроль остальных пар процессоров. В приоритетном режиме за цикл работы ВС, равный, в данном случае, (т+2) тактам, выбранная пара процессоров будет проверена внешним

20 контролем (т/2+2) раз, а остальные процессоры - один раз.

Приоритетный контроль может быть отменен, если в последующие L тактов работы число сбоев ни для одной из пар процессо25 ров не достигло порога К. В этом случае возобновится неприоритетный (последовательный) контроль, всех пар процессоров. Приоритетный контроль может быть назначен вновь или продолжен без его отмены с

30 той же или любой другой парой процессоров, для которой число сбоев превысило порог К за L тактов работы.

При обнаружении неисправного процессора внешний контроль прекращается,

35 неисправный процессор восстанавливается, а исправные m процессоров на это время подключаются к соответствующим m модулям памяти. Решение задачи продолжается без снижения производительности систе40 мы, контроль работоспособности системы осуществляется только встроенными средствами контроля процессоров. После восстановления отказавшего процессора, система вновь функционирует с резервным

45 процессором и использованием внешнего контроля,

Заданный уровень достоверности результатов работы системы обеспечивается выбором длительности такта в цикле конт50 роля. Значение следует выбирать таким, чтобы в течение допустимого времени перерыва в работе отказавший процессор был локализован и перекоммутирован с резервным процессором.

55 Резервированная вычислительная система работает следующим образом. В исходном состоянии все процессоры 1i1m,

1т+1 исправны, во всех разрядах регистра 20 готовности процессоров записаны нули, триггеры 51, 52, 53, 54 находятся в единичном состоянии, во всех разрядах счетчиков группы 55, счетчика 19, регистров 57, 58, 59 .записаны нули, в регистре 56 записан код 100...0. Сигналы высокого уровня с инверсных выходов регистра 20 разрешают про- хождение через соответствующие элементы

И 23123m, 23т+1 на выходы 7i7m, 7т+1

устройства управления сигналов пуска соответствующих процессоров от генератора 30. В каждом такте работы формируются управляющие коды: код для подключения процессоров к модулям памяти (на выходе 8 устройства управления) и код для коммутации выходов пары параллельно работающих процессоров на входы схемы 11 сравнения (на выходе 10 устройства управления).

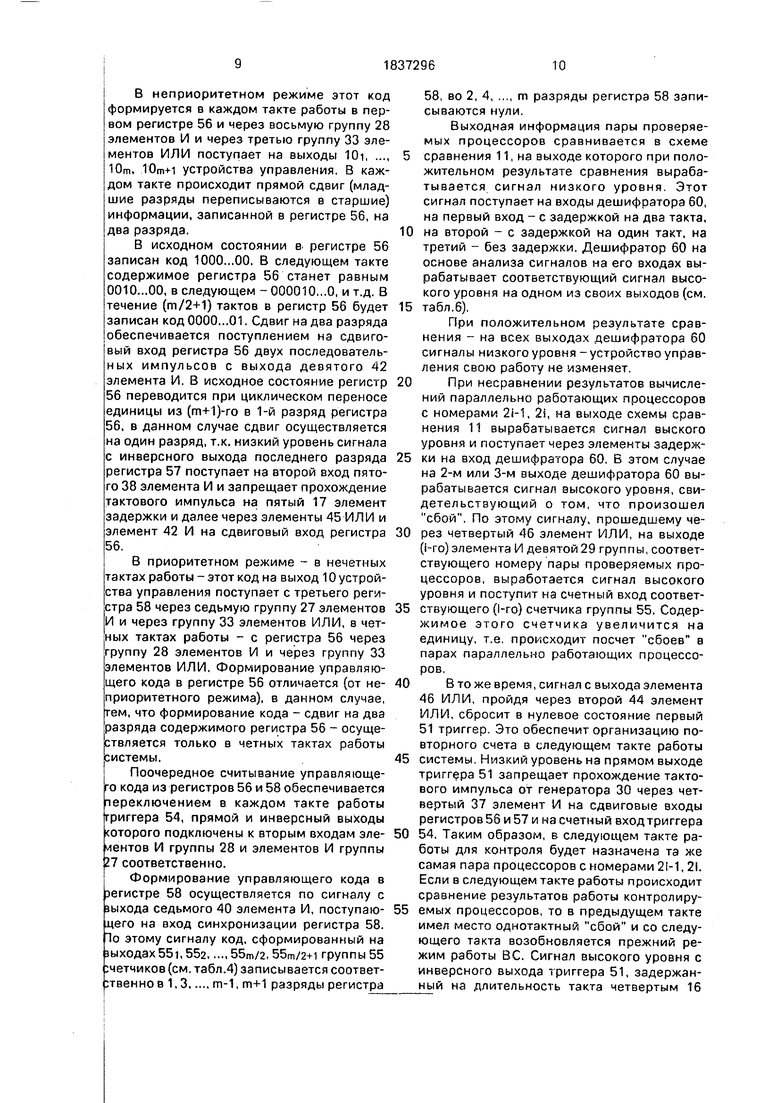

Таким образом, осуществляется последовательный (неприоритетный) контроль всех пар процессоров путем их поочеред- ной параллельной работы и последующего сравнения результатов работы. Порядок назначения пар параллельно работающих процессоров в режиме неприоритетного контроля показан в табл.1.

Организация приоритетного контроля зыбранной пары процессоров происходит следующим образом: третий 53 триггер пе- эеводится в нулевое состояние и высокий потенциал с инверсного выхода этого триг- ера разрешает прохождение тактовых импульсов с выхода пятого 38 элемента И через шестой 39 элемент И на счетный вход четвертого 54 триггера, обеспечивая тем са- лым переключение триггера 54 в каждом акте работы системы. Нулевое состояние риггера 54 обеспечивает контроль (параллельную работу) выбранной пары процессо- ов через каждый такт работы системы. Единичное состояние триггера 54 обеспечи- мает последовательный (поочередный) кон- гроль остальных пар процессоров.

Режим приоритетного контроля может начаться в любом такте контроля, но для определенности и удобства описания при- нем, что он начался в нечетном такте работы системы. Помня о том, что данный режим ног начаться и в четном такте работы. Порядок назначения параллельно работающих процессоров для неприоритетного контроля и приоритетного контроля пары процессоров с номерами (21-1, 21) показан табл.2.

Для приоритетного контроля выбирается та пара процессоров, где число сбоев достигло порога К за L тактов работы системы. Выбор такой пары процессоров происходит следующим образом. Каждой паре гараллельно работающих процессоров поставлены в соответствие счетчик из группы

55 счетчиков. В каждом такте работы на выходах третьей группы 33 элементов ИЛИ формируется позиционный код для коммутации выходов контролируемой пары процессоров на входы схемы 11 сравнения. Наличие высокого уровня на одном из выходов элементов ИЛИ 33i33m, 33m+i однозначно определяет номер пары процессоров, контролирующихся в данном такте. По разрешающему сигналу высокого уровня, подключенному к вторым входам элементов 29 И девятой группы и свидетельствующему о том, что в одном из процессоров контролируемой пары произошел сбой, позиционный код с выходов элементов ИЛИЗЗт, ЗЗзЗЗт-1 через соответствующие элементы И 29i, 29а 29т/2,

29т/2+1 поступает на соответствующие счетные входы счетчиков 55i, 552 55m/2,

5m/2+1.

Содержимое счетчика, соответствующего паре процессоров, при параллельной работе которых произошел сбой, увеличится на единицу. Подсчет числа сбоев в счетчиках группы 55 будет продолжаться до тех пор, пока какой-либо из счетчиков не выдаст сигнал переполнения, который свидетельствует о том, что число сбоев для соответствующей пары процессоров достигло

критерия К, К 2п;п 2, 3, 4разрядность

счетчиков группы 55 выбирается в зависимости от заданного критерия К. Счетчик 19 реализует подсчет L тактов работы системы, на его счетный вход через четвертый 37, третий 36 и пятый 38 элементы И поступают тактовые импульсы от генератора 30.

L 2Л, п 2, 3, 4 разрядность счетчика

19 выбирается в зависимости от заданного критерия L, причем должно выполняться неравенство К L.

Любой из сигналов переполнения с выходов счетчиков 55 группы поступает через пятый 47 элемент ИЛИ на вход установки в ноль счетчика 19 и через шестой 48 элемент ИЛИ на входы установки в ноль счетчиков группы 55, а также на вход установки в ноль триггера 53. Это обеспечивает перевод названных счетчиков в исходное состояние и назначение режима приоритетного контроля, так как выполнен критерий - К сбоев за L тактов работы системы. Сигнал переполнения с выхода счетчика 19 поступает на входы установки в единичное состояние триггеров 53 и 54, а также через шестой элемент 48 ИЛИ на входы установки в ноль счетчиков группы 55, обеспечивая этим отмену приоритетного режима контроля при отсутствии К сбоев за L последующих тактов работы системы.

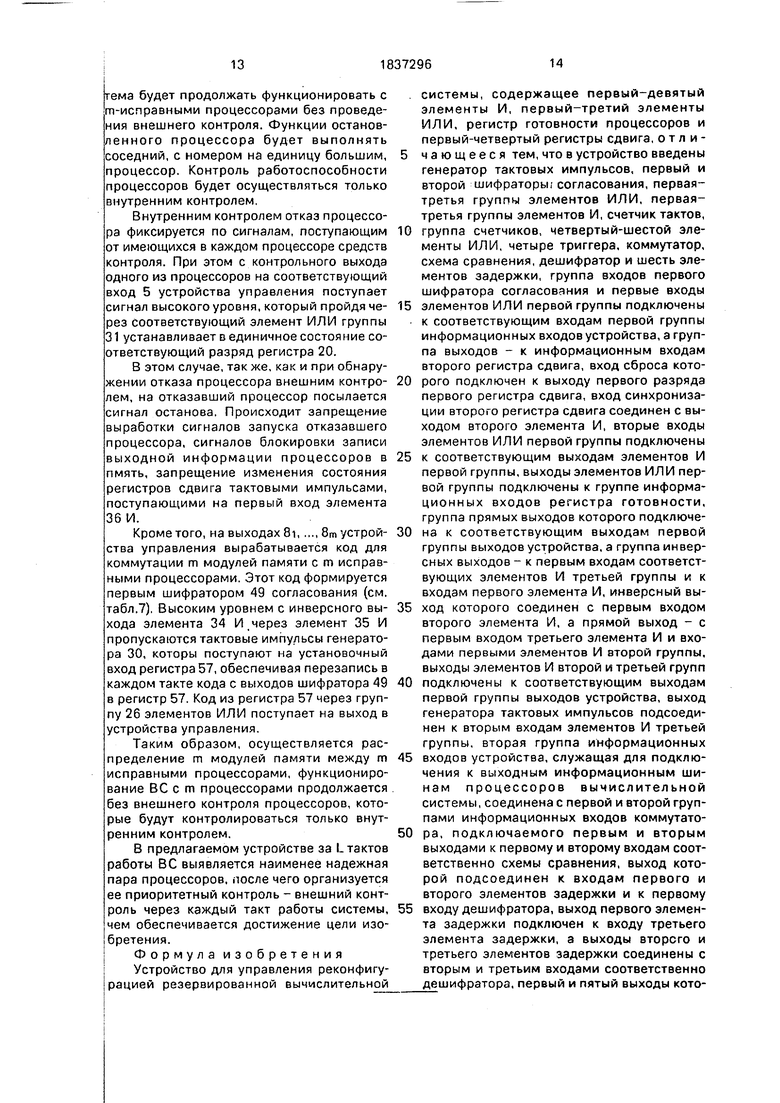

Для организации вычислений в ВС, в каждом такте работы на коммутаторы вывода 2i,.... 2m соответственно с выходов 81

8m устройства управления поступает управляющий код, определяющий порядок под- ключения процессоров к модуля памяти (см. табл.3). Низкий уровень на выходах 8i,..., 8m означает подключение соответствующего процессора 12,.... 1т, 1т+1 к модулю памяти с номером, на единицу меньшим номера процессора. Процессор 11 всегда подключен к модулю памяти 31. Высокий уровень

на выходах 818m означает подключение

соответствующего процессора к модулю памяти с номером, равным номеру процессо- ра, за исключением процессора 1т-и который будет подключен в данном случае к модулю памяти 3i.

В неприоритетном режиме управляющий код формируется в каждом такте рабо- ты во втором регистре 57 и через пятую группу 25 элементов И и через вторую группу 32 элементов ИЛИ поступает на выходы 8i, .,., 8m устройства управления. В исходном состоянии в регистре 57 записан код 0000...00, в следующем такте содержимое регистра 57 станет равным 1100.,.00, в следующем- 11110...00 и т.д. В течение (т/2+1) тактов в регистр 57 будет записан код 1111... 11. Запись двух единиц в регистр 57 осуществляется путем задержки тактового импульса пятым 17 элементом задержки на время, превышающее время длительности тактового импульса. Таким образом, на выходе 62 третьего 45 элемента ИЛИ (см. фиг.З) формируются два последовательных сигнала - тактовый импульс и задержанный тактовый импульс - и через элемент И 42 поступают на сдвиговые входы регистров 56 и 57. В исходное состояние регистр 57 пере- водится сигналом высокого уровня с выхода первого разряда регистра 56, поступающего на вход установки в ноль регистра 57. Затем процесс заполнения единицами регистра 57 повторяется.

В приоритетном режиме - в нечетных тактах работы - управляющий код на выход 8 устройства управления поступает с четвертого регистра 59 через группу 24 элементов И и через группу 32 элементов ИЛИ, в четных тактах работы - с регистра 57 через группу 25 элементов И и через группу 32 элементов ИЛИ. Формирование управляющего кода в регистре 57 отличается (от неприоритетного режима) в данном случае тем, что формирование кода - запись двух единиц со сдвигом - осуществляется только в четных тактах работы системы, то есть код 1111.„11 будет сформирован в регистре 57 за (т+2) тактов работы.

Поочередное считывание кода коммутации из регистров 57 и 59 обеспечивается переключением в каждом такте работы триггера 54, прямой и инверсный выходы которого подключены к вторым входам элементов И группы 25 и элементов И группы 24 соответственно, а также наличием сигнала высокого уровня на третьих входах элементов И групп 24 и 25, поступающего с прямого выхода первого 34 элемента И (все процессоры исправны).

Формирование управляющего кода в регистре 59 осуществляется по сигналу с выхода пятого 47 элемента ИЛИ, который, при наличии высокого уровня с прямого выхода второго 52 триггера, проходит через седьмой 40 элемент И и поступает на вход синхронизации регистра 59. По этому сигналу код с выходов группы 55 счетчиков, преобразуемый вторым 50 шифратором записывается в регистр 59. В соответствии с этим кодом в нечетных тактах работы будет организовано подключение выбранной пары процессоров к одному модулю памяти. Соответствие номеров счетчиков группы 55, в которых вырабатывается сигнал переполнения, кодов управления на входе и выходе шифратора 50 и номера выбранной пары процессоров представлено в табл.4.

После выполнения вычислений результаты с информационных выходов непроверяемых и одного из пары проверяемых процессоров через коммутаторы 2 вывода информации поступают на входы модулей 3 памяти и записываются в них.

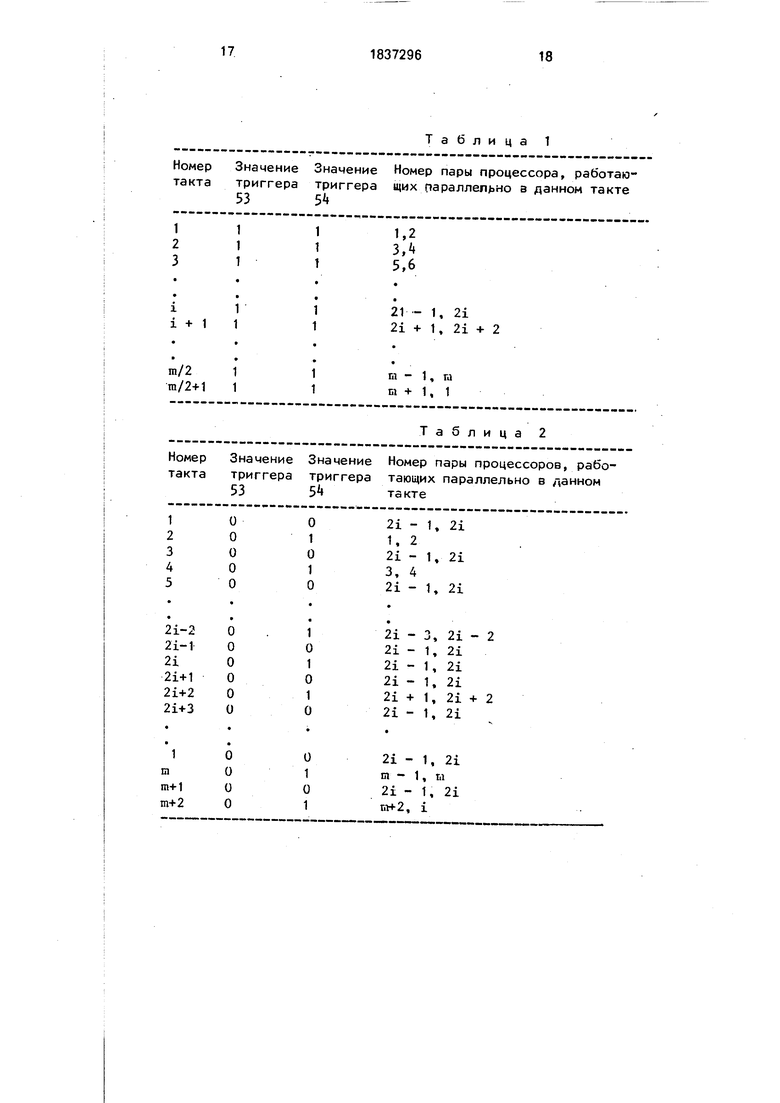

Информация в модуль памяти считывается с того процессора, из пары проверяемых процессоров, который имеет младший номер (см. табл.5). Это достигается путем блокировки в каждом такте работы старшего по номеру процессора из пары проверяемых. Для этого код с выходов элементов ИЛИ группы 33 поступает на вторые входы второй группы 22 элементов И, и, при разрешающем уровне на первых входах элементов 22, высокий уровень на выходе одного, определенного элемента 22 передается в соответствующую выходную шину 7 устройства управления.

Результаты вычислений с информационных выходов всех процессоров поступают также на информационные входы коммутаторов 9. С выхода 10 устройства управления на адресный вход коммутатора 9 в каждом такте работы поступает управляющий код, который разрешает коммутацию информационных выходов пары проверяемых процессоров на схемы схема 11 сравнения (табл.5).

В неприоритетном режиме этот код формируется в каждом такте работы в первом регистре 56 и через восьмую группу 28 элементов И и через третью группу 33 элементов ИЛИ поступает на выходы 10i, ..., 10m, tOm-и устройства управления. В каждом такте происходит прямой сдвиг (младшие разряды переписываются в старшие) информации, записанной в регистре 56, на два разряда.

В исходном состоянии в регистре 56 записан код 1000...00. В следующем такте содержимое регистра 56 станет равным 0010...00, в следующем - 000010...О, и т.д. В течение (т/2+1) тактов в регистр 56 будет записан код 0000...01. Сдвиг на два разряда обеспечивается поступлением на сдвиговый вход регистра 56 двух последовательных импульсов с выхода девятого 42 элемента И, В исходное состояние регистр 56 переводится при циклическом переносе единицы из (т+1)-го в 1-й разряд регистра 56, в данном случае сдвиг осуществляется на один разряд, т.к. низкий уровень сигнала с инверсного выхода последнего разряда регистра 57 поступает на второй вход пятого 38 элемента И и запрещает прохождение тактового импульса на пятый 17 элемент задержки и далее через элементы 45 ИЛИ и элемент 42 И на сдвиговый вход регистра 56.

В приоритетном режиме - в нечетных тактах работы - этот код на выход 10 устройства управления поступает с третьего регистра 58 через седьмую группу 27 элементов И и через группу 33 элементов ИЛИ, в четных тактах работы - с регистра 56 через группу 28 элементов И и через группу 33 элементов ИЛИ. Формирование управляющего кода в регистре 56 отличается (от не- приоритетного режима), в данном случае, тем, что формирование кода - сдвиг на два разряда содержимого регистра 56 - осуществляется только в четных тактах работы системы.

Поочередное считывание управляющего кода из регистров 56 и 58 обеспечивается переключением в каждом такте работы триггера 54, прямой и инверсный выходы оторого подключены к вторым входам эле- иентов И группы 28 и элементов И группы 27 соответственно.

Формирование управляющего кода в эегистре 58 осуществляется по сигналу с зыхода седьмого 40 элемента И, поступаю- дего на вход синхронизации регистра 58. 1о этому сигналу код, сформированный на

шходах 55i,55255т/2, 55т/2+1 группы 55

:четчиков (см. табл.4) записывается соответ- ггвенно в 1,3т-1, т+1 разряды регистра

58, во 2, 4, ..., m разряды регистра 58 записываются нули.

Выходная информация пары проверяемых процессоров сравнивается в схеме сравнения 11, на выходе которого при положительном результате сравнения вырабатывается сигнал низкого уровня. Этот сигнал поступает на входы дешифратора 60, на первый вход - с задержкой на два такта, на второй - с задержкой на один такт, на третий - без задержки. Дешифратор 60 на основе анализа сигналов на его входах вырабатывает соответствующий сигнал высокого уровня на одном из своих выходов (см. табл.6).

При положительном результате сравнения - на всех выходах дешифратора 60 сигналы низкого уровня -устройство управления свою работу не изменяет.

При несравнеиии результатов вычислений параллельно работающих процессоров с номерами 2i-1. 2i, на выходе схемы сравнения 11 вырабатывается сигнал выского уровня и поступает через элементы задержки на вход дешифратора 60. В этом случае на 2-м или 3-м выходе дешифратора 60 вырабатывается сигнал высокого уровня, свидетельствующий о том, что произошел сбой. По этому сигналу, прошедшему через четвертый 46 элемент ИЛИ, на выходе (i-ro) элемента И девятой 29 группы, соответствующего номеру пары проверяемых процессоров, выработается сигнал высокого уровня и поступит на счетный вход соответствующего (1-го) счетчика группы 55. Содержимое этого счетчика увеличится на единицу, т.е. происходит посчет сбоев в парах параллельно работающих процессоров.

В то же время, сигнал с выхода элемента 46 ИЛИ, пройдя через второй 44 элемент ИЛИ, сбросит в нулевое состояние первый 51 триггер. Это обеспечит организацию повторного счета в следующем такте работы системы. Низкий уровень на прямом выходе триггера 51 запрещает прохождение тактового импульса от генератора 30 через четвертый 37 элемент И на сдвиговые входы регистров 56 и 57 и на счетный вход триггера 54. Таким образом, Б следующем такте работы для контроля будет назначена та же самая пара процессоров с номерами 21-1, 21. Если в следующем такте работы происходит сравнение результатов работы контролируемых процессоров, то в предыдущем такте имел место однотэктный сбой и со следующего такта возобновляется прежний режим работы ВС. Сигнал высокого уровня с инверсного выхода триггера 51, задержанный на длительность такта четвертым 16

элементом задержки, пройдя через второй 44 элемент ИЛИ, обеспечит переключение триггера 51 в исходное (единичное) состояние и. тем самым, возврат устройства управления к исходному режиму работы.

При повторном несравнении результатов (код на выходе дешифратора - 110) на четвертом выходе дешифратора 60 появится сигнал высокого уровня, который сбрасывает в нулевое состояние второй 52 триггер. С этого момента принимается решение о неисправности одного из контролируемых процессоров и осуществляется его поиск в течение последующего такта работы. В последующем такте для параллельной работы будет назначена пара процессоров с номерами 2i, 21+1, что обеспечивается прямым сдвигом информации на один разряд либо в регистрах 58, 59 - если отказ выявлен в паре процессоров, выбранной для приоритетного контроля, триггер 54 в нулевом состоянии, либо в регистрах 56, 57 - если отказ выявлен в любой другой паре процессоров, триггер 54 в единичном состоянии.

Сдвиг информации на один разряд обеспечивается наличием сигнала низкого уровня на третьем входе пятого 38 элемента И, поступающего с прямого выхода триггера 52 и запрещающего прохождение тактового импульса через элемент 17 задержки, элемент 45 И-и далее на входы прямого сдвига регистров 56, 57 или регистров 58, 59.

Отсутствие тактовых импульсов на выходе элемента 38 И обеспечивает неизменность состояния триггера 54 во время выявления отказавшего процессора, т.к. эти импульсы не поступают на счетные входы счетчика 19 и триггеры 54. При выявлении отказавшего процессора запрещен также прием новой информации в регистры 58,59, на входы синхронизации которых с седьмого 40 элемента И поступает сигнал низкого уровня.

Если при параллельной работе пары процессоров с номерами 21,21+1 произошло сравнение результатов вычислений (код на входе дешифратора - 011), то неисправным является (21-1)-й процессор. На первом выходе дешифратора 60 вырабатывается сигнал высокого уровня по которому .осуществляется обратный сдвиг (старшие разряды переписываются в младшие) на один разряд в регистрах 56 и 58. По этому же сигналу, прошедшему через первый 43 элемент ИЛИ и задержанному шесты 18 элементом задержки на время, необходимое для обратного сдвига информации в регистрах 56, 58 будет сформирован разрешающий сигнал на первых входах элементов И первой 21 группы. В зависимости от состояния триггера 54, скорректированный в регистрах 56 и 58 код поступит либо из регистра 56 через группу 28 элементов И, либо из регистра 58 через группу 27 элементов И на входы группы 33 элементов ИЛИ и далее через группу 21 элементов И и группу 31 элементов ИЛИ на информационные входы регистра 20 готовности процессоров. Таким образом, в (2М)-ом разряде регистра 20 го0 товности процессоров будет записана единица.

Если при параллельной -работе пары процессоров с номерами 21, 21+1 произошло несравнение результатов вычислений (код

5 на входе дешифратора ), то неисправным считается 21-й процессор. На пятом выходе дешифратора 60 вырабатывается сигнал высокого уровня, по которому код (без обратного сдвига) из регистра 56 или

0 регистра 58 будет переписан, как указано выше, в регистр 20 готовности процессоров, В данном случае единица будет записана в 21-й разряд регистра 20 готовности процессоров.

5 На прямом выходе разряда, в котором записана единица, регистра готовности процессоров вырабатывается сигнал останова отказавшего процессора и поступает в соответствующую выходную шину группы

0 7i,,.., 7m, 7m-H выходов устройства управления. На инверсном выходе - сигнал низкого уровня запрещает прохождение через соответствующий элемент И группы 23 сигналов запуска от генератора 30 в соответстеую5 щую выходную шину группы 7i, ..., 7m, 7m+i выходов устройства управления. При наличии единицы в одном из разрядов регистра 20 готовности процессоров на прямом выходе первого 34 элемента И формируется сиг0 нал низкого уровня, который поступает на первые входы элементов И группы 22 и запрещает прохождение сигналов блокировки

записи на выходные шины группы 7i7т

7т+1 выходов устройства управления. Кроме

5 того, сигнал низкого уровня с прямого выхода элемента 34 И запрещает прохождение информации через четвертую 24 и пятую 25 группы элементов И, запрещает прохождение тактовых импульсов через третий 36

0 элемент И, запрещая тем самым, изменение содержимого регистров сдвига. Сигнал высокого уровня с инверсного выхода элемента 34 И разрешает прохождение информации через шестую 26 группу эле5 ментов И, разрешает прохождение тактовых импульсов через второй 35 элемент И на установочный вход регистра 57.

Таким образом, происходит подготовка системы к работе с m-исправными процессорами. Начиная со следующего такта сиетема будет продолжать функционировать с m-исправными процессорами без проведения внешнего контроля. Функции остановленного процессора будет выполнять соседний, с номером на единицу большим, процессор. Контроль работоспособности процессоров будет осуществляться только внутренним контролем.

Внутренним контролем отказ процессора фиксируется по сигналам, поступающим от имеющихся в каждом процессоре средств контроля. При этом с контрольного выхода одного из процессоров на соответствующий вход 5 устройства управления поступает сигнал высокого уровня, который пройдя через соответствующий элемент ИЛИ группы 31 устанавливает в единичное состояние соответствующий разряд регистра 20.

В этом случае, так же, как и при обнаружении отказа процессора внешним контролем, на отказавший процессор посылается сигнал останова. Происходит запрещение выработки сигналов запуска отказавшего процессора, сигналов блокировки записи выходной информации процессоров в пмять, запрещение изменения состояния регистров сдвига тактовыми импульсами, поступающими на первый вход элемента 36И.

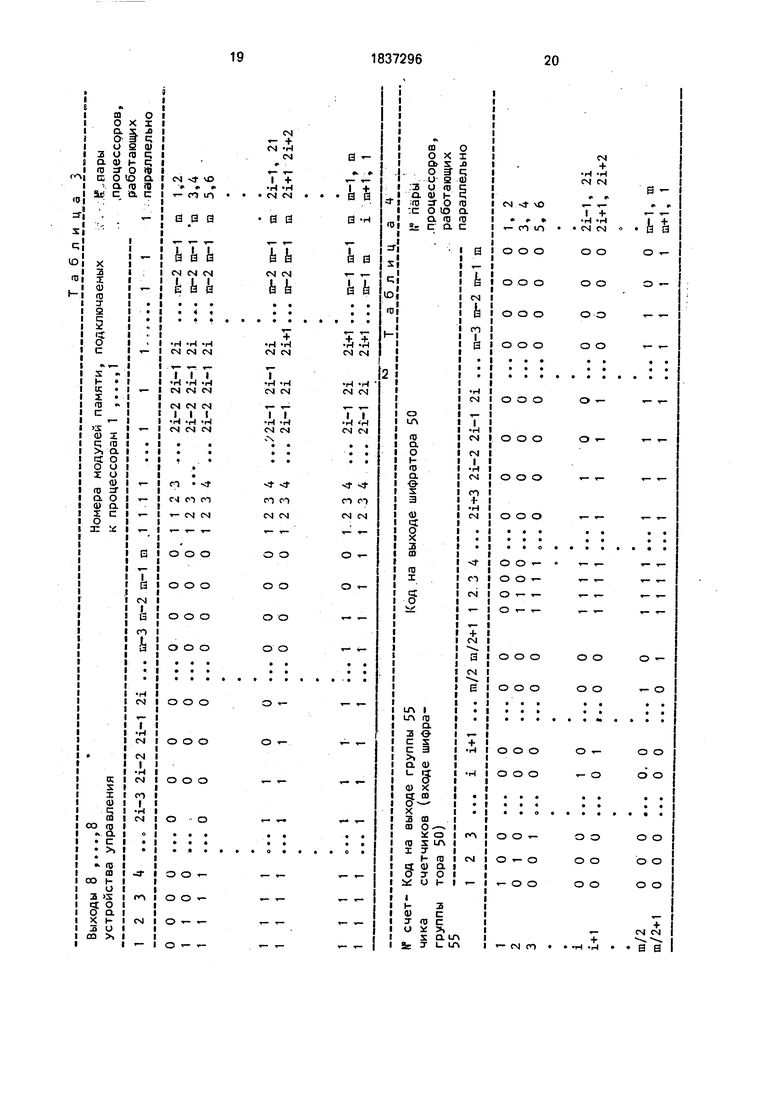

Кроме того, на выходах 8i, ..., 8m устройства управления вырабатывается код для коммутации m модулей памяти с m исправными процессорами. Этот код формируется первым шифратором 49 согласования (см. табл.7). Высоким уровнем с инверсного выхода элемента 34 И через элемент 35 И пропускаются тактовые импульсы генератора 30, которы поступают на установочный вход регистра 57, обеспечивая перезапись в каждом такте кода с выходов шифратора 49 в регистр 57. Код из регистра 57 через группу 26 элементов ИЛИ поступает на выход в устройства управления.

Таким образом, осуществляется распределение m модулей памяти между m исправными процессорами, функционирование ВС с m процессорами продолжается без внешнего контроля процессоров, которые будут контролироваться только внутренним контролем.

В предлагаемом устройстве за L тактов работы ВС выявляется наименее надежная пара процессоров, после чего организуется ее приоритетный контроль - внешний контроль через каждый такт работы системы, чем обеспечивается достижение цели изобретения.

Формула изобретения

Устройство для управления реконфигурацией резервированной вычислительной

. системы, содержащее первый-девятый элементы И, первый-третий элементы ИЛИ, регистр готовности процессоров и первый-четвертый регистры сдвига, о т л и чающееся тем, что в устройство введены генератор тактовых импульсов, первый и второй шифраторы/ согласования, первая- третья группы элементов ИЛИ, первая- третья группы элементов И, счетчик тактов,

0 группа счетчиков, четвертый-шестой элементы ИЛИ, четыре триггера, коммутатор, схема сравнения, дешифратор и шесть элементов задержки, группа входов первого шифратора согласования и первые входы

5 элементов ИЛИ первой группы подключены к соответствующим входам первой группы информационных входов устройства, а группа выходов - к информационным входам второго регистра сдвига, вход сброса кото0 рого подключен к выходу первого разряда первого регистра сдвига, вход синхронизации второго регистра сдвига соединен с выходом второго элемента И, вторые входы элементов ИЛИ первой группы подключены

5 к соответствующим выходам элементов И первой группы, выходы элементов ИЛИ первой группы подключены к группе информационных входов регистра готовности, группа прямых выходов которого подключе0 на к соответствующим выходам первой группы выходов устройства, а группа инверсных выходов - к первым входам соответствующих элементов И третьей группы и к входам первого элемента И, инверсный вы5 ход которого соединен с первым входом второго элемента И, а прямой выход - с первым входом третьего элемента И и входами первыми элементов И второй группы, выходы элементов И второй и третьей групп

0 подключены к соответствующим выходам первой группы выходов устройства, выход генератора тактовых импульсов подсоединен к вторым входам элементов И третьей группы, вторая группа информационных

5 входов устройства, служащая для подключения к выходным информационным шинам процессоров вычислительной системы, соединена с первой и второй группами информационных входов коммутато0 ра, подключаемого первым и вторым выходами к первому и второму входам соответственно схемы сравнения, выход которой подсоединен к входам первого и второго элементов задержки и к первому

5 входу дешифратора, выход первого элемента задержки подключен к входу третьего элемента задержки, а выходы второго и третьего элементов задержки соединены с вторым и третьим входами соответственно дешифратора, первый и пятый выходы которого подключены к входам первого элемента ИЛИ, соединенного выходом с входом шестого элемента задержки, выход которого подключен к первым входам элементов И первой группы, второй и третий выходы дешифратора подключены к входам четвертого элемента ИЛИ, выход которого подключен к первым входам элементов И девятой группы и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента задержки, а выход - к счетному входу первого триггера, инверсный и прямой выходы которого подключены соответственно к входу четвертого элемента задержки и первому входу четвертого элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход - к вторым входам второго и третьего элементов И, четвертый выход дешифратора соединен со счетным входом второго триггера, инверсный выход Которого подключен к первому входу восьмого элемента И, а прямой выход - к первым входам пятого и седьмого элементов И, выход которого соединен с входами синхронизации третьего и четвертого регистра сдвигов, первый вход управления сдвигом третьего регистра сдвига соединен с входом управления сдвига четвертого регистра сдвига и выходом восьмого элемента I/I, второй вход управления сдвига третьего регистра сдвига соединен с первым входом управления сдвига первого регистра сдвига и первым выходом дешифратора, группа выходов третьего регистра сдвига подключена к первым входам соответствующих элементов И седьмой группы, выходы которых подключены к первым входам соответствующих элементов ИЛИ третьей группы, вторые входы которых подключены к выходам соответствующих элементов И восьмой группы, а выходы - к вторым входам соответствующих элементов И первой и второй групп и к адресному входу коммутатора, выходы нечетных элементов ИЛИ третьей группы элементов ИЛИ подключены к вторым входам элементов И девятой группы, выходы которых подключены к счетным входам соответствующих счетчиков группы, входы сброса которых соединены с выходом шестого элемента ИЛИ, а выходы переполнения счетчиков группы подключены к группе входов пятого элемента ИЛИ, к группе нечетных информационных входов третьего регистра сдвига и к группе входов второго шифратора согласования, группа выходов которого подключена к группе информационных входов четвертого регистра сдвига, группа выходов которого подключена к первым входам соответствующих элементов И четвертой группы, выход пятого элемента ИЛИ подключен к первому входу шестого элемента ИЛИ, второму входу седьмого элемента И, входу сброса третьего триггера и входу сброса

счетчика тактов, выходы переполнения которого соединен с вторым входом шестого элемента ИЛИ л входами установки в единичное состояние третьего и четвертого триггеров, инверсный выход третьего триггера подключен к первому входу шестого элемента И, выход которого соединен со счетным входом четвертого триггера, инверсный выход которого подключен к вторым входам элементов И четвертой и седьмой

групп и к второму входу восьмого элемента И, а прямой выход - к первым входам элементов И пятой и восьмой групп и к первому, входу девятого элемента И, выход которого соединен с входом управления сдвигом второго регистра сдвига и вторым входом управления сдвигом первого регистра сдвига, группа выходов которого подключена к вторым входам соответствующих элементов И восьмой группы, группа выходов второго регистра сдвига подключена к вторым входам соответствующих элементов И пятой группы и первым входам соответствующих элементов И шестой группы, вторые входы элементов И шестой группы соединены с

инверсным выходом первого элемента И, прямой выход которого соединен с третьими входами элементов И четвертой и пятой групп, выходы элементов И четвертой, пятой и шестой групп подключены к входам

соответствующих элементов ИЛИ второй группы, выходы которых подключены первой группе управляющих выходов устройства, инверсный выход старшего разряда второго регистра сдвига подключен к второму входу пятого элемента И, третий вход которого соединен с выходом третьего элемента И и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, счетным входом счетчика тактов и вторым входом шестого эпемен га И, выход третьего элемента ИЛИ подключен к второму входу девятого элемента И и третьему входу восьмого элемента И, а выход генератора тактовых импульсов соединен с вторыми входами элементов И первой группы.

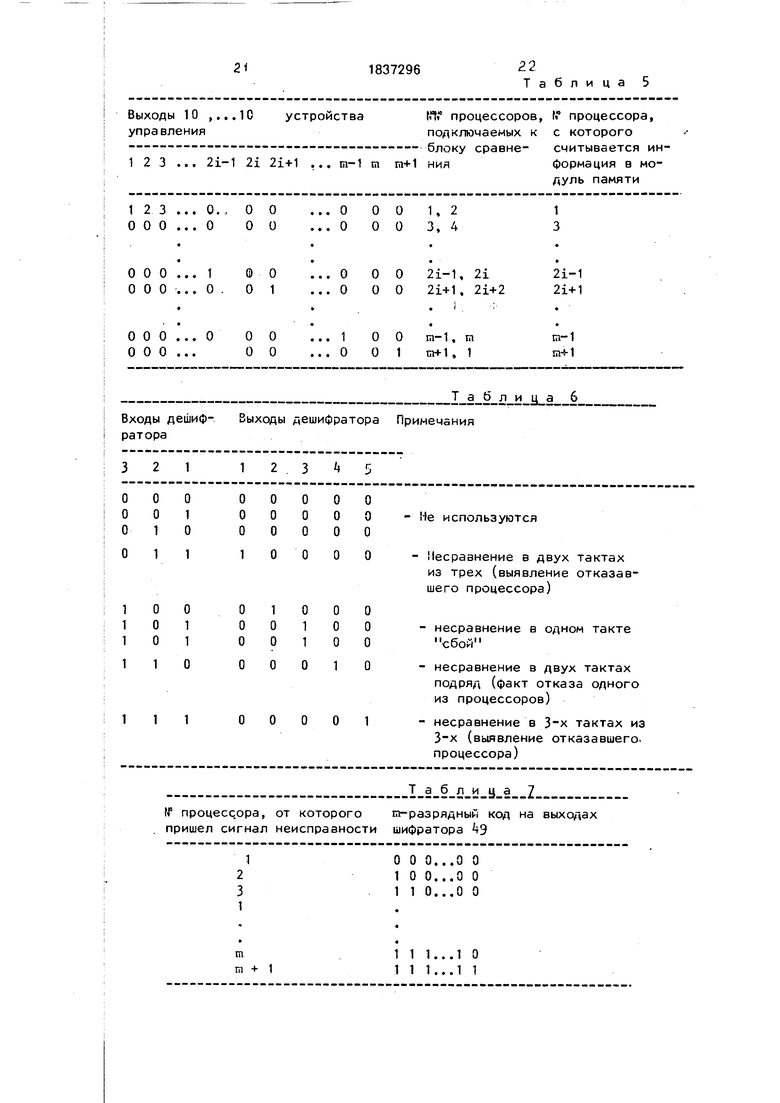

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Резервированная вычислительная система | 1989 |

|

SU1691991A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления резервированной вычислительной системой | 1989 |

|

SU1755399A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Сущность изобретения: устройство содержит: элементы И 34-42, элементы ИЛИ 43-48, регистр 20 готовности процессоров, регистры сдвига 55-59, генератор 30 тактовых импульсов, шифраторы согласования 49,50, группы элементов ИЛИ 31-33, счетчик 19 тактов, группы счетчиков 55, триггеры 51- 54, коммутатор 9, схему сравнения 11, дешифратор 60, элементы задержки 13-18. 3 ил,7 табл.

Авторы

Даты

1993-08-30—Публикация

1991-02-25—Подача