Изобретение относится к вычислительной технике и может быть использовано для контроля, испытания и исследования диодных матриц постоянных запоминающих устройств с электрической перезаписью информации.

По основному авт. св. № 898507 известно устройство для контроля матриц памяти, содержащее блок управления, телевизионный приемник, формирователь видеосигналов, формирователь сигналов координатной сетки, схему сравнения, генератор синхросигналов, блок адреса, формирователь тестовых сигналов, группу коммутаторов, блок местного управления, блок индикации и формирователь маркерных сигналов, причём вход телевизионного приемника подключен к Выходу формирователя видеосигналов первый вход которого соединен с первым выходом генератора синхросигналов , а второй вход - с первым выходом формирователя сигналов координатной сетки, вход которого подключен к первому входу схемы сравнения и второму выходу генератора синхросигналов, третий выход которого соединен с входом блока управления, первый и второй входы формирователя маркерных сигналов подключены соответственно к первому входу и к выходу схемы сравнения, первый выход соединен с третьим входом формирователя видеосигналов, а второй выход - с первым входом блока местного управления, второй вход которого соединен с вторым выходом формирователя сигналов координатной сетки, одни из входов коммутаторов группы подключены к первому, входу схемы сравнения, а другие входы к выходам блока адреса, второму входу схемы сравнения и первому входу формирователя тестовых сигналов , второй вход которого соединен с выходом блока управления, а один из выходов - с входом блока адреса, другие выходы формирователя тестовых сигналов подключены соответственно к третьему и четвертому входам блока местного управления, 1ятый вход которого соединен с четвертим выходом генератора синхросигналов, а шестой вход подключен к выходам коммутаторов группы информационный и управляющий ВЫХОДЕЦ блока местного управления соединены соответственно с четвертым входом формирователя видеосигналов, с входами управления коммутаторов и третьим входом формирователя тестовых сигналов , индикаторный выход соединен с входом блока индикации, а седьмой вход и контрольные выходы.являются соответственно входом и выходами устройства, при этом блок местного управления содержит логический блок

блок считывания, группу ключей, группу генераторов сигналов, формирователь сигналов временной диаграммы и дешифратор j причем входы ключей соединены соответственно с выходом дешифратора и одними из выходов формирователя сигналов временной диаграммы и генератора сигналов группы, входы и другие выходы которых подключены соотвеаственно к . другим выходам формирователя сигналов временной диаграммы и к одним из входов блока считывания, выход которого соединен с одним из входов логического блока, другие входы которого, входы дешифратора и формирователя сигналов временной диаграммы, другие входы блока считывания являются входами блока местного управления, выходами которого являются выходы логического блока, блока считывания и ключей til.

В известном устройстве запоминающая ячейка контролируемой матрицы отображается на телевизионном приемнике в двух состояниях: в состоянии логического О и состоянии логической 1, которые отмечают высокоомное и низкоомное состояния соответственно. Бывают случаи, когда запоминающая ячейка находится в промежуточном между высокоомным и низкоомньм состоянии. Это состояние обычно неустойчиво. В процессе перезаписи такое состояние является сбоет, в процессе считывания отказом. Сбой устраняется повторной подачей импульса перезаписи. На экране телевизионного .приемника промежуточное состояние отображается либо элементом с произвольно меняю1цимся состоянием, либо логическим О или логической 1. в первом случае промежуточное состояние неустойчиво, во втором устойчиво, однако недолговременно. Отобргокение промежуточного состояния логическимг О или логической 1 не отражает действительного состояния запоминающей ячейки. Это снижает надежность устройства.

Цель изобретения -. повышение :достоверности контроля.

V

Поставленная цель достигается тем, что в устройство для контроля матриц памяти введен селектор строк входы которого соединены соответственно с одними из выходов генератора синхросигналов и фО1 1ирователя тестовых сигналов, а выход подключен к одному из входов блока местного управления.

Селектор строк содержит коммутатор и SR-триггер, 9- и R-входы которого соединены с выходами коммутатора, счетный вход 5R -триггера и входы коммутатора являются входами селектора строк, выходом которого является выход SR -триггера.

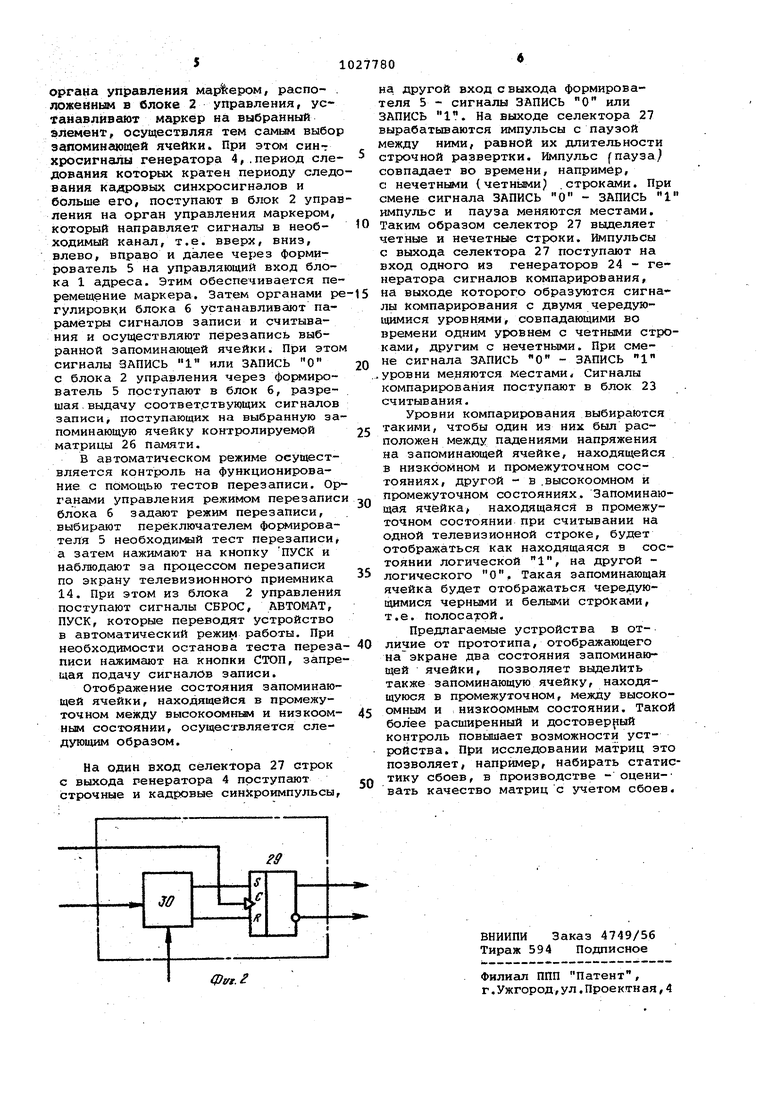

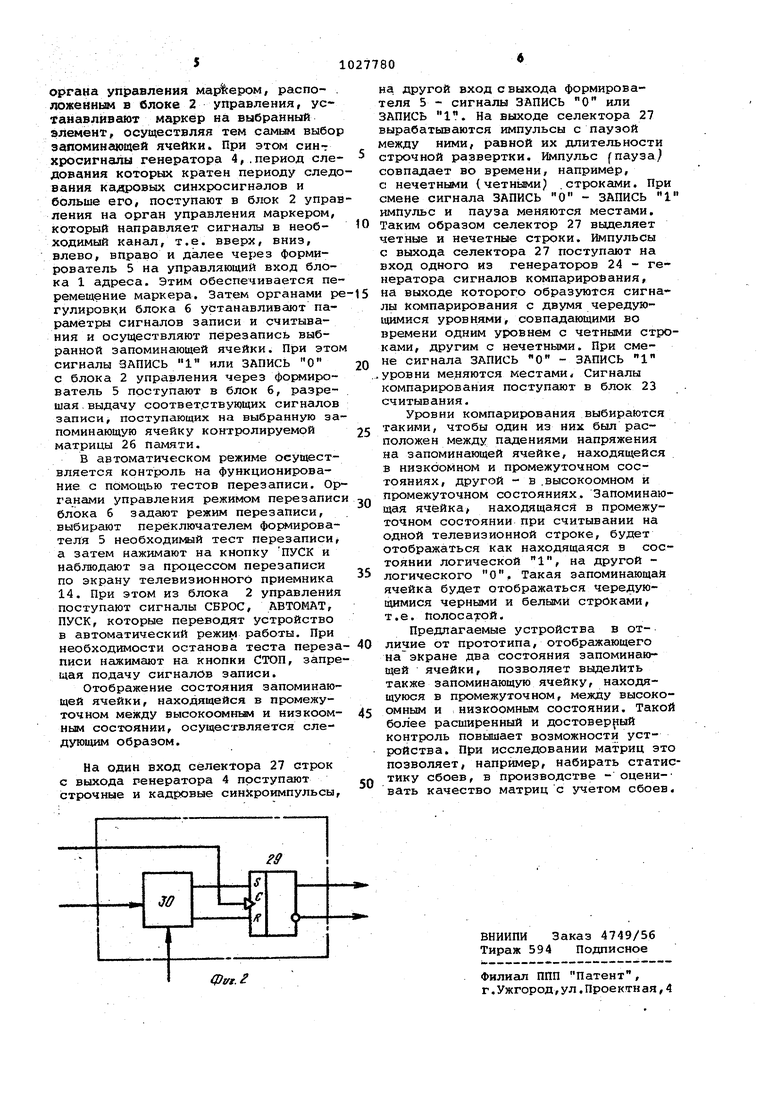

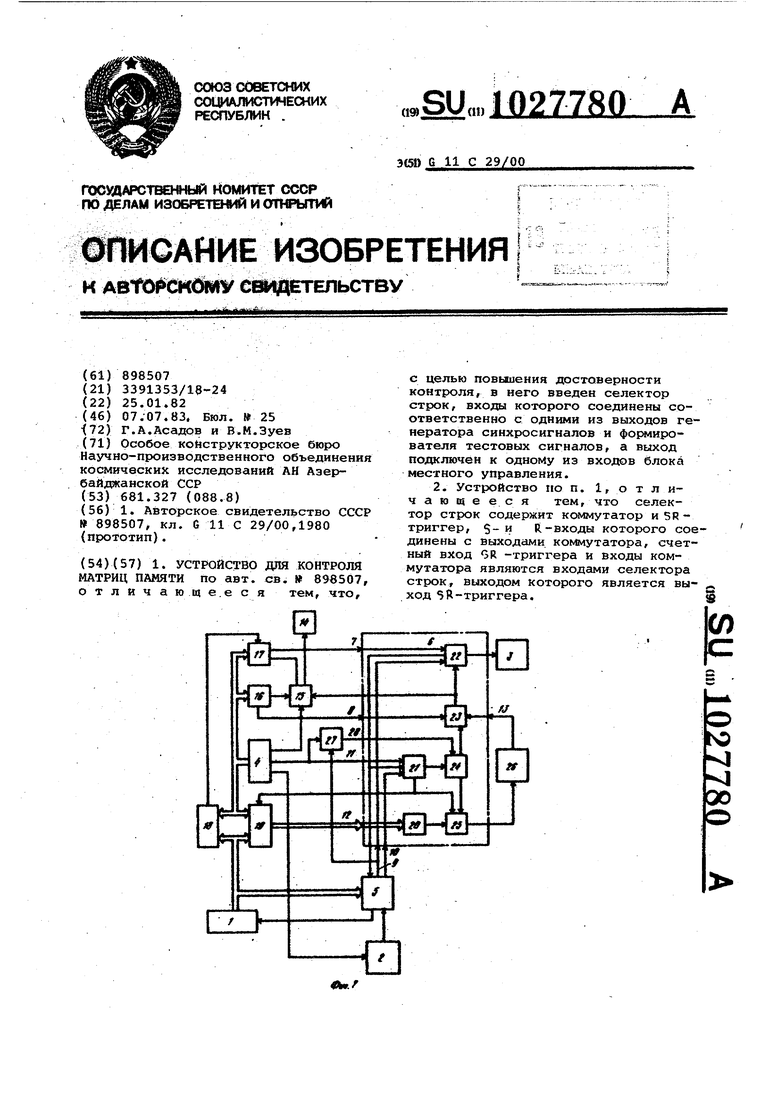

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема селектора строк.

Устройство (фиг. 1) содержит блок 1 адреса, блок 2 управления, блок 3 индикации, генератор 4 синхросигналов, формирователь 5 тестовых сигналов, блок 6 местного упраления с вкодамтл 7-13, телевизионный приемник 14,формиров атель 15 видеосигналов, формирователь 16 синалов координатной сетки, формирователь 17 маркерных сигналов, схему 18 сравнения и группу коммутаторов 19.

Блок 6 местного управления включает дешифратор 20, формирователь 21 сигналов временной диаграивды, логический блок 22, блок 23 считывания, группу генераторов 24 сигналов, группу ключей 25.

Блок.6 подключается к контролируемой матрице 26 памяти.

Устройство для контроля матриц памяти также содержит селектор 27 строк, выход которого подключен к входу 28 блока 6.

Селектор 27 строк (фиг. 2) состоит из5й. -триггера 29 и коммутатора 30.

Устройство работает следующим образом.

На экране телевизионного приемника 14 формируется информационное поле, разделенное координатной сеткой на элементы, отображающие состояния запоминающих ячеек контролируемой матрицы 26 памяти и соответствунадие физическим адресам этих ячеек. Размер элемента по горизонтали (по строке ) определяется длительностью отображения запоминшощей ячейки матрицы 26, а по вертикгши (по кадру/ - числом строк.

Информация, отображаемая на экране, имеет три градации яркости: черную, белую и серую. Черная соответствует логической 1, белая логическому О состояния запоминающей ячейки матрицы 26.Серую градацию имеет координатная сетка и обрамляющее поле. Маркер - белый на черном элементе и чёрный - на белом. Запоминающая ячейка, находящаяся в промежуточном состоянии, отображается элементом с чередующимися черНЕЛ и и белыми строками. Такой элемент выглядит полосатым.

Формирователь 17 формирует сигналы маркера, которые поступают на формирователь 15, и сигналы середины маркера, поступающие в логический блок 22. Если маркер изображается в виде крестика, то он образуется с помощью сетки, располо.женнрй внутри координатной сетки« выделение крестика (перекрестия сетки маркера) осуществляется сигналом, поступающим с выхода схемы 18 сравнения. Адрес маркера определяется кодом, находящимся в блоке 1 адреса.,

Формирователь 15, на входы которого поступают сигналы координат-ной сетки с формирователя 16, .сигналы маркера - с формирователя 17, синхросигналы - с генератора 4 и информация, считанная из контролируемой матрицы 26 памяти, формирует полный видеосигнал, который поступает на вход телевизионного приемника 14. Блок 6 осуществляет считывание и перезапись т.е. дозапись, корректирование или смену/ информации в контролируемой матрице 26 памяти в соответствии с тестом перезаписи в автоматическом или ручном режиме. При этом логический блок 22 определяет и запоминает состояние выбранной запоминающей ячейки, разрешает или запрещает подачу сигналов записи, выдает сигналы для индикации в блок 3 индикации.

Блок 23 считывания осуществляет параллельную выборку информации из контролируемой матрицы 26 памяти и выдачу ее последовательно на вход формирователя 15. Ключи 25 осуществляют коммутацию шин контролируекюй матрицы 26 памяти. Генераторы 24 вырабатывают сигналы записи 1 и О, считывания, компарирования и подзапирающего напряжения, необходимые для перезаписи и считывания информации. Формирователь 21 формирует сигналы и временные соотношения, необходимые для работы генератора 24, дешифратор 20 осуществляет дешифрацию кода координат..

В режиме считывания по входу 12 в блок 6 поступает код координат элементов разложения, информационного поля. В соответствии с этим кодом производится последовательный опрос каждой адресной шины контролируемой матрицы 26 памяти и выборка информации с разрядных шин, с которых она выбирается столько раз, сколько телевизионных строк составляет элемент отображающий запоминающую ячейку на экране телевизионного приемника 14. С выхода формирователя 16 в блок 6 поступают сигналы вертикальных линий координатной сетки, с помойц ю которых осуществляется последовательное считывание содержимого разрядных шин матрицы.

Режим перезаписи подразделяется на ручной и автоматический.

В ручном режиме по желанию оператора П.РОИЗВОДИТСЯ выбор запоминаюокей ячейки и ее перезапись. С помощь

органа управления мар1сером, распо- . ложенным в блоке 2 управления, устанавливают маркер на выбранный элемент, осуществляя тем самым выбор запоминающей ячейки. При этом синт хросигналы генератора 4,.период еледования которых кратен периоду следования кадровых синхросигналов и больше его, поступают в блок 2 управления на орган управления маркером, который направляет сигналы в необходимый канал, т.е. вверх, вниз, влево, вправо и далее через формирователь 5 на управляющий вход блока 1 адреса. Этим обеспечивается перемещение маркера. Затем органами ре гулиров и блока 6 устанавливают параметры сигналов записи и считывания и осуществляют перезапись выбранной запоминающей ячейки. При этом сигналы ЗАПИСЬ 1 или ЗАПИСЬ О с блока 2 управления через фор лирователь 5 поступают в блок б, разрешая . выдачу соответствующих сигналов записи, поступающих на выбранную запоминающую ячейку контролируемой матрицы 26 Пс1мяти.

В автоматическом режиме осуществляется контроль на функционирование с помощью тестов перезаписи. Органами управления режимом перезаписи блока б задают режим перезаписи, выбирают переключателем формирователя 5 необходи1«ый тест перезаписи а затем нажимают на кнопку ПУСК и наблюдают за процессом перезаписи по экрану телевизионного приемника 14. При этом из блока 2 управления поступают сигналы СБРОС, АВТОМАТ, ПУСК, которые переводят устройство в автоматический режим работы. При необходимости останова теста перезаписи нажимают на кнопки СТОП, запрещая подачу сигналов записи.

Отображение состояния запоминающей ячейки, находящейся в промежуточном между высокоомным и низкоомным состоянии, осуществляется следующим образом.

На один вход селектора 27 строк с выхода генератора 4 поступают строчные и кадровые синхроимпульсы.

на другой вход с выхода формирователя 5 - сигналы ЗАПИСЬ О или ЗАПИСЬ 1. На выходе селектора 27 вырабатываются импульсы с паузой между ними, равной их длительности строчной развертки. Импульс (пауза совпадает во времени, например, с нечетными {четньми) .строками. При смене сигнала ЗАПИСЬ О - ЗАПИСЬ 1 импульс и пауза меняются местами. Таким образом селектор 27 выделяет четные и нечетные строки. Импульсы с выхода селектора 27 поступают на вход одного из генераторов 24 - генератора сигналов компарироВания, на выходе которого образуются сигналы Компарирования с двумя чередующимися уровнями, совпадающими во времени одним уровнем с четными строками, другим с нечетными. При смене сигнала ЗАПИСЬ О - ЗАПИСЬ 1 .уровни меняются местами. Сигналы Компарирования поступают в блок 23 считывания.

Уровни Компарирования выбираются такими, чтобы один из них был расположен между падениями напряжения на запоминающей ячейке, находящейся в низкооМном и промежуточном состояниях, другой - в .высокоомном и промежуточном состояниях. Запоминающая ячейка, находящаяся в промежуточном состоянии при считывании на одной телевизионной строке, будет отображаться как находящаяся в состоянии логической 1, на другой логического О, Такая запоминающая ячейка будет отображаться чередующимися черными и белыми строками, т.е. полос атой.

Предлагаемые устройства в отличие от прототипа, отображающего на экране два состояния запоминающей ячейки, позволяет выделить также запоминающую ячейку, находящуюся в промежуточном, между высокоомным и низкоомным состоянии. Такой более расширенный и достоверный контроль повышает возможности устройства. При исследовании матриц это позволяет, например, набирать статистику сбоев, в производстве - оценивать качество матриц с учетом сбоев.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1191934A2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1980 |

|

SU959143A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1357998A1 |

| УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО КОНТРОЛЯ СВАРНЫХ СОЕДИНЕНИЙ И ИЗДЕЛИЙ | 1990 |

|

RU2018816C1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАТРИЦ ПАМЯТИ по авт. св. 89в507, отличайте.вся тем, что. с целью повыиения достоверности контроля, в него введен селектор строк, входы которого соединены соответственно с одними из выходов генератора синхросигналов и формирователя тестовых сигналов, а выход подключен к одному из входов блока мест ного управле н ия. 2. Устройство по п. 1, о т л ичающе еся тем, что селектор строк содержит коммутатор и 5Rтриггер, S- и R-входы которого соединены с выходами коммутатора, счетный вход OR -триггера и входы коммутатора являются входами селектора строк, выходом Которого является выход SR-триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-07-07—Публикация

1982-01-25—Подача