Известны цифровые автоматические оптимизаторы, содержащие коммутатор с выходным реле, запоминающее устройство, операционный и исполнительный блоки. Быстродействие их сравнительно невысоко.

Предложенный оптимизатор обладает расщиренным динамическим диапазоном работы и повышенной помехоустойчивостью. Он отличается тем, что в нем установлен кольцевой счетчик с автономным источником питания, к которому подсоединены два ключа с последовательно включенной ячейкой «И, логическая ячейка «ИЛИ, подключенная своими входами к выходам ячеек «И, и четыре линии задержки, подсоединенные к выходу ячейки «ИЛИ. Второй вход каждой ячейки «И подсоединен соответственно к выходам второго и последнего триггеров кольцевого счетчика, выход схемы «ИЛИ подключен к щине сброса счетчика. Вход первого триггера подключен к выходу выходного реле, а выходы линий задержек соединены с запоминающим устройством, операционным и исполнительным блоками.

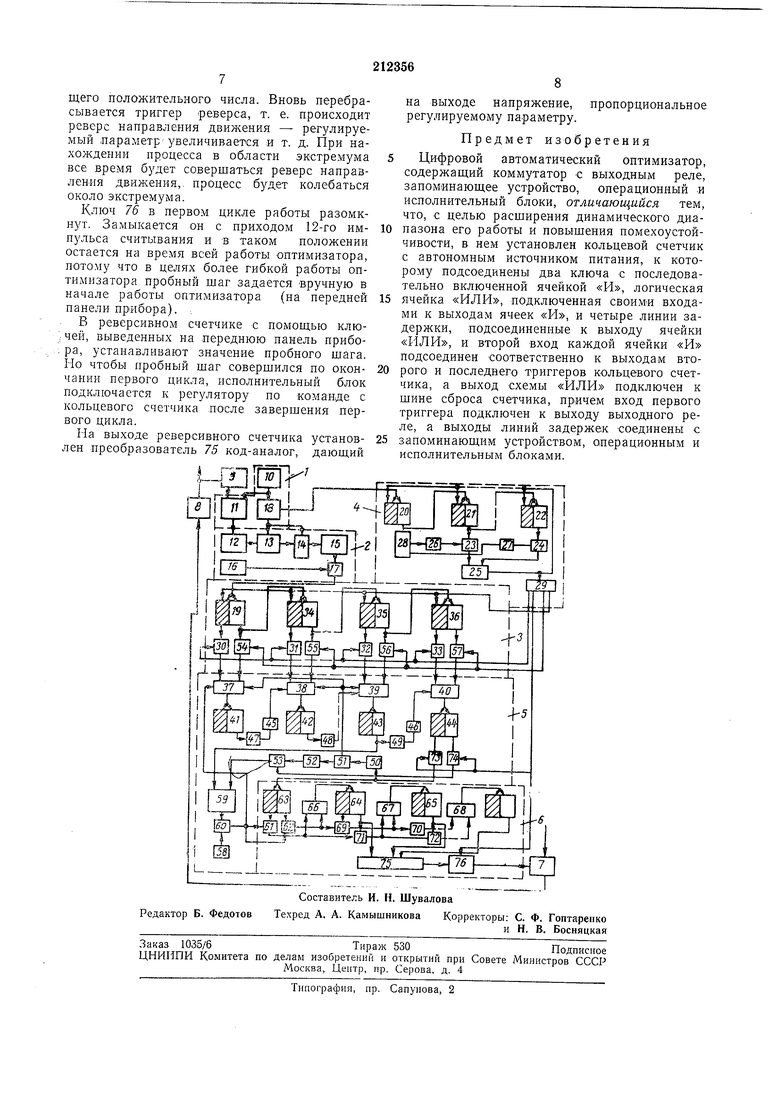

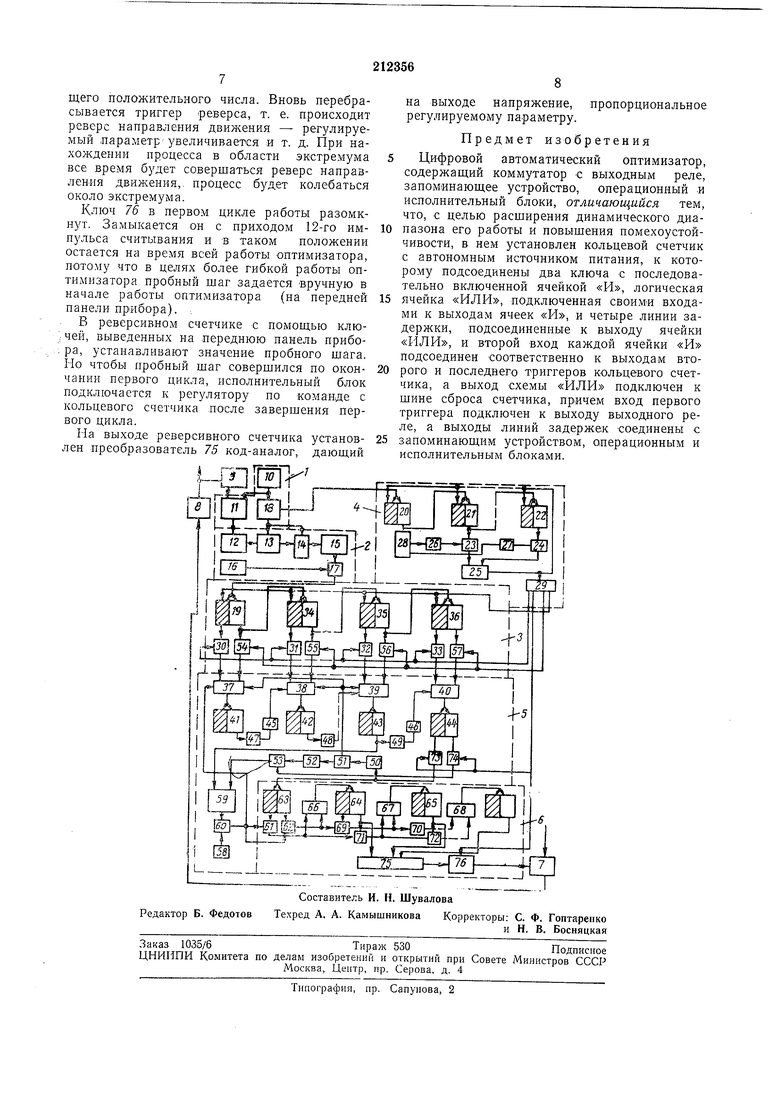

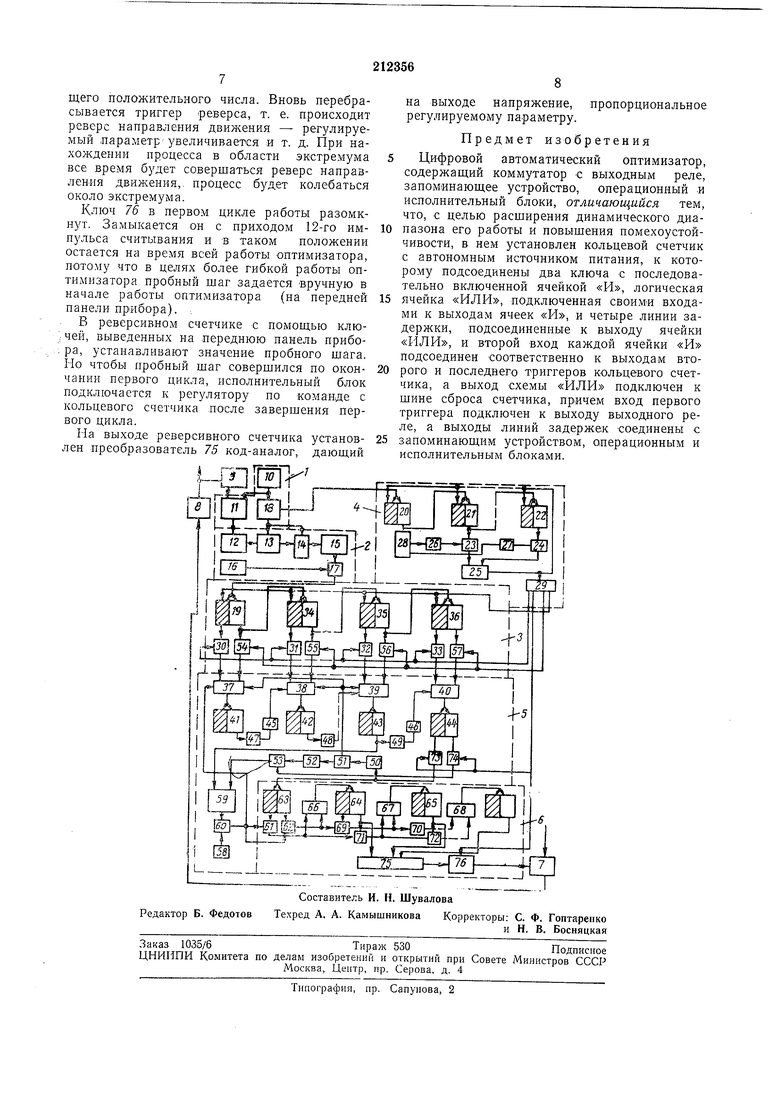

Иа чертеже представлена блок-схема цифрового оптимизатора.

5 исполнительного блока 6, регулятора 7, который регулирует процесс в объекте S, и датчика 9.

Данный оптимизатор является системой 5 шагового типа с методом поиска экстремума по градиенту и с совмещенным пробным и рабочим щагами. Областью оптимальных значений оптимизатора является область, в которой функции (к)(х. - регулируемый пара0 метр; (х) - показатель данного процесса, когорый оптимизируется) принимает экстремальное значение или находится вблизи него. Для отыскания направления движения к оптимуму в оптимизаторе заложен принцип изменения знака приращения функции при лереходе ею экстремума.

Работает оптимизатор следующим образом. Коммутатор 10 с заданной частотой подключает текущее значение измеряемой функции /; (х) на в.ход .ключа П, который ири подаче команды с коммутатора 10 пропускчет текущее значение /; (х,) на вход преобразователя 2 аналог-число импульсов. Он состоит из преобразователя аналог-напряжение 12, преобразователя 13 напряжение-длительность импульса, ячейки «ИЛИ 14, триггера 15, генератора импульсов 16 и ячейки «И П. Для более четкой работы на выходе коммутатора 10 ставится реле 18, которое будет вклюПри срабатывании этого реле подается команда в виде положительного импульса напряжения на Преобразование напряжения с преобразователя 12 в длительность импульса, пропорциональную этому напряжению, и на выходе преобразователя 13 появляется отрицательный скачок напряжения (0-,/7i). Положительный скачок напрял ения (-tVi-нО) появляется через время Г, которое должно быть пропорционально измеряемому напряжению. Следовательно, на выходе преобразователя образовался отрицательный импульс, длительность которого пропорциональна измеряемому напряжению. Генератор импульсов 16 вырабатывает импульсы, которые пропускаются ячейкой «К 17. Работой ее управляет триггер 15, который находится в единичном состоянии в течение времени Т. Начальное состояние этого триггера - нулевое. Прн срабатывании реле 18 положительный импульс напрянсения через схему «ИЛИ 14 перебрасывает триггер 15 в единичное состояние, в котором он находится до тех пор, пока положительный перепад напряжения преобразователя 13, пройдя через схему «ИЛИ 14, через время Т не перебросит его вновь в нулевое состояние. Следовательно, ячейка «И 17, подключенная к правому плечу григгера 15, находится в рабочем состоянии только время Т и пропустит с генератора импульсов 16 количество импульсов «я, пропорциональных 7, а значит, и измеряемому напряжению. Эти имнульсы в каждом замере проходят на вход запоминающего устройства 3 и суммируются в течение цикла работы оптимизатора с теми, что были записаны там ранее. Значит, после каждого замера в заноминающем устройстве хранится количество иимпульсов Zni, где ni - количество импульсов в каждом t-ом замере. В результате в конце цикла в запоминающем устройстве образуется величина, пропорциональная среднему значению функции в течение цикла. Эта величина будет тем ближе к ее истинному значению, чем больше замеров будет сделано в течение цикла, так как при больше.м количестве замеров более полно снижается влияние помехи на результат измерения вследствие ее усреднения, если помеха является случайной стационарной функцией от времени.

Запоминающее устройство 3 выполнено по схеме двоичного счетчика. Импульсы с ячейки «И 17 поступают на первый его триггер 19. Количество разрядов запоминающего устройства выбирают из условия непереполнения счетчика. Цикл работы онтимизатора задается с помощью кольцевого счетчика 4. Кольцевой счетчик, содержащий триггеры 20, 21 и 22 - основной логический элемент схемы, так как он управляет почти всеми логическими операциями оптимизатора. Счетчик собран ио схеме двоичного счетчика и дополнен схема.ми «И 23 и 24 (промежуточные ячейки на чертеже не показаны), схемой «ИЛИ 25 и ключами 26 и 27 (управление ключами осуществляется с передней панели лрибора) по числу схем «И. Его настраивают на определенное время цикла (которое можно менять), т. е. на определенное число замеров. Пусть, например, кольцевой счетчик настраивают на количество импульсов (k...n). Каждый раз при Срабатывании реле 18 положительный импульс напряжения поступает на первый триггер 20 кольцевого счетчика. Когда реле 18

срабатывает 2-ый раз, на правом плече ()-ого трнггера 21 счетчика в первый раз за цикл возникает положительный импульс напряжения. Этот импульс пропускается (/(-1)-ой ячейкой «И 23, на которую в начале

работы было подано питающее напряжение через триггер 20 от источника питания счетчика на ноль. С ячейки «ИЛИ 25 импульс идет на управление логическими операцияА1Я оптимизатора, поступая на блок линий задержки 29. Этот блок состоит из четырех линий задержки. С каждой из них импульс, задержанный относительно предыдущего имиульса на время, необходимое для последнего замера цикла и залиси измеренного знпчения функции в запоминающее устройство 3, поступает на ячейки «И 30-33. Последние подключены к левым плечам триггеров 19, 34, 35 и 36 запоминающего устройства, и с тех ячеек, которые подключены к триггерам, находящимся в нулевом сОСтоянии (левое плечо единичное), импульсы подаются на входы соответствующих ячеек «ИЛИ 37-40 и далее на входы триггеров 41-44 олерационного блока 5. Таким образом, с запоминающего устройства снимается записанное там среднее значение /ср (x)fcp (х) проиорционально (x)l в обратном коде и поступает на операционный блок, где суммируется с занисанным там ранее числом, т. е.

это равнозначно Операции вычитания

f/cp (x)fi -flcp(), так как (х) поступает в обратном коде, fjcpW записано в прямом. Затем с бло:ка 29 поступает второй

импульс на считывание результата вычитания из операционного блока. Олерационный блок состоит из триггеров 41-44, линий задержки 45 и 46 и блока реверса, состоящего из ключей 47-49, управляемых реле 50, лиНИИ задержки 51 и 52 и схемы «ИЛИ 53. Триггер 44 является триггером знака. Иа него поступают импульсы знака триггера ЗС запоминающего устройства. Триггер 36 всегда находится в нулевом состоянии, но с левого плеча снимается импульс, поступающий на триггер 44, когда число из запоминающего устройства поступает на олерационный блок в обратном коде. При этом иаипульс переполнения перебрасывает триггер 44 в ноль, но

переноса в младший разряд при суммировании на данном участке не происходит. Это искажает результат вычисления на единицу, но такая ошибка на работе оптимизатора не сказывается в силу принципа его дейСтвия.

как не требуется специального сброса операционного блока. Третий импульс с блока 29 цоступает на ячейки «И 54-57, подключенные к правым плечам триггеров 19 и 34 запоминающего устройства, и число переписывается оттуда Б прямом коде в операционный блок. Четвертый импульс с блока задержки 29 сбрасывает запоминающее устройство в нулевое состояние, и оптимизатор готов к работе в следующем цикле. Из сказанного ясно, что частота работы коммутатора должна выбираться из условия, чтобы все логические операции успели выполниться за время от момента прихода последнего импульса предыдущего цикла до прихода первого импульса следующего цикла. Во втором и последующих циклах оптимизатор в основном повторяет работу в первом цикле. Разница лишь в том, что в первом цикле в операционном блоке производится операция Q-fi(x), а в последующих f (х)-fi+i (х) и со второго цикла подобного шага не делается, о чем будет сказано ниже.

Величина приращения «з операционного блока считывается с помощью генератора импульсов 58, триггера 55 и ячейки «И 60 методом переполнения.

Генератор импульсов 58 вырабатывает импульсы, которые пропускаются ячейкой «И 60 на вход первого триггера 41 операционного блока, и эти же импульсы поступают на вход исполнительного блока 6, а через ячейки 61 и 62 - на вход реверсивного счетчика исполнительного блока. Реверсивный счетчик состоит из триггеров 63-65, ячеек «ИЛИ 66-68, ячеек «И 69 и 70, подсоединенных к левым плечам триггеров и осуществляющих сквозной перенос при вычитании импульсов, а также ячеек «И 71 и 72, подсоединенных к правым плечам триггеров и осуществляющих сквозной перенос при вычитании импульсов.

Через ячейку «И 60 импульсы проходят до заполнения операционного блока. При поступлении следующего имнульса операционный блок переполняется и с последнего его триггера 43 снимается положительный импульс, перебрасывающий триггер 59 из единичного состояния в нулевое. Этот триггер управляет ячейкой «И 60, следовательно, она закрывается и не пропускает больше импульсов с генератора импульсов. Таким образом, через ячейку «И 60, а значит, и на вход исполнительного блока прошло количество импульсов, которое соответствует дополнительно1му входу числа, записанного в операционном блоке. Для более простой и надежной работы исполнительного блока в момент считывания в операционном блоке должно быть записано число в обратном коде, чтобы на исполнительный блок оно поступало в прямол коде.

ходе импульса считывания с блока линий задержки 29 на выходе ячейки «1-1 73 появляется импульс, который поступает на блок 59, и ключи 47-49 размыкаются на некоторый промежуток времени. С линии задержки 51 импульс поступает на все триггеры операционного блока, кроме триггера знака, и перебрасывает их. Ключи 47-49 вновь замыкаются. В операционном блоке образуется

число в обратном коде. С линии задержки 5/ импульс проходит через линию задержки 52, поступает на ячейку «ИЛИ 53, а с нее на триггер 59, который перебрасывается в единичное состояние, и начинается считывание.

Если число в операционном блоке к моменту начала считывания было отрицательным, то при приходе импульса считывания на выходе ячейки «И 74 возникает импульс, который непосредственно через ячейку «ИЛИ

53 поступает на вход триггера 59 и происходит считывание.

Триггер 59 имеет два раздельных входа. Иа первый вход поступают илшульсы с ячейки «ИЛИ 53, перебрасывающие его в единичное состояние, а на второй - импульс переполнения с триггера 43, возвращающий его в нулевое состояние. Это сделано для того, чтобы при переполнении операционного блока при вычитании, когда fi(x)f{+i(x) не

произошло ложного срабатывания триггера 59.

Исполнительный блок представляет собой реверсивный счетчик, в который входят: триггеры 63-65, ячейки «ИЛИ 66-68, ячейки

«И 69 и 70, подсоединенные к левым плечам триггеров 63-65 и осуществляющие сквозной перенос при вычитании импульсов; ячейки «И 71 и 72, подсоединенные к правым плечам триггеров и осуществляющие

сквозной перенос при сложении импульсов; триггер реверса 63; ячейки «И 61 и 62, подсоединенные к его плечам; преобразователь 75 код-аналог; ключ 76. В нем все время хранится текущее значение регулируемого параметра для нормальной работы регулятора.

Перед началом работы оптимизатора реверсивный счетчик настраивают на сложение импульсов, поступающих с ячейки «И 60, т. е. триггер реверса 63 находится в нулевом

состоянии. В первом цикле работы оптимизатора в операционном блоке перед считыванием будет записано начальное значение функции в обратном коде. Следовательно, на реверсивный счетчик через ячейки «И 69 и

70 будет поступать значение регулируемого параметра. Затем делается пробный шаг, и на реверсивный счетчик после второго цикла будут поступать приращения регулируемого параметра. Если приращение отрицательное,

направление движения к экстремуму не меняется. Если же приращение положительное, то е ячейки «И 73 снимается импульс, который перебрасывает триггер 63 в единичное состояние, и импульсы с ячейки 60 поступают

Даты

1968-01-01—Публикация