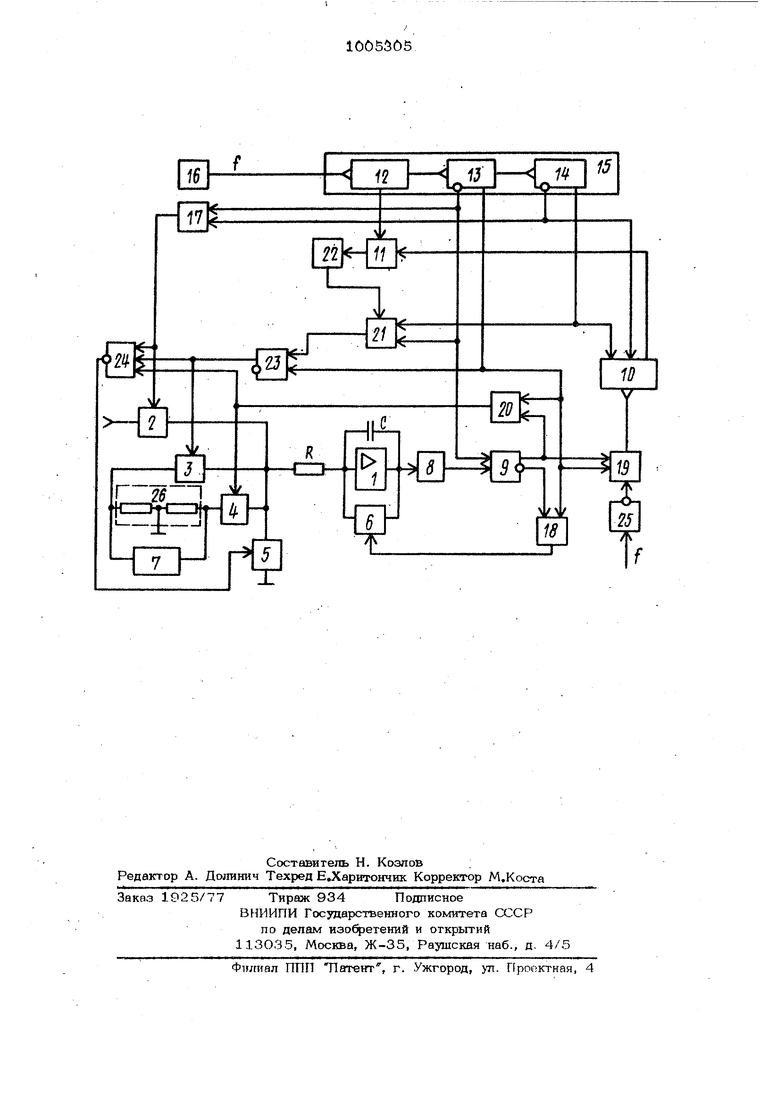

Изофегение относится к технике аналого-цифрового преобразователя и мо жет быть применено в устройствах ввода информации в управляющие ЦВМ и цифровых вольтметрах, работающих по методу двухтактного интегрирования. Известно устройство, содержащее интегратор, выход которого соединен с устройством сравнения, выход последнего подключен к нулевому входу -тригге управления, ключ, генера-тор импульсов,-э мент И, счетчик импульсов и источник эталонного напряжения С11 . Этому устройству присущи погрешности, связанные с температурным и временным дрейфами, а также существенный недостаток, препятствующий его широному применению - нелинейная связ между входным и выходным кодом. Известен также преобразователь, реа лизующий метод двухтактного интегрирования и содержащий интегратор, вьшолненный на операционном усилителе, вкод которого через ключи подключен к ышне входного сигнала и к источнику эталонного напряжения, а выход соединен со входом компаратора, оцкп выход коггорога соединен с входом установки триггера в нулевое состояние, а второй вход с входом установки триггера в единичное состояние, выход последнего соединен с первым входом элемента И, второй вход которого соединен с выходом генератора, выход элемента И подключен к счетному входу счетчика, его выход к блоку управления, содержащего триггеры и логические элементы Tsl . К недостаткам этого преобразователя следует отнести влияние на точность преобразования температурного и временного дрейфа интегратора, компаратора и аналоговых электронных ключей. Целью изобретения является повыше- ние точности аналого-цифрового преобразования. Для достижения поставленной цели в аналого-цифровой преобразователь, содержащий интегратор, выполненный на операционном усилителе, вход которого через первый, второй и третий ключи подсоединен к шине входного сигнала и к клеммам эталонного источника напряжения, соответственно, выход интеграТора через когипаратор соединен с первьп входом триггера управления, генератор, выход которого подсоединен ко входу - четчика времени, включающего последо вательно соединенные счетчик времени такта, триггеры тактов. и хниклов, нулевые выходы которых подсоединены ко .Входам первого элемента И, выход-которого подсоединен к управляющему входу первого ключа, нулевой и единичный выходы триггера циклов подсоединены к первому, и второму входам управления кодирующего счетчика, соответственно, конденсатор интегратора зашунтирован четвертым ключом, управляющий вход которого подсоединен к выходу элемента И, перкые входы второго, третьего и четвертого элементов И соединены с единичным выходом триггера тактов, нулевой выгсод которого соединен со вторым входом триггера управления, нулевой выхрд которого соединен со вторьпи входом второго элемента И, .а единичный - со вторыми входами треть его и четвертого элементов И, выход третьего элемента И подсоединен к счет ному кодирующего счетчика, управ ляклций вход третьего ключа подсоединен к выходу четвертого элемента И, в него дополнительно введены цифровые устрой- .ство сравнения, первый и второй элементы временной задержки, пятый элемент И, пятый ключ, элемент ИЛИ-НЕ и триггер подключения сшорного напряжения, причем выход последнего соединен с nepBbiM входом элемента ИЛИ-НЕ и с управляющим входом второго ключа, а входы установки в О и 1 подсоединены к единичному выходу триггера тактов и выходу пятого элемента И, соответственно, первый вход последнего соединен с единичным выходом триггера циклов, второй вход - с нулевым выходом триггера тактов, а третий вход через первый элемент временной .задержки соединен с выходом цифрового устрой ства сравнения, первая группа в;ходов которого соединена с выходами триггеро счетчика времени такта, а вторая группа входов - с выходами триггеров кодирующего счетчика, причем клеммы этало ного источника напряжения череа резисто ры подсоедине гы к нулевой шине, а выхо генератора через вггорой элемент времен ной задержки подсоединен к входу третьего элемента И, при этом вход интегратора через пятый ключ, управляющий вход которого соединен с выходами элемента ИЛИ-НЕ, подсоединен к нулевой шине, причем второй и третий входы элемента ИЛИ-НЕ соединены с выходами первого и четвертого элементов И, соответственно. На чертеже изображена блок-схема устройства. Устройство содержит интегратор 1, вьшолненный на операционном усилителе, ключи 2-6, эталонный источник напряжения 7, компаратор 8, триггер управления 9, кодирующий счетчик 10 цифровое устройство сравнения 11, счетчик времени 12, триггер тактов 3, триггер циклов 14, счетчик времени 15, генератор 16 с частотой , элементы И 17 - 21, элемент временной задержки на 4-22, подключения on oJ3Horo напряжения 23, элемент ИЛИ-НЕ, 24,элемент временной задержки на О,5 J- 25, резистивный делитель напряжения 26. Кроме того, приняты :ледуюоше обозначения:и.х - входной сигнал; Ug - эталонное напряжение; U(jp- опорное напряжение; ЬХ. .- Время интегрирования входно го сигнала; t| - время интегрирования опорного напряжения; -t - временной интервал,, соответствующий входному сигналу; t - временной И1гт«фв, соответствующий опорному напряжению;е - приведенное ко входу интегратора суммарное значение напряжения дрейфа; fltj,2J-tQ- погрешности формирования временных интерв(шов; i , номинальные значения временных интервалов; NV- код преобразования параметра;Ngir код преобразования опорного напряжения; Nj - номинальный код параметра; ANj(-. ошибка кодирования. Устройство работает следующим образом. От генератора 16 работает счетчик времени 15. Счетчик времени 15 включает счетчик времени такта 12, триггер тактов 13, триггер циклов 14, .представляющие собой по отношению к . счетчику времени такта последукише разряды. Когда триггеры тактов 13 и циклов 14 находятся в состоянии О, включается ключ 2, и интегрируется входной сигнал. В состоянии . триггера тактов 13 происходит формирование временного интервала, с подзчетом заполНЯКЩИХ импульсов КОДИруКШгаМ СЮТЧИком 1О, по окончании временного интервала триггер управления 9 перебрасывается в О сигналом компаратора 8, и счёт прекращается. При СОСТОЯ1ШИ триггера циклов 14 и О триггера тактов 13 производится интегрирование опорногчэ напряжения, начиная с момента, определяемого гшфровьпи устройством сравнения 11, которое вырабатывает сигнал рввенст-. ва кода, офазуемого инверсными выхода ми триггеров кодирующего счетчика Ю, и кода счетчика времени такта 12, npHf чем момент включения ключа 3 задерживается элементом временной задержки 2 2 относительно момента формирования импульса цифровым устройством сравнения 11 на время, с.оответствующее временному дискрету, т.е. на период генератора 16. При преобразовании входного сигнала на кодирующем счетчике Ю идет сложение, при преобразовании опорного напряжения - вычитание. Эталонное и опорное напряжения формируются на двух плечах прецизионного резистивного делителя 26, подключенного к эталонному источнику напряжения, причем средняя точка делителя подсоединена к общей шине устройства. Отн шение сопротивления плеч делителя 1-1 По окончанию временного интервала замыкаются ключи 5 и 6, конденсатор интегратора 1 разряжается до нуля. Ключ 6 размьшае-тся при перекоде триггера тактов 13 в О, ключ 5 - с момента начала интегрирования. Таким образом, получение кода сигна ла занимает цикл, включающий четьфе такта, из них два занимают преобразование МхзДва - преобразование UonПогрешность, возникающая из-за дрей фа операционного усилителя интегратора, можно разпелить на аддитивную и мул1 типликатную (погрешность масштаба) составляющие. Для того, чтобы скомпенс фовать обе указанные составляющие погрешности, используется алгоритм, реализуемый в предлагаемой схеме. Учитывая дрейф интегратора, U.+ e „ t ь WошибкаЛ-t - 4- И i- I е Ч-) Так как ключ 6 шунтирования емкоти как при преобразовании и ри преобразовании Uj( в такте интегриования разомкнут в одно и то же врея, время интегрирования дрейфа в обех случаях одинаково, и ошибка преобазования и,. on имеет вид ОП ., АЧ) Из уравнений (2) и (3) при услоииХ,1 j.0n и - . т.е. номинальное значение временных тгсервалов, формируемых при преобразовании УХ ОП должно совпадать. Если -t -номинальный временной тгторвал при определенном U/ , и задать п то при ion txf И Aijjj,Atj, Если при получении -if вычесть д у дЧ;лрлТо получим -t которое, во-первых, есть неис1хаженное значение временного интервала, во вторьпс, опредепяет требуемое значение t , при котором Д х-Процесс определения требуемого tS носит итерационный характер; преобраэуется Ux ; преобразуется tu -fcv ., выявляется oшибкaf преи - - Xобразуется Ux i причем -tx корректируется на величину ошибки; преобразуется Цх при-b z-t выявляется уточненИлнее значение ошибки, преобразуется Uy с учетом уточненного значения ошибки и т.д. В реальных схемах, процесс итерадиовного приближения носит очень быстрый знакопеременный характер. Изменение не вносит погрешности, так как частота преобразований У выбирается, исходя из взменений Ux между двумя 7 преобразованияMTi на 1, максшюум НЕЗСколько дискрет Ш1ФРОВОГО аналога Из формулы (2) видно, что т. к.тт- 1 ,изменение лЧ;х этом будет составпять малые доли дискрета. Таким образом, необходимо подчерк нуть, что процесс итервяионности прибт лижения выполняется автоматически в ходе преобразований, снятие кода параметра производится в каждый цикл. При итерационном процессе в кодирующем счетчике Ю к началу нового цикла остается код коррекции ошибтш, полученный в предыдущем цикле. Импульсы счета, поступакяцие на счетчик 10, сдвинуты относите льно импульсов, поступающих на счетчик вре мени, на половину периода, например, элементом задержки 25, который при скважности частоты генератора, равной 2, представпяет собой просто эл мент инверсии НЕ. Этим достигает ся значение ошибки дискретизации временного интервала в пределах iO,5--j 1ак как время интегрирования ; определяется по коду параметров в сче чике 1О, оно на 0,5 дискрета зболыие точного значения , соответствующе™ го моменту смены кода (Мх-1) на код NV и при этом времени t достигает ся максимальная вероятность получения кода NQP, равного нескорректированному значению кода параметра J , т.е. минимальное значение случайной погреш кости на коррекцию 4° IN П Х 0,5 . Nx.-f torv N +T где -tf - момент смены кода ( ) на код -till - момент смены кода NvHa код .; (NX+-I), причем момент ton максимально отстоит обоих граничных моментов временного дискрета, при переходе которых имела бы .место ошибка кода единицу дискрет Для реализашга равенства (9) служит цифровое устройство сравнения 11, триггер 23, элемент задержки 22, элемент 21, на который через элемент 22 поступает сигнал цифрового устройства сравнения 11, разрешает включение клю ча 3 в ппределснном такте - такте интегрирования Ufjp. б58 На устройство 11 подаются прямые выходы триггеров счетчика времени такта 12 и инверсные кодирующего счетчика 1О (либо наоборот), элемент временной задержки 22 задерживает: импульс с выхода стройства сравнения на 4 j это обеспечивает длительность зйиыкания ключа 3 с момента установки триггера 23 в единичное состояние импульсом с элемента И 21 до момента установки его в нулевое состояние в связи сг окончанием такта, соответствукяцуто равенству (8). Положим, в начальный момент код коррекции равен О, код преобразования и в первом цикле . , Тде 0 ( э1 uNpj- суммарная аддиттивная составляющая погрешности, связанная црежде всего с дрейфом интегратора и дрейфом порога ко таратора. Ошибка кодирования в первом цикле f x m aКод (-Non)t полученный при преобразовании УОП в первом цикле -Щ-Mj.,J«.|vl..bl(11) ,4ЛN в следутацем цикле при кодировании и получается код (VNon)N«-d(.aNj ошибка кодирования . ПЗ) Так как | | л {, максимальная величина погрешности I ДМ М в конкретных случаях может удовлетворить требованиям к тохности преобразования. В этих случаях итерационный роцесс сводится к своему частному случаю к одноразовой коррекции по веичине N. Действительно, из (12) ,-N,,. .е. при преобразовании U заполняющая j частота должна подаваться на кодируюий счетчик 10 иепосрелгггвенно на 2-й разряд, на устройство сравнения 11 код счетчика 10 подается сдвинутым на (-1) разряд, т.е. 2-й разряд счетчика 10 сравнивается с 1-м счетчиком &ре- мени такта 12, и т. д. при кодировании Ujjn частота f подается, на первый разряд счетчика Ю и производится вычитание. Удобство такого процесса заключается в том, что значение поправки не должно запоминаться для коррекции в следующем цикле, счетчик 1О перед каждым циклом обнуляется, т.е. при многоканальном преобразовании с време ным разделением не требуются регистры для запоминания поправок по каждо- му NXV Сигнал сложение, поступахсишй на вход управления направлением счета реверсивного счетчика 10 во втором такте цикла, при этом используется так же как сигнал, пропускающий счетные импульсы на вход второго триггера без деления частоты на 2 первым разрядом счетчика 10. Формула изобретения Аналого-цифровой преобразователь, содержащий интегратор, вьшолненный на операционном усилителе,, вход которого через первый, второй и третий ключи подсоединен к шине входного сиг нала и к клемам эталонного источника напр жений соответственно, выход интегратора рез компаратор соединен с первым входо триггера управления, генератор, выхоц к торого подсоединен к вхоцу счетчика вре Нй.включающего последовательно соедин НЫ9 сметчик времени такта, триггеры тактов и циклов, нулевые выходы которых подсоединены к входампервого элемента И, выход которого подсоедине к управляющему входу первого ключа, нулевой и единичный выходы триггера циклов подсоединены к первому и второму входам управления кодирующего счетчика соответственно, конденсатор интегратора зашунтирован четвертым ключом, управляющий вход которого по ключен к выходу второго элемента И, первые входы второго, третьего и четвертого элементов И соединены с .единичным выходом триггера тактов. нулевой выход гкоторого соединен с вторым входом триггера управления, Нулевой выход которого соединен с вторым входом второго элемента И, а единичный - с вторыми входами третьего и четвертого элементов И, выход третьего элемента И подсоединен к счетному входу кодирующего счетчика, управляющий вход третьего ключа подсоединен к выходу четвертого элемента И, отличающ и и с я тем, что, с целью увеличения точности аналого-цифрового преобразов ния, в него дополнительно введены цифровое устройство сравнения, першлй и второй элементы временной задержки, пятый элемент И, пятый ключ, элемент ИЛИ-НЕ и триггер подключения опорного напряжения, причем выход последнего соединен с первым входом элемента ИЛИ-НЕ и с управляющим входом вггорого ключа, а входы зпстановки в О и 1 подсоединены к единичному выходу триггера тактов и выходу пятого элемента И соот-. ветственно, первый вход последнего соединен с eдини raы выходом триггера циклов, второй вход - с нулевым выходом триггера тактов, а третий вход через первый элемент временной задержки соединен с выходом цифрового устройства сравнения, первая группа входов которого соединена с выходами триггеров счетчика времени такта,. а вторая группа входов - с выходами триггеров кодируклдего счетчика, причем клеммы эталонного источника напряжения через резисторы подсоединены к нулевой шине, а выход генератора через второй элемент временной задержки подсоединен к входу третьего элемента И, при этом вход интегратора через пятый ключ, упр 1вляющий Вход которого соединен с выходом элемента ИЛИ-НЕ, подсоединен к нулевой шине, причем второй и третий входы элемента ИЛИ-НЕ соединены с выходами первого и четвертого элементов И соответственно. Источники информации, принятые во внимание при экспертизе 1.Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия, 1970, с. 334-336, рис. 7-6а. . 2.Авторское свидетельство СССР № 132863, кл. Н 03 К 13/20, 1960 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Цифровой термометр | 1986 |

|

SU1404844A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Цифровой инфранизкочастотный широкополосный фазометр мгновенных значений | 1986 |

|

SU1368806A2 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1246376A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Аналого-цифровой преобразователь двойного интегрирования | 1981 |

|

SU1001464A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

Авторы

Даты

1983-03-15—Публикация

1974-05-31—Подача