Известные феррит-диодные сумматоры содержат большое количество различных элементов, что снижает их надежность, быстродействие и экономичность.

Предложенный феррит-диодный последовательный сумматор отличается тем, что в нем выходы первого универсального логического элемента, соответствующие равнозначным выходным сигналам, соединены с выходными обмотками одного из сердечников второго универсального элемента, а выходы, соответствующие разнозначным сигналам, соединены с входной обмоткой другого сердечника второго универсального элемента, причем одна из обмоток, соответствующих равнозначным сигналам, соединенная по выходу с входной обмоткой, соответствующей разнозначным сигналам, включена на один из входов элемента задержки, на второй вход которого подключен выход другой входной обмотки второго универсального элемента, соответствующей равнозначным сигналам.

Предлагаемая схема сумматора позволяет значительно сократить число элементов и повысить быстродействие при суммировании последовательных кодов, причем основной выигрыш получается за счет съема с одного универсального элемента двух различных логических функций, а именно функции «отрицание равнозначности» (сумма) и функции «И» (перенос) двух переменных.

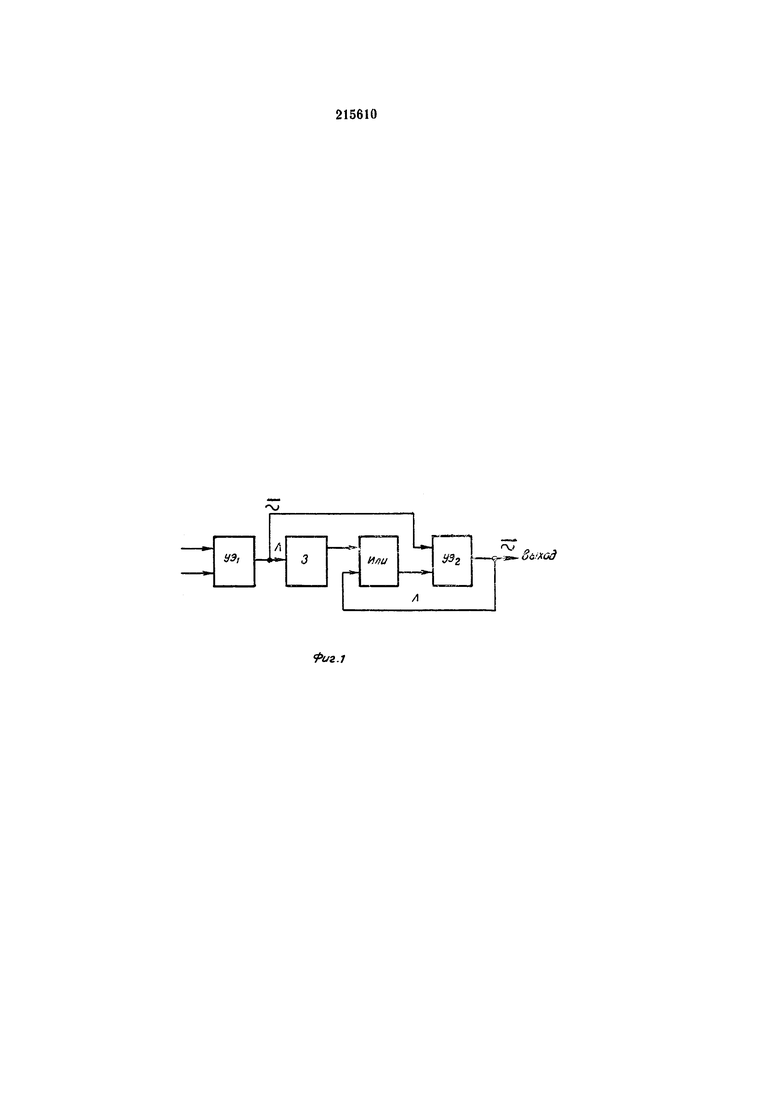

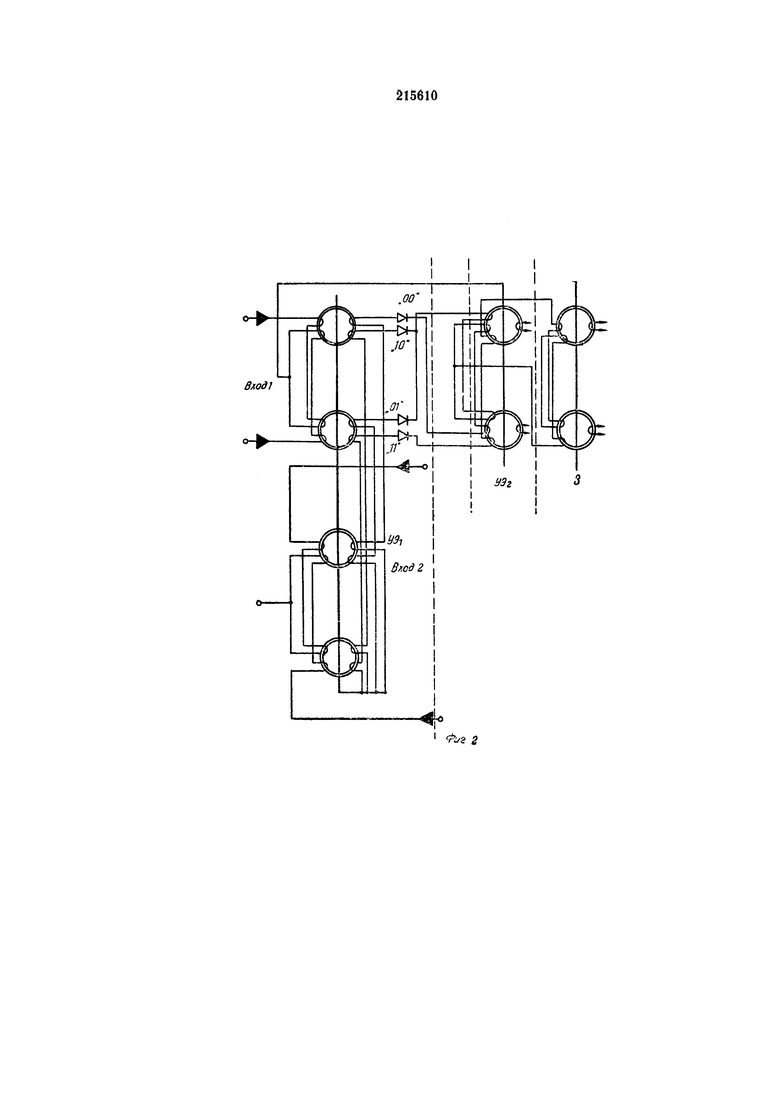

На фиг. 1 приведена структурная схема сумматора; на фиг. 2 - схема соединений универсальных элементов и элемента задержки. |

Сумматор содержит универсальные логические элементы (УЭ1 и УЭ2), элемент З задержки, и элемент «ИЛИ».

Элементы УЭ1 и УЭ2 дают возможность снимать с их выходов две логические функции (отрицание равнозначности и «И»), а элементы З и «ИЛИ» согласуют во времени работу сумматора.

Если ток выхода элемента УЭ1 коммутируется в ветвь «OO», то, проходя на вход элемента УЭ2, он записывает «О» -и далее записывает «О» на элементе З.

Если ток выхода элемента УЭ1 коммутируется в ветви «10» или «01» (они объединены), то, проходя на вход элемента УЭ2, он записывает «1», а далее через среднюю точку этим же током записывается «О» на элементе З.

Если ток выхода элемента УЭ1 коммутируется в ветвь «11», то в элементе УЭ2 он записывает «О», а в элементе З происходит запись «1» (вход - верхний сердечник).

Одновременное получение результатов суммы и переноса позволяет приблизительно в два раза сократить число сердечников и диодов по сравнению с существующими феррит-диодными схемами, повысить быстродействие, экономичность и надежность работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНЫЙ ФЕРРИТ-ДИОДНЫЙ КОММУТАЦИОННЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1968 |

|

SU207474A1 |

| П- V 'I! ^ | 1967 |

|

SU190416A1 |

| УНИВЕРСАЛЬНЫЙ ФЕРРИТ-ДИОДНЫЙ КОММУТАЦИОННЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU375793A1 |

| ФЕРРИТ-ДИОДНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГОДЕЙСТВИЯ | 1968 |

|

SU218519A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1968 |

|

SU217714A1 |

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА БИАКСЕ | 1967 |

|

SU195718A1 |

| ПИРАМИДАЛЬНЫЙ ДЕШИФРАТОР | 1973 |

|

SU385271A1 |

| Цифровой анализатор спектра | 1980 |

|

SU900210A1 |

| СПОСОБ ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ НА ЗАПОМИНАЮЩЕМ ЭЛЕМЕНТЕ | 1966 |

|

SU224160A1 |

Феррит-диодный сумматор последовательного действия, содержащий два универсальных феррит-диодных коммутационных логических элемента, элемент задержки и элемент «ИЛИ», отличающийся тем, что, с целью упрощения устройства, повышения быстродействия, экономичности и надежности работы, выходы первого универсального логического элемента, соответствующие равнозначным выходным сигналам, соединены с входными обмотками одного из сердечников второго универсального элемента, а выходы, соответствующие разнозначным сигналам, соединены с входной обмоткой другого сердечника второго универсального элемента, причем одна из обмоток, соответствующих равнозначным сигналам, соединенная по выходу с входной обмоткой, соответствующей разнозначным сигналам, включена на один из входов элемента задержки, на второй вход которого подключен выход другой входной обмотки второго универсального элемента соответствующей равнозначным сигналам.

Авторы

Даты

1968-06-20—Публикация

1967-02-06—Подача