Известны способы выполнений логических операций на запоминающем элементе с импульсно-фазовой модуляцией двоичных чисел.

Предлагаемый способ отличается тем, что сигналы первой и второй групп подают на первом интервале цифрового периода и запоминающий элемент переводят в состояние «0» или подтверждают это состояние, причем сигналы первой группы обозначают «1» в текущем цифровом периоде, а сигналы второй группы - «0» в предшествующем периоде; формируют на выходе сигнал «0» предшествующего периода при переводе запоминающего элемента в состояние «0», подают сигнал перевода запоминающего элемента в состояние «1» на втором интервале цифрового периода, если его значение равно «1», подают сигналы первой и второй групп на третьем интервале цифрового периода и переводят запоминающий элемент в состояние «0» или подтверждают это состояние, причем сигналы первой группы обозначают «0» в текущем цифровом периоде, а сигналы второй группы - «1» в текущем цифровом периоде; формируют на выходе сигнал «1» текущего периода при переводе запоминающего элемента в состояние «0», подают сигнал перевода запоминающего элемента в состояние «1», на четвертом интервале цифрового периода, если его значение равно «0». Это позволяет унифицировать систему используемых элементов.

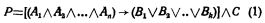

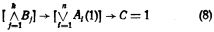

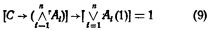

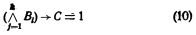

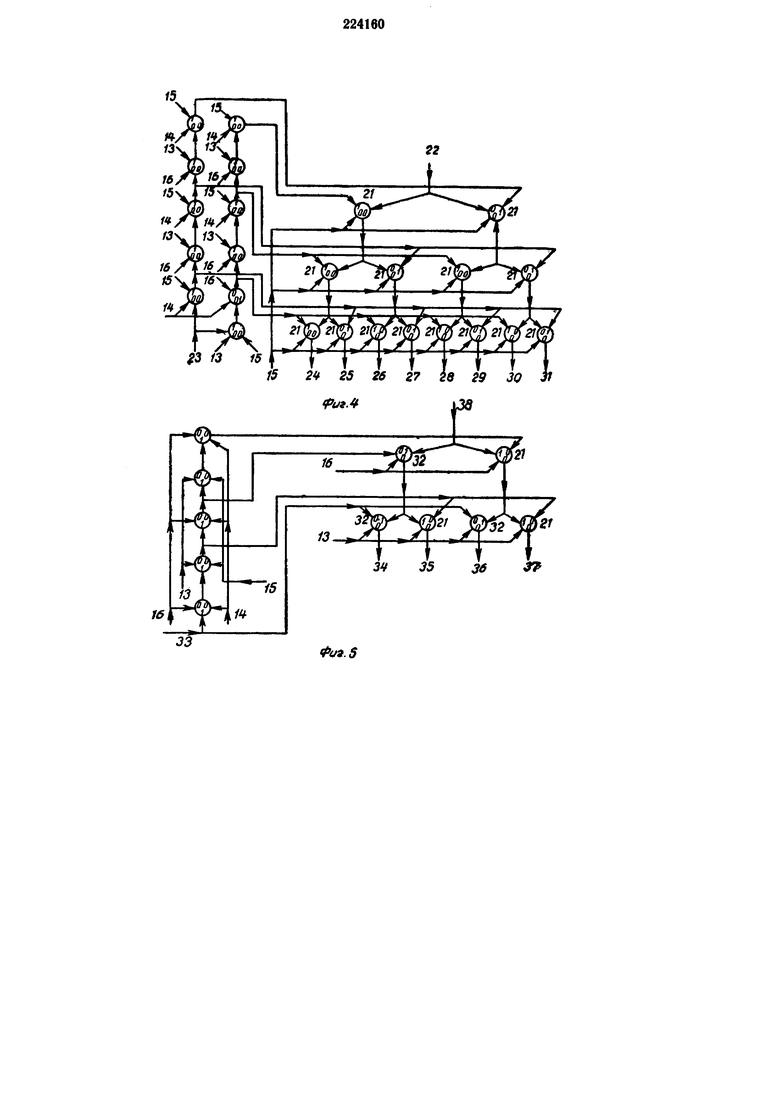

На фиг. 1 представлена блок-схема запоминающего элемента, реализующего логическую операцию согласно предлагаемому способу; на фиг. 2 - графики и таблица значений входных и выходного чисел, поясняющие принцип работы блок-схемы на фиг. 1; на фиг. 3 - блок-схема и принципиальная схема последовательного сумматора; на фиг. 4 - схема дешифратора на пирамидах из элементов «И»; на фиг. 5 - схема дешифратора на пирамидах из элементов «И» и «запрет».

Запоминающий элемент 1 (фиг. 1) переводится в состояние «0» любым из сигналов первой группы (A1-An), поступающих по шинам 2, 3, 4, и любым из сигналов второй группы (B1-Bk), поступающих по шинам 5, 6, 7, и переводится в состояние «1» сигналом C, поступающим по входу 8.

Выходной сигнал Р поступает на шину 9 при переводе запоминающего элемента из состояния «1» в состояние «0». Цифрами «0» и «1» против входных стрелок обозначено состояние запоминающего элемента, в которое он переводится поступившим по данному входу (шине) сигналом.

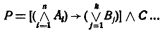

Схема позволяет реализовать за каждый цифровой период зависящую только от значений в этом периоде разрядов (цифр) входных чисел логическую операцию конъюнкции цифры числа типа C с импликацией двух цифр, первая из которых является конъюнкцией по цифрам всех n входных чисел группы А, а вторая - дизъюнкцией по цифрам всех k входных чисел группы В, т.е.

или

Указанная логическая операция реализуется только при следующих условиях:

а) подача на входы ячейки сигналов, переводящих триггер в состояние «0», должна быть отделена по времени от подачи сигналов, переводящих триггер в состояние «1», причем минимальный интервал определяется необходимым временем перехода триггера в предшествующее моменту подачи сигнала состояние «0» или «1»;

б) входные числа должны быть сфазированы таким образом, чтобы текущие цифровые периоды чисел группы А опережали, а чисел группы В - отставали относительно текущего цифрового периода числа типа С. Сдвиг фаз должен быть такой величины, чтобы:

сигналы, изображающие значение «1» для чисел группы А в текущем и «0» для чисел группы B в предшествующем периодах, находились между сигналами, изображающими значения «0» предшествовавшего и «1» текущего периодов числа типа С;

сигналы, изображающие значения «0» для чисел группы А и «1» для чисел группы B в текущем периоде, находились в интервале между сигналами, изображающими значения «1» и «0» числа типа С в текущем периоде;

сигналы, изображающие значения «1» для чисел группы А в последующем и «0» для чисел группы B в текущем периодах, находились в интервале между сигналами, изображающими значения «0» в текущем и «1» в последующем периодах числа типа С;

в) к моменту, совпадающему с положением сигнала, изображающего значение «1» для числа типа С в каждом цифровом периоде, с запоминающего элемента должна быть обязательно списана «1». Запоминающий элемент к этому моменту должен быть в состоянии «0».

При реализации логических операций по данному способу сигналы, изображающие в текущем периоде значения «1» и «0» выходного числа P, находятся в том же интервале относительно сигналов числам типа С, что и входные сигналы чисел группы B в текущем периоде.

Для выполнения условия перевода триггера в состояние «0» к моменту, совпадающему с положением сигнала «1» числа типа С, при наличии неблагоприятных (для этого периода) сочетаний значений разрядов входных чисел, над которыми производится логическая операция, на вход триггера дополнительно может быть подано основное число, принимающее постоянное значение разрядов, эквивалентное нулю для числа группы В. Использование для этих целей сигнала, эквивалентного В const = 0, наиболее удобно.

Приведенные на фиг. 2 временные графики и таблица, поясняющие работу схемы универсальной логической ячейки при nυ=kυ=2 (nυ, kυ - количество входных чисел групп А и В соответственно, принимающих переменные значения разрядов), могут служить подтверждением правильности формулы (1) и необходимости для реализации этой операции условий.

На графиках (фиг. 2) цифре «1» соответствует наличие сигнала (импульса) в начале цифрового периода, а цифре «0» - наличие сигнала (импульса) в середине цифрового периода. Сигналы (импульсы) «1» и «0» входных и выходных чисел обозначены черточками вверх от оси времени, начала цифровых периодов этих чисел обозначены черточками вниз от оси времени. На графике, изображающем сигналы выходного числа Р, точками на оси времени обозначены моменты времени записи «1» в триггере.

На приведенных графиках начало каждого «текущего» цифрового периода чисел группы А опережает, а чисел группы В - отстает на фазу, равную четверти цифрового периода, относительно начала соответствующих цифровых периодов числа типа С. При этом период входного числа Р находится в фазе с периодом чисел группы В.

Для обеспечения благоприятных сочетаний значений разрядов входных чисел на вход триггера подается также число B3 принимающее постоянное значение разрядов, равное нулю (см. графики фиг. 2). На этих же графиках для пояснения фазирования заштрихован один из «текущих» периодов для всех чисел.

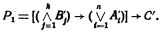

Примечание. Приведенное выше справедливо и в случае применения обратного (по отношению к принятому в описании) кодирования. В этом случае значения сигналов «0» и «1» меняются местами, а формула (1) принимает вид:

В приведенной формуле (1) количество входных чисел группы А и группы В может быть любым в пределах от нуля до mmax - максимально допустимого количества основных входных чисел для конкретного триггера, причем отсутствие чисел группы В эквивалентно Bj=0, а отсутствие чисел группы А эквивалентно Ai=1. При этом на вход триггера должно быть в любом случае подано число типа С, принимающее либо переменные, либо постоянные значения разрядов.

Для реализации более простых, чем в общем случае (формула 1), логических операций в пределах этого общего случая на вход триггера может быть подано меньшее количество входных чисел, причем некоторые из них могут принимать постоянное значение разрядов. Применяя известные приемы синтеза схем логических устройств, при, достаточном количестве элементов можно на основе предложенного способа реализовать любую логическую операцию.

Для составления схем логических устройств лучше всего применить сигналы четырехфазного тактового питания - четыре последовательности тактовых сигналов (импульсов), периоды которых равны цифровому и сдвинуты последовательно на фазу, примерно равную четверти цифрового периода. Эти тактовые сигналы применяются в качестве постоянных значений разрядов входных чисел, к ним привязываются (по фазе) сигналы «1» и «0» входных и выходных чисел. Фазирование четырех последовательностей тактовых импульсов t1, t2, t3 и t4 можно проследить по графикам фиг. 2.

Способ и его достоинства поясняются примером.

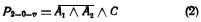

На феррит-транзисторной ячейке «ИЛИ», имеющей три основных входа и один подготовительный, можно выполнить следующие логические операции при полном задействовании ее входов и при подаче на один вход только одного числа:

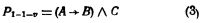

А) при переменном значении разрядов числа типа С (Сυ):

при nυ=2, kυ=0

при nυ=kυ=1

при nυ=0, kυ=2.

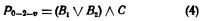

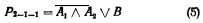

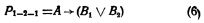

Б) при постоянном значении разрядов числа типа С, равном единице (С const),

при nυ=2, kυ=1

при nυ=1, хυ=2

при nυ=0, kυ=3.

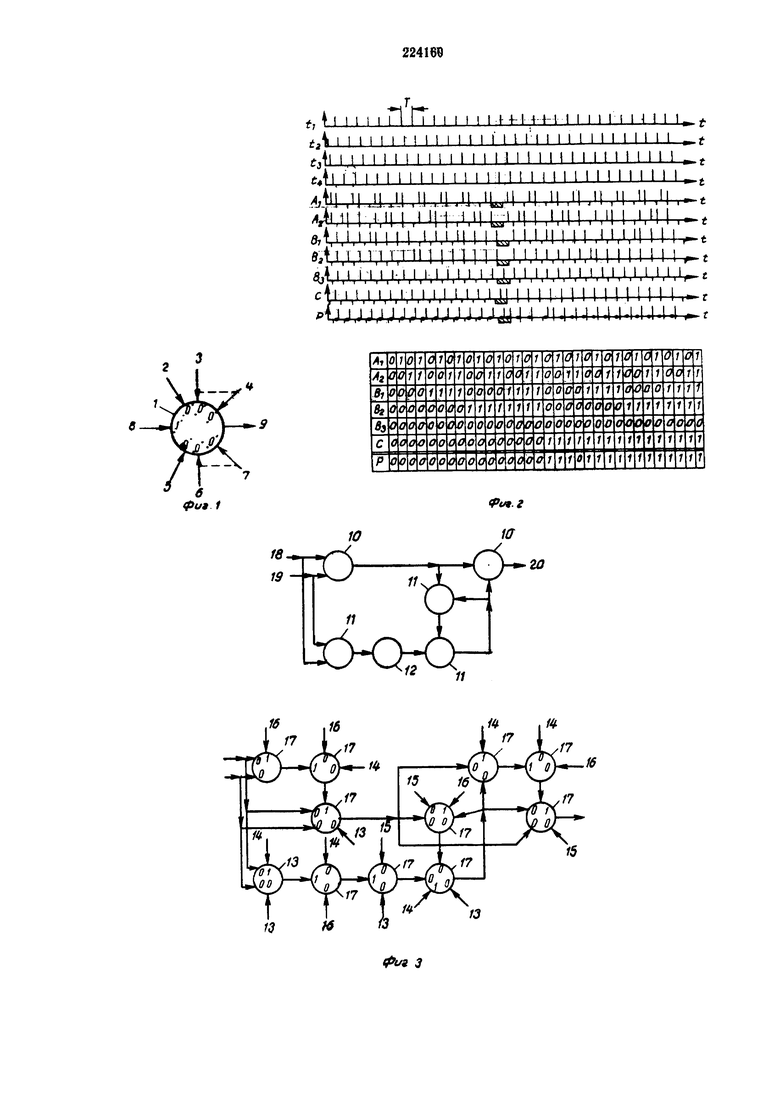

Случаи, определяемые формулами (2-6), являются граничными для ячейки с тремя основными входами, причем в случаях, определяемых формулами (2-4), требуется дополнительная подача входного числа В const = 0, а в случаях, определяемых формулами (5-7). условие благоприятных сочетаний значений разрядов входных чисел выполняется автоматически, и в подаче числа В const = 0 нет необходимости. Здесь можно отметить, что условия наличия только благоприятных сочетаний значений разрядов входных чисел определяется следующими выражениями:

при n≠0, k≠0

при n≠0, k=0

при n=0, k≠0,

где Bj, С, Ai - значения разрядов входных чисел в текущем периоде, a Ai (1) -значение разряда числа Ai в последующем периоде.

Таким образом, одна феррит-транзисторная ячейка с указанным количеством входов при полном их задействовании решает шесть различных логических операций.

При задействовании меньшего, чем в граничных случаях, числа входов или при подаче на некоторые входы постоянных значений разрядов чисел на этой ячейке можно реализовать и более простые логические операции.

Например:

- из формулы (5) при В const = 0

- операция Шеффера,

- операция Шеффера,

- из формулы (2), если опустить A2 при С const = 1

- отрицание,

- отрицание,

- из формулы (3) при С const = 1

Р=А→В - импликация,

- из формулы (2), если опустить А2

- запрет,

- запрет,

- из формулы (4), если опустить В2

- конъюнкция.

- конъюнкция.

При фазировании входных чисел необходимые задержки могут быть также получены на этом типовом элементе. В этом случае используется временной сдвиг между числом типа C с одной стороны и выходным числом Р с другой стороны.

Например; при Bj const = 1 или Ai const = 0 (формула 1), Р=С с задержкой выходного сигнала. При равномерном сдвиге фаз четырехфазного тактового питания можно записать  где

где  указывает на сдвиг фазы числа Р, равный четверти цифрового периода. При разработке схем по данному способу было установлено, что необходимые фазовые соотношения при согласовании отдельных узлов и логических элементов выполняются практически без лишних материальных затрат и схемы содержат меньше элементов по сравнению с применяемыми феррит-транзисторными схемами.

указывает на сдвиг фазы числа Р, равный четверти цифрового периода. При разработке схем по данному способу было установлено, что необходимые фазовые соотношения при согласовании отдельных узлов и логических элементов выполняются практически без лишних материальных затрат и схемы содержат меньше элементов по сравнению с применяемыми феррит-транзисторными схемами.

В качестве примера рассмотрим схему сумматора на один разряд. Блок-схема сумматора (фиг. 3) содержит элементы 10 отрицания равнозначности, элементы 11, реализующие операцию «трех Шеффера», и элемент 12 задержки на половину периода. Для тактирования схем используются импульсы t1, t2, t3, t4 четырехтактного питания, поступающие по шинам 13, 14, 15 и 16 соответственно.

Сумматор собран на однотипных феррит-транзисторных ячейках 17. Входные и выходные числа перемещаются по шинам 18, 19 и 20 соответственно.

Другой пример построения логических схем (фиг. 4 и 5) включает две схемы дешифраторов.

Особенностью дешифратора (фиг. 4), построенного на элементе 21 «И», является отсутствие задержки выходного числа относительно числа опроса, поступающего по шине 22. Питание схемы - четырехтактное по шинам 13-16. Дешифрируемая информация поступает по входу 23.

Результат поступает по выходным шинам 24-31. Дешифратор (фиг. 5) построен на элементах 21 «И» и элементах 32 «запрет». Для согласования с пирамидой при последовательном вводе требуется малое число ячеек. Информация поступает по шине 33, дешифрированный сигнал поступает по шинам 34-37. Опрос дешифратора происходит по шине 38.

На фиг. 4 по входу 23 сигналы поступают с фазой t2. Соответственно сигналы по шинам 22 и 24-31 имеют фазу t1. На фиг. 5 шины 33 и 38 имеют фазу t1, а входные шины 34-37 - t3.

Предложенный способ позволяет применить любой элемент памяти, обеспечивающий хранение двоичной цифры, значение которой («0» или «1») однозначно определяется параметрами последнего поступившего на вход импульсного сигнала или входом, по которому подается этот импульсный сигнал. Это обстоятельство позволяет применять элемент памяти как с долговременным, так и с недолговременным запоминанием состояний «0» и «1».

В качестве логического элемента при данном способе может применяться элемент памяти, имеющий и более двух состояний, у которого в данном случае используются либо только два состояния, либо две группы состояний, одна из которых эквивалентна значению «0», а другая - «1». При этом сигнал на выходе должен появиться только при переводе элемента памяти из состояния, эквивалентного «1», в состояние, эквивалентное «0».

При использовании элементов памяти, не имеющих развязанных входов или необходимых для сопряжения с другими аналогичными элементами значений параметров выходных сигналов, для развязки, а также выделения и преобразования входных или выходных сигналов (например, дифференцирование, усиление, инвертирование импульсов) в схему можно ввести специальные развязывающие, преобразующие и согласующие входные или выходные цепи.

Такими элементами памяти являются, например, обычные триггеры, используемые в потенциальных схемах, последовательно соединенные туннельный диод и сопротивление (резистор), трансформатор с входной и выходными обмотками на ферритовом кольце с прямоугольной петлей гистерезиса, динамические триггеры.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Логическая ячейка для ассоциативного запоминающего устройства | 1981 |

|

SU980162A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для программного управления технологическим оборудованием | 1985 |

|

SU1325407A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Имитатор кардиосигнала | 2024 |

|

RU2827990C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

Способ выполнения логических операций на запоминающем элементе с импульсно-фазовой модуляцией двоичных чисел, отличающийся тем, что, с целью унификации системы используемых элементов, подают сигналы первой и второй групп на первом интервале цифрового периода и переводят запоминающий элемент в состояние «0» или подтверждают это состояние, причем сигналы первой группы обозначают «1» в текущем цифровом периоде, а сигналы второй группы - «0» в предшествующем периоде, формируют на выходе сигнал «0» предшествующего периода при переводе запоминающего элемента в состояние «0», подают сигнал перевода запоминающего элемента в состояние «1» на втором интервале цифрового периода, если его значение равно «1», подают сигналы первой и второй групп на третьем интервале цифрового периода и переводят запоминающий элемент в состояние «0» или подтверждают это состояние, причем сигналы первой группы обозначают «0» в текущем цифровом периоде, а сигналы второй группы - «1» в текущем цифровом периоде, формируют на выходе сигнал «1» текущего периода при переводе запоминающего элемента в состояние «0», подают сигнал перевода запоминающего элемента в состояние «1» на четвертом интервале цифрового периода, если его значение равно «0».

Авторы

Даты

1968-11-26—Публикация

1966-05-04—Подача