Изобретение относится к измерительной технике и предназначено для измерений амплитуд широкополосных динамических сигналов с динамической погрешностью, не превьшающей методической погрешности аналого-цифрового преобразователя. .

Цель изобретения - расширение области применения устройства.

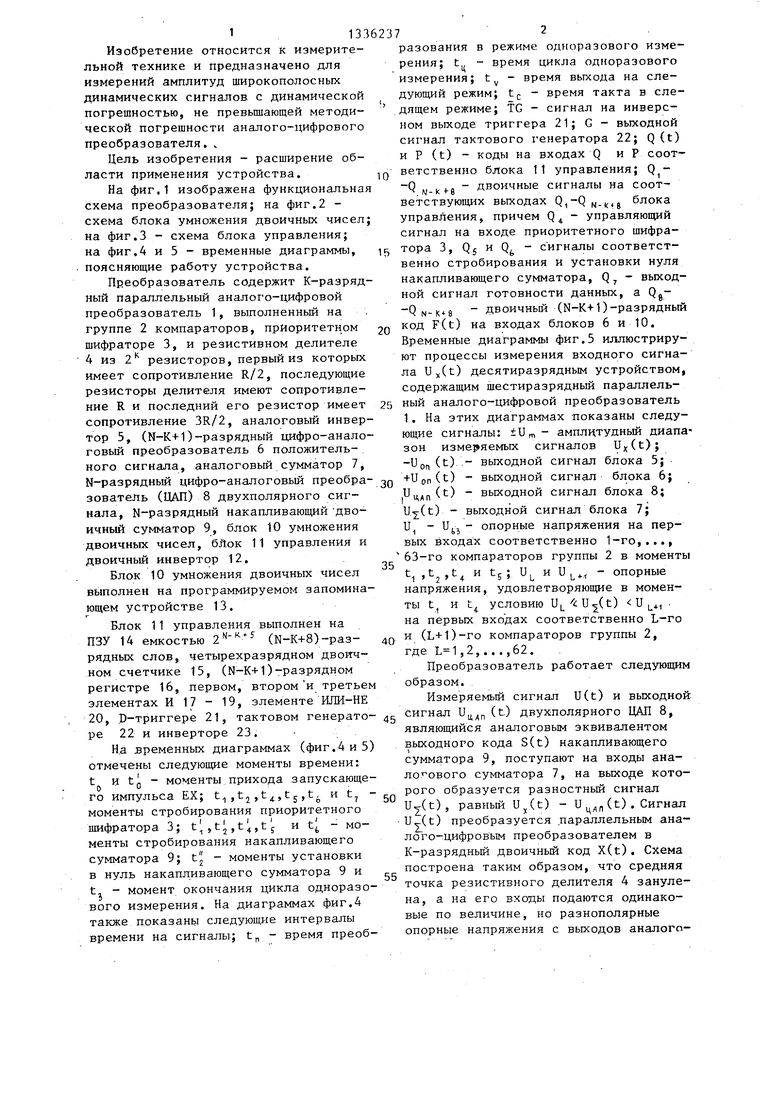

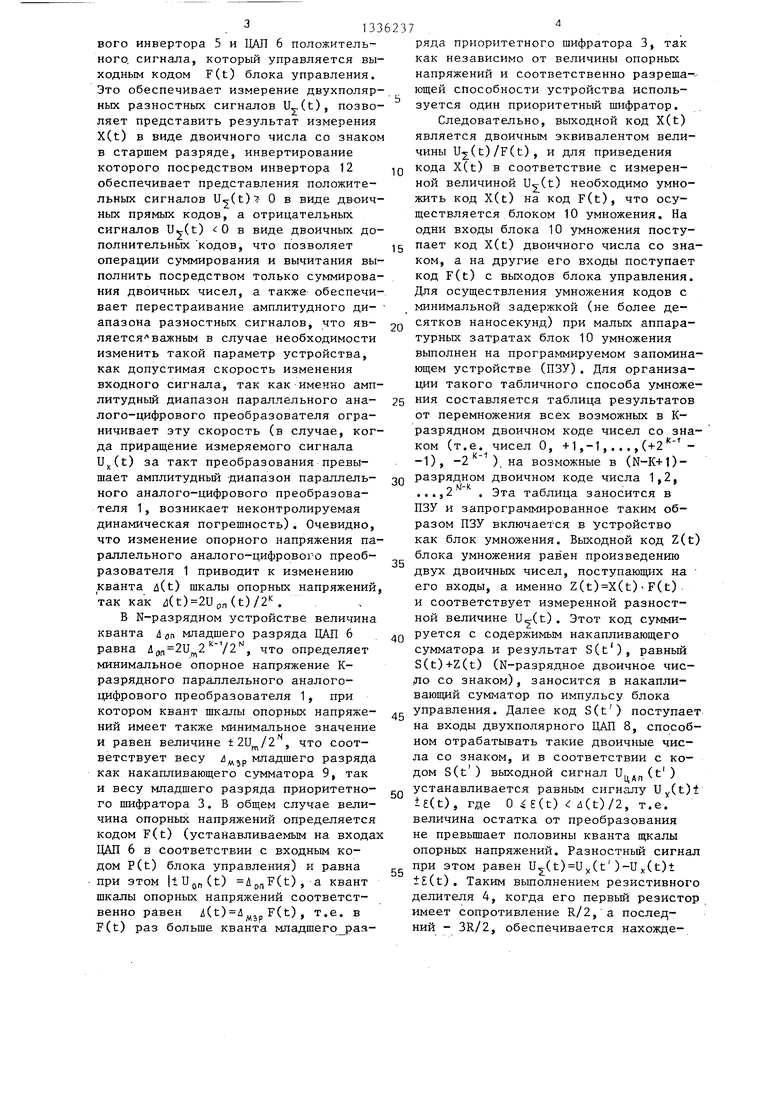

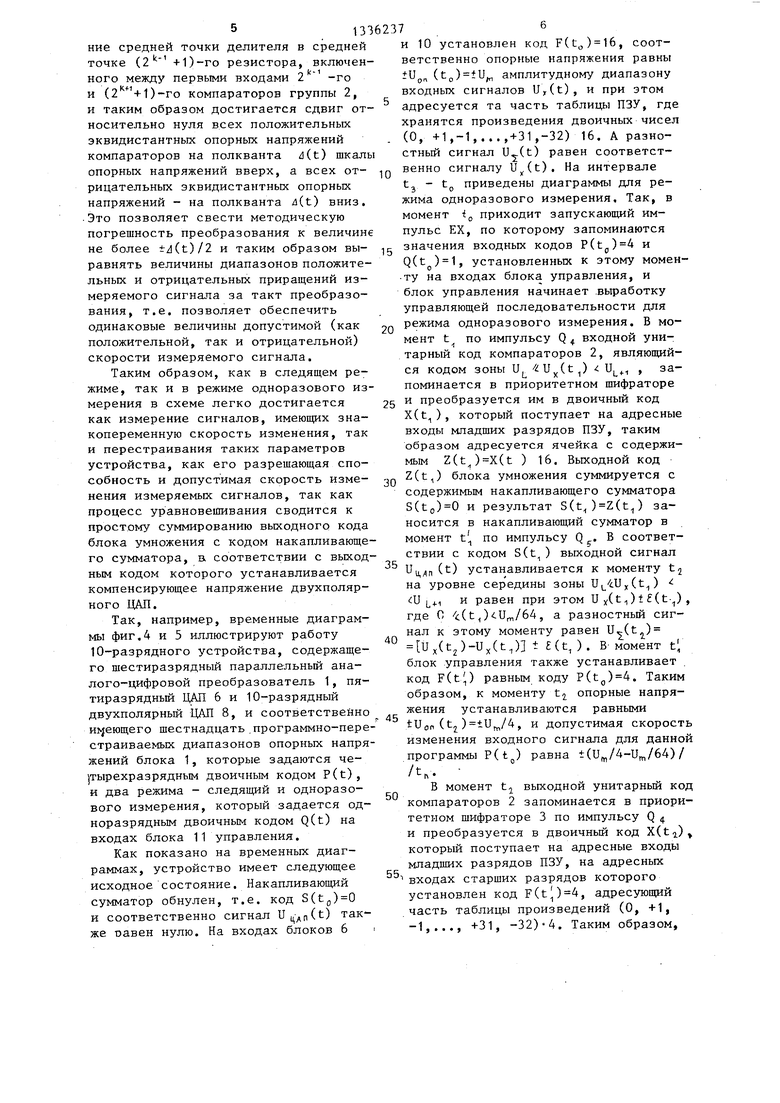

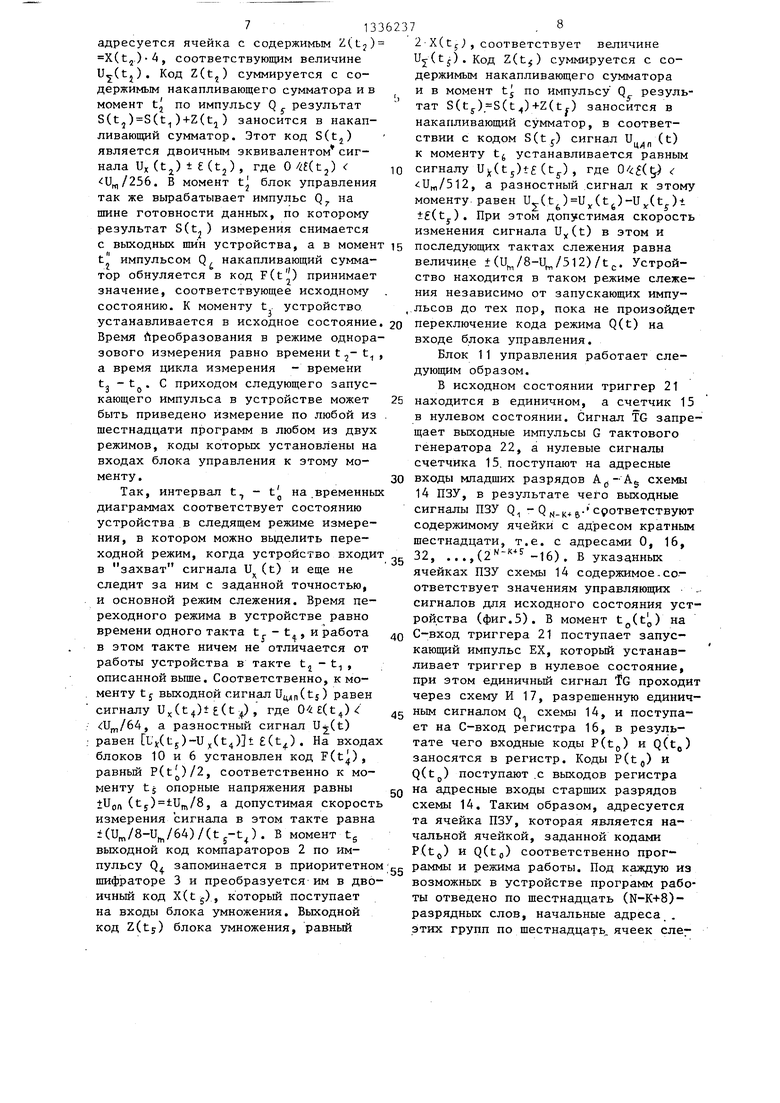

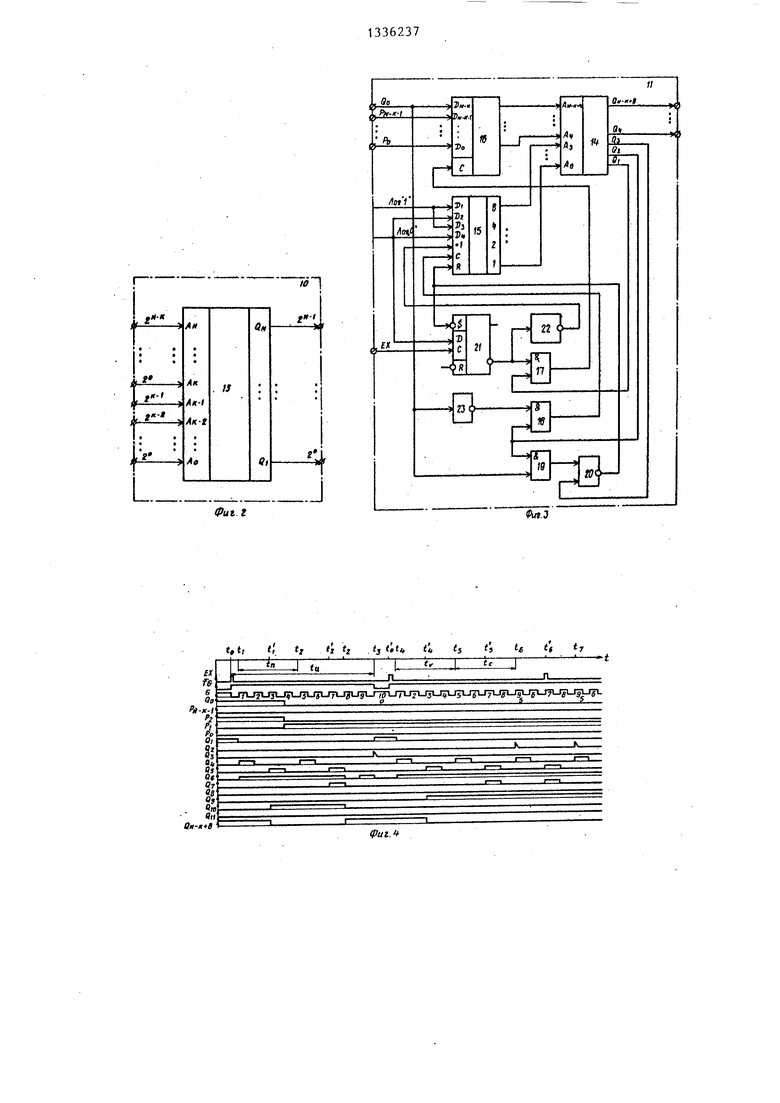

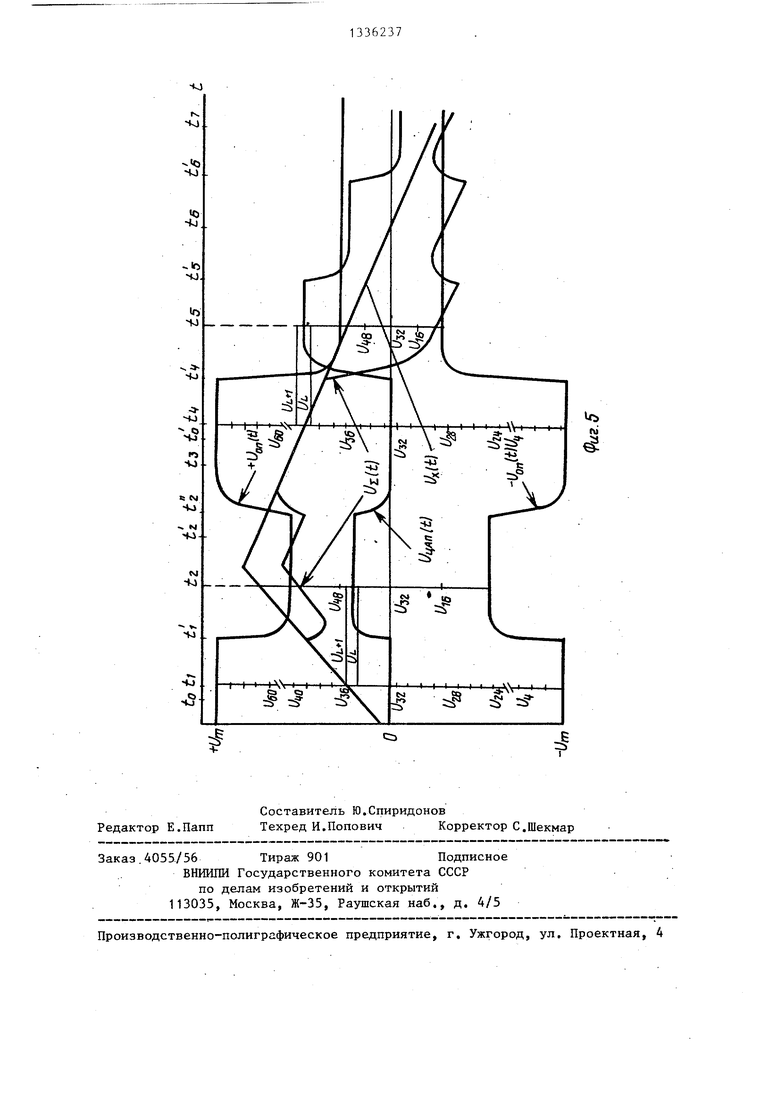

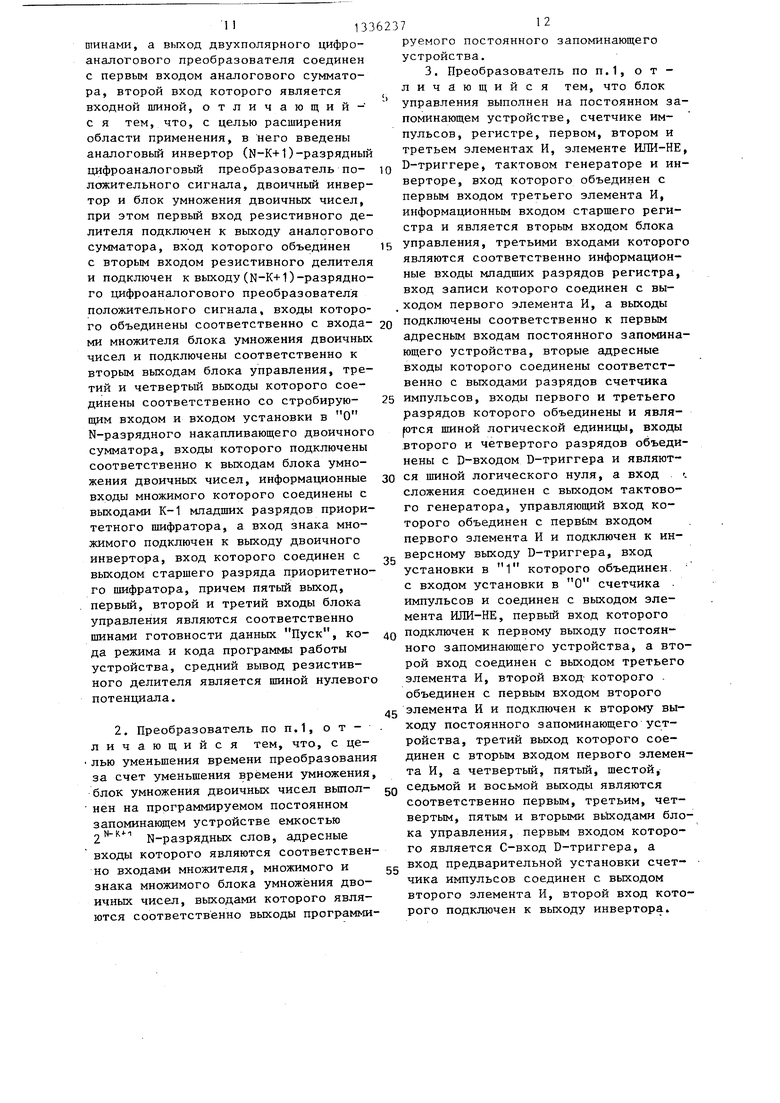

На фиг.1 изображена функциональная схема преобразователя; на фиг.2 - схема блока умножения двоичных чисел на фиг.З - схема блока управления; на фиг.4 и 5 - временные диаграммы, поясняющие работу устройства.

Преобразователь содержит К-разряд- ный параллельный аналого-цифровой преобразователь 1, выполненный на группе 2 компараторов, приоритетном шифраторе 3, и резистивном делителе 4 из 2 резисторов, первый из которых имеет сопротивление R/2, последующие резисторы делителя имеют сопротивление R и последний его резистор имеет сопротивление 3R/2, аналоговый инвертор 5, (М-К+1)-ра;зрядный цифро-аналоговый преобразователь 6 положительного сигнала, аналоговый сумматор 7, N-разрядный цифро-аналоговый преобра- зователь (ЦАП) 8 двухполярного сигнала, N-разрядный накапливающий двоичный сумматор 9, блок 10 умножения двоичных чисел, бЛок 11 управления и двоичный инвертсэр 12.

Блок 10 умножения двоичных чисел выполнен на программируемом запоминающем устройстве 13.

Блок 11 управления выполнен на ПЗУ 14 емкостью (Н-К+8)-раз- рядных слов, четырехразрядном двоичном счетчике 15, (N-K+1)-разрядном регистре 16, первом, втором и третьем элементах И 17 - 19, элементе ИЛИ-НЕ 20, Р-триггере 21, тактовом генерато- ре 22 и инверторе 23.

Н.а временных диаграммах (фиг.4 и 5) отмечены следующие моменты времени; t и tl - моменты прихода запускающе и

го импульса ЕХ; t,t,,t,t5,t и t моменты стробирования приоритетного шифратора 3; t ,t ,,t ,t и t - моменты стробирования накапливающего сумматора 9; t l - моменты установки в нуль накапливающего сумматора 9 и t, - момент окончания цикла одноразового измерения. На диаграммах фиг.4 также показаны следующие интервалы времени на сигналы; t - время преоб

5 о

0 5

0 g

5

разования в режиме одноразового измерения; t - время цикла одноразового измерения; t - время выхода на следующий режим; t,- - время такта в следящем режиме; TG - сигнал на инверсном выходе триггера 21; G - выходной сигнал тактового генератора 22; Q (t) и Р (t) - коды на входах Q и Р соответственно блока 11 управления; Q - Q „ 1/ д.о двоичные сигналы на соот, PJ- к и

ветствующих выходах (4e ° управления, причем Q 4. управляющий сигнал на входе приоритетного шифратора 3, Qj и Q - сигналы соответственно стробирования и установки нуля накапливающего сумматора, Q выходной сигнал готовности данных, а Qg- -Рм-(;.9 двоичный (N-K+I)-разрядный код F(t) на входах блоков 6 и 10. Временные диаграммы фиг.З иллюстрируют процессы измерения входного сигнала U)((t) десятиразрядным устройством, содержащим шестиразрядный параллельный аналого-цифровой преобразователь 1. На этих диаграммах показаны следующие сигналы: tUm амплитудный диапазон измеряемых сигналов ); -Uof, (t) .- выходной сигнал блока 5; +Uon(t) выходной сигнал блока 6; (t) - выходной сигнал блока 8; U(t) - выходной сигнал блока 7; и - Uj, - опорные напряжения на первых входах соответственно 1-го,..., 63-го компараторов группы 2 в моменты t ,tj,t и tj; } и UL+.I - опорные напряжения, удовлетворяющие в моменты t, и t условию ) U +, . на первых входах соответственно L-ro и (L+1)-ro компараторов группы 2, где ,2,.. .,62.

Преобразователь работает следующим образом.

Измеряемый сигнал U(t) и выходной сигнал (t.) двухполярного ЦАП 8, являющийся аналоговым эквивалентом выходного кода S(t) накапливающего сумматора 9, поступают на входы ана- ло ового сумматора 7, на выходе которого образуется разностный сигнал U(t), равный Ujj(t) - и t) . Сигнал U(t) преобразуется параллельным ана лого-цифровым преобразователем в К-разрядный двоичный код X(t). Схема построена таким образом, что средняя точка резистивного делителя 4 зануле- на, а на его входы подаются одинаковые по величине, но разнополярные опорные напряжения с выходов аналого3133

вого инвертора 5 и ЦДЛ 6 положительного, сигнала, который управляется выходным кодом F(t) блока управления, Это обеспечивает измерение двухполяр- ных разностных сигналов U(t), позволяет представить результат измерения X(t) в виде двоичного числа со знаком в старшем разряде, инвертирование которого посредством инвертора 12 обеспечивает представления положительных сигналов Uy(t) О в виде двоичных прямых кодов, а отрицательных сигналов Ut(t) 0 в виде двоичных дополнительных кодов, что позволяет операции суммирования и вычитания выполнить посредством только суммирования двоичных чисел, а также обеспечивает перестраивание амплитудного ди- апазона разностных сигналов, что яв- ляется важным в случае необходимости изменить такой параметр устройства, как допустимая скорость изменения входного сигнала, так как именно амплитудный диапазон параллельного ана- лого-цифрового преобразователя ограничивает эту скорость (в случае, когда приращение измеряемого сигнала Uj(t) за такт преобразования превышает амплитудный диапазон параллель- ного аналого-цифрового преобразователя 1, возникает неконтролируемая динамическая погрешность). Очевидно, что изменение опорного напряжения параллельного аналого-цифрового преобразователя 1 приводит к изменению кванта ia(t) шкалы опорных напряжений так как d(t)2U (t).

В N-разрядном устройстве величина кванта & on младшего разряда ЦАП 6 равна VZ, что определяет минимальное опорное напряжение К- разрядного параллельного аналого- цифрового преобразователя 1, при котором квант шкалы опорных напряже- НИИ имеет также минимальное значение и равен величине t 21)/2 , что соответствует весу л„5р младшего разряда как накапливающего сумматора 9, так и весу младшего разряда приоритетно- го шифратора 3. В общем случае величина опорных напряжений определяется кодом F(t) (устанавливаемым на входах ЦАП 6 в соответствии с входным кодом P(t) блока управления) и равна при этом ItUgnCt) (t), а квант шкалы опорных напряжений соответственно равен 4(t) F(t) , т.е. в F(t) раз больше кванта младшего раа

5 о

о g Q c

5

ряда приоритетного шифратора 3, так как независимо от величины опорных напряжений и соответственно разреша-- ющей способности устройства используется один приоритетный шифратор.

Следовательно, выходной код X(t) является двоичным эквивалентом величины U2(t)/F(t), и для приведения кода X(t) в соответствие с измеренной величиной U(t) необходимо умножить код X(t) на код F(t), что осуществляется блоком 10 умножения. На одни входы блока 10 умножения поступает код X(t) двоичного числа со знаком, а на другие его входы поступает код F(t) с выходов блока управления. Для осуществления умножения кодов с минимальной задержкой (не более десятков наносекунд) при малых аппаратурных затратах блок 10 умножения выполнен на программируемом запоминающем устройстве (ПЗУ). Для организации такого табличного способа умножения составляется таблица результатов от перемножения всех возможных в К- разрядном двоичном коде чисел со знаком (т.е. чисел О, +1 ,-1,.. ., ( - -1), -2 ). на возможные в (N-K+1)- разрядном двоичном коде числа 1,2,

kf-k

...,2 . Эта таблица заносится в ПЗУ и запрограммированное таким образом ПЗУ включается в устройство как блок умножения. Выходной код Z(t) блока умножения рав ен произведению двух двоичных чисел, поступающих на его входы, а именно Z(t)X(t)F(t) и соответствует измеренной разностной величине U(t) . Этот код суммируется с содержимым накапливающего сумматора и результат S(t ), равный S(t)-t-Z(t) (N-разрядное двоичное число со знаком), заносится в накапливающий сумматор по импульсу блока управления. Далее код S(t ) поступает на входы двухполярного ЦАП 8, способном отрабатывать такие двоичные числа со знаком, и в соответствии с кодом S(t ) выходной сигнал Цц(t ) устанавливается равным сигналу Uy(t)t t(t), где О (t) ; 4(t)/2, т.е. величина остатка от преобразования не превьш1ает половины кванта щкалы опорных напряжений. Разностный сигнал при этом равен U(t)U(t )-Ux(t)t ±(t). Таким выполнением резистивного делителя 4, когда его первый резистор имеет сопротивление R/2, а последний - 3R/2, обеспечивается нахожде51336237

ние средней точки делителя в средней точке (2 +1)-го резистора, включенноге между первыми входами 2 -го и ( + 1)-го компараторов группы 2, и таким образом достигается сдвиг относительно нуля всех положительных эквидистантных опорных напряжений компараторов на полкванта (t) шкал опорных напряжений вверх, а всех отрицательных эквидистантных опорных напряжений - на полкванта 4(t) вниз. .Это позволяет свести методическую погрешность преобразования к величин не более ±(t)/2 и таким образом вы- равнять величины диапазонов положительных и отрицательных приращений измеряемого сигнала за такт преобразования, т.е. позволяет обеспечить одинаковые величины допустимой (как положительной, так и отрицательной) скорости измеряемого сигнала.

Таким образом, как в следящем режиме, так и в режиме одноразового измерения в схеме легко достигается как измерение сигналов, имеющих знакопеременную скорость изменения, так и перестраивания таких параметров устройства, как его разрешающая способность и допустимая скорость изменения измеряемых сигналов, так как процесс уравновешивания сводится к простому суммированию выходного кода блока умножения с кодом накапливающего сумматора, п соответствии с выходным кодом которого устанавливается компенсирующее напряжение двухполяр- ного ЦАП.

Так, например, временные диаграммы фиг,4 и 5 иллюстрируют работу 10-разрядного устройства, содержащего шестиразрядный параллельный аналого-цифровой преобразователь 1, пятиразрядный ЦАП 6 и 10-разрядный двухполярньш ЦДЛ 8, и соответственно И1 еющего шестнадцать программно-перестраиваемых диапазонов опорных напряжений блока 1, которые задаются че- {тырехразрядным двоичным кодом P(t), и два режима - следящий и одноразового измерения, который задается одноразрядным двоичным кодом Q(t) на входах блока 11 управления.

Как показано на временных диаграммах, устройство имеет следующее исходное состояние. Накапливающий сумматор обнулен, т.е. код S(t(,)0 и соответственно сигнал ицдп(ь) также тэавен нулю. На входах блоков 6

6

10

и 10 установлен код Р(с„)1б, соответственно опорные напряжения равны tUp (to)tU амплитудному диапазону входных сигналов Ux(t), и при этом адресуется та часть таблицы ПЗУ, где хранятся произведения двоичных чисел (О, +1,-1,...,+31,-32) 16. А разностный сигнал U(t) равен соответственно сигналу Uj(t). На интервале

Ч приведены диаграммы для ре15

жима одноразового измерения. Так, в момент (; приходит запускающий импульс ЕХ, по которому запоминаются значения входных кодов P(t.,)4 и

20

Q(t)1, установленных к этому моменту на входах блока управления, и блок управления начинает .выработку управляющей последовательности для режима одноразового измерения. В момент t по импульсу Q входной унитарный код компараторов 2, являющийся кодом зоны Uj(t ) - ., , запоминается в приоритетном шифраторе

25 и преобразуется им в двоичный код X(t), который поступает на адресные входы младших разрядов ПЗУ, таким образом адресуется ячейка с содержимым Z(t)X(t ) 16. Выходной код

„-. Z(t,) блока умножения суммируется с содержимым накапливающего сумматора S(to)0 и результат S(t,)Z(t) заносится в накапливающий сумматор в момент t, по импульсу Q . В соответствии с кодом S(t) выходной сигнал Уцлп (t) устанавливается к моменту tj на уровне середины зоны ,) :и L4.1 и равен при этом U x(t) t (t-) , где О i.Ct ,), а разностный сиг1

35

40

нал к этому моменту равен U,j(t,)

45

50

55,

U(t2)-U(t,) t (t, ). В- момент t блок управления также устанавливает код F(tl|) равным коду P(tg)4. Таким образом, к моменту t опорные напряжения устанавливаются равными tHOf (), и допустимая скорость изменения входного сигнала для данной программы P(t) равна ±(и|„/4-и„/64) /

/t.. Б момент t выходной унитарный код компараторов 2 запоминается в приоритетном шифраторе 3 по импульсу Q и преобразуется в двоичный код XCt) который поступает на адресные входы младших разрядов ПЗУ, на адресных входах старших разрядов которого установлен код F()4, адресующий часть таблицы произведений (О, +1, -1,..., +31, -32)-4. Таким образом,

71336237, 8

адресуется ячейка с содержимым Z(t2) 2-XCt j, соответствует величине X(t,.) 4, соответствующим величине и5-(й).Код Z(t) суммируется с соU(tj). Код Z(tj) суммируется с содержимым накапливающего сумматора и в момент tj по импульсу Q результат S(t,j)S(t )+Z(tg ) заносится в накапливающий сумматор. Этот код S(tj) является двоичным эквивалентом сигнала U; (t,) ± (t), гдeO/ Kt2) . В момент t блок управления так же вьфабатывает импульс Q., на шине готовности данных, по которому результат SCtj) измерения снимается

10

держимым накапливающего сумматора и в момент tf по импульсу Q резуль тат S(ty)S(t)+Z(tг) заносится в накапливающий сумматор, в соответствии с кодом S(tj) сигнал U (t) к моменту tj устанавливается равным сигналу UjfCtj) (tj) , где O-ifC) : :и„/512, а разностный сигнал к зтом моменту равен U(t)Uy(tj)-U,(t)t ±(tj.). При этом допустимая скорост изменения сигнала U(t) в этом и

с выходных ши н устройства, а в момент 15 последующих тактах слежения равна

t импульсом Q , накапливающий сумматор обнуляется в код F(t ) принимает значение, соответствующее исходному

величине ±(U /8-U /512)/t.

w4 t - I / I Г J С. ТрОИ

ство находится в таком режиме слежения независимо от запускающих импульсов до тех пор, пока не произойдет

устанавливается в исходное состояние. 2о переключение кода режима Q(t) на Время {преобразования в режиме однора- входе блока управления, зового измерения равно времени t -t,

состоянию. К моменту t. устройство

Блок 11 управления работает следующим образом.

а время цикла измерения - времени tg -tjj. С приходом следующего запускающего импульса в устройстве может быть приведено измерение по любой из шестнадцати программ в любом из двух режимов, коды которых установлены на входах блока управления к этому моменту .

Так, интервал t, - t на.временны диаграммах соответствует состоянию устройства в следящем режиме измерения, в котором можно выделить переN-K+F

ходной режим, когда устройство входит . 32, .. ., ( -16) , В указанных в захват сигнала U (t) и еще не следит за ним с заданной точностью, и основной режим слежения. Время переходного режима в устройстве равно

ячейках ПЗУ схемы 14 содержимое.со.- ответствует значениям управляющих сигналов для исходного состояния устройства (фиг.5). В момент tp(tp) на времени одного такта t. - t , и работа 40 С-вход триггера 21 поступает запусв этом такте ничем не отличается от работы устройства в такте t - t, описанной Bbmie. Соответственно, к мо- . менту tj выходной сигнал Ui,n(tj) равен сигналу Ux(t4)i(t ф), где O i(t)

, а разностный сигнал Uj(t) ; равен U,f(t5)-U(t4)t (t) . На входах блоков 10 и 6 установлен код F(tp, равный P(t)/2, соответственно к мокающий импульс ЕХ, который устанавливает триггер в нулевое состояние, при этом единичный сигнал TG проходит через схему И 17, разрешенную единич- 45 ным сигналом Q схемы 14, и поступает на С-вход регистра 16, в результате чего входные коды P(tp) и Q(tg) заносятся в регистр. Коды PCtj) и Q(tp) поступают .с выходов регистра

менту tj опорные напряжения равны gQна адресные входы старших разрядов

lUon (tj)tUn,/8, а допустимая скоростьсхемы 14. Таким образом, адресуется

измерения сигнала в этом такте равната ячейка ПЗУ, которая является наi()/(tj-t). В момент tgчальной ячейкой, заданной кодами

выходной код компараторов 2 по им-PCt) HQCtj,) соответственно прогпульсу Q запоминается в приоритетномVgраммы и режима работы. Под каждую из

шифраторе 3 и преобразуется им в две-возможных в устройстве программ рабоичный код XCtj), который поступаетты отведено по шестнадцать (N-K+8)на входы блока умножения. Выходнойразрядных слов, начальные адреса.,

код Z(t5) блока умножения, равныйэтих групп по шестнадцать, ячеек сле

держимым накапливающего сумматора и в момент tf по импульсу Q результат S(ty)S(t)+Z(tг) заносится в накапливающий сумматор, в соответствии с кодом S(tj) сигнал U (t) к моменту tj устанавливается равным сигналу UjfCtj) (tj) , где O-ifC) : :и„/512, а разностный сигнал к зтому моменту равен U(t)Uy(tj)-U,(t)t ±(tj.). При этом допустимая скорость изменения сигнала U(t) в этом и

последующих тактах слежения равна

величине ±(U /8-U /512)/t.

w4 t - I / I Г

переключение кода режима Q(t) на входе блока управления,

Блок 11 управления работает следующим образом.

В исходном состоянии триггер 21

находится в единичном, а счетчик 15 в нулевом состоянии. Сигнал TG запрещает выходные импульсы G тактового генератора 22, а нулевые сигналы счетчика 15. поступают на адресные

входы младших разрядов схемы 14 ПЗУ, в результате чего выходные сигналы ПЗУ Q - Q .jg. соответствуют содержимому ячейки с адресом кратным шестнадцати, т.е. с адресами О, 16,

N-K+F

32, .. ., ( -16) , В указанных

кающий импульс ЕХ, который устанавливает триггер в нулевое состояние, при этом единичный сигнал TG проходит через схему И 17, разрешенную единич- 45 ным сигналом Q схемы 14, и поступает на С-вход регистра 16, в результате чего входные коды P(tp) и Q(tg) заносятся в регистр. Коды PCtj) и Q(tp) поступают .с выходов регистра

5N-K+ 4

дующие: 0,16,32,..., ( -16) для программ следящего режима и , (2М-М4 +16)( -16) для программ одноразового режима измерения. Таким образом, в ПЗУ схемы 14 хранятся значения управляющих после; овательностей для -ти программ работы.

Единичный сигнал TG так же разрешает прохождение импульсов G на вход +1 счетчика 15, выходные сигналы которого поступают на младшие адресные входы Ар - AJ схемы 14, в тате чего содержимое ПЗУ последовательно выбирается на выходы Q,,...,

и, таким образом, вьфабатываходном состоянии до следующего запускающего импульса.

Как показано выше, в предлагаемом преобразователе возможны два режима - следящий и одноразового измерения, причём время выхода на следящий режим не зависит от входного сигнала и всегда равно времени одного такта 10 в отличие от известной схемы, которая имеет переменное время выхода на следящий режим, равное в худшем случае величине 2 периодов тактовой частоты. Более того, в отличие от резуль- 15 известного устройства в каждом из

двух режимов обеспечено по программно-перестраиваемых диапазонов допустимых приращений измеряемого

ется последовательность управляющих сигналов в соответствии с заданной кодами P(to) и Q(tp) программы и режима работы. В режиме одноразового

20

сигнала за такт, что эквивалентно устройствам с различными допустимой скоростью изменения измеряемого сигнала и разрешающей способностью; Таким образом, предлагаемый преобразователь в отличие от извест- сительно начального адреса программы, 25 ног о в одном устройстве обеспечивает вьфабатывается импульс Qj, который высокую разрешающу о способность 2и„/

измерения в момент tj выбора ячейки. ПЗУ с адресом, смещенным на 10 отнопроходит через схему ИЛИ-НЕ 20 и устанавливает триггер 21 и счетчик 15 в исходное состояние, в результате чего режим измерения завершается. 30

8следящем режиме при выборе содержимого ячейки с , смещенным на

9относительно начального адреса программы P(t(,), вьфабатывается импульс Qj, который поступает на входы схем 35 18 и 19, которые по вторым входам управляются прямым и инверсным битом Q(t). В зависимости от значения Q(t) происходит выполнение еще одного такта t или следящий режим завершается. 40 Так, если Q(t)0 в момент t вьфабот- ки импульса Q,, т.е. подтверждается

/2 при измерении сигналов, скорость изменения которых не Превьш1ает вели- 12 /t.,, а в верхнем

чины

H2U.2

-(

Ч

продолжение следящего режима, то импульс QJ проходит через схему 19 на вход стробирования счетчика 15, ив счетчик заносится двоичное число 5 с его D-входов. Таким образом, на адресных входах схемы 14 устанавливается адрес, соответствующий началу управляющей последовательности такта t, соответственно еще раз выполняется такт слежения. Если же к моменту выработки импульса Qj состояние кода Q(t) изменилось и стало единичнымд то импульс QJ проходит через схемы 19 и 20 и устанавливает триггер 21 и счетчик 15 в исходное состояние, в результате чего следящий режим завершается, и устройство находится в испредельном случае позволяет измерять высокочастотные сигналы параллельным К-разрядным аналого-цифровым преобра зователем как в следящем режиме, так и в режиме одноразового измерения. Это существенно расширяет область применения предлагаемого устройства в сравнении с известным.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий К-разрядный параллельный аналого-цифровой преобразователь, вьшолненньш на группе компа45 раторов, приоритетном шифраторе и резистивном делителе, выходы которого соединены соответственно с первым входами компараторов группы, вторые входы которых объединены и подключен

gQ к выходу аналогового сумматора, а выходы соединены соответственно с информационными входами приоритетного шифратора, стробирующий вход которого подключен к первому выходу

gg блока управления, выходы N-разрядно го накапливающего двоичного сумматор подключены соответственно к входам двухполярного цифроаналогового преобразователя и являются выходными

1336237

10

20

сигнала за такт, что эквивалентно устройствам с различными допустимой скоростью изменения измеряемого сигнала и разрешающей способностью; Таким образом, предлагаемый преобразователь в отличие от извест- ног о в одном устройстве обеспечивает высокую разрешающу о способность 2и„/

/2 при измерении сигналов, скорость изменения которых не Превьш1ает вели- 12 /t.,, а в верхнем

чины

H2U.2

-(

предельном случае позволяет измерять высокочастотные сигналы параллельным К-разрядным аналого-цифровым преобразователем как в следящем режиме, так и в режиме одноразового измерения. Это существенно расширяет область применения предлагаемого устройства в сравнении с известным.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий К-разрядный параллельный аналого-цифровой преобразователь, вьшолненньш на группе компараторов, приоритетном шифраторе и резистивном делителе, выходы которого соединены соответственно с первыми входами компараторов группы, вторые входы которых объединены и подключены

к выходу аналогового сумматора, а выходы соединены соответственно с информационными входами приоритетного шифратора, стробирующий вход которого подключен к первому выходу

блока управления, выходы N-разрядно- го накапливающего двоичного сумматора подключены соответственно к входам двухполярного цифроаналогового преобразователя и являются выходными

тинами, а выход двухполярного цифро- аналогового преобразователя соединен с первым входом аналогового сумматора, второй вход которого является входной шиной, отличающий - с я тем, что, с целью расширения области применения, в него введены аналоговый инвертор (N-K+1)-разрядный цифроаналоговый преобразователь положительного сигнала, двоичньй инвертор и блок умножения двоичных чисел, при этом первый вход резистивного делителя подключен к выходу аналогового сумматора, вход которого объединен с вторым входом резистивного делителя и подключен к выходу(N-K+1)-разрядного цифроаналогового преобразователя положительного сигнала, входы которого объединены соответственно с входа- ми множителя блока умножения двоичных чисел и подключены соответственно к вторым выходам блока управления, третий и четвертый выходы которого соединены соответственно со стробирую- щим входом и входом установки в О N-разрядного накапливающего двоичного сумматора, входы которого подключены соответственно к выходам блока умножения двоичных чисел, информационные входы множимого которого соединены с выходами К-1 младших разрядов приоритетного шифратора, а вход знака множимого подключен к выходу двоичного инвертора, вход которого соединен с выходом старшего разряда приоритетного шифратора, причем пятый выход, первый, второй и третий входы блока управления являются соответственно шинами готовности данных Пуск, кода режима и кода программы работы устройства, средний вывод резистивного делителя является шиной нулевого потенциала.

2. Преобразователь по п.1, отличающийся тем, что, с целью уменьшения времени преобразования за счет уменьшения времени умножения, блок умножения двоичных чисел вьшолнен на программируемом постоянном запоминающем устройстве емкостью N-разрядных слов, адресные входы которого являются соответственно входами множителя, множимого и знака множимого блока умножения двоичных чисел, выходами которого являются соответственно выходы программи0

5

5

0

5

руемого постоянного запоминающего устройства.

3. Преобразователь по п.1, о т - личающийся тем, что блок управления выполнен на постоянном запоминающем устройстве, счетчике импульсов, регистре, первом, втором и третьем элементах И, элементе ИЛИ-НЕ, D-триггере, тактовом генераторе и инверторе, вход которого объединен с первым входом третьего элемента И, информационным входом старшего регистра и является вторьм входом блока управления, третьими входами которого являются соответственно информационные входы младших разрядов регистра, вход записи которого соединен с выходом первого элемента И, а выходы подключены соответственно к первым адресным входам постоянного запоминающего устройства, вторые адресные входы которого соединены соответственно с выходами разрядов счетчика импульсов, входы первого и третьего разрядов которого объединены и явля- ртся шиной логической единицы, входы второго и четвертого разрядов объединены с D-входом D-триггера и являются шиной логического нуля, а вход сложения соединен с выходом тактового генератора, управляющий вход которого объединен с первым входом первого элемента И и подключен к инверсному выходу D-триггера, вход

0

установки в 1 которого объединен. с входом установки в О счетчика . импульсов и соединен с выходом элемента ИЛИ-НЕ, первый вход которого подключен к первому выходу постоянного запоминающего устройства, а второй вход соединен с выходом третьего элемента И, второй вход- которого . объединен с первым входом второго 5 элемента И и подключен к второму выходу постоянного запоминающего устройства, третий выход которого соединен с вторым входом первого элемента И, а четвертый, пятый, шестой, седьмой и восьмой выходы являются соответственно первым, третьим, четвертым, пятым и вторыми вьЬсодами блока управления, первым входом которого является С-вход D-триггера, а вход предварительной установки счетчика импульсов соединен с выходом второго элемента И, второй вход которого подключен к выходу инвертора.

0

5

Фиг г

f. t/ .. t, t f tf t, t .t t ti t , tf t f ti

tu

ftrt.3

|. t, и J

tput.f

Us

ru

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

| Аналого-цифровое устройство для возведения в куб | 1985 |

|

SU1251113A1 |

Изобретение относится к измерительной технике и предназначено для измерения амплитуд широкополосных динамических сигналов с динамической погрешностью, не превышающей методической погрешности аналого-цифрового преобразователя. Целью изобретения является расширение области применения устройства. В устройство, содержащее аналого-цифровой преобразователь 1, аналоговый сумматор 7, двух- полярный цифроаналоговый преобразователь (ЦАП) 8, двоичный сумматор 9, блок 11 управления, введены аналоговый инвертор 5, ЦАП 6 положительного сигнала, блок 10 умножения и двоичный инвертор 12. 2 з.п. ф-лы, 5 ил. (Л со со а to 00 «Ч

Редактор Е.Папп

Составитель Ю.Спиридонов

Техред И,Попович Корректор С.Шекмар

Заказ. 4055./56 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Титце У., Шенк.К | |||

| Полупроводниковая схемотехника | |||

| - М.: Мир, 1982 | |||

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах | |||

| /Под ред | |||

| Г.М.Петрова | |||

| - М.: Машиностроение, 1973, с.256-257, рис.100. |

Авторы

Даты

1987-09-07—Публикация

1985-06-26—Подача