12

СХ

ю

О1

.{

Шина адреса

«

рийньгми блоками датчиков и тем самлм упростить устройство, nocTpoeaiioe ;ia базе микропроцессора. Это ;;.остнгае гс:я введением по числу блоко ;;атчиков цифроаналоговьж преобразовй телей 7, многоканального аналого цифрово) о тре образователя 16 (АЦП),, триггера, 10 и последовательно соединенмых элема- - та И 11, счетчика 12 ммпул1:,сов и бгю- ка 13 памяти. При этом многоразря л- ные коды с выходов каищого блока да г- чиков преобразуют с помошт-ло соответствующего цифроаналогового преобразователя в аналоговьм сигнал, который передают по протяженной двутспрозодной линии на вход многоканального ЛИЛ,

ол11яю1де го комму г с:; гна;1г. . В ячейках блог. jji заданных согт;- личных UHK.iax y:i , элемент 1 и сч орку содержимого II и к а жд о г о г а к т а с вьг-:одоп МП с выходах блока 1J падении формиру-с не ссора операнд, ьзлпот д.ля: реализ до в а те дь i-i о : о у п р нем. 3 ил„, 2 та

aiiiiK) 1: нреооразоV .К Сиива.чентный а памяти хранятся ЯНЛГ11 д,атчнг.:о в равлешьч, а триг- етчнк обес :1ечк)аю tis я -еек. По окон пр е о б р а 3 о в а н ия )аннивают с

памяти и при их т на входе микрокоторый затем ис ации программы по авления оборудо- бл.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство для многоканальной магнитной записи аналоговых сигналов | 1987 |

|

SU1520582A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

Изобретение относится к управлению циклическими технологическими процессами, например каталитического получения бутадиена или изопрена в производстве ci-штетического каучука. Цель изобретения - упрощение устройства путем сокращения числа проводов лин1Ш связи с периферийными блоками датчиков. Изобретение позволяет сократить число проводных линий связи с перифе

1

Изобретение относится к управлепи цикли ;ecки ш технолог}5чесхкми процессами например, катал гтич12 ского получения бутадиена или и:югфена в про- изводсл ве синтетического к аучука к может быть использовано в .1ическс1Н; нефтехимической и других отраслях промьшшенности.

Цель изобретения - упрощение ройства путем со;: ращения числа проводов линин связи с перкферийньЕ-п- бло-- ками датчиков,

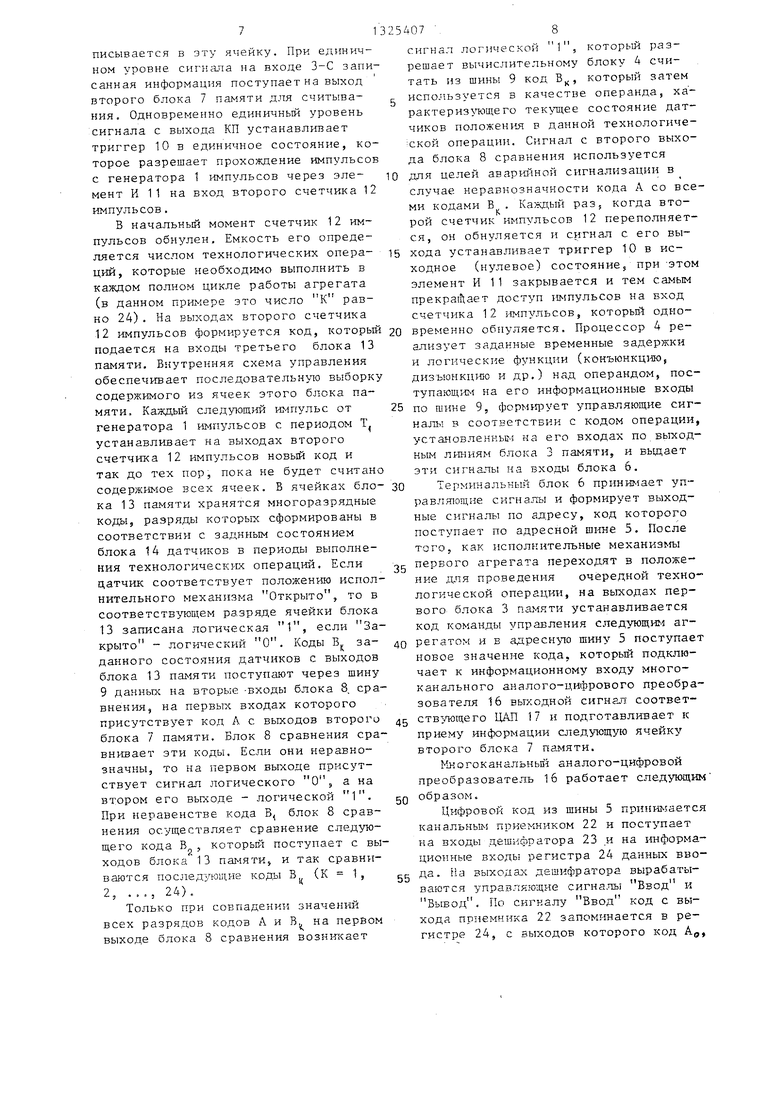

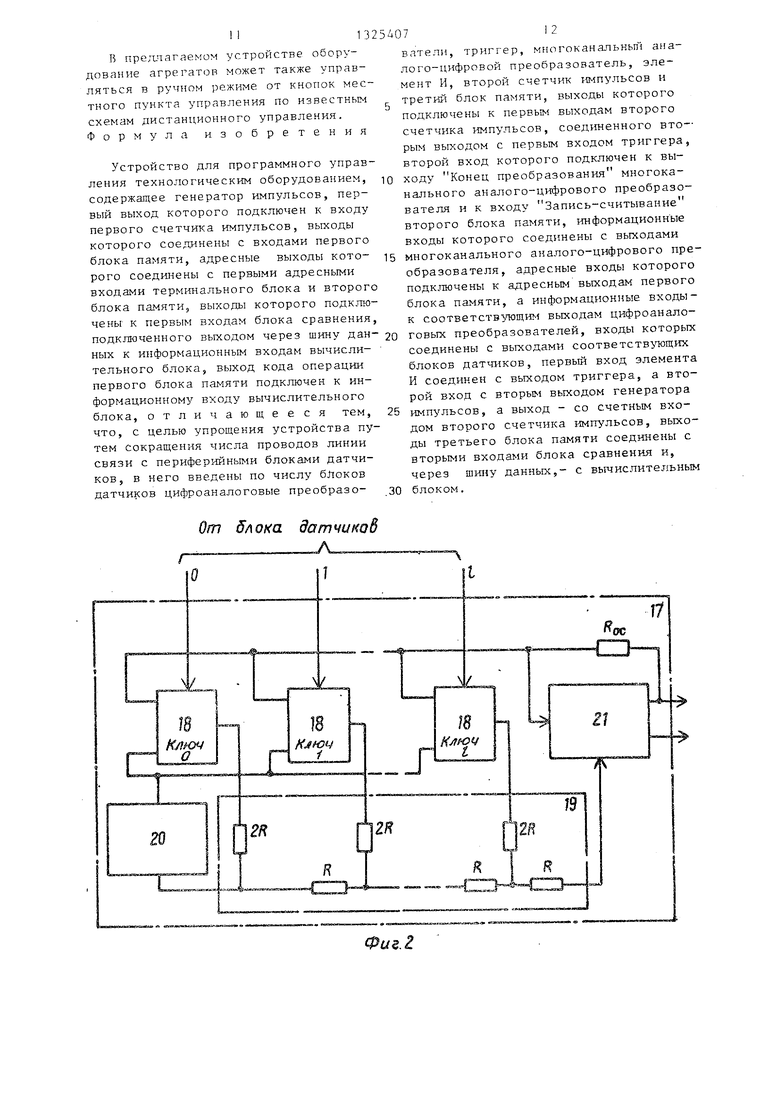

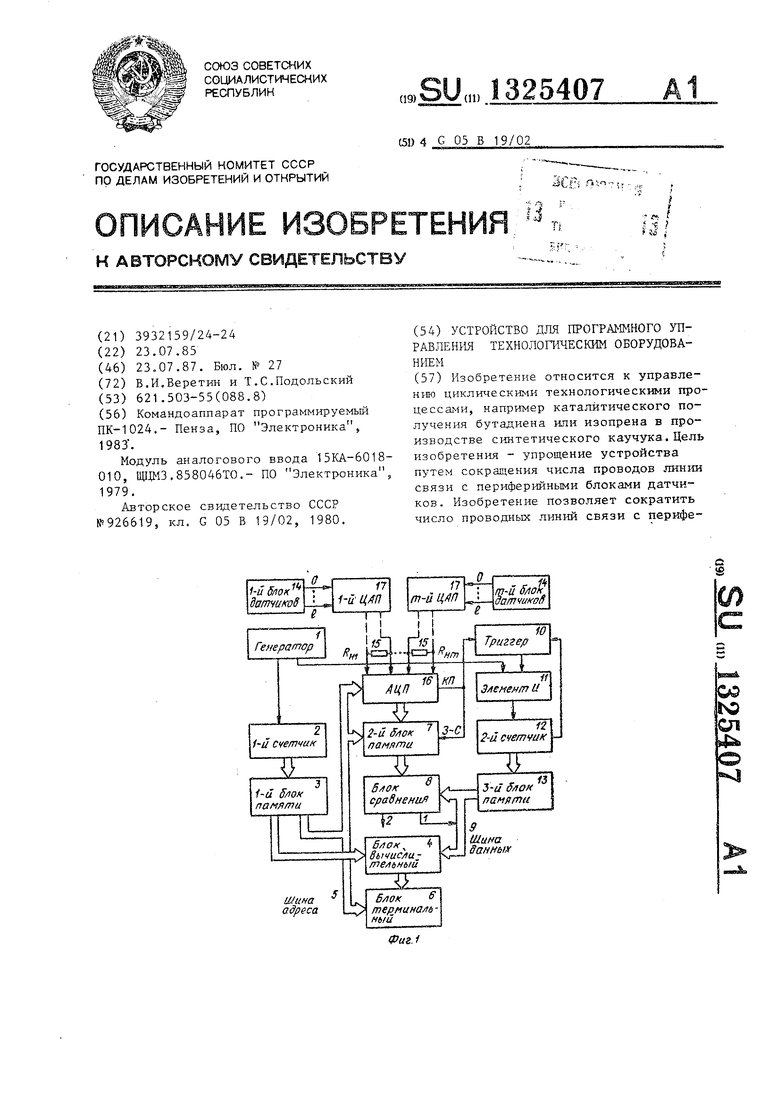

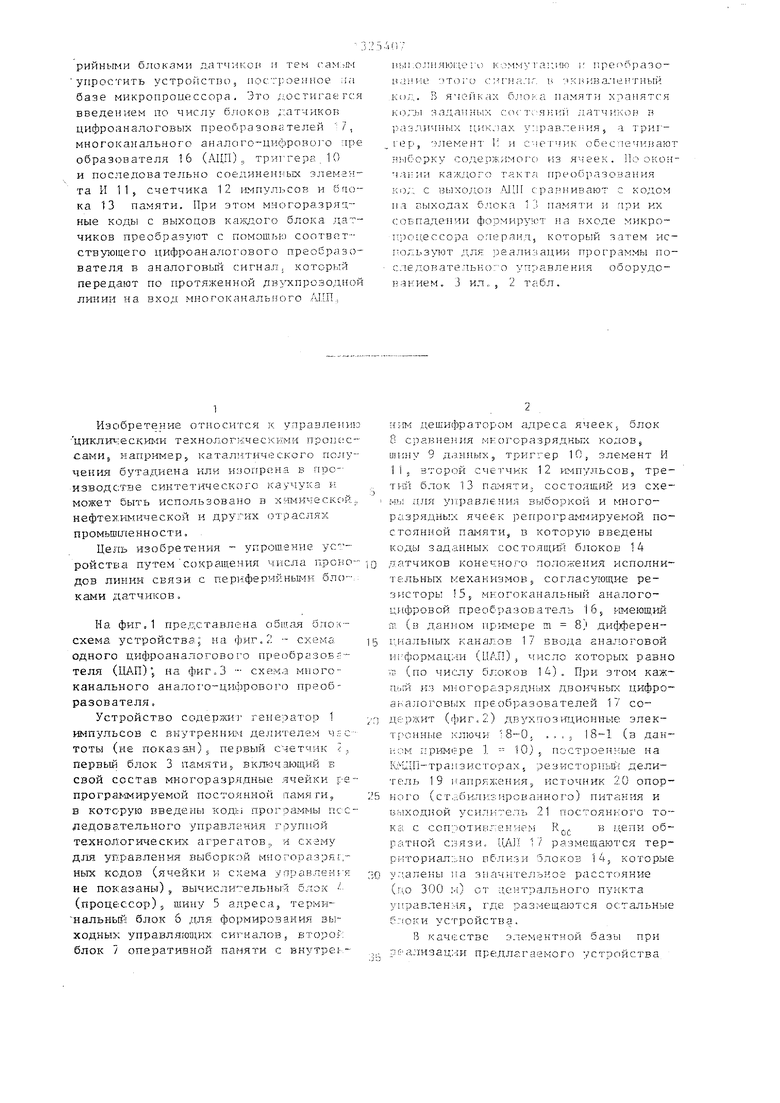

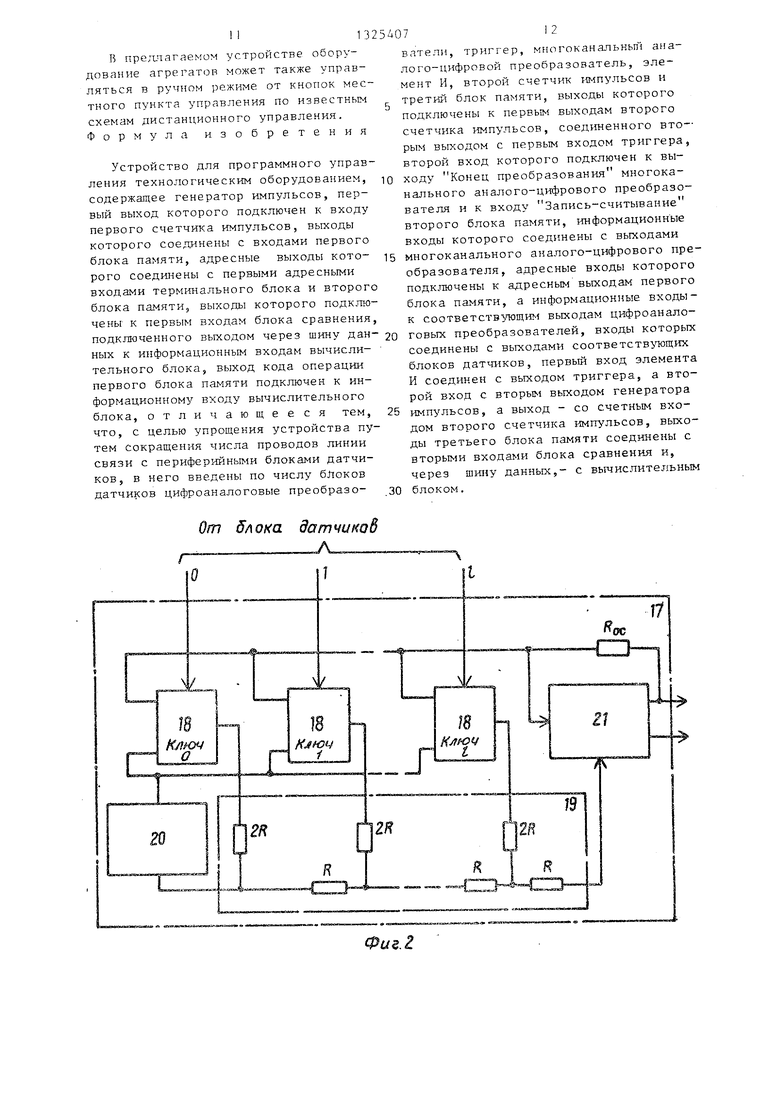

На фиг.1 представлена С)6щ;1я бпол- схема устройства; на (тг,2 - схема одного цифроаналогово го преобразов-:- теля (ЦАП) J на фиг.2 - cxeiM.a много-канального аналого-цифрового преобразователя.

Устройство содержит генератор 1 импульсов с в1-гутренню . делителем чгс тоты (не показ.ан)р первый счетч.ик I. первый блок 3 па-мяти.. вкг&зчшощий в свой состав многоразрл дные ячейки f-e програ мируемой постоянной памяти, в которую введены кодь прогоаммы пес ледов ательного управления группой технояогическкх агрегатов,, и схему для управления выборкой многоразряг,- ных кодов (ячейки к схема управлекгя не поксоаны) , вычисли гельныч блок (процессор) 5 5 адреса, терми- нальньй блок б для формирования выходных управляюп их: сигналов, второе- блок 7 оперативной памяти с внутреь

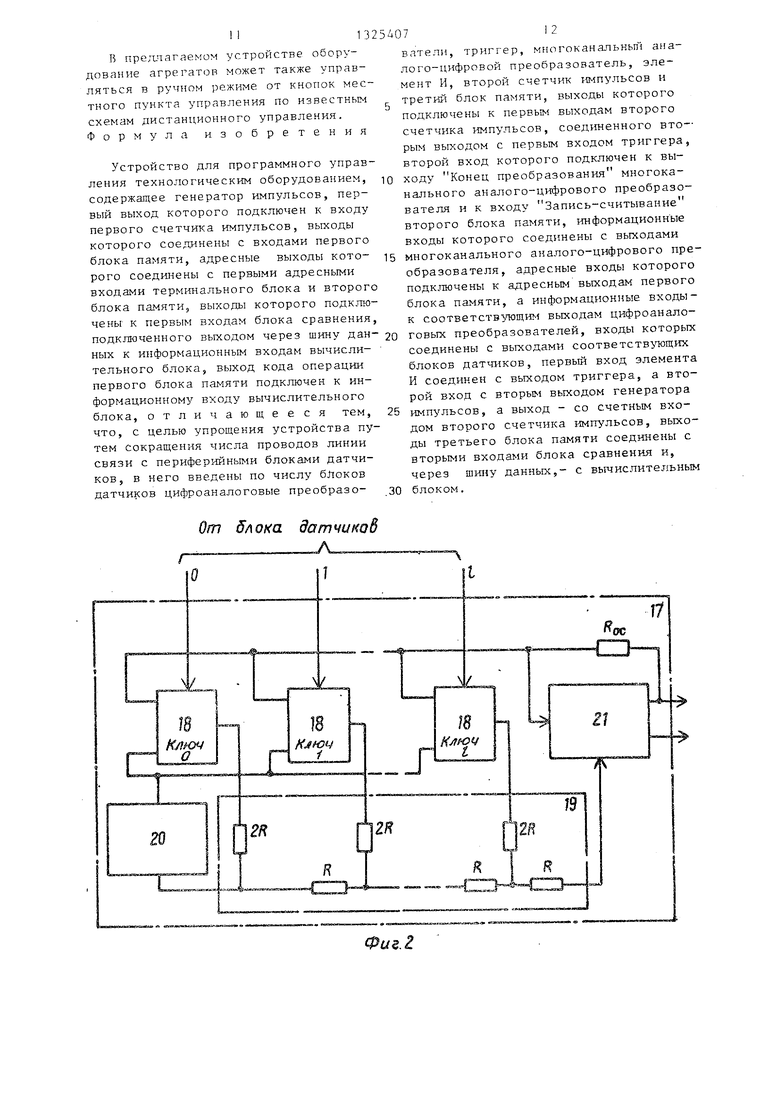

дешифратором адреса ячеек, блок 8 сравне 1ия мног оразрядньи кодов, ьчину 9 данирях 3 триггер 10, элемент И 11; -йторой счетчмк 12 импульсов, тре- Tnii блок 13 пгьмяти, состояи:ий из схе- нь: и,ля управления выборкой и многоразрядных ячеек 15епрограммируемой постоянной памяти, в которую введены коды заданных состоящей блоков 14 датчиков конечного пологдения исполнительных механ5- змов J, согласхтащие ре- зисторь 15; многоканальный аналого- цифровой преобразователь 16. имеющий m (в данном прршере т 8) дисЗ -ерен- -г.иальных каналов 17 ввода аналоговой И1--формац;-- и (U/Ul) ; число которьк равно а; (по числу блоков 14). этом каж- п.ьгй из многоразрядных двоичньк цифро- аьа;юговЕ 1х преоб азователей 17 содержит ((Ьиг,2) двл хпозт-тционные элек- тг-онные ключи , ..., 18-1 (в данном 1 - 10) J пост эоенные на КМлПЬ ТранзистораХ; резксторпыг: делитель 19 |5апрял;енкяJ источник 20 опорного (ст.;-.билизнрованно1 о) пита} ня и выходной усилг;тель 21 постоян -;ог о торатной с;зязи, ГАП Г/ размещаются тер- риториал::,но вблизи Злокоз 14, которые -,апены на Зг1; |-ч;ительно расстояние (fiO 300 м) от схснтрального пункта управления,, где размещаются остальные б п: о к и у ст р о и с т в а ,

8 кач1:.ствс элементной базы при р : ал и:заи:-1р пре,длаг аемого у с трои ства

П

могут быть использованы микроироцесго ры и сопутствующие им интегральные микросхемы общего назначения. Например, устройство можно скомпоновать на базе микроэвм Электроника-60 с основными платами (процессор М2, блоки памяти ОЗУ и РПЗУ) и дополнительньии модулями (ЦАП. аналогового ввода и дискретного вывода). Используемый при этом преобразователь АЦП должен удовлетворять следующим требованиям: имет разрядность не меньше, чем разрядность входного кода ЦАП, иметь погрешность, не превьш1аюшую половины уровня сигнала, соответствующего младшему значащему разряду ЦАЦ, иметь большое входное сопротивление (не менее 1 МОм) . Первоначальный ввод рабочей программы в блоки памяти устрой- ства и их возможная корректировка могут осуществляться с помощью автономных программаторов из номенклатуры гредств вычислительной техники.

В состав технологического оборудования j предназначенного для проведения, например, процесса получения бутадиена или изопрена, входит группа параллельно включенных реакционных аппаратов (агрегатов). Работа каждого агрегата описывается циклами последовательного выполнении ряда технологических операций; подготовка к пуску, продувка паром, контактирование, ре- генерация катализатора и др. Для переключения с одной операции на другую каждый агрегат имеет запорн-что арматуру, снабженную исполнительными механизмами с датчиками конечного положа- ния (Открыто, Закрыто). Циклы работы агрегатов смещены во времени таким образом, что в то время, как-часть агрегатов находится, например, на контактировании, в остальных осущест- вляют другие технологические операции.

Сигналы с первого выхода генератора 1, подключе})Ного к первому входу элемента И 11, имеют форму непрерыв- ной последовательности стандартных импульсов пря;чоугольной формы с регу- лируемьв- интервалом времени Т между ними (например, наиболее часто Т 1 с) . Сигналы с второго выхода ге- нератора 1, подключенного через внут- рениж делитель частоты к входу первого счетчика 2, такую же форму, но увель ченную периодичность

повторения и ятульсов (например, Т 60 Т, с) .

Блок 8 сравнения выпо.гп1яет известную операцию сравнения двух многораз рядных чисел А и R. Для определения момента, когда А В, производится поразрядное с т- МТ рование по модулю два. При п-разрядных числах блок 8 состоит из п сумматоров по модулю два, выходы которых подключены к элементу ИПИ-НЕ. При этом реализуется функциональная зависи юсть (выходная цепь 1):

о,А т Б

F(A,B)

I 1,А Bj, ,

принимающая значение, равное 1 толко при попарном- равенстве всех одноименных разрядов чисел А (а, ) а, ) и В| (Ъ , . . . , Ь, ) , где а,, и Ь - старшие разряды.

Устройство работает след К1Щ15м образом.

Генератор 1 импульсов формирует импульсы с периодом Т, поступающие на вход делителя частоты, коэффициен деления которого равен d. Периодичность повторе 1ия 1гмпульсов на выходе делителя определяется соотношением 1 d-T и устанавливается несколько больше интервала времени, необ- для срабатьшания исполнительного механизма (открытия или за крытил). По сигналу с выхода делителя первый счетчик 2 изменяет свое состояние на очередное и формирует код адреса команд, которые хранятся в первом блоке 3 памяти. На выходах блока 3 последовательно устанавливаются коды команд, состоящие из двух частей: кода адреса и кода операции. Код операции поступает на входы вычислительного блока, а код адреса - в адресн то шину 5. Сигналы от блока 14 датчиков в виде 1-разрядного кода поступает на входы ЦАП 17, которьш осуш,ествляет перевод кода в аналоговый сигнал. Электронные ключи 18 обеспечивают сопряжение выходных цепей датчиков ЦАП 17. Срабатывание кахсдого контакта датчика вызывает срабатывание соответствующего ключа, который переключает выходные цепи делителя 19 то к шине с нулевым потенциалом источника 20J то к выходной шине. При переходе от старщего разряда к -шадшему и наоборот выходной ток изменяется два раза. Усилитель

21 сумьшрует разрядныг токи и формирует на вькоде сигнал, прэпорциоНсии- ный входному коду;

JL УВЬ. .,

где К R /2R 2 ;

Вхонной код

О О О О (ООООО

О О О О (1ОО(О1 11111 11 11 0 О О О ООО IОО

О О О О ООО(О1

1 1 1 1 1 I11

Выходной сигнал КЕНВДОГО ЦДП 17 nti- редается по протяженной дву-хпроводяой линии связи через согласующий резистор 15 на соответствующий вход многоканального аяалого-цифровог о npeoEKsa- зователя 1б, При каждом изменении кода адреса5 поступающего по шине 5 -ла управляющие входы многоканального аналого-цифрового преобразователя 16, последний осуществляет коммутацию„ - ввод и преобразование аналоговой информации в эквивалентньш Д1зоич11ый код

кото рыи зс а р 1 к: т е р и з у в т

текущее состояние блока 14 датчиков j-ro агрегата (j 1 2, „:., m). В табл. 2 приведено соответствие вхоц512Е

1000000000

в табл. 2 Е - значение сигнала на входе многоканального ана юго-цифро- ного сигнала цифровому коду на выхэ- ого преобразователя 16. гоотнетству- дах А:ЦП 16.„

Т а б ; и ц а 2

юпг,ее мла,7,п1ему разряду на его выходе. Например, Е - 0,01 В для аз рядного АЦП при верхнем значе} ии входного

.Входной сигнал

Выходной код

О

00000 ОО

000000ОО -

00000 ОО1 О

000 О О О100

и - опорное 1-;апркже ние источника;

а. 1о,1 - коэффициенты; i О, . . . J 1 - число разрядов. В табл. 1 показаны значения выход- нъгА сигналов десятиразрядного ЦДЛ при различных входных кодах (при Р. ,,с - R 10 кОм:) .

Т а б л з ц а 1 Выходной сигнал

О

К-и,. ( ) К-П „ (1/2 - )

К-и,,, /2

К-и„, (1/2 -ь Г- )

(1 - )

Продолжение табл.2

16Е

32Е

64Е

28Е

256Е

512Е

30000 1 0000. О 000100 О О О Э О О 1 000000 3 О 1 О О О О О О О

01 00000000

1000000000

в табл. 2 Е - значение сигнала на входе многоканального ана юго-цифро- ого преобразователя 16. гоотнетству-

юпг,ее мла,7,п1ему разряду на его выходе. Например, Е - 0,01 В для аз рядного АЦП при верхнем значе} ии входного

греса |Х,, , . . . ., Х( J, поступающими

шине .5;, и сигнллом с , выхода Ко- ц преоб-разоЕ;ания (КП) А1Щ 16. Сиг- и UI кода адреса при помощ -: внутренней скемы уп;;: авлекия выбирает одну из за- л.анных к -геек памяти. При нулевом уров- и. сигнала на входе Запр сь-считыва- н.ие (3-е) код с многоканального ана- ,;К : о--цифгюво1 с преобразователя 16 записывается в эту ячейку. При единичном уровне сипиша на входе 3-С записанная информация поступает на выход второго блока 7 памяти для считывания. Одновременно единичный уровень сигнала с выхода КП устанавливает триггер 10 в единичное состояние, которое разрешает прохождение импульсов с генератора 1 импульсов через элемент И 11 на вход второго счетчика 12 импульсов.

в начальный момент счетчик 12 импульсов обнулен. Емкость его определяется числом технологических операций, которые необходимо выполнить в каждом полном цикле работы агрегата (в данном примере это число К равно 24). На выходах второго счетчика

12импульсов формируется код, который подается на входы третьего блока 13 памяти. Внутренняя схема управления обеспечивает последовательную выборку содержимого из ячеек этого блока памяти. Каждый следутощж импульс от генератора 1 и Jпyльcoв с периодом Т устанавливает на выходах второго счетчика 12 импульсов новый код и так до тех пор, пока не будет считано содержимое всех ячеек. В ячейках блока 13 памяти хранятся многоразрядные коды, разряды которых сформированы в соответствии с заднпым состоянием блока 14 датчиков в периоды выполнения технологических операций. Если цатчик соответствует положению исполнительного механизма Открыто, то в соответств 5/та1дем разряде ячейки блока

13записана логическая 1, если Закрыто логический О. Коды В, заданного состояния датчиков с выходов блока 13 памяти поступают через шину 9 данных на вторые -входы блока 8. сравнения, на первых входах которого присутствует код А с выходов второго блока 7 памяти. Блок 8 сравнения сравнивает эти коды. Если они неравнозначны, то на первом выходе присутствует сигнал логического О , а на втором его выходе - логической 1. При неравенстве кода В, блок 8 сравнения осуществляет сравнение следующего кода В , который поступает с выходов блока 13 памяти, и так сравниваются последурощие коды В (К 1 ,

2, ..., 24),

Только при совпадении значений всех разрядов кодов А и В„ на первом

выходе олока

сравнения возн1-ткает

, который разрешает вычислительному блоку 4 считать из шины 9 код В, который затем используется в качестве операнда, характер из oщe го состояние датчиков положение в данной технологиче- ской операции. Сигнал с второго выхода блока 8 сравнения используется

для целей аварийной сигнализации в

случае неравнозначности кода А со всеми кодами В,. Каждый раз, когда второй счетчик импульсов 12 переполняется, он обнуляется и С11гнал с его выхода устанавливает триггер 10 в исходное (нулевое) состояние, при -этом элемент И 11 закрывается и тем самым пpeкpa aeт доступ дашульсов на вход счетчика 12 шчпульсов, который одновреь енно обнуляется. Процессор 4 ре- апизует заданные временные задержки и логические функции (конъюнкц1-ЕЮ, дизъюнкцшо и др.) над операндом, пос- тупающиь на его информационные входы

по шине 9, форм$-фует управляющие сигналы в соответствии с кодом операции, установленньи на его входах по выходным Л1-ШИЯМ блока 3 памяти, и вьщает эти сигналы на входы блока 6.

Терминальный блок 6 пpини aeт управляющие сигналы и формирует выходные сигналы по ад.ресу, код которого поступает по адресной miiHe 5. После того, как исполнительные механизмы

первого агрегата переходят в положение для проведения очередной технологической операции, на выходах первого блока 3 памяти устанавливается код команды управления следующиг- агperатом и в адресную шину 5 поступает новое значение кода, которьш подключает к информационному входу многоканального аналого-цифрового преобразователя 16 вьт ;одной сигнал соответствующего ЦДЛ 17 и подготавливает к приему информации следующую ячейку второго блока 7 памяти.

Многоканальньй аналого-цифровой преобразователь 16 работает следующим

образом.

Цифровой код из шины 5 при ш-5ается канальньш приемником 22 и поступает на входы дешифратора 23 и на информационные входы регистра 24 данных ввода. На выходах дешифратора вырабатываются управляющие сигналы Ввод и Вывод. По сигналу Ввод код с выхода приемника 22 запоминается в регистре 24, с выходов которого код А,

А s посту идет 1 а упраел;:- иия мультиплексором 25, r. U- и тывается снгиа;; )a конкретного входного капали (схема у;г;;ав ;ания ,-хо дит в состан мультмг.г-екс 25).Нуль ткплексор обеспеч иу;: ;;т i оочерр гцюе подключение линий 31-:)да; ча нахо,п,ится вхс дная И1(|)ормаа,ия от согласующих р;;зистс1ров ; 5 (-Ьиг . 1 ) к входу схемы aяaлoгo пифpo зr ::) лреобразо-- вания (на вкоц KOMviKpaTop: 30) , Упраъ ленна схемой аналогс-цифооного преобразования обеспечипают гот ерато 26. элемент И 27, тригл-ср 28 i-t сдвига ;;- щий регистр 29, Каж.пый u j-ixj:; о;1кократ- ного лрвобразопалчя ,; ае чти ; -:/-; дачи уровня логической (оргла/ Пуск)., котог,лй г;опг л1рул- ся гри:;г:-- ром 28 по лололси ra.:7T-rio;--iy (,- : ir- нала Ввод.. Сдл - лл 11уск усга.иа-;;- ливает в исход;ное -::; с топ л ке репслгр 29 сдвига,; реглс л; ;:. данных ,,u-. и элемр - :т И 2/, Лри сток га / регистра 29 залисываг-тск Ч, . ходит устз; о1зка з ст;илла о ра зрл. да чразрлл; 1,) регистра и сбну. всех остальньк гго разг1я;чсБ,

Компаратор iO ос 1 ;естт:: яет оп;;.-;деление знака разкос гд мсжгду уг ОгЛГгм напря;кенч:и U,,, с в: ходг: мyJ:ыл, АС.К сора 25 я уровнем напряжения U с выхода лреобразовател:я 31. .; -;:- ватель 31 БьграбатЕмва ;;Т п:с ожиталы С ;;

натф.яжения Ц.. , то iia вьгхог е ,Р;:- тора 30 уст;шавлт-1Еае гея уровгпд, . cii- ческой Г , в протил-:::ок ;:;,уоа;; л/: :-: ходе компарато15а 30 ус ;: адавлидае ля уровелпэ погическсч о О Д Зате,; ос ;-- ществляют 1 тактов (I - рая);;:- доз регистра) лосл;2доват;1 льло О грг- блгскензш напряже ;ил ,, .m-t or о напря кел;,ю К,. , |,а ка;кдсн такте: преобразозаьик ,, зад,а Baei SCM j t:-- нератором 26, сигна.,; с задход;а лолга- ратора 30, в cjr/чаа ..-, :-- IJ,,, , лрох:г дит олькс через ют еледакт 11 32 д ИЛИ--П1; 33, да Бторс й лхо,:.:, г. додас;тс: pa3 oei:-.:uo(i sfl-i ciu isn с сд -л/ о из р Д рядов с:дни::чиои;,лго ;:;€гистра 29 При этом прсис;;оддгг бро-;; в л Д1а ;д-,; состс яние соотдатспгдоашдс разу л га регис гра 3 . троис; :о дн7 сдвиг разргдчающего с;-лл;а.да на ахдд щего Unia iiie- Оу ;:д;:эр;,;.1й., л момегд перехлючекия -зт ого скгна..7а

, 11/,10

(т.е. в MObien i сдвига) устанавливаЕсли la ;:iaiiHOM такте пре3)мПОЛНЯ :ТСЯ УСЛОВИЕ

У, и,. , то сигна сброса не выраба- | |,длается компаратором 30 и соответствующий разряд регистра ЗА остается н единичном состоянии. В течение 1 таи-стов происходит последоватедьная уС-тано1;:ка в 1 или в О всех разрядов рег;-:стра 34 Операция заканчи- гзается в момент лереходг. синхронизи- pyrouf.erci ед,И:-:;иного сигнгша в послед- н1-;й разряд сдвигающего регистра 29, так каи при этом с помощью триггера 28 вырабатывается сигнал запрета на а;;од алеменга И 2 дропускающего тад-уговые ид-шульсь; от генератора 26 да вход, сдн иуающе г о 29. В рй зу;1ьтате досле (Д-сопчагия преобразо- зания г:апр;1;кени1 з i.U будет приближено к уел5Д-:ине U с точностью до вклада саксд о младшего разряда; т.е.

и э - - а; и ji и,, ,

г,е а.; -- ко:;)ффициенть 1 или О в разрядах кода, снимаемого с вько710В оегистоа 34

-1 1},,г. --j,,,,/2 - вклад 1-го разряД1У-. в ;1а1Пря5хение на зьуходе пре ;бразоватедя 31 , и, 10„:: 3 В - максимальное преобра1зуемс: е напряжение. Сигнал с лосдеГ Него разряда сдвига ion:;ero регис Г :а 29 (сигнал окончания а:н алого-дифр(37зог о преобразования) по- гупает таю-се на вход регистра 35 со- :тоядия . где запоминается. При появ- ,;екии сигнсда БыЕюд на выходе де- | 1иф ратора 23 форкгируется разрешающий У Г-овень логического О (сигнал КП) до которому код с выходов регистра 34 дерез канальные пе:редатчики 36 посту- те.ет в блок ла1чя1Д1 (фиг. 1) .

При достудтлеггии иа вход блока 16 дтугого значения :ода; достулаюцего :то шине 5, дродесс аналого-ддфрового дреобра:чод дмя прсд сходит ан,адогично : :чдожекному, Гаки образом, блок 16 iiC у1дест}1дяе ко:--;му тад1до, ввод и преобразовал ие ада; ;оговой инфор; адни в дкфропой дво -диь1Й ь од, который характеризует vei-iy/iuee состояние бдока 14 ;:;--.тдикоп j- -: c i-exh oлoyи iecкo -o агре- .та.

П;- таиие a iaJ ;oгc:вoй части модуля ос ущас 1 }1дяе :а:я с;т изсУ1ирую1це го источ- :ПД(а дитадид и источника опорного на- лу :-Д|;:епКД (не доказалы).

и13

В предлагаемом устройстве оборудование агрегатов может также управляться в ручном режиме от кнопок местного пункта управления по известным схемам дистанционного управления. Формула изобретения

Устройство для программного управления технологическим оборудованием, содержащее генератор импульсов, первый выход которого подключен к входу первого счетчика импульсов, выходы которого соединены с входами первого блока памяти, адресные выходы кото- рого соединены с первыми адресными входами терминального блока и второго блока памяти, выходы которого подключены к первым входам блока сравнения подключенного выходом через шину дан- ных к информационным входам вычислительного блока, выход кода операции первого блока памяти подключен к информационному входу вычислительного блока, отличающееся тем, что, с целью упрощения устройства путем сокращения числа проводов линии связи с периферийными блоками датчиков, в него введены по числу блоков датчиков цифроаналоговые преобразо-

От 5лока датчиков А

I

}712

ватели, триггер, многоканальньш ана- лого-:1,ифровой преобразователь, элемент И, второй счетчик импульсов и третий блок памяти, выходы которого подключены к первым выходам второго счетчика импульсов, соед шенного вто-- рым выходом с первьм входом триггера, второй вход которого подключен к выходу Конец преобразования многоканального аналого-цифрового преобразователя и к входу Запись-считывание второго блока памяти, информационные входы которого соединены с выходами многоканального аналого-цифрового преобразователя, адресные входы которого подключены к адресным выходам первого блока памяти, а информационные входы- к соответствующим выходам цифроанало- говьгх преобразователей, входы которых соединены с выходами соответств ьтощих блоков датчиков, первый вход элемента И соединен с выходом триггера, а второй вход с вторым выходом генератора импульсов, а выход - со счетным входом второго счетчика 1-1мпульсов, выходы третьего блока памяти соединены с вторыми входами блока сравнения и, через шину данных,- с вычислительным блоком.

Фиё.1

5

i

,.

.S...::fi- .. I

С:

SC

А

iT)

(50

ссэ

Редактор Е.Папп Заказ 3557

Ткра};: 8оЗПодписное

ВНИИПИ Государствек;1отс комитета СССР

по fienai-i -азобрете НИИ к отлрытий 113035, Москва,, Ж-ЗЗ, Рауиская чаб.. д, 4/5

Производственно-полиграфическое :;редир и; тпе j г. Ужгород, уд. Проектная. 4

| АСИНХРОННЫЙ ДВИГАТЕЛЬ С КОРОТКОЗАМКНУТЫМ РОТОРОМ, ПУСКАЕМЫЙ В ХОД БЕЗ РЕОСТАТА | 1923 |

|

SU1024A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| ПО Электроника, 1979 | |||

| Устройство для программного управления технологическим оборудованием | 1980 |

|

SU926619A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-23—Публикация

1985-07-23—Подача