ляется низкое быстродействие при его использовании в контуре управления процессом в реальном масштабе времени, где операнды формируются поразрядно, начиная со старших разрядов, вне устройства. Известно устройство для вычитания чисел с плавающей запятой, содержаще регистры порядков первого и второго слагаемых, сумматор мантисс, регистр мантисс первого и второго слагаемых cyMMai;op порядков и регистр предварите.льного порядка 4. Данное устройство не позволяет совмещать во времени процессы поразрядного ввода слагаемых и их обработ ку. Следовательно, существенным недостатком такого устройства является низкое быстродействие при вычитании операндов, формирующихся вне устройства и поступающих на его входы последовательно старшими разрядами. вперед. Наиболее близким к предлагаемому является устройство для выполнения операций сложения и вычитания с плавающей запятой, содержащее регистры порядков первого и второго операндов, регистры мантисс первого и второго операндов, регистр кода операции, коммутатор порядков, выхода которого подключены к входам схемы кор ректировки:, порядка, коммутатор мантисс, управляющий вход которого соединен с управляющим входом коммутатора порядков и подключен к выходу схемы сравнения порядков. Кроме того устройство содержит схему для определения модуля разности порядков, схему для увеличения на единицу моду ля разности порядков, схему для сдви га на один разряд вправо мантиссы, соответствующей большему порядку, схему для сдвига вправо мантиссы, со ответствующей меньшему порядку, схему для вычисления мантиссы результата операции и схему нормализации,содержащую детектор нормализационного сдвига влево модуля мантиссы результата, схему для выполнения этого сдвига и схему для вычисления порядка р ультата операции 5 , Недостатком известного устройства является низкое быстродействие при егоиспользовании в контуре управления в реальном масштабе времени, гд.операнды формируются поразрядно вне устройства, поскольку этому устройству для получения результата опе раций потребуется выполнить поразряд ный ввод операндов, выравнивание их порядков, суммирование мантисс операндов и нормализацию результата последовательно во времени. . Целью изобретения является увели ение быстродействия устройства, за счет совмещения во времени процессов поразрядного ввода операндов, выравнивания их порядков, суммирования и нормализации. Поставленная цель достигается тем, что в устройство, содержащее триггер операции, коммутатор мантисс, блок сравнения порядков, блок вычисления разности порядков, коммутатор порядков, блок корректировки порядка, счетчик нормализации и блок вычисления порядка результата, первая группа входов которого соединена с выходами счетчика нормализации, а вторая группа входов - с выходами блока корректировки порядка, подключенного своими входами к выходам коммутатора порядков , управляющий вход которого соединен с первым упр авляющим входом коммутатора мантисс и подключен к выходу блока сравнения порядков, содержит сумматор, дешифратор, триггер, два коммутатора выравнивания порядков, элемент ИЛИ, блок сравнения с .минимальным порядком, регистр управления, регистр порядка результата и два сдвигающих регистра, причем . первые группы входов блока сравнения порядков, блока вычисления разности порядков и коммутатора порядков соединены однсГименными входами между собой и подключены к входным шинам порядка первого операнда,входные шины порядка второго операнда подключены к соответствующим входам второй группы входов коммутатора порядков, блока сравнения порядков и блока вычисления разности порядков, выходы которого подключены к одноименным управляющим входам двух коммутаторов выравнивания порядков, причем выходы первого и второго коммутаторов выравнивания порядков подключены к первому и второму входам второго слагаемого сумматора, к выходам которого подключены выходные шины мантиссы результата устройства и входы дешифратора, который своим первымвыходом соединен с единичным входом триггера, а вторым своим выходом дешифратор подключен к счетному входу счетчика нормализации,вход установки нуля которого соединен со входами установки нуля сдвигающих регистров, сумматора и подключен к выходу элемента ИЛИ, который первым входом соединен с выходом блока сравнения с минимальным порядком, а вторым входом - с входом установки нуля регистра порядка результата, с выходом старшего разряда регистра управления и с нулевьам входом триггера, который своим прямым выходом подключен к управляющему входу регистра управления, входу блокировки блока сравнения с минимальным порядком и К входу разрешения записи регистра порядка результата, выходы которого подключены к выходным шинам порядка

результата устройства, .а информационные входы соединены с выходами блока вычисления порядка результата и с входами блока сравнения с минимальным порядком, выходы первого сдви- . гакмцего регисхра подключены,к всем кроме первого, информационным входам nepBorjo коммутатора выравнивания порядков, первый информационный вход которого соединен с информационным входом последовательного ввода первого ввода первого сдвигающего регистра и с первым выходом второй группы выходов коммутатора мантисс, первая группа входов которого под ключена к входным шинам мантиссы первого операнда устройства, а второ своей группой входов коммутатор мантисс подключен к входным шинам мантиссы второго операнда устройства причем своим вторым управляющим входом коммутатор мантисс соединен с выходом триггера операции, а своей первой группой выходов коммутатор матисс подключен к входам первого слагаемого сумматора, выходы второго сдвигающего регистра подключены к всем, кроме первого, информационным входам второго коммутатора выравнива ния порядков, первый информационный вход которого соединен с информационным входом последовательного ввода второго сдвигающего регистра и с вторЕлм из выходов второй группы выходов коммутатора мантисс.

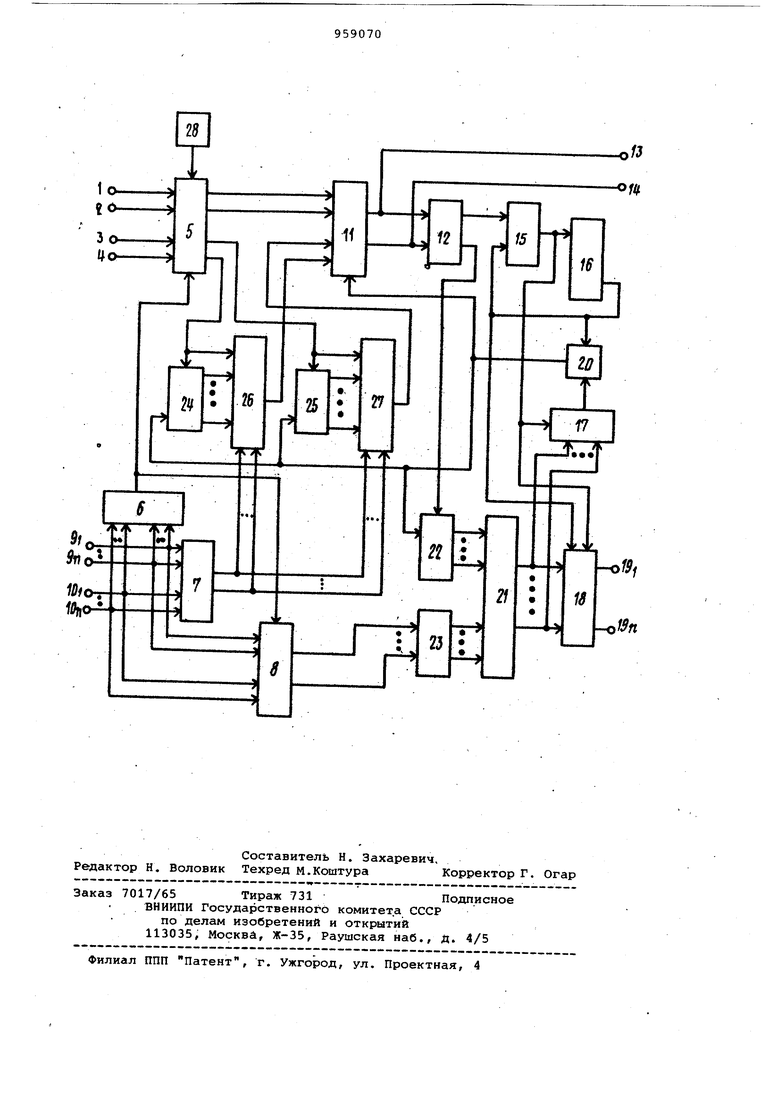

На чертеже представлена структурная схема предлагаемого устройства для сложения и вычитания чисел.

Устройство содержит входные шины 1 и 2 разрядов мантиссы первого операнда устройства, входные шины 3 и 4 разрядов мантиссы второго операн-да устройства, коммутатор 5 мантисс, причем входные шины 1 и 2 подключены к первой группе входов коммутатора 5 мантисс, вторая группа входов которого подключена к входным шинам 3 и 4. Устройство также содержит бло 6 сравнения порядков, блок 7 вычисления разности порядков, коммутатор 8 порядков, входные шины 9 -9,, порядка первого операнда устройства, входные шины 10)-10г, порядка второго операнда устройства, причем i-е входы первых групп входов блоков 6 к 7 и коммутатора 8 соединены между собой и подключены к входной шине 9 порядка первого операнда устройства, а i -е -ВХОДЫ вторых групп входов блоков .6 и 7 и коммутатора 8 соединены между собой и подключены к входной шине 10,- порядка второго операнда устройства. Выход блока 6-соединен с управляющими входами коммутаторов 5 и б. Кроме того, в состав устройства входят сумматор 11, дешифратор 12, выходные шины 13 и 14- разрядов мантиссы результата устройства, триггер

15, регистр 16 управления,блок 17 сравнения с минимальным порядком, регистр 18 порядка результата, выходные шины , порядка результата устройства, элемент 20 ИЛИ, блок 21 вычисления порядка результата, счетчик 22 нормализации, блок 23 корректировки порядка, сдвигающие регистры 24 и 25, коммутаторы 26 и 27 выравнивания порядков:и. триггер 28 опера0ции.

Первая группа выходов коммутатора мантисс 5 подключена к входам первого слагаемого сумматора 11, который своими выходами связан с входами де шифратора 12 и с выходными шинами

5 13 и 14 мантиссы результата.

Дешифратор 12 своим первым выходом соединен с единичным входом триггера 15, прямой выход которого подклю0чен к управляющему входу регистра 16 управления, входу блокировки блока

17сравнения с минимальным порядком и к входу разрешения записи регистра

18порядка результата. Выходы регист5ра порядка результата 18 подключены

к выходным шинам порядка результата устройства, а вход установки нуля этого регистра соединен с выходом старшего разряда регистра 16

0 управления, с нулевым входом триггера 15 и с первым входом элемента 20 ИЛИ, второй вход которого подключен к выходу блока 17 сравнения с минимальным порядком. Входы блока 23

5 подключены к выходам коммутатора порядков 8, а выходы - к второй группе входов блока 21. Первая группа входов блока 21 соединена с выходами счетчика 22 нормализации, вход уста0новки нуля которого подключен к выходу элемента 20 ИЛИ и соединен со входами установки нуля сумматора 11 и сдвигающих регистров 24 и 25. Выходы регистра 24 подключены ко всем,

5 кроме первого, информационным входам коммутатора 26 выравнивания порядков,; а выходы регистра 25 - ко всем кроме ,дервогО|информационным входом коммугатора 27 выравнивания порядков.Коммутаторы 26 и 27 соединены между со0бой i-ми управляющими входами,которые подключены к выходам блока 7, Выходы коммутаторов 26 и 27 соедине;Ны с первым и вторым входами второго слагаемого сумматора 11 соответствен5но. .Инфорьиционные входы последова ; тельного ввода операндов регистров 24 и 25 соединены с-первыми информационными входами соответственно коммутаторов 26 и 27 и подключены к

0 второй группе выходов коммутатора мантисс 5, второй управляющий вход которого подключен к прямому выходу триггера 28 операции, и, кроме того, счетный вход счетчика 22 подключен i

5 к второму выходу дешифратора 12. Блок б сравнения порядков представляет собой схему сравнения -раз рядных чисел. Этот блок выполняет сравнение порядков с учетом их знаков и формирует на своем выходе сиг нал логической 1, если порядок пе вого операнда больше или равен поряд ку второго операнда, и логический О - в противном случае. Блок 7 вычисления разности поряд ков может быть построен на основе вычи тателя,или сумматора п -разрядных чисе выполняющего вычитание порядков опера дов с учетом их знаков. На выходе этого блока формируется модуль разности порядков операндов. Блок 23 корректировки порядка предназначен для увеличения больщего порядка яа величину +2. Этот блок мо жет быть построен на основе сумматора п-разрядных чисел, выполняющего суммирование большего порядка с числом +2 с учетом знака порядка. Блок 21 вычисления порядка резуль тата предназначен для формирования текущего значения порядка результата в зависимости от значений цифр манти сы результата. Этот блок может быть построен на основе вычитателя или сумматора п-разрядных чисел, выполня ющего операцию вычитания чисел с уче том их знаков. Блок 17 сравнения с минимальным порядком представляет, собой схему сравнения текущего значения порядка с величиной минимального порядка с учетом их знаков. Величина минимального порядка при п -разрядах порядка равна -2 (один разряд порядка используется для представления его знака), Если величина минимального порядка совпадает с текущим значением порядки, то блок 17 формирует на выходе сигнал логической 1. Сигнал логической 1 на входе блокировки блока 17 запрещает формирование сигнала совпадения на выходе этого блока. Регистр 16 управления представляет собойm-разрядный сдвигающий регистр, при этом любое число А с плавающей запятой имеет вид .,-i-% где Р - величина порядка; m - разрядность мантиссы; р,-- цифры мантиссы. В предлагаемом устройстве для представления порядков операндов используется двоичная система счислеНИН с. Цифрами 1 и О. Для представленая мантисс операндов , которые поступают на входы устройстЕ.а последовательно, старшими разрядами вперед, используется избыточная двоичная система с цифрами 1, О, 1. Цифры избыточной двоичной системы можно представить сочетаниями цифр 1 и О двоичной системы в соответствии с табл. 1. Таблица 1 Сумматор 11 предназначен для суммирования последовательно поступающих мантисс операндов со старших разрядов, представленных в избыточ- . ной двоичной системе с цифрами 1, О и 1. Этот сумматор может быть построен на основе двух комбинационных двухразрядных cs iMaTopOB и трех элементов задержки, в качестве которых могут быть применены триггеры с внутренней задержкой. Нулевые входы этих триггеров соединены с входом установки нуля сумматора 11. На входы синхронизации этих триггеров, так же как и .на входы синхронизации регистра-16, регистров 24 и 25 и дешифратора 12, подаются сигналы, которые синхронизируют поступление разрядов мантисс операндов на входы устройства (входы синхронизации на чертеже условно не показаны)- Коммутаторы 26 и 27 предназначены для выравниэания порядков операндов, первые информационные входы коммутаторов 26 и 27, соединенные соответственно с информационными входами последовательного ввода операндов регистров 24 и 25, подключаются к их выходам если дэоичный код на, их управляющих входах есть нуль, если этот код не нуль, то к выходам коммутаторов 26 и 27 подключаются их информационные входы, соединенные с соответствующими выходами регистров 24 и 25. Регистры 24 и 25 имеют «1+2 разрядов. Следовательно, старшие, т+2 разряды этих регистров соединены с т+3 информационными входами коммутаторов 26 и 27 и дляих подключения к выходу коммутаторов необходимо по дать управляющий код, равный т+2. Если управляющий код превышает значение т+2, то на выходы коммутаторов подается логический О. Коммутатор 5 мантисс предназначен для подключения входных шин мантисс . числа, имеющего больший порядок,

к входам первого слагаемого сумматора 11, а также для подключения входных шин мантиссы числа, имеющего меньший порядок, ко входам регистров 24 и 25, и коммутаторов 26 и 27.Кро:ме того, коммутатор 5 выполняет инвертирование сигналов, поступающих на входные шины 3 и 4 мантиссы второго операнда по управляющему сигналу от триггера 28 операций для реализации устройством операции вычитания.

Дешифратор 12 предназначен для декодирования кодов цифр мантиссы результата по сигналам, синхронизирующим поступление разрядов мантисс операндов , При поступлении на входы дешифратора 12 кодов цифр 1 или 1, сигнал логической 1 формируется на первом выходе дешифратора 12, который подключен к единичному входу триггера 15. Если на входы дешифратора 12 поступает код цифры О, то сигнсш логической 1 формируется на втором его выходе, который соединен со счетным входом счетчика 2 нормализации.

Устройство работает следующим образом.

Перед выполнением операции все регистры, счетчик и триггеры устанавливаются в нулевое состояние. Затем в триггер операции 28 заносится код операции, и на его прямом выходе устанавливается логический О для операций сложения, либо логическая 1 для операции вычитания.

На шины 9-1 .-9 у с тройств а поступает двоичный код порядка первого операнда, а на шины двоичный код порядка второго операнда. Блок 6 выполняет сравнение поступивших на его входы порядков и формирует соответст вующий сигнал на выходе. .Этот сигнал является управляющим для коммутаторов 5 и 8. Коммутатор 8 выполняет подключение большего порядка ко входам блока 23 корректировки порядка, который этот порядок с учетом его знака суммирует с числом +2. Блок 21 на своих выходах формирует разность двоичных кодов чисел, поступающих от блоков 23 и 22, причем код на выходах блока 23 является уменьшаемым, а код на выходах блока 22 - вычитанием. При этом блок 17 выполняет сравнение двоичного кода на выходах блока 21 с двоичным кодом минимального порядка. Кроме того, блок 7 на своих выходах формирует ДВОИЧНЫЙ код модуля разности порядков, который задает для коммутаторов 26 и 27 номер их информационного входа, подключаемого к их выходам.

Одновременно с поступлением порядков операндов, на входные шины 1, 2 и 3, 4 поступают коды старших разрядов мантисс опер)андов. Коммутатор 5 в зависимости от выполняемой операции (сложение или вычитание) не инвертирует или инвертирует коды на входных шинах 3 и 4. Кроме того, в зависимости от выходного сигнала блока 6 коммутатор 5 выполняет подключение входной шины 2 или 4 к входам регистра 24 и коммутатора 26 мантиссы того числа, которое обладает меньшим порядком. Если же порядки операндов равны, то к входам указанных регистров и коммутаторов подключаются входные шины 3 и 4. Входные шины мантиссы числа, обладающего боль шим порядком, подключаются коммутатором 5 к входам первого слагаемого сумматора 11.

Регистры 24 и 25 и коммутаторы 26 и 27 выполняют выравнивание порядков операндов по управляющему двоичному коду от блока 7, т.е. обеспечивают поступление на входы второго слагаемогЬ сумматора 11 разрядов мантиссы меньшего порядка с таким же весом, как и у разрядов мантиссы, поступающих на входы первого слагаемого сумматора 11. Сумматор 11 выполняет суммирование разрядов операндов. На его выходах формируются разряды мантиссы результата. По синхронизирующему сигналу коды этих разрядов через выходные шины 13 и 14 выдаются из устройства. Кроме того, эти коды анализируются дешифратором 12. Если текущей цифрой мантиссы.результата является О, то дешифратор 12 на своем втором выходе формирует сигнал логической 1.,Этот сигнал поступает на счетный вход счетчика 22 нормализации и увеличивает его содержимое на единицу. При этом, значение текущего порядка результата уменьшается на единицу, блоком 21. Кроме того, по синхронизирующему сигналу происходит

сдвиг информации-в сдвигающих регистрах 24 и 25, а на шины 1, 2 и 3, 4 поступают очередные разряды операндов. Сумматор 11 снова выполняет суммирование поступивших разрядов слагаемых, а дешифратор 12 выполняет анализ цифр мантиссы результата. Если текущая цифра снова О, то содержи;Мое счетчика нормализации 22 снова

увеличивается на единицу, а значение текущего порядка результата снова уменьшается на единицу блоком 21. Таким образом, выполняется совмещение во времени процессов поразрядного ввода операндов, выравнивание их порядков, суммирование и нормализация. Процесс, нормализации прекращается в случае, когда на выходах сумматора 11- будет получена первая значащая цифра мантиссы результата 1 или

,1,либо значение текущего порядка результата станет равным . Если получим первую значащую цифру мантиссы результата, то происходит следующее. По синхронизирующему сигналу

дешифратор 12 на свой первый выход

выдаст сигнал логической 1. Этот сигнал установит на выходе триггера 15 логическую 1, которая блокирует работу блока 17. Кроме того, 1 на выходе триггера 15 установит в единицу младший разряд регистра 16 управления. В регистр 18 по сигналу 1 от триггера 15 записывается Значение порядка результата, поступающего от блока 21, а на выходных шинах устанавливается порядок числа, мантисса которого вычисляется. Под действием синхронизирующих сигналов в регистре 18 порядка результата происходит сдвиг единицы, из младших раз-рядов в старшие, а сумматор 11 производит вычисление разрядов мантиссы результата. Процесс вычисления прекращается, когда единица в регистре управления 16 перейдет в гл-й разряд. При этом устройством выдается, через выходные шины 13 и 14, m -разрядов мантиссы результата. Логическая 1 в tn-M разряде регистра 16 управления устанавливает в нуль регистр 18 порядка результата триггер 15 и через элегмент 20 ИЛИ - сумматор 11, счетчик нормализации 22 и сдвигающие регистры 24 и 25. Таким образом, устройст:во подготавливается к обработке следующей пары операндов.

Если в процессе нормализации значение текущего порядка результата на

выходах блока 21 станет ра-вным (например, это возможно при вычитании равных между собой операндов), то блоком 17 выдается логическая 1 на вход элемента 20 ИЛИ. При этом

0 устройство подготавливается к обработке следующей пары операндов, так как устанавливаются в исходное нулевое состояние сумматор 11, счетчик 22 нормализации и регистры 24 и 25.

5 4

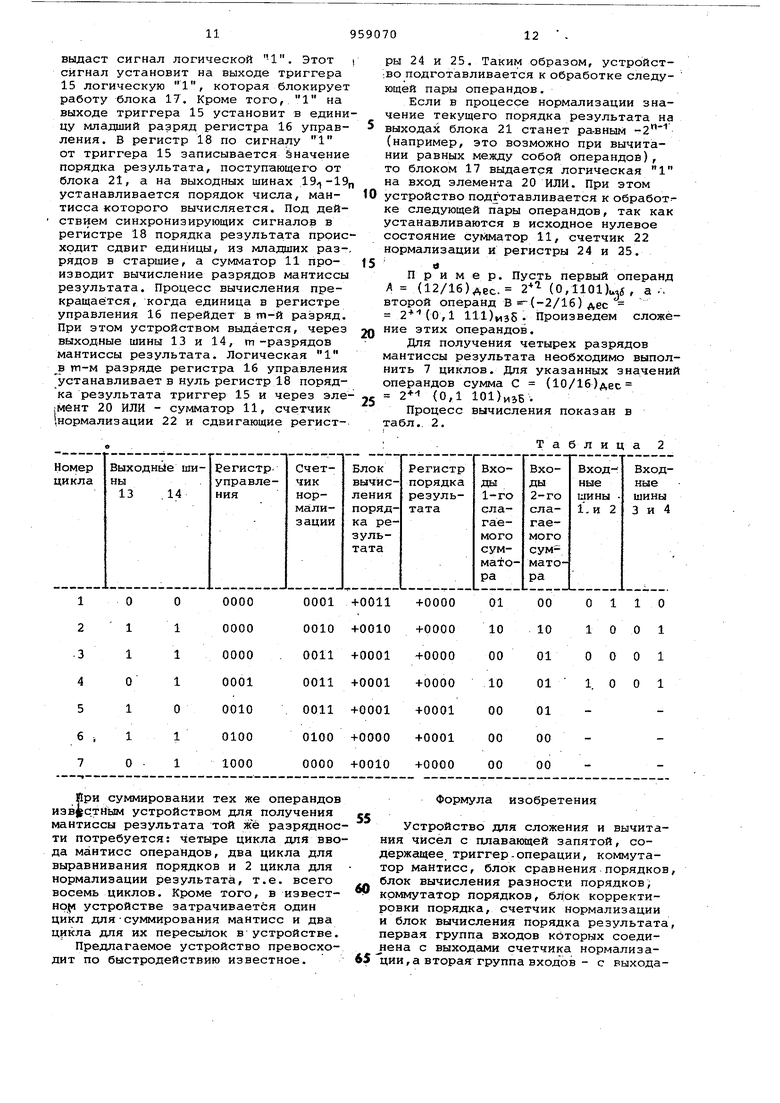

Пример. Пусть первый операнд

А (12/16)Аес. 2 (0,1101Ц«, а-. второй операнд В -(-2/16) дес (0,1 111 ) Произведем сложеQ ние этих операндов.

Для получения четырех разрядов мантиссы результата необходимо выполнить 7 циклов. Для указанных значений операндов сумма С (10/16)дес (0,1 101)изБ .

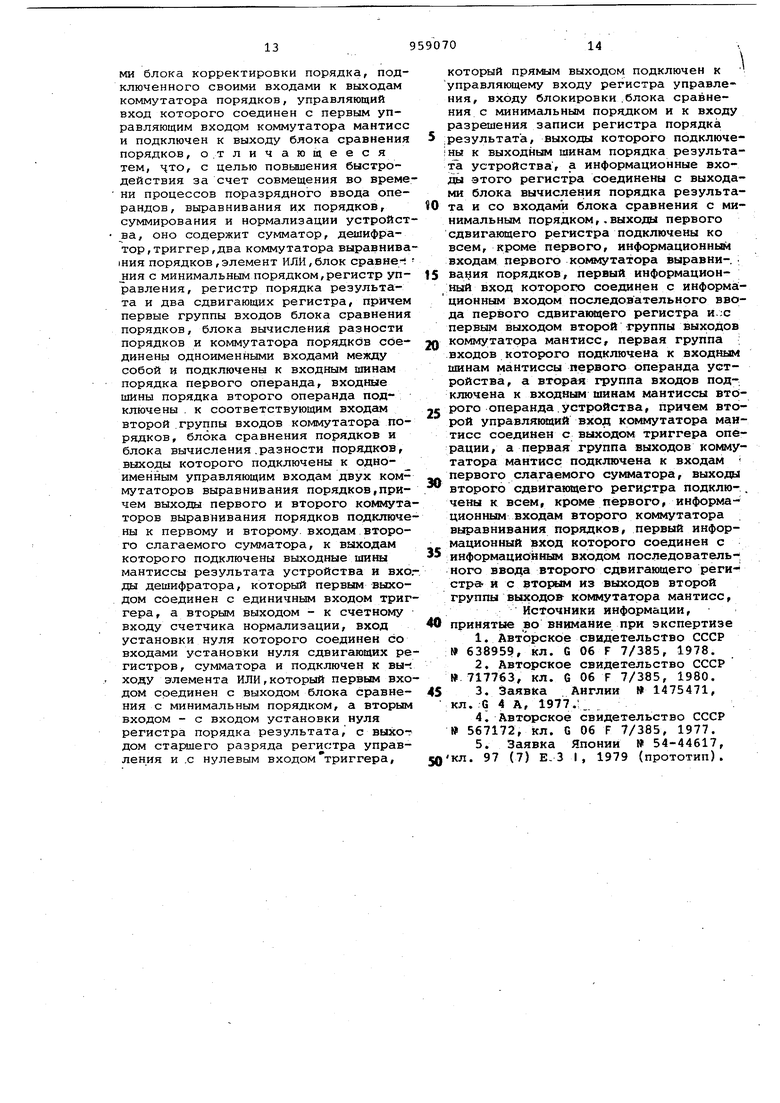

Процесс вычисления показан в табл.. 2.

: .Т а б л и ц а 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

Йри суммировании тех же операндов .тйым устройством для получения мантиссы результата той же разрядности потребуется: четыре цикла для ввода мантисс операндов, два цикла для выравнивания порядков и 2 цикла для нормализации результата, т.е. всего восемь циклов. Кроме того, в известнр|(л устройстве затрачивается один цикл длясуммирования мантисс и два цркла для их пересылок вустройстве.

Предлагаемое устройство превосходит по быстродействию известное.

Формула изобретения

Устройство для сложения и вычитания чисел с плавающей запятой, содержащее, триггер-операции, коммутатор мантисс, блок сравнения порядков, блок вычисления разности порядков; коммутатор порядков, блок корректировки порядка, счетчик нормализации и блок вычисления порядка результата, первая группа входов которых соедиjieHa с выходами счетчика нормализации,а вторая группа входов - с выходами блока корректировки порядка, подключенного своими входами к выходам коммутатора порядков, управляющий вход которого соединен с первым управляющим входом коммутатора мантисс и подключен к выходу блока сравнения порядков, о.тличающееся тем, что, с целью повьшзения быстродействия за счет совмещения во времени процессов поразрядного ввода операндов, выравнивания их порядков, суммирования и нормализации устройства, оно содержит сумматор, дешифратор, триггер, два коммутатора выравнивашия порядков,элемент ИЛИ,блок сравне 1ия с минимальным порядком,регистр управления, регистр порядка результата и два сдвигающих регистра, причем первые группы входов блока сравнения порядков, блока вычисления разности порядков и коммутатора порядков соединены одноименными входами между собой и подключены к входным шинам порядка первого операнда, входные шины порядка второго операнда подключены . к соответствующим входам второй .группы входов коммутатора порядков, блока сравнения порядков и блока вычисления .разности порядков, выходы которого подключены к одноименным управляющим входам двух коммутаторов выравнивания порядков,причем выходы первого и второго коммутаторов выравнивания порядков подключены к первому и второму входам второго слагаемого сумглатора, к выходам которого подключены выходные шины мантиссы результата устройства и вхо ды дешифратора, который первым выходом соединен с единичным входом триггера, а вторым выходом - к счетному входу счетчика нормализации, вход установки нуля которого соединен со входами установки нуля сдвигающих регистров, сумматора и подключен к вы-; ходу элемента ИЛИ,который первым входом соединен с выходом блока сравнения с минимальным порядком, а вторым входом - с входом установки нуля регистра порядка результата, с выходом старшего разряда регистра управления и .с нулевым входомтриггера.

который пряким выходом подключен к управляющему входу регистра управления, входу блокировки .блока сравнения с минимальным порядком и к входу разрешения записи регистра порядка

:результата, выходы которого подключе ны к выходным шинам порядка результата устройства, а информационные входы этого регистра соединены с выходами блока вычисления порядка результата и со входами блока сравнения с минимальным порядком,.выходы первого сдвигающего регистра подключены ко всем, кроме первого, информационным входам первого коммутатора выравни-.

вания порядков, первый информационньй вход которого соединен с информа:ционным входом последовательного ввода первого сдвигакицего регистра и.;с первым выходом второй группы выходов

коммутатора мантисс, первая группа ; входов которого подключена к входным шинам мантиссы первого операнда устройства, а вторая группа входов под-; ключена к входным шинам мантиссы второго операнда.устройства, причем второй управляющий вход коммутатора мантисс соединен с выходом триггера операции, а первая группа выходов коммутатора мантисс подключена к входам первого слагаемого сумматора, выходы второго сдвигающего региртра подклю-. чены к всем, кроме первого, информационным входам второго коммутатора выравнивания порядков, первый информационный вход которого соединен с

информационным входом последовательного ввода второго сдвигающего регистра- и с вторым из выходов второй группы выходов коммутатора мантисс,

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-15—Публикация

1980-12-16—Подача