Известны счетные устройства с потенциальным запуском, содержащие элементы памяти, вентили и схему «НЕ».

Предлагаемое устройство отличается тем, что оно содержит дополнительный элемент памяти, фиксирующий паузы, входы которорого через вентили и схему «НЕ» соединены со входной шиной, а управляющие входы вентилей и выходы дополнительного элемента памяти подключены соответственно к выходам основных элементов памяти счетного устройства.

Это позволяет сократить количество оборудования устройства.

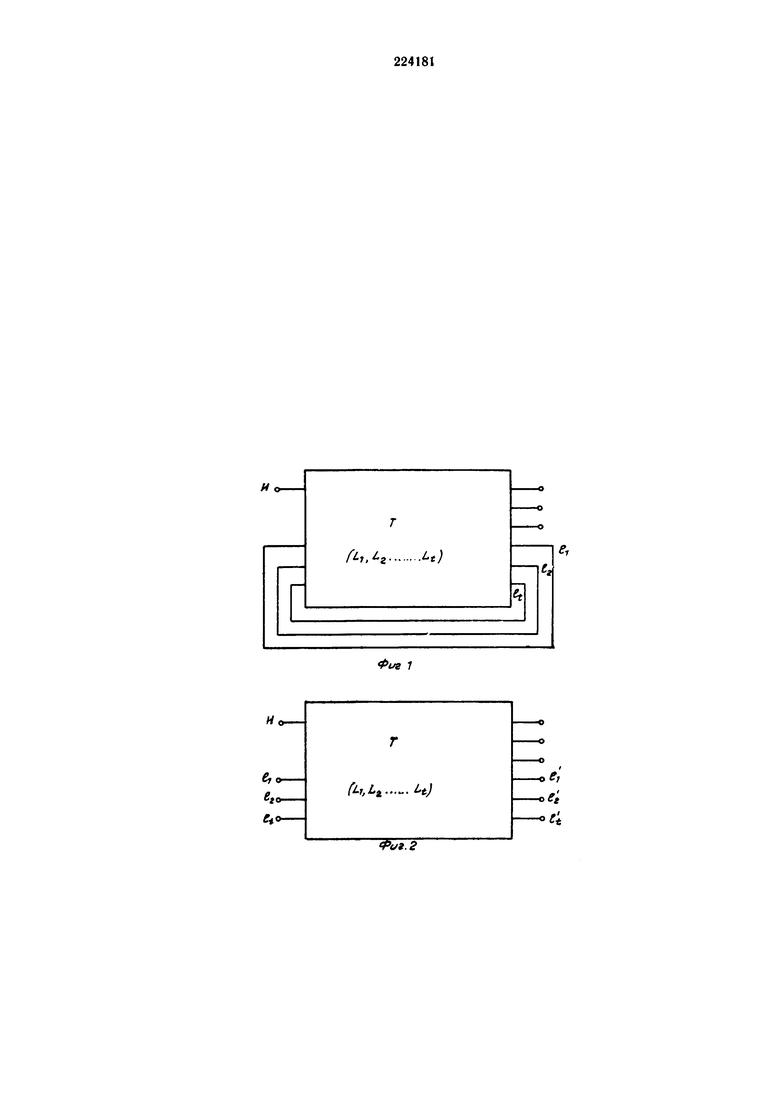

Скелетная схема счетного устройства без декодирующего узла изображена на фиг. 1 и 2. На фиг. 3 и 4 приведены конкретные варианты счетных устройств соответственно на бесконтактных и релейных элементах.

Скелетная схема представлена в виде многополюсника с одним входом И, который содержит запоминающие элементы L1, L2, … Lt, а также управляемые ими цепи обратной связи  .

.

На фиг. 2 обратные связи рассечены. Счетное устройство представлено в виде многополюсника, имеющего (t+1) вход И,  и t выходов

и t выходов  .

.

Совокупность значений переменных на входах обозначается через И, а соответствующая им совокупность состоящих элементов памяти - через  .

.

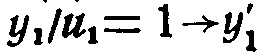

Начальные условия можно записать следующим образом:

*) Символ «→» - знак логической операции, называемой импликацией. Расшифровывается он словом «влечет».

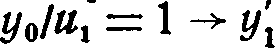

Это значит, что в начальный момент совокупность сигналов на входах при отсутствии сигнала И (И0=0) влечет совокупность  состояний запоминающих элементов. При первом появлении сигнала И (И1=1) создаются условия для изменения состояний запоминающих элементов, т.е.

состояний запоминающих элементов. При первом появлении сигнала И (И1=1) создаются условия для изменения состояний запоминающих элементов, т.е.

Запоминающие элементы меняют свое состояние и, вследствие обратной связи, меняется совокупность сигналов на входах:

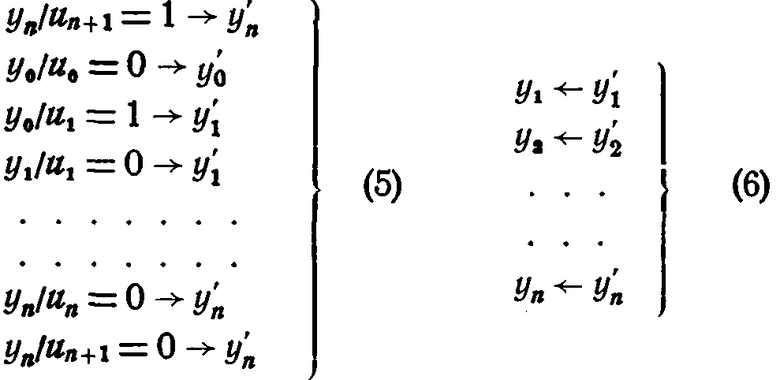

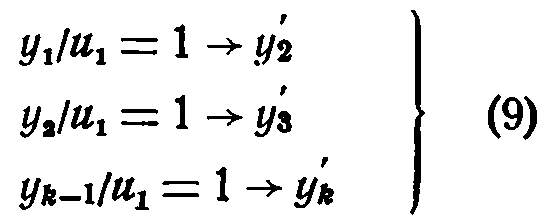

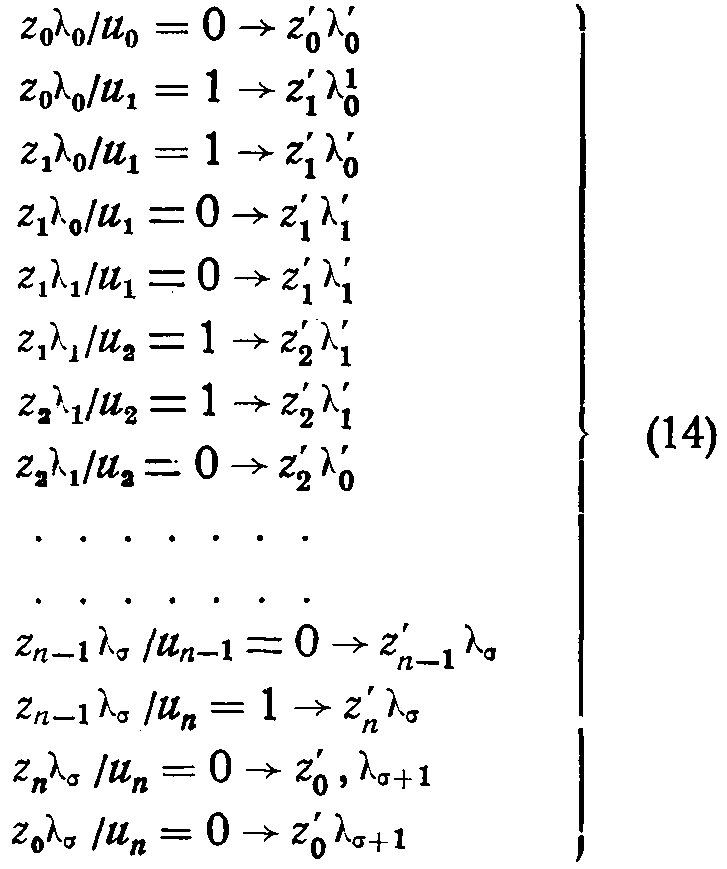

Повторяя предыдущие рассуждения, можно получить систему рекуррентных уравнений, которая характеризует последовательность работы счетного устройства до n счетов при изменении сигнала на входе n+1 раз:

Набор импликаций (4) разбивается на два набора:

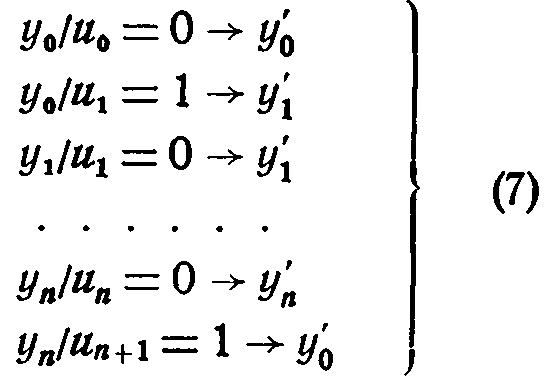

Каждая импликация в наборе (5) называется тактом. Все импликации при одном i называются импликациями цикла i. Поскольку система (5) описывает условия подготовки цепей срабатывания запоминающих элементов, а система (6) устанавливает тот факт, что при изменении состояний запоминающих устройств меняются сигналы на их входах, то при синтезе схемы достаточно задать систему (5). Для кольцевого счетчика система (5) будет иметь вид:

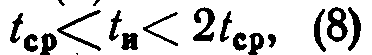

Наборы импликаций (5) и (7) описывают только частный случай, когда

где tcp - время изменения состояний запоминающих устройств;

tи - продолжительность сигнала И.

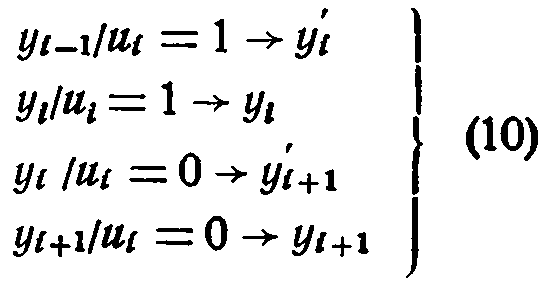

Первая часть неравенства (tср<tи) очевидна, так как в противном случае схема не успела бы перейти в следующее состояние. Если нарушена вторая часть неравенства, то при tи>2tср в наборах (5) и (7) после импликации  вместо

вместо  будет следовать

будет следовать

Такой режим практически непригоден для работы счетного устройства из-за нерационального использования состояния запоминающих устройств, а также из-за нестабильности tср и tи. Первое приводит к большому числу элементов, а второе - к неоднозначности отсчета, поэтому импликации цикла примут вид:

где i=1, 2, 3 … n.

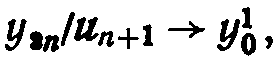

Теоретически режим (9) пригоден для отсчета длительного импульса. При этом, если счетчик кольцевой,  а если конечный, обычно вводятся условия (n+1)-20 цикла.

а если конечный, обычно вводятся условия (n+1)-20 цикла.

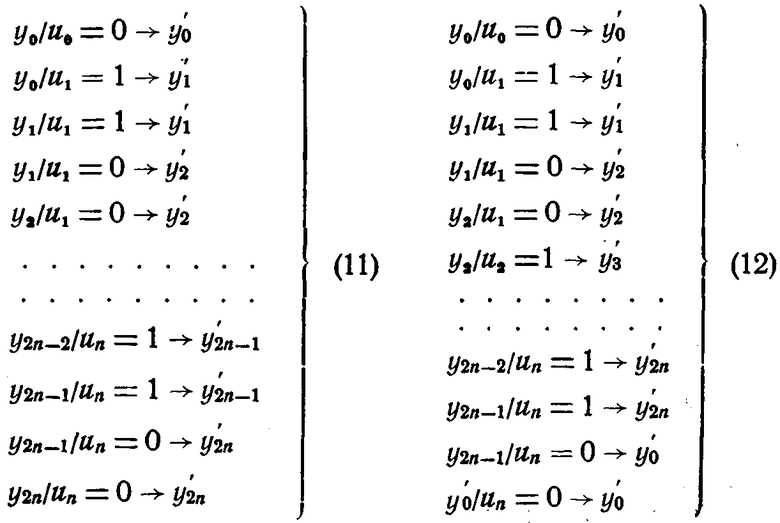

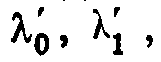

Таким образом, в общем случае работа конечного счетчика описывается системой логических уравнений (11), а кольцевого - системой (12).

Введем (к+1) элемент.

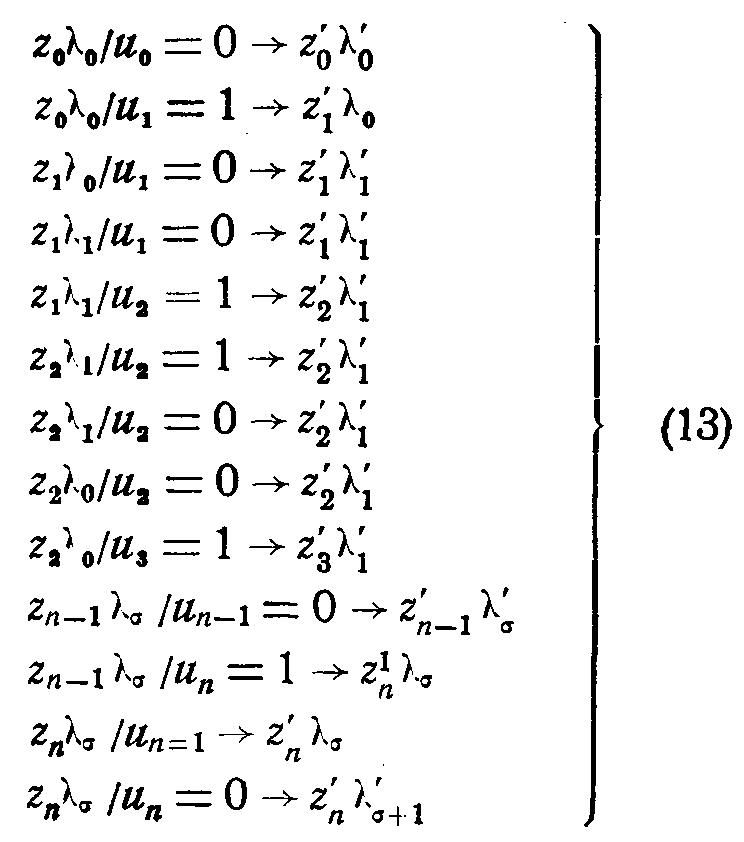

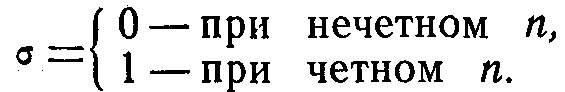

Обозначим состояние дополнительного элемента памяти через  а соответствующие им значения переменной - через λ0 и λ1.

а соответствующие им значения переменной - через λ0 и λ1.

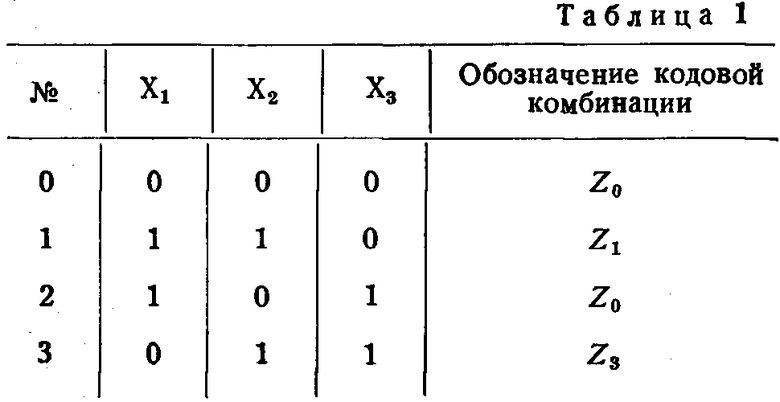

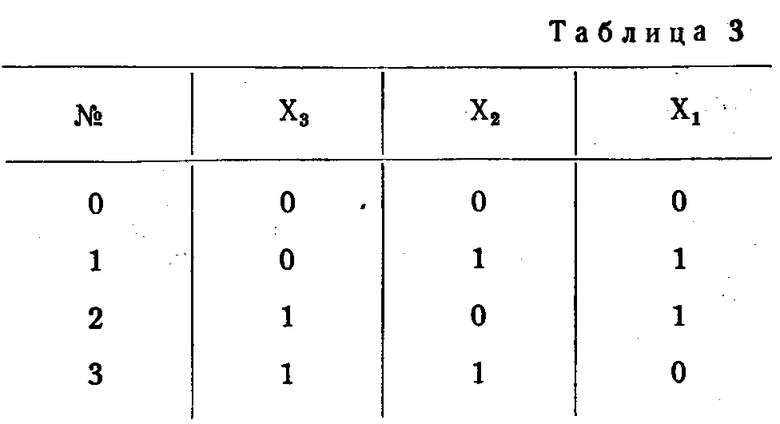

Например, пусть задан код «2 из 3», показанный в табл. 1.

В ее первом столбце записаны номера импульсов от «0» до «3», во втором, третьем и четвертом - соответствующие каждому из этих номеров последовательности в коде «2 из 3». Последний столбец показывает обозначения последовательности этой таблицы в уравнении (13).

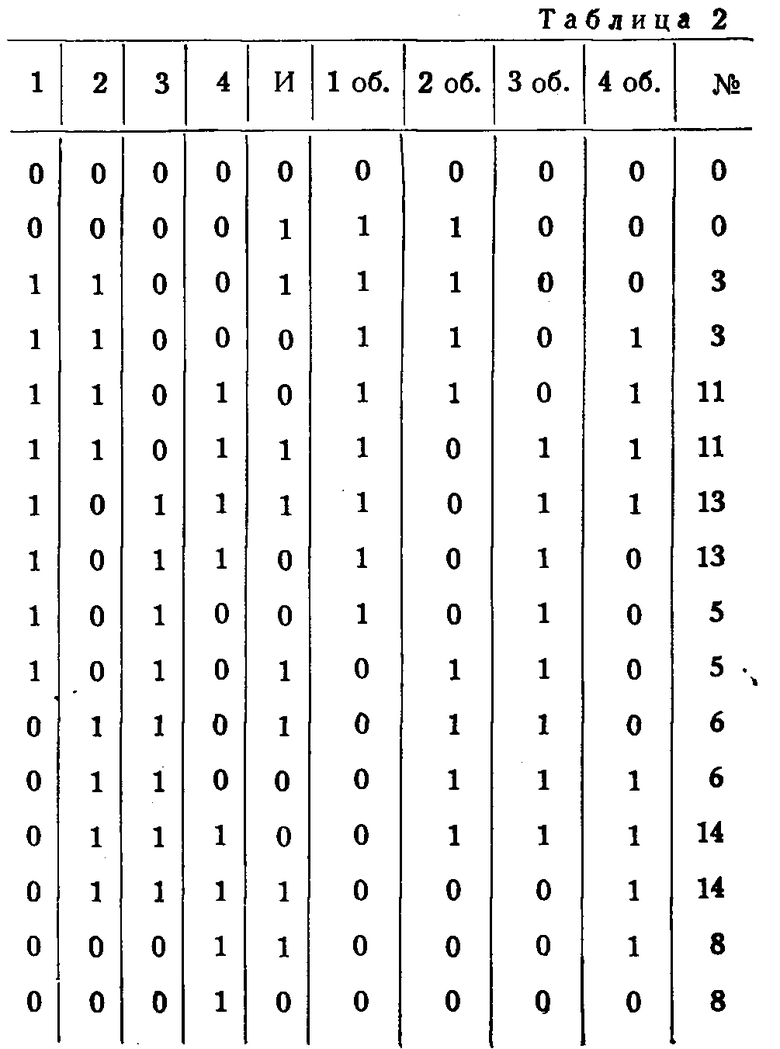

Подставляя последовательности, приведенные в табл. 1, в уравнение (13), можно получить табл. 2.

Таблица 2 состояний счетного устройства, работающего в коде «2 из 3», состоит из двух частей. Если схема реализуется на электромагнитных реле (хотя в общем случае можно использовать любые другие элементы релейного действия), то первые три столбца первой части показывают положение контактов реле, соответствующих первому, второму и третьему элементам кода «2 из 3», четвертый столбец показывает положение дополнительного элемента, пятый - положение импульсного входа. Вторая часть таблицы показывает положение обмоток (токовое или бестоковое).

Будем считать, что состояние элемента λ меняется только в паузу, причем состояния yi совпадают с соответствующими состояниями zi выходного кода. Тогда системы логических уравнений (11) и (12) примут вид:

Первые три столбца второй части показывают положение обмоток реле, соответствующих элементам кода, четвертый столбец - положение обмотки дополнительного реле. «0» обозначает нормальное разомкнутое состояние контактов или бестоковое положение обмотки, а «1» - нормальное замкнутое состояние контактов или токовое положение обмотки.

В последнем столбце приведены номера, которые вычисляются следующим образом.

Каждому столбцу присваивается произвольный вес (в данном случае 1-1, 2-2, 3-4, 4-8). Для каждой строки вес столбца умножается на значение переменной в строке и результаты умножения складываются.

Например, для первой и второй строк столбца номер будет:

0·1+0·2+0·4+0·8=0,

для третьей и четвертой:

1·1+1·2+0·4+0·8=3,

для пятой и шестой:

1·1+1·2+0·4+1·8=11 и т.д.

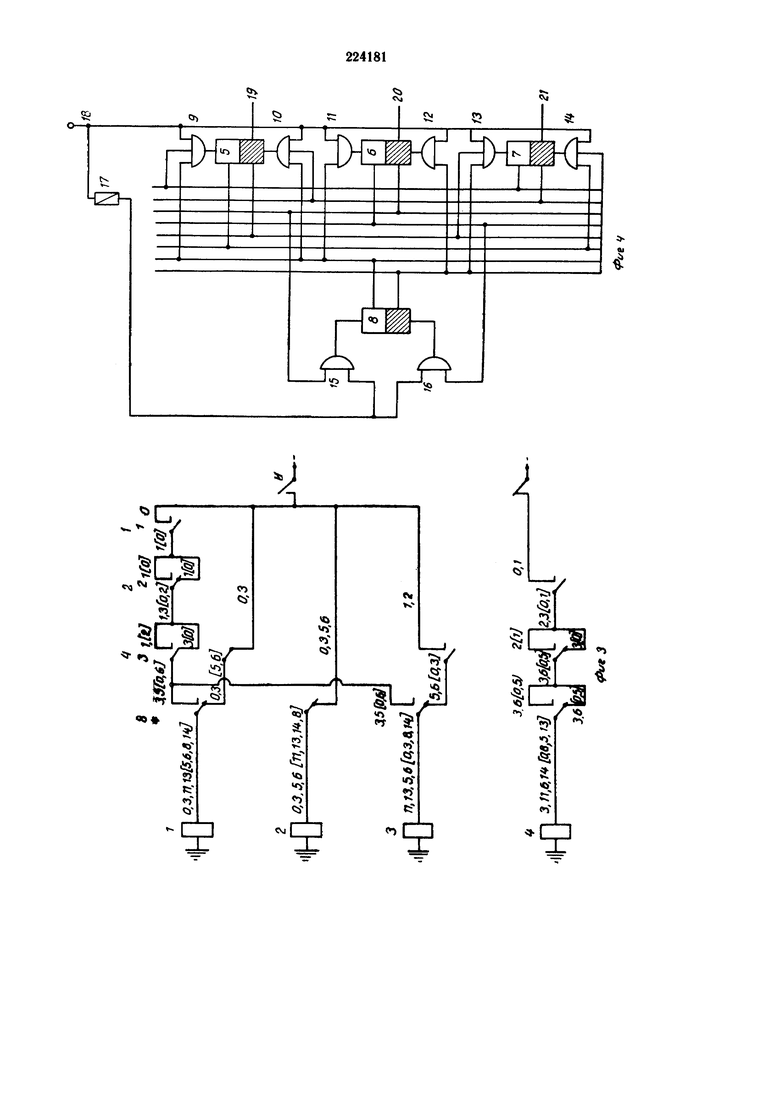

На фиг. 3 приведено построение счетной схемы, выполненное численно-графическим методом в соответствии с таблицей 2 на основе логических уравнений для рассматриваемого в примере случая.

Слева изображены обмотки реле. Для обмотки 1 из таблицы 2 выписаны номера, при которых И=1 и обмотка 1 находится под током (1 об.=1).

В квадратных скобках выписаны номера, при которых И=1, а обмотка 1 находится в бестоковом состоянии (1 об.=0), аналогично для обмоток 2 и 3. Для обмотки 4 выписаны состояния, когда И=0, а 4 об.=1, в квадратных скобках - когда И=0, а 4 об.=0.

Синтез происходит следующим образом.

1) Сверху на фиг. 3 выписывают номер реле с наибольшим весом (в данном случае 8); у каждой обмотки рисуют группу на переключение; у контакта на замыкание пишут все номера, большие или равные взятому весу, уменьшенные на его величину. У контакта на размыкание пишут без изменения номера меньше выбранного веса.

2) Просматривают вновь полученные наборы номеров, одинаковые наборы объединяют и им приписывают один набор.

3) Выписывают сверху следующий вес и проделывают указанные выше операции.

При И=0 легко доказать, что все цепи  состоят из контакта на замыкание. Поэтому эти цепи не синтезируют.

состоят из контакта на замыкание. Поэтому эти цепи не синтезируют.

На фиг. 4 в качестве примера приведена принципиальная схема устройства, работающего на следующий узел, у которой входным является код «2 из 3» (см. табл. 1). Схема выполнена на бесконтактных элементах. Цифрами 5, 6 и 7 обозначены соответствующие элементам кода элементы памяти; цифрой 8 -элемент памяти, фиксирующий паузу. Цифрами 9-16 обозначены схемы совпадения (схема «И»), 17 - схема «НЕ», 18 - вход устройства, 19, 20, 21 - соответственно выходы элементов памяти 5, 6, 7. Схема совпадения 9 связана с запускающим входом элемента памяти 5, сбрасывающий вход которого соединен с выходом схемы совпадения 10.

Прямой и инверсный выходы элемента памяти 5 соединены соответственно со входами схем совпадения 13 и 14. Схема совпадения И связана с запускающим входом элемента памяти 6, сбрасывающий вход которого соединен с выходом схемы совпадения 12. Прямой и инверсный выходы элемента памяти 6 соединены соответственно со входами схем совпадения 15 и 16.

Схема совпадения 13 связана с запускающим входом элемента памяти 7, сбрасывающий вход которого соединен с выходом схемы совпадения 14. Прямой и инверсный выходы элемента памяти 7 соединены со входами схем совпадения соответственно 10 и 9.

Схема совпадения 15 связана с запускающим входом элемента памяти 8, сбрасывающий вход которого соединен с выходом схемы совпадения 16. Прямой и инверсный выходы элемента памяти 8 соединены со входами схем совпадения соответственно 12, 13, 14 и 9, 10, 11.

В исходном положении элементы памяти 5, 6 и 7 в нерабочем состоянии, и на входах 19, 20, 21 нет сигналов. На выходе устройства образуется нулевое положение кода «2 из 3».

Входной импульс поступает на входы схем совпадения 9-14. При этом работает схема совпадения 9, так как на ее вход поступают рабочие сигналы с элементов памяти 7 и 8.

Схема 11 работает, так как на ее вход подается рабочий сигнал с элемента памяти 8. Схема 72 не работает, так как на ее вход подается инверсный сигнал с элемента памяти 8. Схема 13 не работает, так как на ее входы поступают инверсные сигналы с элемента памяти 5. Схема 14 не работает, так как на один из ее входов поступает инверсный сигнал с элемента памяти 8. От сигнала схемы совпадения 9 срабатывает элемент памяти 5, на его прямом входе появляется запрещающий сигнал, а на инверсном выходе- разрешающий сигнал. От сигнала схемы совпадения 11 срабатывает элемент памяти 6, на его прямом выходе появляется запрещающий сигнал, а на инверсном выходе - разрешающий сигнал.

После окончания первого импульса инвертор 17 оказывается в исходном положении, срабатывает схема совпадения. 15. От сигнала последней срабатывает элемент памяти 8. Элементы памяти 5 и 6 сохраняют первое кодовое положение, и на выходе устройства ничто не меняется.

При поступлении четвертого импульса срабатывают схемы совпадения 12 и 14. Сигнал схемы совпадения 12 переводит в исходное положение элемент памяти, а сигнал схемы совпадения 14 переводит в то же состояние элемент памяти 7. На выходе устройства появляется код нулевого положения (000).

По окончании четвертого импульса срабатывает схема совпадения 16. Ее сигнал переводит в исходное положение элемент памяти 8. Со следующего импульса работа устройства повторяется.

Следует отметить, что для других кодов устройства будут отличаться от рассмотренных, и даже для одного и того же кода может быть несколько вариантов устройств. Единственный характерный признак всех схем - наличие дополнительного элемента памяти, фиксирующего паузу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоточечной сигнализации | 1990 |

|

SU1795496A1 |

| МОДУЛИ СТРУЙНОЙ ПНЕВМО- и ГИДРОАВТОМАТИКИ | 1967 |

|

SU195721A1 |

| Устройство для автоматического вызова абонентов | 1986 |

|

SU1363527A1 |

| Устройство автоматического управления удалением осадка из отстойника | 1981 |

|

SU1172577A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| ПНЕВМАТИЧЕСКОЕ УСТРОЙСТВО СЧИТЫВАНИЯ ИНФОРМАЦИИ | 1971 |

|

SU419926A1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Устройство для программного управления технологическим оборудованием | 1988 |

|

SU1638707A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛОВ МАГНИТОТЕРАПЕВТИЧЕСКОГО ВОЗДЕЙСТВИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2205043C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Счетное устройство с потенциальным запуском, содержащее элементы памяти, вентили и схему «НЕ», отличающееся тем, что, с целью сокращения количества оборудования, оно содержит дополнительный элемент памяти, фиксирующий паузы, входы которого через вентили и схему «НЕ» соединены со входной шиной, а управляющие входы вентилей и выходы дополнительного элемента памяти подключены соответственно к выходам основных элементов памяти счетного устройства.

Авторы

Даты

1969-03-03—Публикация

1966-08-19—Подача