элемента ИЛИ соединены соответственно с входом кода операции процессора, выходом регистра сдвига, четвертыми выходами устройств местного управления и вторыми входа эл1ементов И первой группы, синхровход и иформационные входы регистра сдвига подключены соответственно к выходу генератора тактовых импульсов и вы ходам второго дешифратора, выходы элементов И второй группы и первого выходного регистра соединены с входом управления .записью сдвигателя, а выходы элементов И третьей группы и второго выходного регистра подключены к входам пуска устройств местного управления, при этом управляюпщй вход, первый и второй информационные входы и выход калсдого i-ro блока памяти соединены соответственно с пятым выходом 1-го устройства местного отправления, i-ым иформационным выходом второй группы сдвигателя, выходом i-ro блока сравнения и i-ым информационным входом второй группы блока выходных регистров, а второй информационный вход управляющий вход и выход результата каждого i-ro блока сравнения подключены соответственно к второму информационному выходу i-ro операционного блока, входу управления сравнением и шестому выходу i-ro устройства местного управления, причем устройство местного управления содержит два регистра, пять триггеров, десять элементов ИЛИ, два элемента И, элемент задержки, элемент И-ИЛЙ, семь групп элементов И, группу элементов ИЛИ, два счетчика, два дешифратора и блок селекторов, выход которого соединен с третьим выходом устройства, при этом синхровход, информационный вход, счетный вход и выход первого регистра подключены соответственно к вьЕХоду элемента И-ШТИ, выходу элемента задержки, входу пуска устройства и первым входам элементов И первой группы, вторые входы которых соединены с входом пуска устройства, установочный вход, вход сброса и выход первого триггера подключены соответственно к входу управления сдвигом устройства, выходу элемента задержки и первым входам элементов И второй группы, вторые входы которых соединены с

8

1

выходами элементов И первой группы, входы элементов ИЛИ группы йодключены к выходам элементов И первой груп пы, а выходы первого и второго элементов ИЛИ группы соединены со счетными входами соответственно второго и первого счетчиков, входы первого и второго элементов ИЛИ подключены соответственно к входу управления сравнением устройства и выходу второго счетчика, первый, второй, третий входы и выход третьего элемента ИЛИ соединены соответственно с выходом первого элемента ИЛИ, инверсным выходом второго элемента, ИЛИ, выходами элементов И первой группы и входом сброса второго триггера, установочный, вход которого подключен к выходам элементов И первой группы, установочный вход и вход сброса третьего триггера соединены с выходами соответственно третьего.элемента ИЖ группы и элемента задержки, установочные входы четвертого и пятого триггеров подключены к выходам элементов И первой группы, а входы сброса четвертого и пятого триггеров подключены к выходам соответственно первого и третьего элемен тов ИЛИ, первые входы четвертого и пятого элементов ИЛИ соединены с выходами элементов И первой группы, а вторые входы четвертого и пятого элементов ИЛИ подключены соответственно к выходу третьего элемента ИЛИ и прямому выходу второго элемента ИЛИ, первые входы элементов И третьей группы соединены с входом пуска устройства, а вторые входы первого, второго, третьего и четвертого элементов И третьей группы подключены соответственно к инверсному, выходу третьего триггера, прямому выходу четвертого триггера, инверсному и прямому выходам пятого триггера, первый и второй входы и выход шестого элемента ИЛИ соединены соответственно с выходами элементов И первой группы, выходом второго триггера и первым входом первого элемента И, второй вход которого подключен к входу управления вьщачей информации устройства и первому входу второго элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, а выходы первого и второго элементов И подключены соответственно к второму

и четвертому выходам устройства, первый, второй, третий, четвертый входы и выход элемента И-1ШИ соединены соответственно с выходом второго триггера, входом пуска устройства, выходаьт первого и третьего элементо И третьей группы и .четвертьм вькодом устройства первый и второй вхо.да. я выход седьмого элемента ШШ подключены соответственно к выхо дам элементов И первой группы, выХОДУ второго элемента И третьей группы и шестому выходу устройства, первый и второй входы и выход восьмого элемента ШШ соединены соот-г ветственно с выходом первого элемента И второй группы, выходом девятого элемента ИЛИ и первым выходом устройства, первый н второй входы и выход девятого элемента ШШ подключены соответственно к выходам второго и третьего элементов И второй группы и первому управляющему входу блока селекторрв, первый, второй,третий и четвертый входы десятого элемента ИЛИ соединены соответственно с выходом элемента Й-ШШ, выходами второго и четвертого элементов И третьей группы и выходом элемента задержки, вход которого подключен к выходу восьмого элемента ШШ, вход раэрешения и информационный вход второго регистра соединены соответственно G выходом первого регистра и входом пуска устройства, а выход второго регистра подключен к установочным входам первого и второго счетчиков и первому информационномувходу блока селекторов, выходы второ го и первого счетчиков соединены с первыми входами элементов И соответственно четвертой и пятой группы вторые входы которых подключены к выходам соответственно пятого триггера и первого элемента И второй группы, выходы элементов И четвертой и пятой группы соединены соответственно с входом первого дёш1фратора и пятым выходсм устройства а выход первого дешифратора подключен к второму информационному входу блока селектсфов, первые и вторые .входы и выходы элементов И шестой . группы соединены соответственно с выходом первого счетчика, выходом третьего элемента И шестой группы и входами второго дешифратора, выходы которого подключены к третьему выходу устройства, первые и вторые входы и выходы элементов И седьмой группы соединены соответственно с выходом второго счетчика, выходом седьмого элемента ШШ и шестым выходом устройства, а второй управляющий вход блока селекторов подключен к выходу второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1305658A1 |

| Процессор для реализации операций над элементами расплывчатых множеств | 1985 |

|

SU1256010A1 |

| Лингвистический терминал | 1981 |

|

SU964619A1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Вычислительное устройство | 1985 |

|

SU1283746A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

АССОЩ1АТИВНЫЙ ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР, содержащий сдвигатель, блок выходньк регистров, п операционкых .блоков, п устройств местного управления и устройство управл(ЕКИя, имеющее генератор тактовых импульсов, группу селекторов, два дешифратора и первую группу элементов И, при этом первые входы и выходы селекторов группы соединены соответственно с входом кода операции процессора и входами первого дешифратора, первые входы и выходы элементов И первой группы подключены соответственно к входу кода операции процессора и входам второго дешифратора, вход генератора тактовых импульсов соединен с входом кода операции процессора, а выход этого генератора подключен к входу управления записью сдвигателя и входам пуска устройств местного управления, причем вход управления сдвигом, вход управления выдачей информации, первый, .в.тот рой и третий выходы i-ro

Иэобцетение относится к вычислительной технике и быть использовано при построении вычислительных и управляю1цих систем на основе однородных вычислительных структур.

Цель изобретения - повышение быстродействия, а также расширение функциональных возможностей процессора, а именно получение возможности работы в режиме принятия решений в сложных системах управления на, основе алгоритмов, которые обёспечивают прием, хранение и переработку расплывчатой информации

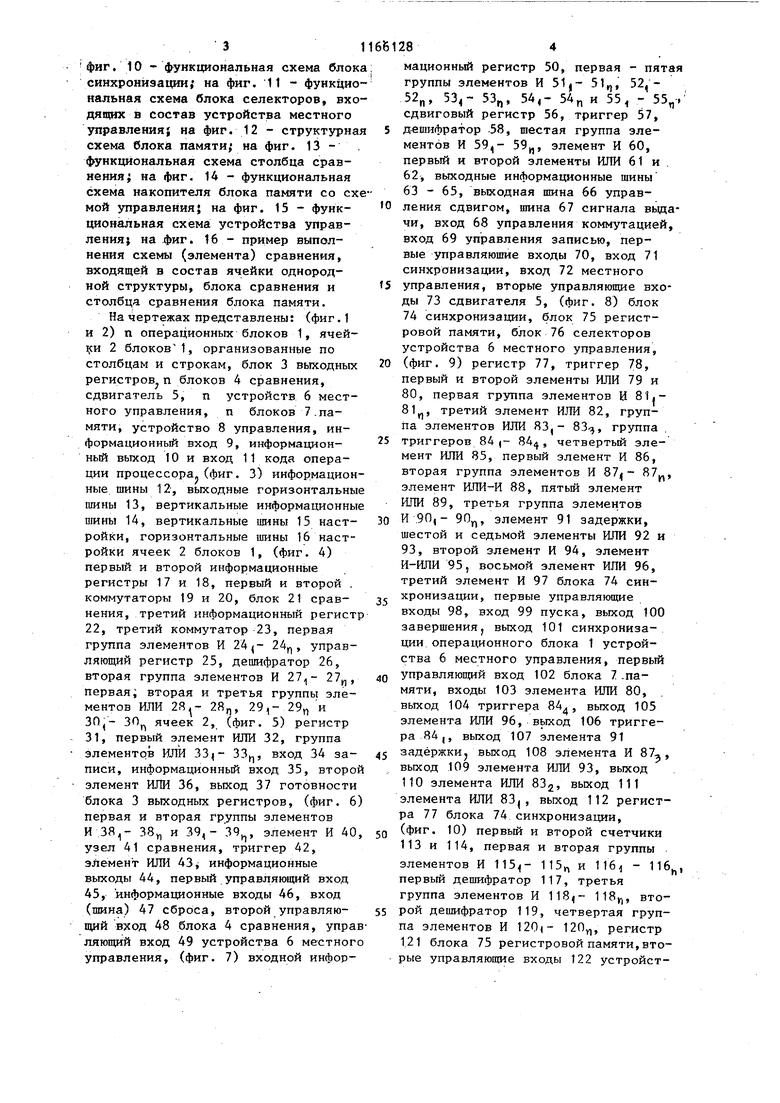

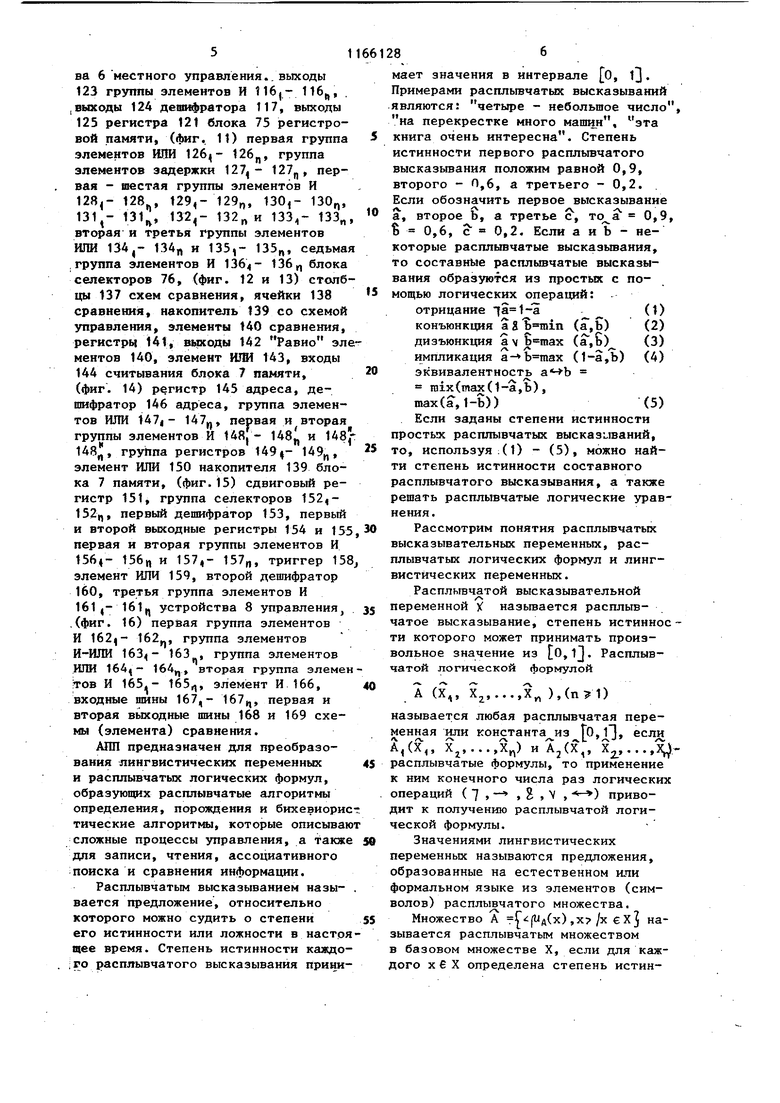

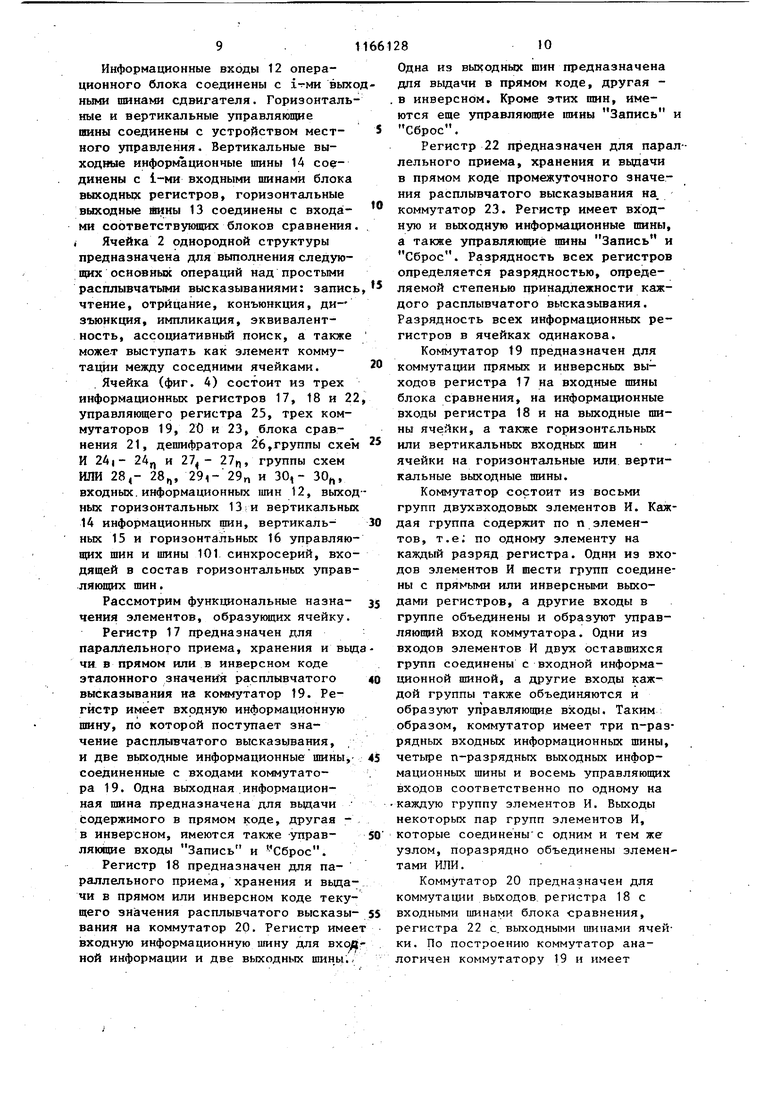

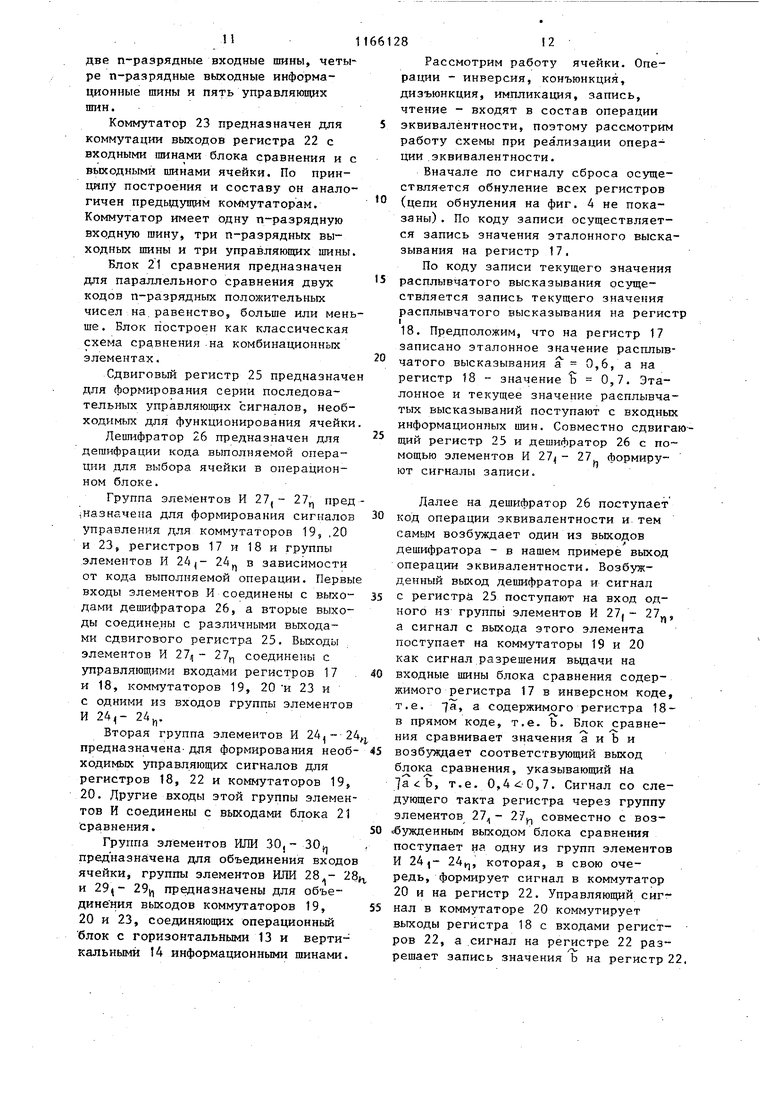

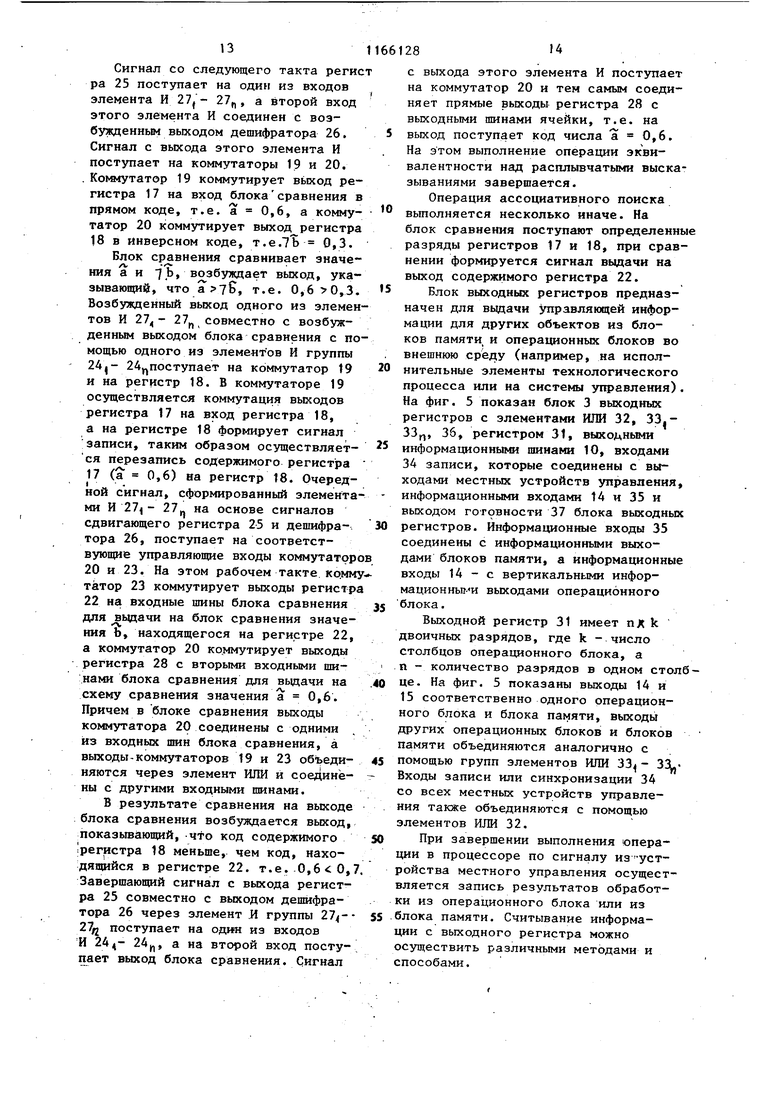

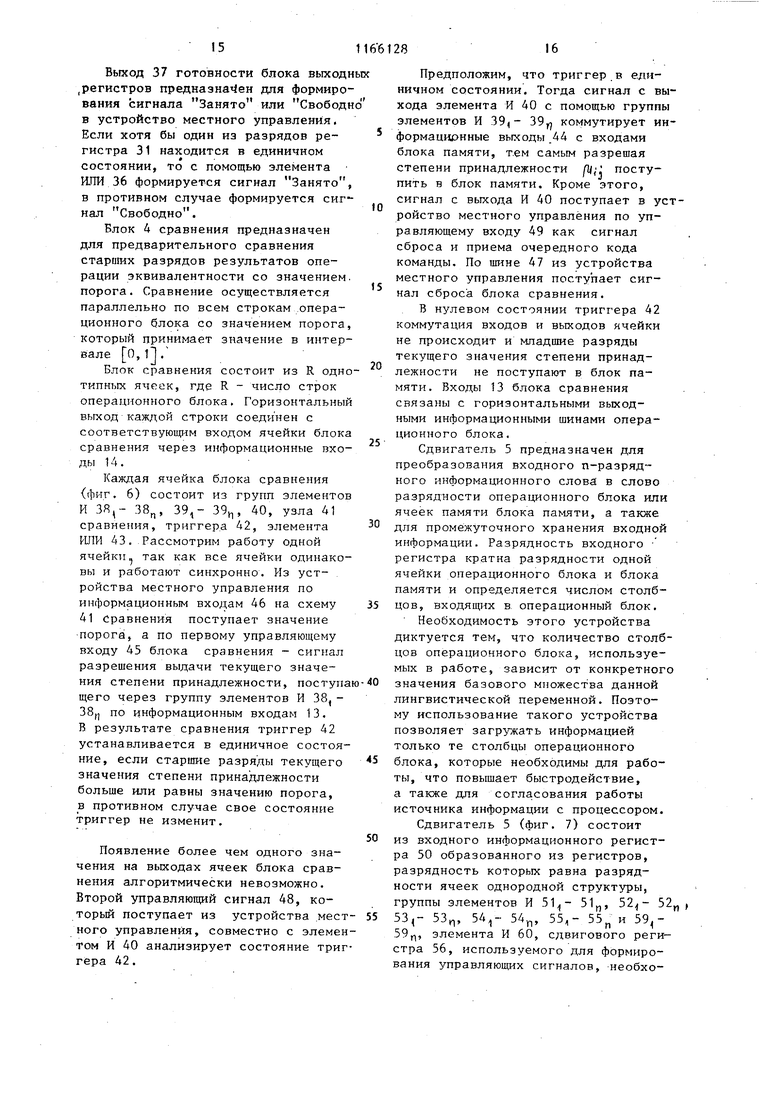

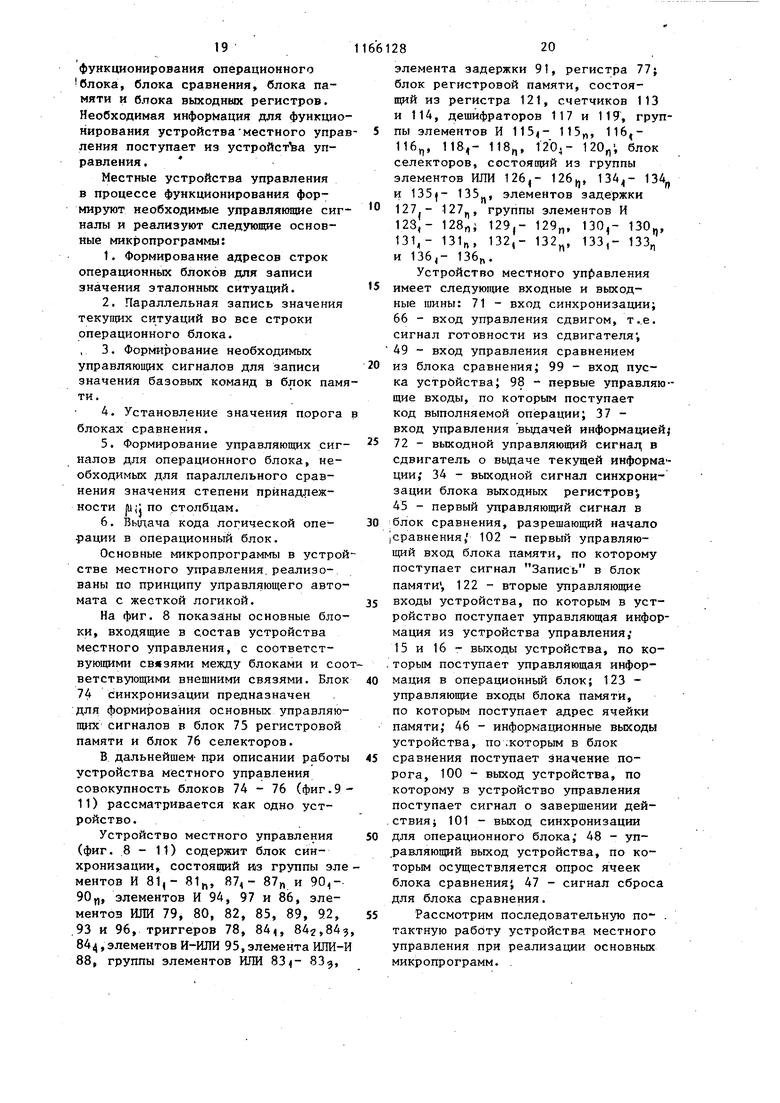

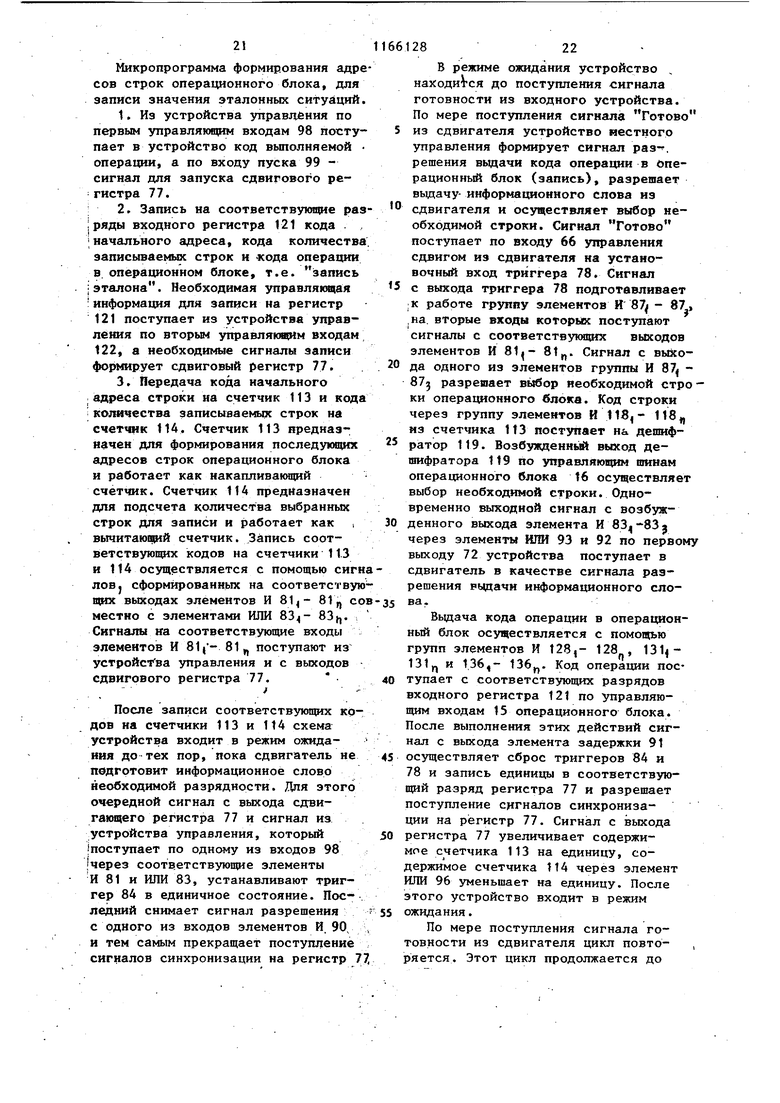

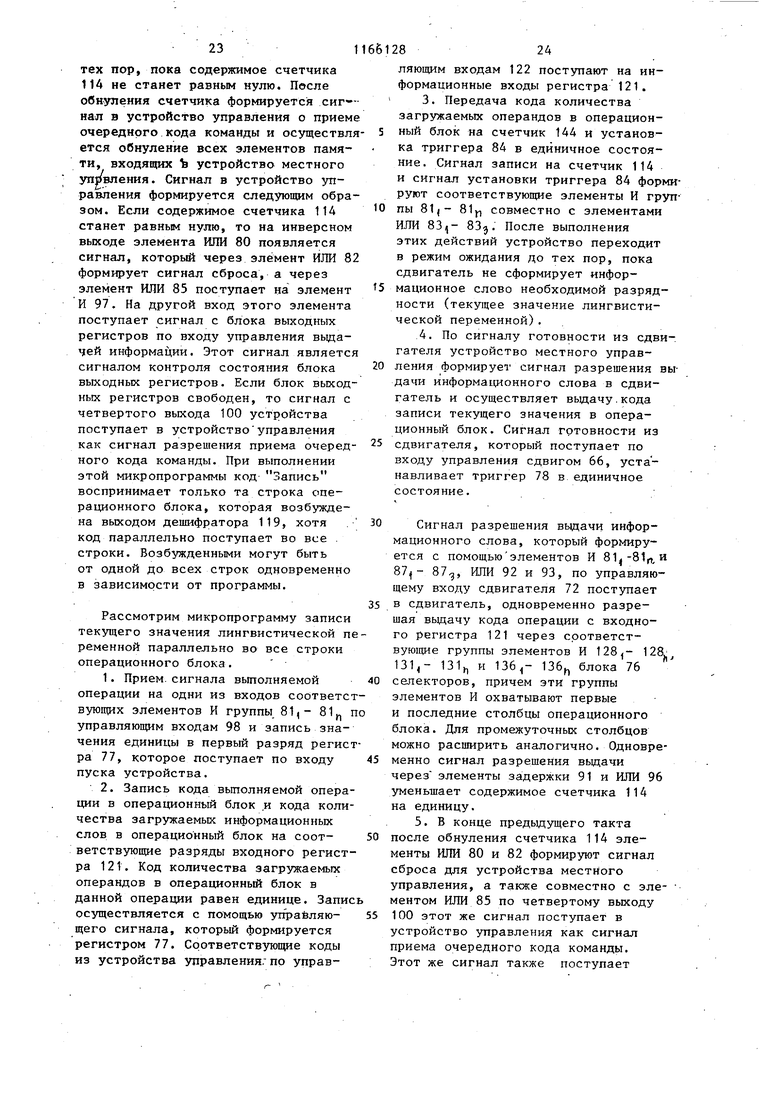

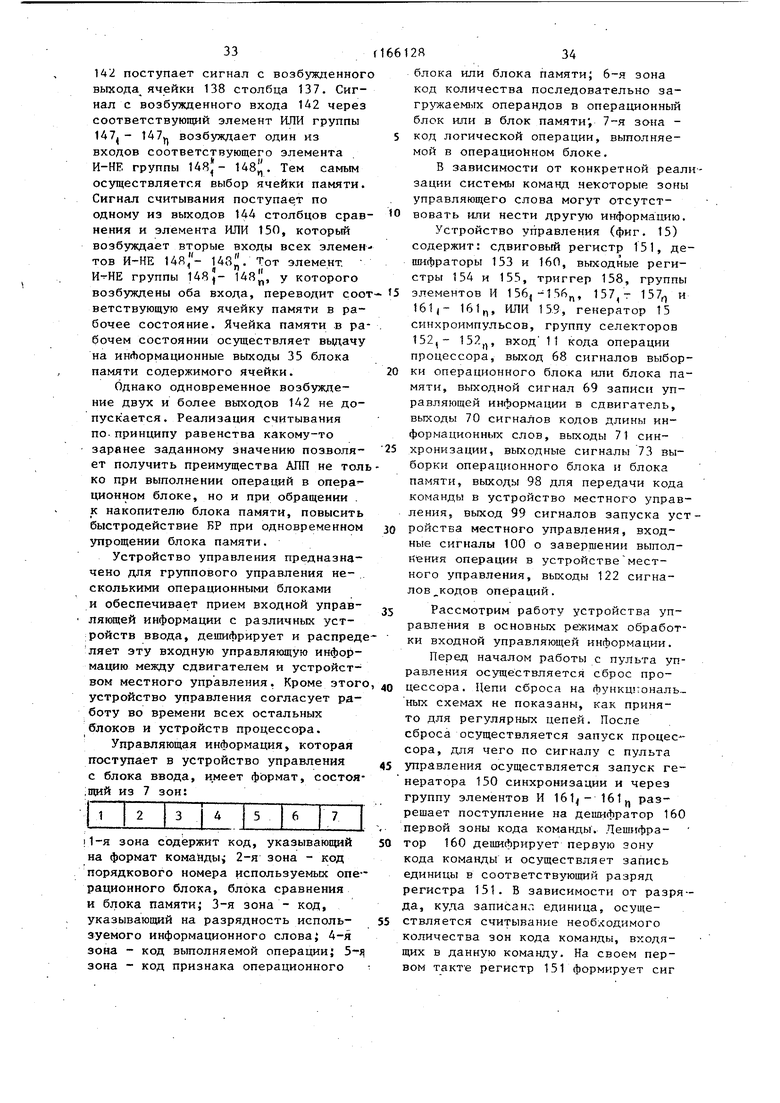

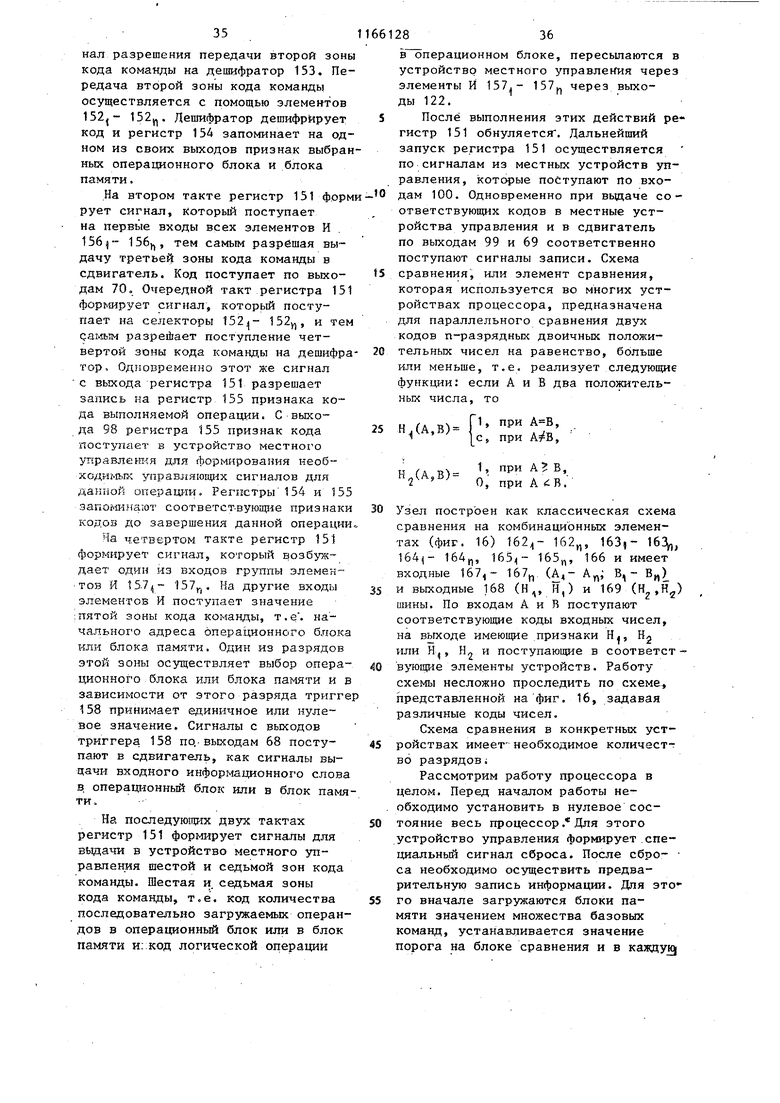

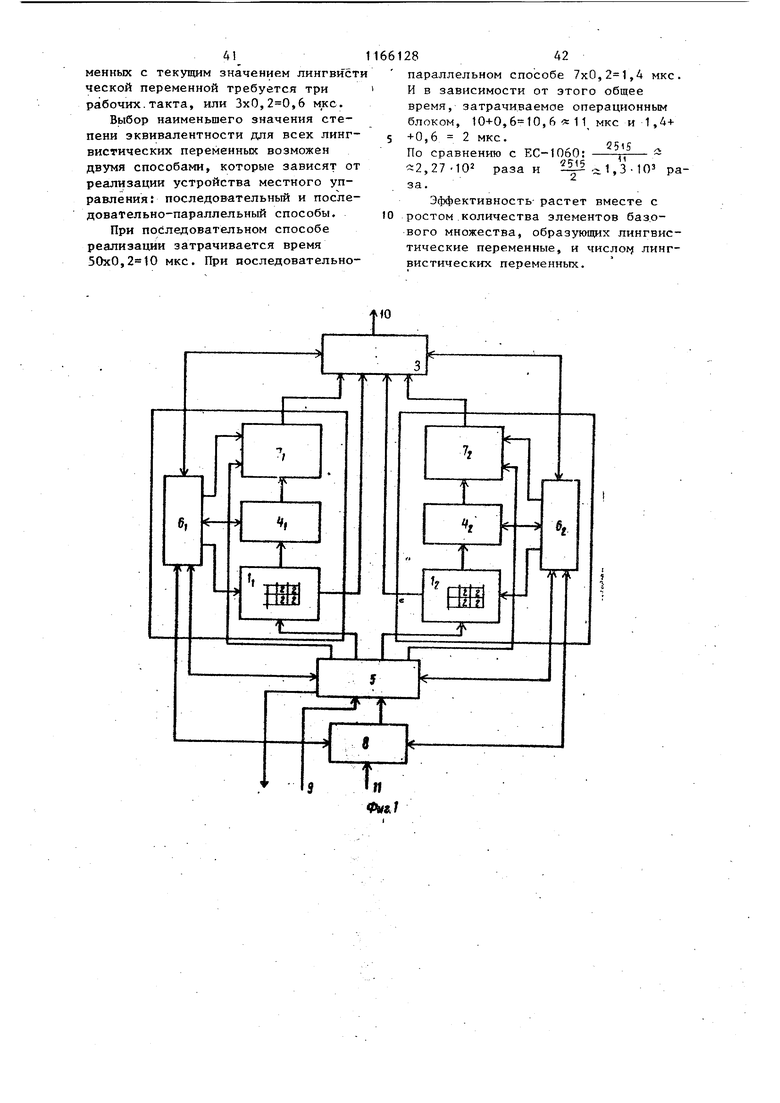

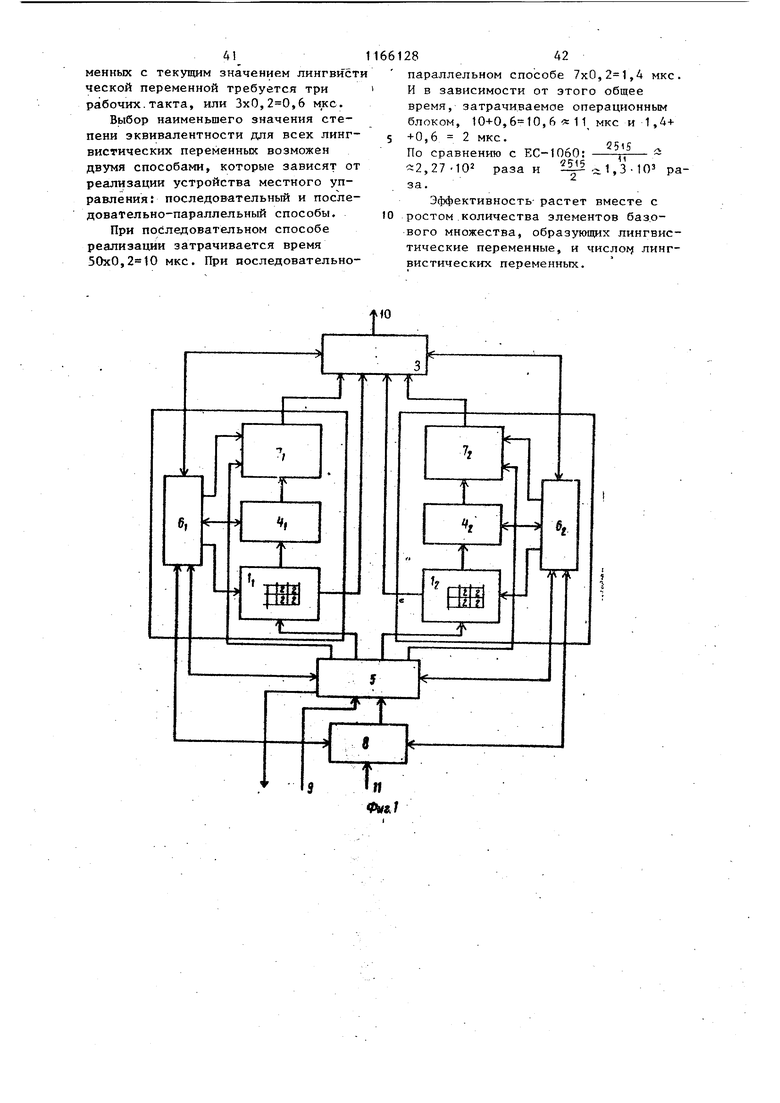

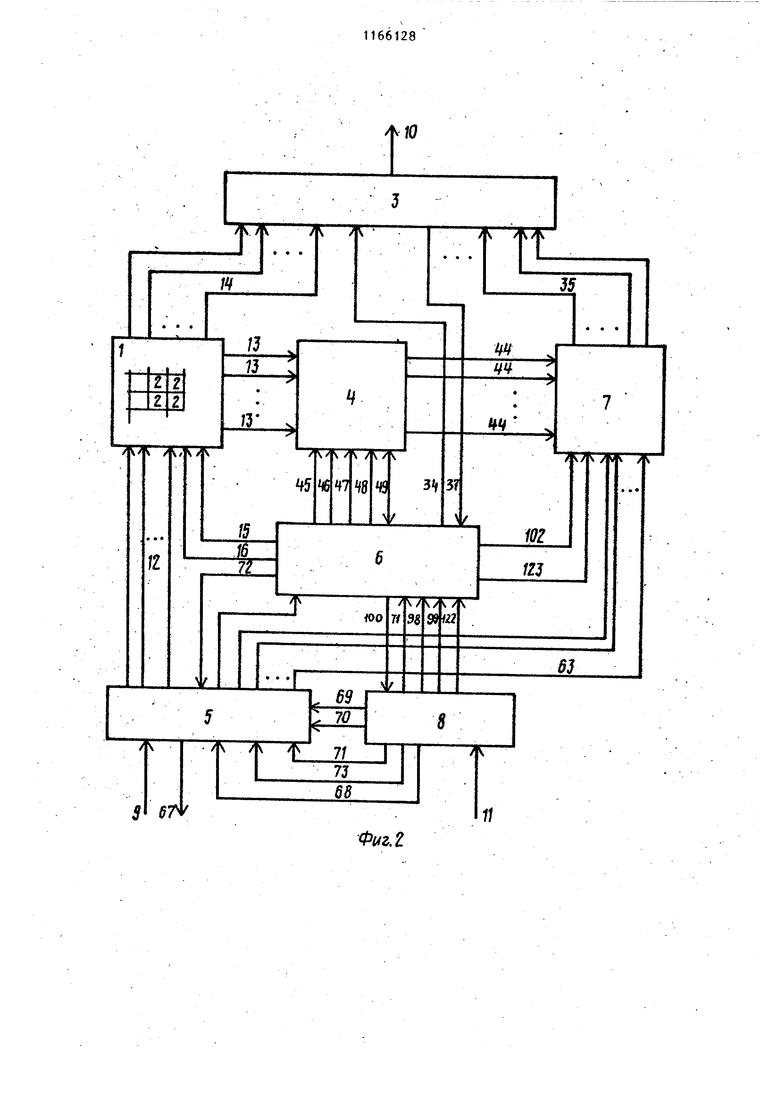

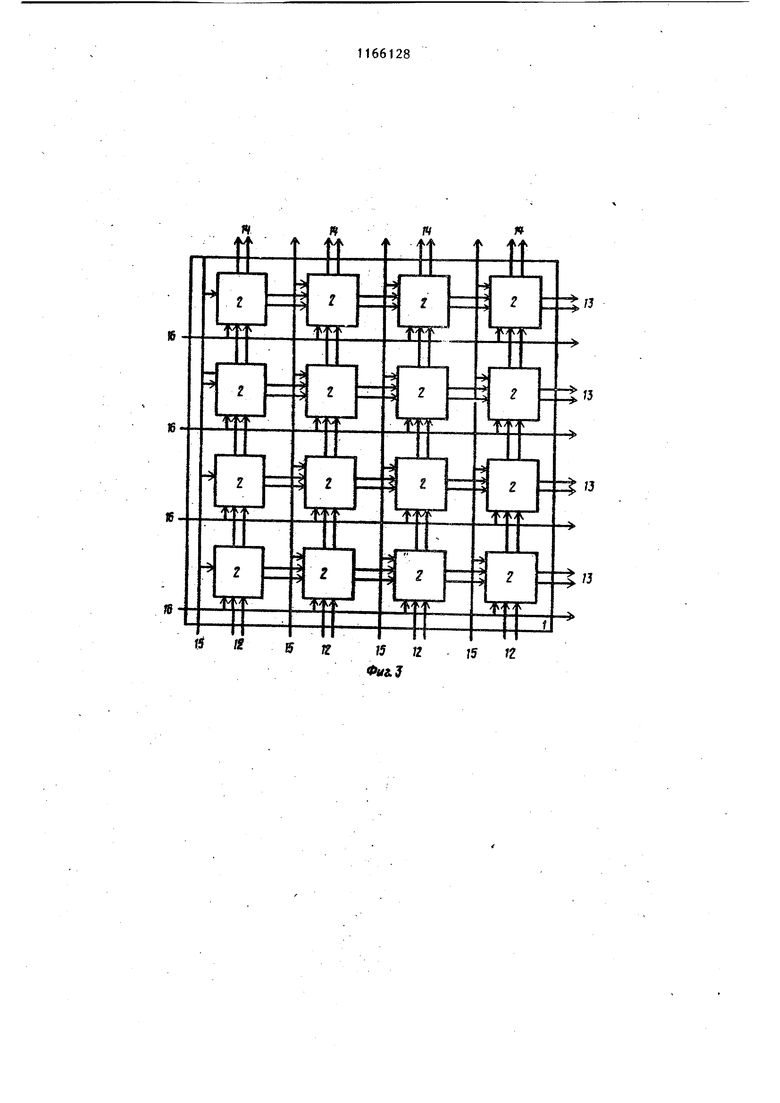

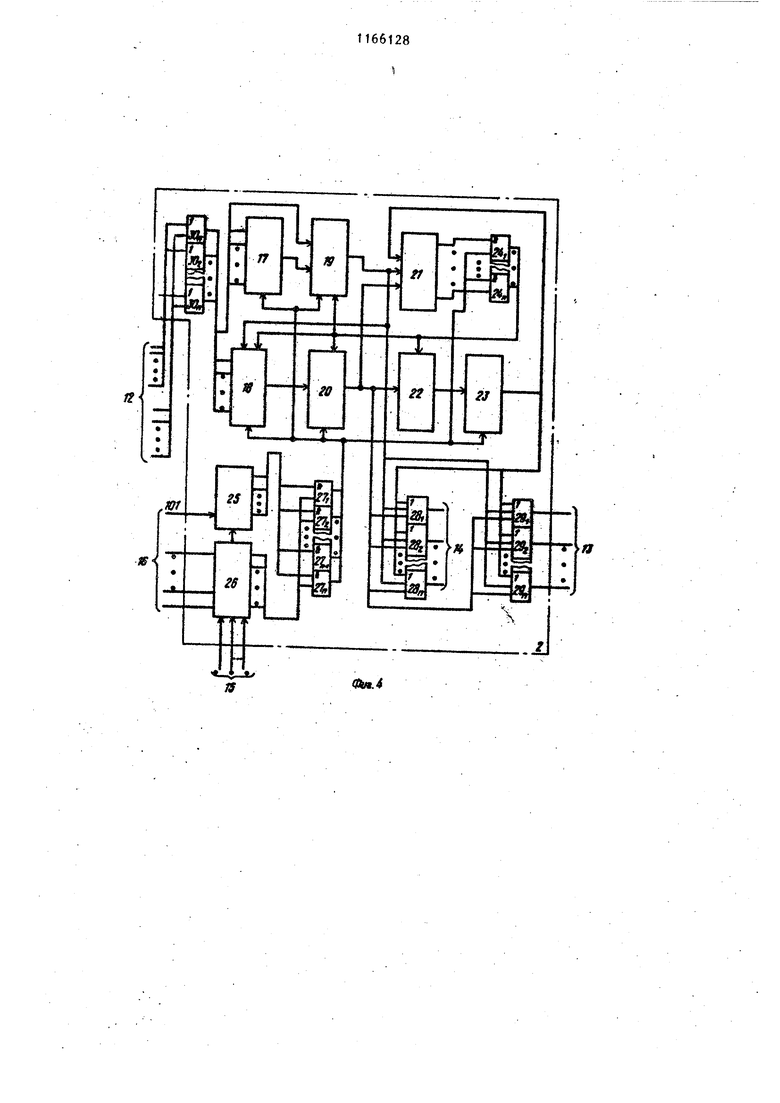

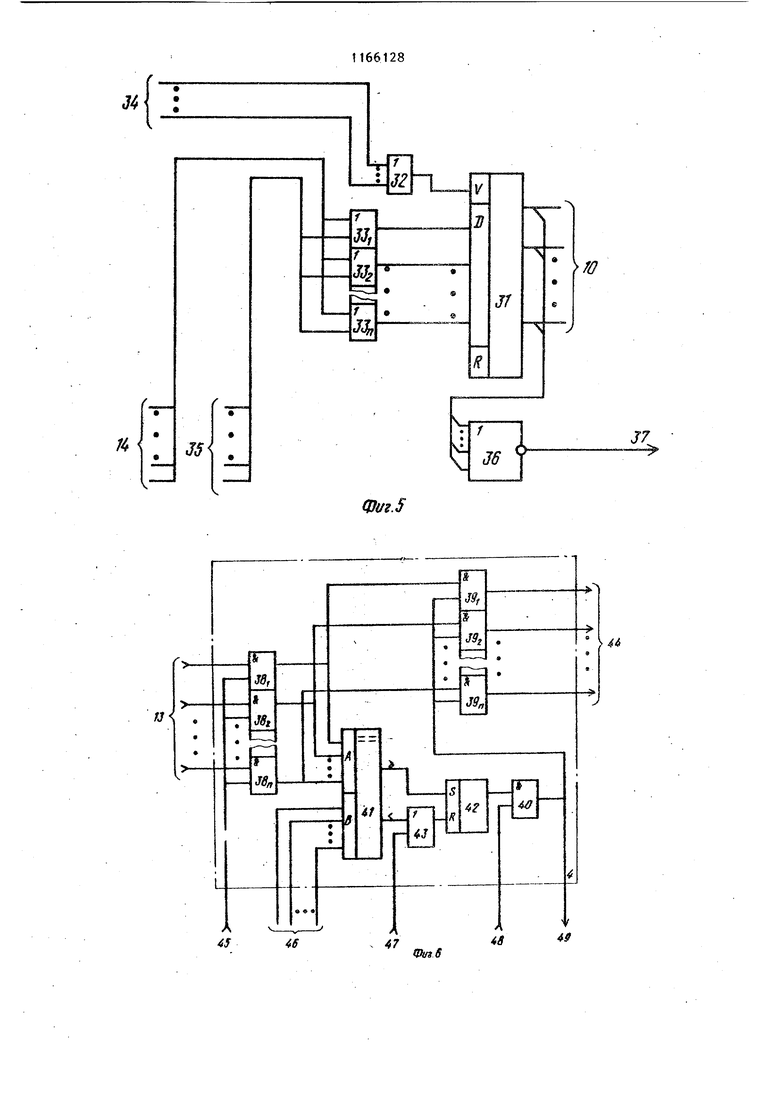

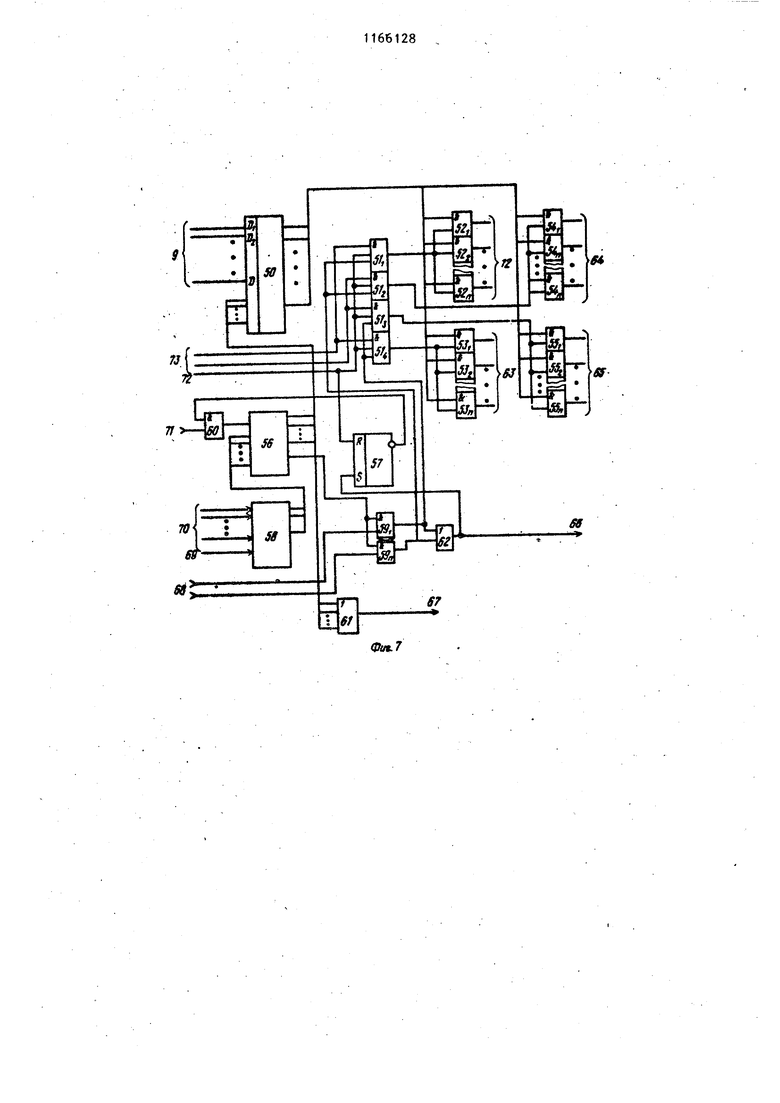

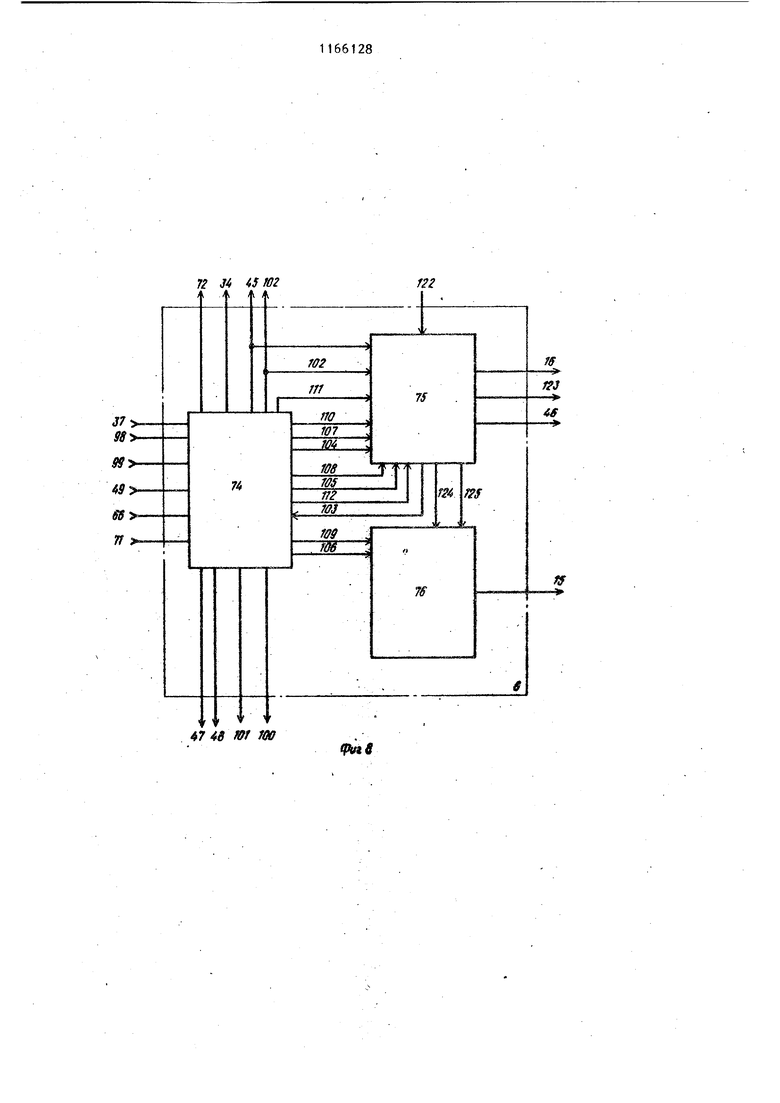

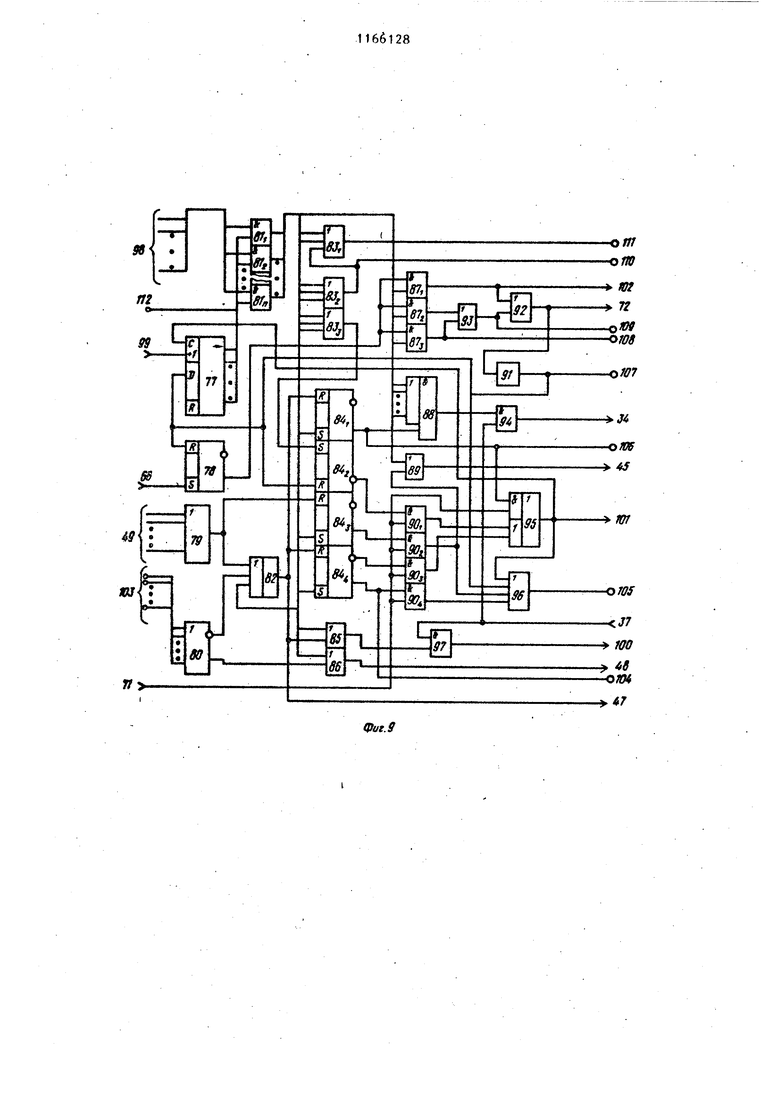

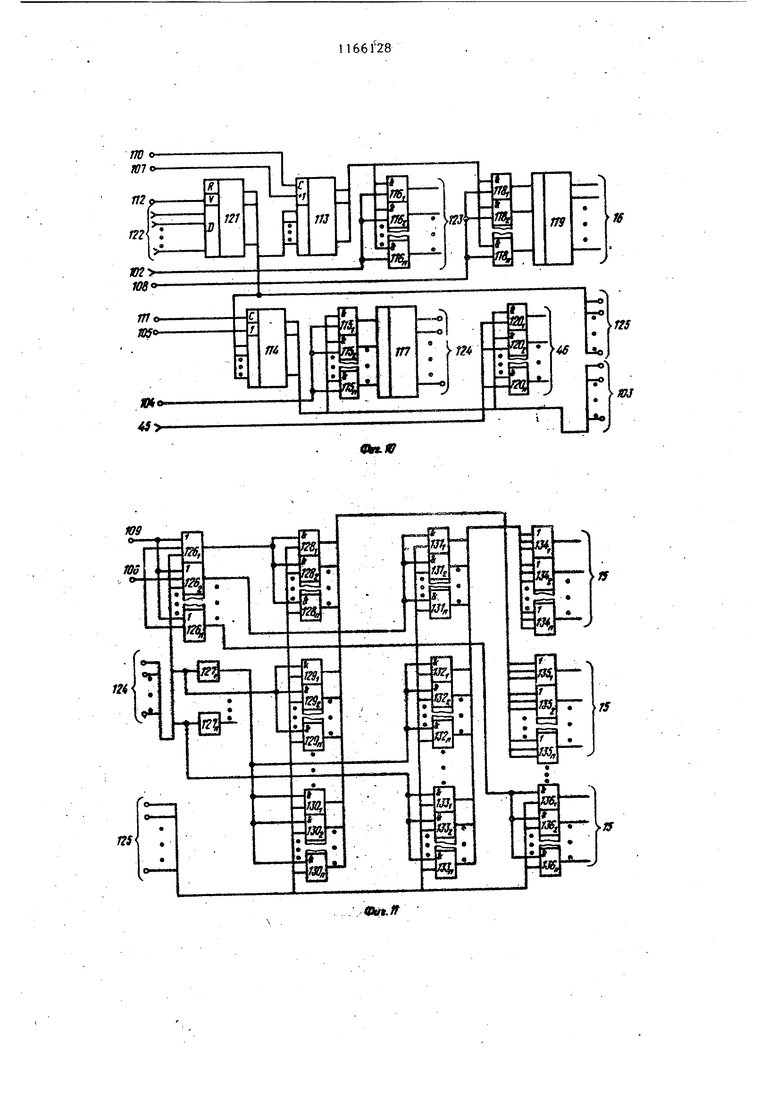

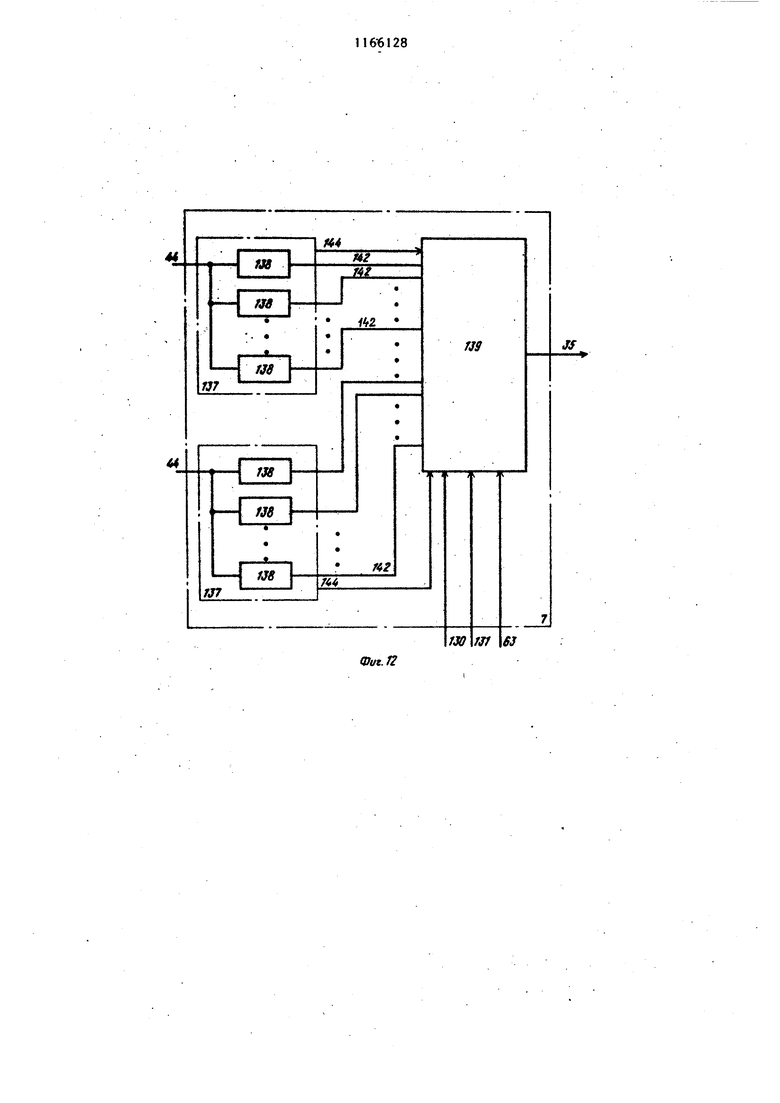

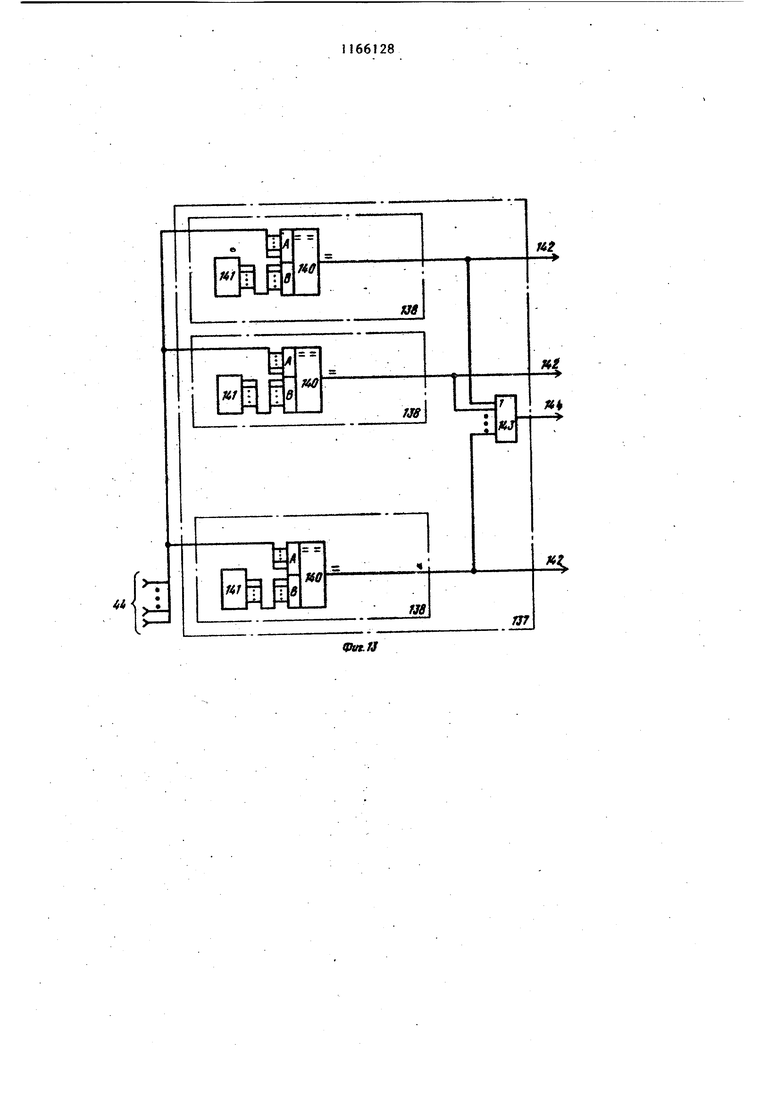

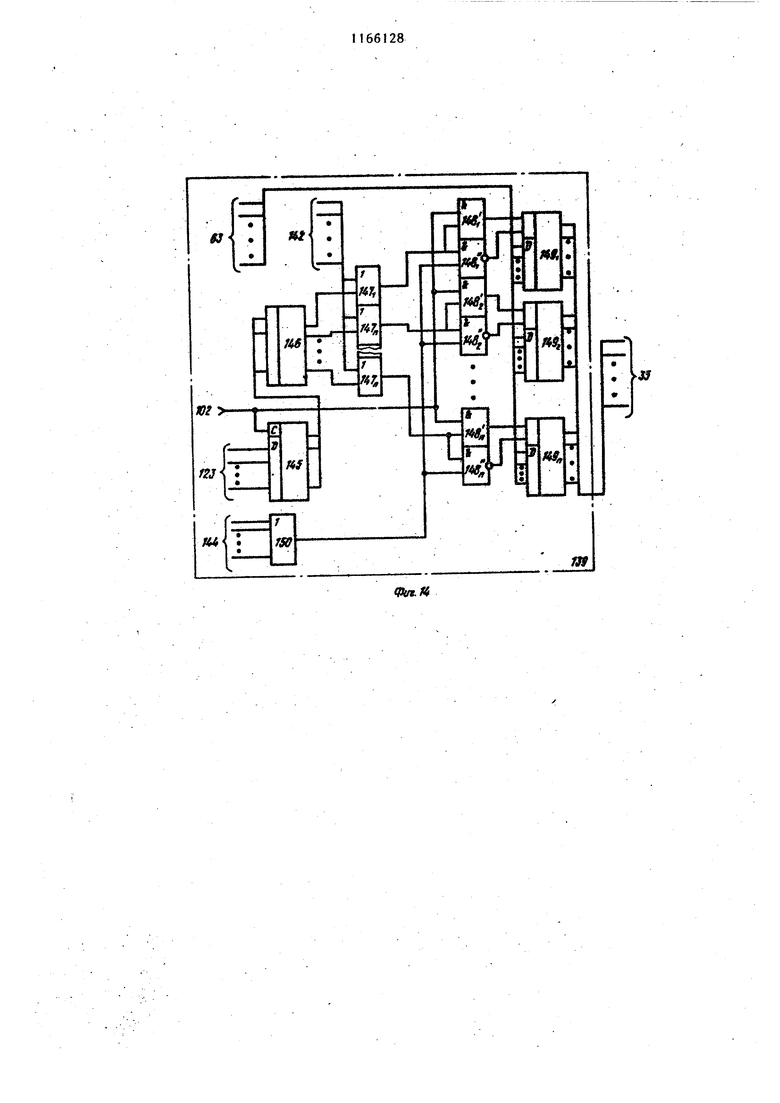

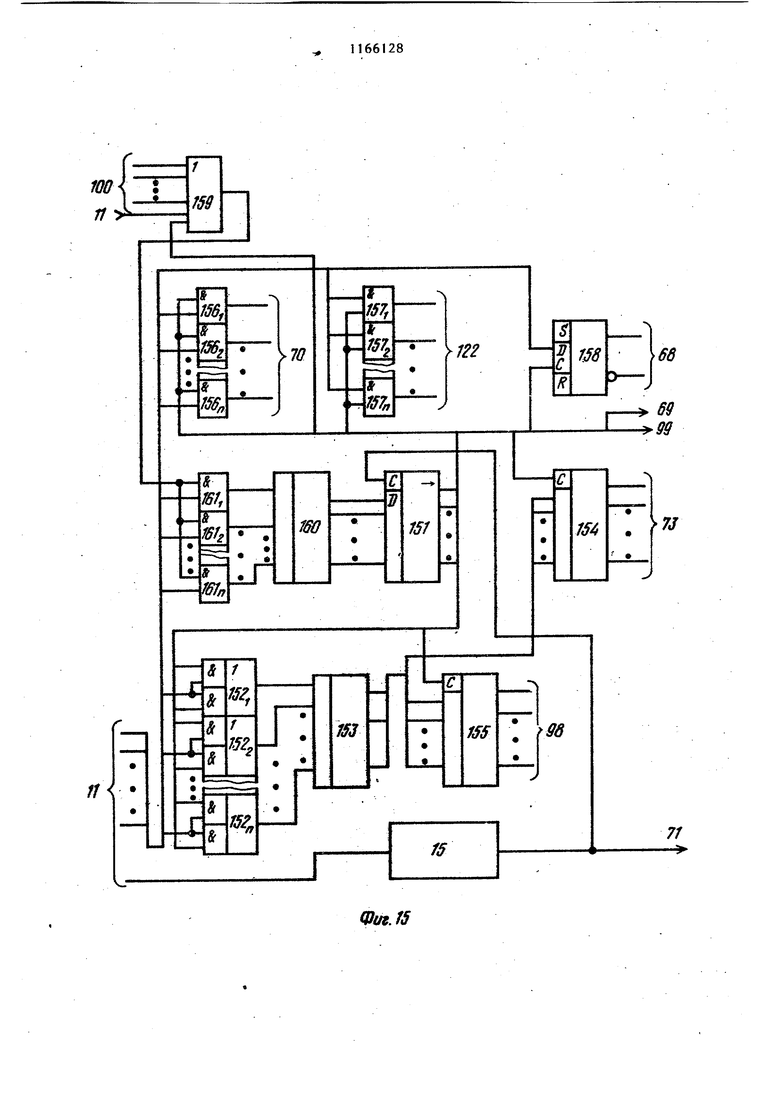

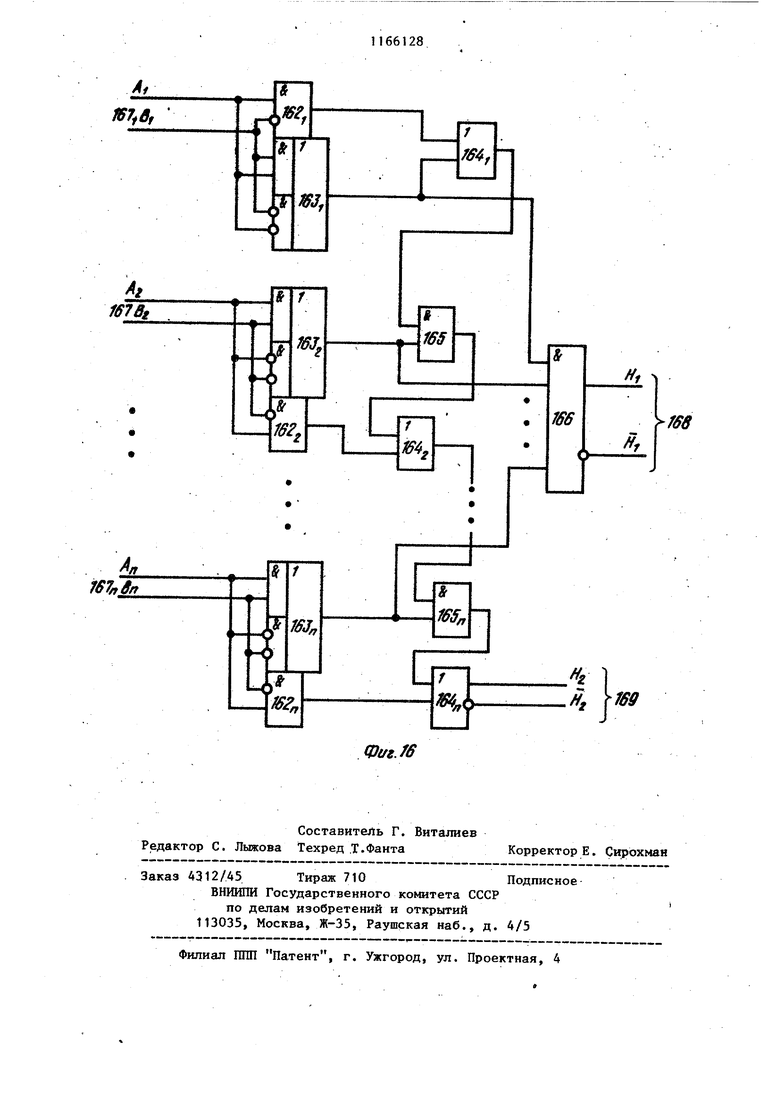

На фиг. 1 приведена структурная схема ассоциативного параллельного процессора (АЛЛ){ на фиг. 2 - пример

выполнения АПП, в состав которого входят по одному операционному блоку, блоку сравнения, блоку памяти н устройству местного управления; на фиг. 3 - структурная схема опе1 ацион ного блока, содержащего шестнадцать ячеек однородной структуры,- на фиг. 4 - функциональная схема ячейки однородной структуры; на фиг. 5 функциональная схема блока выходных регистров; на фиг. 6 - функциональна схема ячейки блока сравнения; на фиг. 7 - функциональная схема ячейки сдвигателя, на фиг. 8 - структура ная схема устройства местного управления; на фиг. 9 - функциональная схема блока регистровой памяти; на 3 фиг ,10 функциональная схема блок синхронизации; на фиг. 11 - функцио нальная схема блока селекторов, вхо дящих в состав устройства местного управления; на фиг. 12 - структурна схема блока памяти; на фиг. 13 функциональная схема столбца сравнения; на фиг. 14 - функциональная схема накопителя блока памяти со сх мой управления; на фиг. 15 - функциональная схема устройства управления } на фкг. 16 - пример выполнения схемы (элемента) сравнения, входящей в состав ячейки однородной структуры, блока сравнения и столбца сравнения блока памяти. На чертежах представлены: (фиг.1 и 2) п операционных блоков 1, ячей и 2 блоковМ, организованные по столбцам и строкам, блок 3 выходных регистров п блоков 4 сравнения, сдвигатель 5, п устройств 6 местного управления, п блоков 7.памяти, устройство 8 управления, информационный вход 9, информационный выход 10 и вход 11 кода операции процессора.(фиг. 3) информацион ные шины 12, выходные горизонтальны шкны 13, вертикальные информационны П1ИНЫ 14, вертикальные шины 15 настройки, горизонтальные 1шны 16 настройки ячеек 2 блоков 1, (фиг. 4) первый и второй информационные регистры 17 и 18, первый и второй . коммутаторы 19 и 20, блок 21 сравнения, третий информационный регист 22, третий коммутатор 23, первая группа элементов И 24, управляющий регистр 25, дешифратор 26, вторая группа элементов И 27„, перваяi вторая и третья группы элементов ИЛИ 28„, 29,- 29„и 30 ячеек 2, (фиг. 5) регистр 31, первый элемент ИЛИ 32, группа элементов ИЛИ 33, вход 34 записи, информационный вход 35, второ элемент ИЛИ 36, выход 37 готовности блока 3 выходных регистров, (фиг. 6 первая и вторая группы элементов И 38„ и 39,- 39, элемент И 40 узел 41 сравнения, триггер 42, элемент ИЛИ 43j информационные выходы 44, первый управляющий вход 45, информационные входы 46, вход (шина) 47 сброса, второй управляющий вход 48 блока 4 сравнения, упра ляющий вход 49 устройства 6 местног управления, (фиг. 7) входной инфор84мационный регистр 50, первая - пятая группы элементов И 51 j- 5Ц, 52,52„, 33,- 53„, 54,- 54„ и 55 - 55„, сдвиговый регистр 56, триггер 57, дешифратор .58, шестая группа элементов И 59, элемент И 60, первый и второй элементы ИЛИ 61 и . 62, выходные информационные шины 63 - 65, выходная шина 66 управления сдвигом, шина 67 сигнала вьщачи, вход 68 управления коммутацией, вход 69 управления записью, первые управляющие входы 70, вход 71 синхронизации, вход 72 местного управления, вторые управляющие входы 73 сдвигателя 5, (фиг. 8) блок 74 синхронизации, блок 75 регистровой памяти, блок 76 селекторов устройства 6 местного управления, (фиг. 9) регистр 77, триггер 78, первый и второй элементы ИЛИ 79 и 80, первая группа элементов И 81,81 , третий элемент ИЛИ 82, групПа элементов ИЛИ 83,- , группа триггеров 84 )- 84, четвертый элемент ИЛИ 85, первый элемент И 86, вторая группа элементов И 87, элемент ИЛИ-И 88, пятый элемент ИЛИ 89, третья группа элементов И .90, - 90j, элемент 91 задержки, шестой и седьмой элементы ИЛИ 92 и 93, второй элемент И 94, элемент И-ИЛИ 95, восьмой элемент ИЛИ 96, третий элемент И 97 блока 74 синхронизации, первые управляющие входы 98, вход 99 пуска, выход 100 завершения выход 101 синхронизации операционного блока 1 устройства 6 местного управления, первый управляющий вход 102 блока 7.памяти, входы 103 элемента ИЛИ 80, выход 104 триггера 84, выход 105 элемента ИЛИ 96, вькод 106 триггера 84,, выход 107 элемента 91 задержкиJ выход 108 элемента И 87,, выход 109 элемента ИЛИ 93, выход 110 элемента ИЖ 832, выход 111 элемента ИЛИ 83|, выход 112 регистра 77 блока 74 синхронизации, (фиг. 10) первый и второй счетчики 113 и 114, первая и вторая группы элементов И 115, и 116 - 116, первый дешифратор 117, третья группа элементов И ,, второй дешифратор 119, четвертая группа элементов И 120(- 120, регистр 1.21 блока 75 регистровой памяти, вторые управляющие входы 122 устройства 6 местного управления.. выходы 123 группы элементов И 116j- 116„, ,выходы 124 дешифратора 117, выходы 125 регистра 121 блока 75 регистровой памяти, (фиг. 11) первая группа элементов 126, группа элементов задержки 127, первая - шестая группы элементов И 128,- 128 , 129,- 129„. 130,- 130, , 132„и 133„, вторая и третья грзтпы элементов ИЛИ 134,- 134„ и 135,- 135„, седьмая группа элементов И 136 блока селекторов 76, (фиг. 12 и 13) столбцы 137 схем сравнения, ячейки 138 сравнения, накопитель 139 со схемой управления, элементы 140 сравнения, регистры 141, выходы 142 Равно элементов 140, элемент И1Ш 143, входы 144 считывания блока 7 памяти, (фиг. 14) регистр 145 адреса, дешифратор 146 адреса, группа элементов ИЛИ 147i- 147jj, первая и вторая группы элементов И 148,- 148 и 148, 148, группа регистров 149„, элемент ИЛИ 150 накопителя 139 блока 7 памяти, (фиг.15) сдвиговый регистр 151, группа селекторов 152,152,, первый дешифратор 153, первый и второй выходные регистры 154 и 155 первая и вторая группы элементов И 156„ и 157,- 157„, триггер 158 элемент ИЛИ 159, второй дешифратор 160, третья группа элементов И 161 ,- 16Ц устройства 8 управления, .(фиг. 16) первая группа элементов И 162,- 162, группа элементов Й-ИЛИ 163,- 163 , группа элементов .ИЛИ 164,- 164,, вторая группа элемен|тов И 165,- 165, элемент И 166, входные шины 167,- 167, первая и вторая выходные шины 168 и 169 схемы (элемента) сравнения.

АШ1 предназначен для преобразования лингвистических переменных и расплывчатых логических формул, образующих расплывчатые алгоритмы определения, порождения и бихевиорис тические алгоритмы, которые описываю сложные процессы управления, а также для записи, чтения, ассоциативного поиска и сравнения информации.

Расплывчатым высказыванием называется предложение, относительно которого можно судить о степени его истинности или ложности в настоящее время. Степень истинности каждо- :го расплывчатого высказывания принимает значения в интервале о, l3. Примерами распльшчатых высказываний являются: четыре - небольшое число на перекрестке много машин, эта книга очень интересна. Степень истинности первого расплывчатого высказывания положим равной 0,9, второго - П,6, а третьего - 0,2. Если обозначить первое высказывание а, второе S, а третье с, 0,9 S - 0,6, с 0,2. Если а и b - некоторые расплывчатые высказьтания, то составные расплывчатые высказывания образуются из простых с помощью логических операций:

отрицание (О конъюнкция (a,b) (2) дизъюнкция av (a,b) (3) импликация (1-a,b) (4) эквивалентность raix(inax(1-a,b), max(a,1-b))(5)

Если заданы степени истинности простьх расплывчатых высказываний, то, используя :(1) - (5), можно найти степень истинности составного расплывчатого высказывания, а также решать расплывчатые логические уравнения .

Рассмотрим понятия расплывчатых высказывательных переменных, расплывчатых логических формул и лингвистических переменных.

Расплывчатой высказывательной

/N

переменной X назьгоается расплывчатое высказывание, степень истинное ти которого может принимать произвольное значение из О,1J. Расплывчатой логической формулой

А (X,, Х.,,...,Х„ ),()

называется любая расплывчатая переменная или константа из Го,11, если

«ч ./л. / л. ,L /X.

А,(Х,, Х,...,Х) и А2(Х,, Х,...,} расплывчатые формулы, то применение к ним конечного числа раз логических операций ( 7 - . X , V , -) приводит к получению расплывчатой логической формулы.

Значениями лингвистических переменных называются предложения, образованные на естественном или формальном языке из элементов (символов) расплывчатого множества.

Множество А :(11д(х) , ех называется расплывчатым множеством в базовом множестве X, если для каждого X е X определена степень истинности расплывчатого высказывания , обозначаемая (ЦдСх).

Степень.равенства л/(,5) двух расплывчатых множеств определяется выражением 5

/Zl(A,B) g (fllA(x)(x)) (6 где - операция конъюнкции, определяемая по (2), которая берется по всем х Х; 10 операция эквивалентности, определяемая по (5), которая берется для соответствующих пар элементов ; расплывчатых множеств А и В, 5

, 1/1 ,0,й/2 , с , 0.6/4 ,: 0,3/5 ,.:0,1 |б можно рассматривать как значение . мало, значение достаточно или

,4/47,сО,9/5,/6,0.8/,0,2/8 ,,

а значение много имеет вид

,: 0,6/7 ,с 0,7/е, O.q/9:,

лингвистической переменной нату- гоперацию (1), найдем значение не

ральные числа до 10, Используя .мало. Получим

- Г

.cQ,,,4/4,Q,7|57 i0.9/6,r1/75,;i/8, {79,«/10 .

Значение не много и не мало можно определить как

,,/3,;0,4/4,сО,7/5,0,7/6 ,4/7 ,0,3/8. 0,1/9 |. Определяя по (6) степень равенства, получим 1 (.С,) 0,6, т.е. А % А2, что хорошо согласуется .с интуитивным пониманием значений не МНОГО и не мало и достаточно. Рассмотрим состав устройств, блоков и узлов, входящих в состав процессора и,их работу. Операционный- блок 1 предназначен для выполнения след тощих основных операций над значениями лингвистичес ких переменных: стирание, запись чтение, конъюнкция, дизъюнкция, импликация, эквивалентность, ассоциативньп1 поиск, а также на основе этих операций программная реализация алгоритмов композиции, определения порождения и бихевиористических алго ритмов . Операционный блок состоит из ячее 2 однородной структуры. Каждая ячейка соединена с соседними ячейками

Предположим, что множество X образовано из элементов, каждый из которых является натуральным числом от 1 до 10, т.е.

X fl, 2, 3, 4, 5, 6, 7, 8, 9, Ю,

Определенным образом выбирая расплыв1,

чатое подмножество А множествл X, можно образовывать понятия, которые являются значениями лингвистической переменной. Например, расплывчатое множество

А 1 А, П 1 А,

т.е. средне принимает расплывчатое множество с помощью информационных шин. Имеются входные.информационные шины 12, выходные горизонтальные 13 и вертикальные 14 информационные шины. Настройка ячейки на выполнение той или другой операции оотцествляется с помощью вертикальных шин 15 настройки (управляющих). Выбор строки, столбца или ячейки операционного блока осуществляется с помощью вертикальных 15 и горизонтальных 16 шин настройки. На фиг. 3 показан операционный блок, состоягдай из четырех строк и четырех столбцов с соответствующими связями. Размерность операционного блока определяется кругом решаемых задач, исходя из наиболее часто используемых значений базовьк множеств, образующих данные лингвистические переменные и множества эталонных ситуаций. Информационные входы 12 операционного блока соединены с i-ми вых ными шинами сдвигателя. Горизонталь ные и вертикальные управляющие шины соединены с устройством местного зтравления. Вертикальные выходные информационные шины 14 соединены с 1-ми входными шинами блока выходных регистров, горизонтальные выходные шины 13 соединены с входами соответствующих блоков сравнения i Ячейка 2 однородной структуры предназначена для выполнения следуюащх основных операций над простыми расплывчатыми высказываниями: запис чтение, отрицание, конъюнкция, дизъюнкция, импликация, эквивалентность, ассоциативный поиск, а также может выступать как элемент коммутации между соседними ячейками. Ячейка (фиг, 4) состоит из трех информационных регистров 17, 18 и 2 управлянэдего регистра 25, трех коммутаторов 19, 20 и 23, блока сравнения 21, дешифратора 26,группы схе И 24,- 24п и 27f), группы схем ИЛИ 28,- 28, 29i- 29п и 30,- 30,, входных.информационных шин 12, выхо ных горизонтальных вертикальны 14 информационных шин, вертикальных 15 и горизонтальных 16 управляю щих шин и шины 101 синхросерий, вхо дящей в состав горизонтальных управ ляющих шин. Рассмотрим функциональные назначения элементов, образующих ячейку. Регистр 17 предназначен для параллельного приема, хранения и вьщ чи. в прямом или в инверсном коде эталонного значени я расплывчатого высказывания на коммутатор 19. Регистр имеет входную информационную шину, по которой поступает значение распльгечатого высказывания, и две выходные информационные шины, соединенные с входами коммутатора 19. Одна выходная информационная шина предназначена для вьццачи содержимого в прямом коде, другая в инверсном, имеются также управляющие входы Запись и Сброс. Регистр 18 предназначен для параллельного приема, хранения и вьща чи в прямом или инверсном коде теку щего значения расплывчатого высказы вания на коммутатор 20. Регистр име входную информационную шину для вход ной информации и две выходных шины. Одна из выходных шин предназначена дпя выдачи в прямом коде, другая в инверсном. Кроме этих шин, имеются еще управляющие шины Запись и Сброс. Регистр 22 предназначен для параллельного приема, хранения и выдачи в прямом коде промежуточного значения расплывчатого высказывания на. коммутатор 23. Регистр имеет входную и выходную информационные шины, а также управляющие шины Запись и Сброс. Разрядность всех регистров определяется разрядностью, определяемой степенью принадлежности каждого расплывчатого высказьшания. Разрядность всех информационных регистров в ячейках одинакова. Коммутатор 19 предназначен для коммутации прямых и инверсных выходов регистра 17 на входные шины блока сравнения, на информационные входы регистра 18 и на выходные шины ячейки, а также горизонтальных или вертикальных входных шин ячейки на горизонтальные или вертикальные выходные шины. Коммутатор состоит из восьми групп двухвходовых элементов И. Каждая группа содержит по п элементов, т.е; по одному элементу на каждый разряд регистра. Одни из входов элементов И шести групп соединены с прямыми или инверсными выходами регистров, а другие входы в группе объединены и образуют управляющий вход коммутатора. Одни из входов элементов И двух оставшихся групп соединены с входной информационной шиной, а другие входы каждой группы также объединяются и образуют управляющие входы. Таким образом, коммутатор имеет три п-разрядных входных информационных шины, четьфе п-разрядных выходных информационных шины и восемь управляющих входов соответственно по одному на каждую группу элементов И. Выходы некоторьгх пар групп элементов И, которые соединеныс одним и тем же узлом, поразрядно объединены элементами ИЛИ. Коммутатор 20 предназначен для коммутации выходов, регистра 18 с входными шинами блока сравнения, регистра 22 с. выходными шипами ячейки. По построению коммутатор аналогичен коммутатору 19 и имеет две п-разрядные входные шины, четыре п-разрядные выходные информационные шины и пять управляющих итн. KoMNfyTHTop 23 предназначен для коммутации выходов регистра 22 с входными шинами блока сравнения и с выходными шинами ячейки. По принципу построения и составу он аналогичен предьщущим коммутаторам. Коммутатор имеет одну п-разрядную входную шину, три п-разрядных выходных шины и три управляющих шины Блок 21 сравнения предназначен для парсшлельного сравнения двух кодов п-разрядньгх положительных чисел на.равенство, больше или мен ше. Блок построен как классическая схема сравнения на комбинационных элементах. Сдвиговый регистр 25 предназначе для формирования серии последовательных управляющих сигналов, необходимых для функционирования ячейки Дешифратор 26 предназначен для дешифрации кода выполняемой операции для выбора ячейки в операционном блоке. Группа элементов И 27| - 27 пред ,назначена для формирования сигнало управления для коммутаторов 19, ,20 и 23, регистров 17 и 18 и группы .элементов И 24 (- 24 в зависимости от кода выполняемой операции. Перв входы элементов И соединены с выхо дами дешифратора 26, а вторые выхо ды соединены с различными выходами сдвигового регистра 25. Выкоды элементов И 27,; - 27 соединены с управляющими входами регистров 17 и 18, коммутаторов 19, 20 и 23 и с одними из входов группы элементо И 24,. Вторая группа элементов И 24 предназначена- для формирования нео ходимых управляющих сигналов для регистров 18, 22 и коммутаторов 19 20. Другие входы этой группы элеме тов И соединены с выходами блока 2 сравнения. Группа элементов ИЛИ 30j- ЗОи предназначена для объединения вход ячейки, группы элементов ИЛИ 28.и 29(., предназначены для объединения выходов коммутаторов 19, 20 и 23, соединяющих операционный блок с горизонтальными 13 и верти кальными 14 информационными шинами 812 Рассмотрим работу ячейки. Операции - инверсия, конъюнкция, дизъюнкция, импликация, запись, чтение - входят в состав операции эквивалентности, поэтому рассмотрим работу схемы при реализации операции эквивалентности. Вначале по сигналу сброса осуществляется обнуление всех регистров (цепи обнуления на фиг. 4 не показаны) . По коду записи осуществляется запись значения эталонного высказывания на регистр 17. По коду записи текущего значения расплывчатого высказывания осуществляется запись текущего значения расплывчатого высказывания на регистр 18. Предположим, что на регистр 17 записано эталонное значение расплывчатого высказывания а 0,6, а на регистр 18 - значение S 0,7. Эталонное и текущее значение расплывчатых высказываний поступают с входных информационных шин. Совместно сдвигающий регистр 25 и дешифратор 26 с помощью элементов И 27 формируют сигналы записи. Далее на дешифратор 26 поступает код операции эквивалентности и- тем самь.м возбуждает один из выходов дешифратора - в нашем примере выход операции эквивалентности. Возбужденный выход дешифратора и сигнал с регистра 25 поступают на вход одного из группы элементов И 27| - 27, а сигнал с выхода этого элемента поступает на коммутаторы 19 и 20 как сигнал разрешения вьщачи на входные щины блока сравнения содержимого регистра 17 в инверсном коде, т.е. 7 3 содержимого регистра 18в прямом коде, т.е. Ь. Блок сравнения сравнивает значения а и b и возбуждает соответствующий выход блока сравнения, указывающий На 7а : Ь, т.е. 0,,7. Сигнал со следующего такта регистра через группу элементов 27;, - 27 совместно с возбужденным выходом блока сравнения поступает на одну из групп элементов И 24ц, которая, в свою очередь, формирует сигнал в коммутатор 20 и на регистр 22. Управляющий сиг нал в коммутаторе 20 коммутирует выходы регистра 18 с входами регистров 22, а сигнал на регистре 22 разрешает запись значения b на регистр 22,

Сигнал со следующего такта регис ра 25 поступает на один из входов элемента И 27, а второй вход этого элемента И соединен с возбужденным выходом дешифратора 26. Сигнал с выхода этого элемента И поступает на коммутаторы 19 и 20. . Ког««утатор 19 коммутирует вькод регистра 17 на вход блокасравнения в прямом коде, т.е. а 0,6, а коммутатор 20 коммзггирует выход регистра 18 в инверсном коде, t.e.7b 0,3.

Блок сравнения сравнивает значения а и 7 Ь возбуждает выход, указывающи }, что а 7б, т.е. 0,6 0,3. Возбужденный выход одного из элементов И 27ц- 27 совместно с возбужденным выходом блока сравнения с помощью одного из элеме«тов И группы 24 J- 24,поступает на коммутатор 19 и на регистр 18. В коммутаторе 19 осуществляется коммутация выходов регистра 17 на вход регистра 18, а на регистре 18 формирует сигнал ;записи, таким образом осуществляется перезапись содержимого регистра 17 (а 0,6) на регистр 18. Очередной сигнал, сформированный элементами И 27( - 27„ на основе сигналов сдвигающего регистра 25 и дешифратора 26, поступает на соответствующие управляющие входы коммутатор 20 и 23. На этом рабочем такте коммтатор 23 коммутирует выходы регистр 22 на входные шины блока сравнения для ввдачи на блок сравнения значения Ь, находящегося на регистре 22, а коммутатор 20 коммутирует выходы регистра 28 с вторыми входными шинами блока сравнения для вьщачи на схему сравнения значения а 0,6. Причем в блоке сравнения выходы коммутатора 20 соединены с одними из входных щин блока сравнения, а выходы-коммутаторов 19 и 23 объединяются через элемент ИЛИ и соеЛинёны с другими входными шинами.

В результате сравнения на выходе блока сравнения возбуждается выход, показывающий, что код содержимого регистра 18 меньше, чем код, находящийся в регистре 22. т.е. 0,6 О, Завершаюпр1й сигнал с выхода регистра 25 совместно с выходом дешифратора 26 через элемент И группы ,2 поступает на один из входов И 24, а на второй вход поступает выход блока сравнения. Сигнал

с выхода этого элемента И поступает на коммутатор 20 и тем самым соединяет прямые вьжоды регистра 28 с выходными шинами ячейки, т.е. на выход поступает код числа а 0,6. На этом выполнение операции эквивалентности над расплывчатыми высказываниями завершается.

Операция ассоциативного поиска вьтолняется несколько иначе. На блок сравнения поступают определенн разряды регистров 17 и 18, при сравнении формируется сигнал выдачи на выход содержимого регистра 22.

Блок выходных регистров предназначен для вьщачи управляющей информации для других объектов из блоков памяти и операщюнных блоков во внешнюю среду (например, на исполнительные элементы технологического процесса или на системы управления) На фиг. 5 показан блок 3 выходных регистров с элементами ИЛИ 32, ,, 36, регистром 31, выходными информационными шинами 10, входами 34 записи, которые соединены с выходами местных устройств управления информационными входами 14 и 35 и выходом готовности 37 блока выходны регистров. Информационные входы 35 соединены с информационными выходами блоков памяти, а информационны входы 14 - с вертикальными информационньп-и выходами операциоиного блока.

Выходной регистр 31 имеет пх k двоичных разрядов, где k - число столбцов операционного блока, а .п - количество разрядов в одном стоце. На фиг. 5 показаны выходы 14 и 15 соответственно одного операционного блока и блока памяти, выходы других операционных блоков и блоков памяти объединяются аналогично с помощью групп элементов ИЛИ 33 - З Входы записи или синхронизации 34 со всех местных устройств управления также объединяются с помощью элементов ИЛИ 32.

При завершении выполнения юперации в процессоре по сигналу из -устройства местного управления осуществляется запись результатов обработки из операционного блока или из .блока памяти. Считывание информации с выходного регистра можно осуществить различными методами и способами. Вьгход 37 готовности блока выход .регистров п ецкаэна ен для формиро вания сигнала Занято или Свобод в устройство местного управления. Если хотя бы один из разрядов регистра 31 находится в единичном состоянии, то с помощью элемента ИЛИ 36 формируется сигнал Занято в противном случае формируется сиг нал Свободно. Блок А сравнения предназначен для предварительного сравнения старших разрядов результатов операции эквивалентности со значением порога. Сравнение осуществляется параллельно по всем строкам операционного блока со значением порога который принимает значение в интер вале Го, Л/ L J Блок сравнения состоит из R одн типных ячеек, где R - число строк операционного блока. Горизонтальны выход каждой строки соединен с соответствующим входом ячейки блок сравнения через информационные вхо ды 14. Каждая ячейка блока сравнения {фиг. 6) состоит из групп элементо И 38,- 38, 39,- 39,, 40, узла 41 сравнения, триггера 42, элемента Ш1И 43..Рассмотрим работу одной ячейки так как все ячейки одинако вы и работают синхронно. Из уст- , ройства местного управления по информационным входам 46 на схему 41 Сравнения поступает значение порога, а по первому управляющему входу 45 блока сравнения - сигнал разрешения выдачи текущего значения степени принадлежности, поступ щего через группу элементов И 38, 38 по информационным входам 13. В результате сравнения триггер 42 устанавливается в единичное состоя ние, если старшие разряды текущего значения степени принадлежности больше или равны значению порога, в противном случае свое состояние триггер не изменит. Появление более чем одного значения на выходах ячеек блока сравнения алгоритмически невозможно. Второй управляющий сигнал 48, который поступает из устройства мес ного управления, совместно с элеме том И 40 анализирует состояние три гера 42. Предположим, что триггер.в единичном состоянии. Тогда сигнал с выхода элемента И 40 с помощью группы элементов И 394- 39 коммутирует информационные выходы 44 с входами блока памяти, тем самым разрешая степени принадлежности fH; поступить в блок памяти. Кроме этого, сигнал с выхода И 40 поступает в устройство местного управления по управляющему входу 49 как сигнал сброса и приема очередного кода команды. По шине 47 из устройства местного управления поступает сигнал сброса блока сравнения. В нулевом состоянии триггера 42 коммутация входов и выходов ячейки не происходит и младшие разряды текущего значения степени принадлежности не поступают в блок памяти. Входы 13 блока сравнения связаны с горизонтальными выходными информационными шинами операционного блока. Сдвигатель 5 предназначен для преобразования входного п-разрядного информационного слова в слово разрядности операционного блока или ячеек памяти блока памяти, а также для промежуточного хранения входной информации. Разрядность входного регистра кратна разрядности одной ячейки операционного блока и блока памяти и определяется числом столбцов, входящих в операционный блок. Необходимость этого устройства диктуется тем, что количество столбцов операционного блока, используемых в работе, зависит от конкретного значения базового множества данной лингвистической переменной. Поэтому использование такого устройства позволяет загружать информацией только те столбцы операционного блока, которые необходимы для работы, что повышает быстродействие, а также для согла.сования работы источника информации с процессором. Сдвигатель 5 (фиг. 7) состоит из входного информационного регистра 50 образованного из регистров, разрядность которых равна разрядности ячеек однородной структуры, группы элементов И 51, 52,, 53,- 53, 54„, 55,- 55„ и 59,59,, элемента И 60, сдвигового регистра 56, используемого для формирования управляющих сигналов, необходимых для работы этого устройства, элементов ИЛИ 61 и 6, триггера 57, дешифратора 58 с памятью, состоящег из регистра и дешифратора, который необходим для хранения и дешифрации кода длины используемого слова. Кроме этих элементов, в состав устройства входят следующие шины: 9 - входные информационные шины, i-ые и i-H-ые выходные информационн шины первой группы 12 и 64, соединенные с операционными блоками, i-ые и i+1-ые выходные информационные шины второй группы 63 и 65, сое диненные с блоками памяти; 66 выходная шина сигнала управления сдвигом в устройство местного управ ления; 67 - шИна сигнала вьщачи очередной порции входной информации на регистр 50; 68 - входы ления коммутации сдвигателя (с помощью этих шин осуществляется выбор ка конкретного операционного блока или блока памяти); 69 - вход .управ ления записью сдвигателя (по этому сигналу осуществляется запись кода управления на регистр дешифратора 5 70 - первые управляющие входы сдвигателя (по этим входам поступает код длины выходного слова)} 71- вхо синхронизации сдвигателя, 72 - вход управляющего сигнала из местных устройств управления, разрешающий выдачу входной информации; 73 - вто рые управляющие входы сдвигателя, по которым осуществляется выборка конкретных операционного блока и блока памяти. Для других операционных блоков и блоков памяти вьдача текущей информации осуществляется аналогично. Добавляются группы элементов И аналогично группам элементов И 52„, 53,- 53, 54, и 55, - 55„ Устройство работает следующим образом. Из устройства 8 управления на ;дешифратор 58 по входам 70 поступает код длины слова, используемого в данной операции. Сигналы, которые поступают по входам 68 и 73, осуществляют выбор из нескольких операционных блоков и блоков памяти одного операционного блока и блока памяти. При вьшолнении этих ДеистВИЙ используются элементы И 59 и 5Ц, которые подготавливают к работе соответствующие г|}упп 53 И 52„, jj ,п. элементов Выходы 12 группы 54, и 55,h и соединены с инэлементов И 52|.- У1 соединены формационными входами первого операционного блока, выходы 63 группы элементов И 53j- 53 соединены с информационными входами nepJBoro блока памяти, соответственно вькоды 64 и 65 группы элементов И 54 и ,554- 55„ соединены с информационными входами вторых операционного блока и блока памяти соответственно. По входу 69 управления записью сдвигателй поступает сигнал запи- ; си из устройства управления в регистр дешифратора 58. Дешифратор кода длины слова формирует единичн сигнал, который поступает, в соответствующий разряд регистра 56. Начиная с этого разряда сдвигающий регистр 56 формирует последовательно сигналы п-разрядной параллельной записи на входнЫ регистр 50, где п-- разрядность одной ячейки операционного блока. Входная текущая информация поступает по входам 9. По управляющему выходу процессора 67 сигнал поступает к источнику входной информации для считывания последующей порции входной информации. Сигнал с последнего такта регистра 56 совместно с сигналом с выхода дешифратора 58 через группу элементов И 59 59 „ переводит схему в режим ожидания, одновременно посылая сигнал о готовности по шине 66 управления сдвигом в устройство местного управления, устанавливает триггер 57 в единичное состояние. По сигналу разрешения выдачи, который поступает по входу 72, осуществляет выдачу информационного слова, устанавливает триггер 57 в нулевое мента И 60 позволяет формировать очередное информационное слово для записи в операционный блок или в блок памяти. Этот цикл продолжается до получения сигнала сброса, который поступает из устройства, управления, или до-изменения кода команды в устройстве управления . По входу 71 из устройства управления поступают сигналы синхронизации. Устройство 6 местного управления предназначено для формирования необходимых управляющих сигналов для

функционирования операционного (блока, блока сравнения, блока памяти и блока выходных регистров. Необходимая информация для функционирования устройстваместного управ ления поступает из устройства управления .

Местные устройства управления в процессе функционирования формируют необходимые управляющие сигналы и реализуют следующие основные мик1зопрограммы:

, 3. Формирование необходимых управляющих сигналов для записи значения базовых команд в блок памяти.

Основные микропрограммы в устройстве местного управления, реализованы по принципу управляющего автомата с жесткой логикой.

На фиг. 8 показаны основные блоки, входящие в состав устройства местного управления, с соответствующими связями между блоками и сооветствующими внешними связями. Блок 74 синхронизации предназначен :для формирования основных управляющих сигналов в блок 75 регистровой памяти и блок 76 селекторов.

В дальнейшем- при описании работы устройства местного управления совокупность блоков 74 - 76 (фиг.911) рассматривается как одно устройство.

Устройство местного управления (фиг. 8 - 11) содержит блок синхронизации, состоящий И|3 группы эле ментов И 81,- 81, 874- 87„ и (, элементов И 94, 97 и 86, элементов ИЖ 79, ВО, 82, 85, 89, 92, .93 и 96, триггеров 78, 84,, 84,84 84ij,элементов И-ИЛИ 95,элемента ИЛИ88, группы элементов ИЛИ 83,

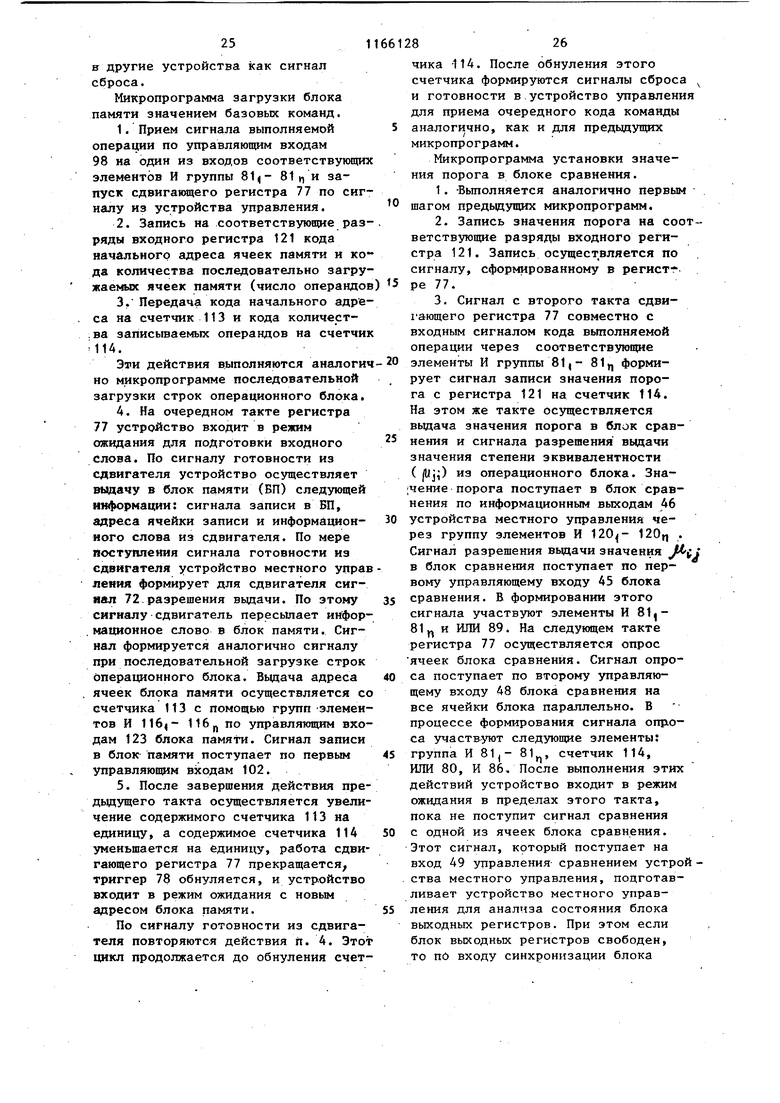

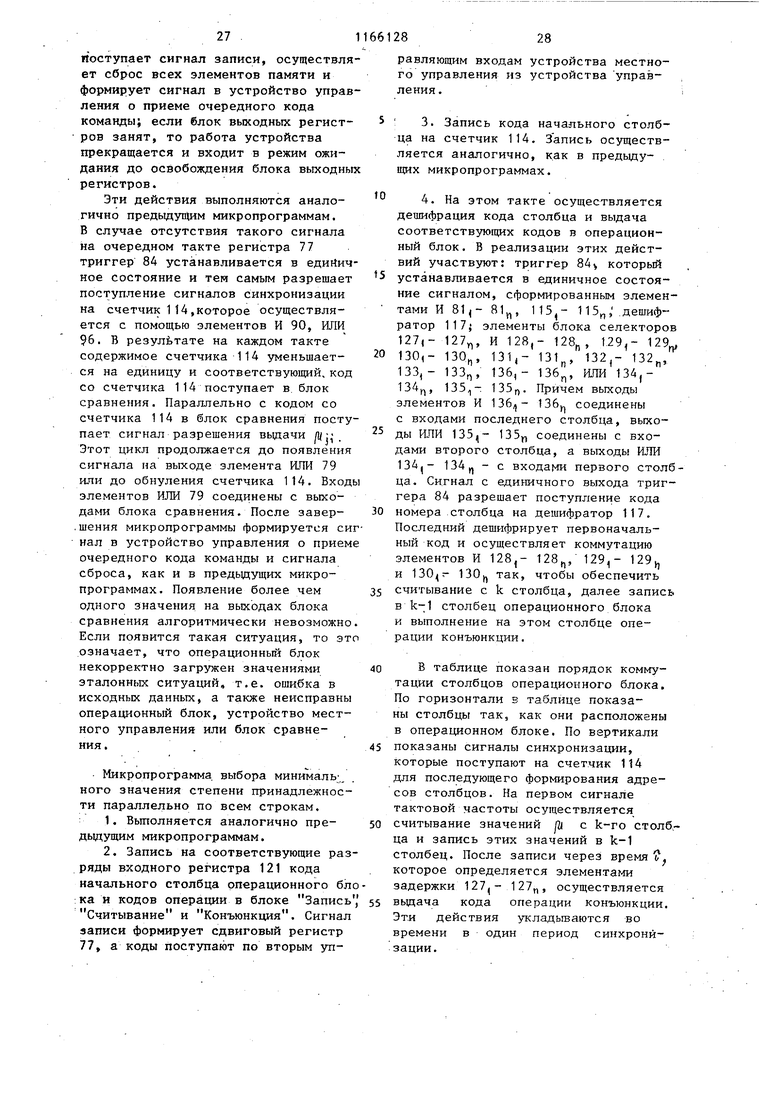

элемента задержки 91, регистра 77; блок регистровой памяти, состоящий из регистра 121, счетчиков 113 и 114, дешифраторов 117 и 119, группы элементов И 115„, 116,116, 118„, 120;- 120„, блок селекторов, состоящий из группы элементов ИЛИ 126,- 126„, 134„ и п элементов задержки 127 - 127, группы элементов И 123,- 128rti 129,- 129п, 130,- 130„, 131,- 131„, 132,- 132„, 133,- 133, и 136,- 136.

Устройство местного уп)авления имеет следующие входные и выходные шины: 71 - вход синхронизации; 66 - вход управления сдвигом, т..е. сигнал готовности из сдвигателя;

49 - вход управления сравнением из блока сравнения; 99 - вход пуска устройстваJ 98 первые управляющие входы, по которым поступает код выполняемой операции; 37 вход управления выдачей информацией, 72 - выходной управляющий сигнад в сдвигатель о выдаче текзпцей информации; 34 - выходной сигнал синхронизации блока выходных регистров, 45 - первый управляющий сигнал в блок сравнения, разрешающий начало

Сравнения/ 102 - первый управляющий вход блока памяти, по которому поступает сигнал Запись в блок памяти , 122 - вторые зп1равляющие входы устройства, по которым в устройство поступает управляющая информация из устройства управления, 15 и 16 - выходы устройства, по которым поступает управляющая информация в операционный блок; 123 управляющие входы блока памяти, по которым поступает адрес ячейки памяти, 46 - информационные выходы устройства, по .которым в блок сравнения поступает значение порога, 100 - выход устройства, по которому в устройство управления поступает сигнал о завершении действия; 101 - выход синхронизации для операционного блока, 48 - управляющий выход устройства, по которым осуществляется опрос ячеек блока сравненияi 47 - сигнал сброса для блока сравнения.

Рассмотрим последовательную по . тактную работу устройства местного управления при реализации основных микропрограмм. . Микропрограмма формирования адр сов строк операционного блока, для записи значения эталонных ситуаций 1, Из устройства з равдёния по первым управляющим входам 98 посту пает в устройство код вьшолняемой операции, а по входу пуска 99 сигнал для запуска сдвигового ре гистра 77. ; 2. Запись на соответствующие ра :ряды входного регистра 121 кода . начального адреса, кода количеств записываем1лс строк и -кода операции в. операционном блоке, т.е. запись i эталона. Необходимая управляющая информация для записи на регистр 121 поступает из устройства управления по вторым управляющим входам 122, а необходимые сигналы записи формирует сдвиговый регистр 77. 3. Передача кода начального адреса строки на счетчик 113 и код :количества записываемьрс строк на счетчик 114. Счетчик 113 предназначен для формирования последующих адресов строк операционного блока и работает как накапливающий счетчик. Счетчик 114 предназначен дпя подсчета количества выбранных строк для записи и работает как . вычитаюорй счетчик. .Запись соответствующих кодов на счетчики 11.3 и 114 осуществляется с помощью сиг лов. сформированных на соответству щих выходах элементов И 81 с местно с элементами ИЛИ 834- 83,. Сигналы на соответствующие входы элементов И 814- 81 поступают из устройсТва управления и с выходов сдвигового регистра 77. - у После записи соответствующих ко дов на счетчики 113 и 114 схема устройства входит в режим ожидания до тех пор, пока сдвигатель не подготовит информационное слово необходимой разрядности. Дпя этого очередной сигнал с выхода сдвигающего регистра 77 и сигнал из устройства управления, который поступает по одному из входов 98 |через соответствующие элементы И 81 и ИЛИ 83, устанавливают триггер 84 в единичное состояние. Последний снимает сигнал разрешения с одного из входов элементов И. 90, и тем самым прекращает поступление сигналов синхронизации на регистр 2822 В режиме ожидания устройство находился до поступления сигнала готовности из входного устройства. По мере поступления сигнала Готово из сдвигателя устройство нестного управления формирует сигнал раз-, решения вьздачи кода операции в операционный блок (запись), разрешает вьщачу- информационного слова из сдвигателя и осуществляет выбор необходимой строки. Сигнал Готово поступает по входу 66 управления сдвигом из сдвигателя на установочный вход триггера 78. Сигнал с выхода триггера 78 подготавливает ;К работе группу элементов И 87j - 87, ,на. вторые входы которых поступают сигналы с соответствуиицих выходов элементов И 81. Сигнал с выхода одного из элементов группы И 87 87 разрешает выбор необходимой стро ки операционного блока. Код строки через группу элементов И 118j- 118, из счетчика 113 поступает на дешифратор 119. Возбужденн{ выход дешифратора 119 по управляющим шинам операционного блока 16 осуществляет выбор необходимой строки. Одновременно выходной сигнал с возбужденного выхода элемента И 83j,-83j через элементы ИЛИ 93 и 92 по первому выходу 72 устройства поступает в сдвигатель в качестве сигнала разрешения рьщачи информационного слова. Вьщача кода операции в операционный блок осуществляется с помощью групп элементов И 128,- 128 , и 136,- 136. Код операции поступает с соответствующих разрядов входного регистра 121 по управляющим входам 15 операционного блока. После выполнения этих действий сигнал с выхода элемента задержки 91 осуществляет сброс триггеров 84 и 78 и запись единицы в соответствующий разряд регистра 77 и разрешает поступление сигналов синхронизации на регистр 77. Сигнал с выхода регистра 77 увеличивает содержимое счетчика 113 на единицу, содержимое счетчика 114 через элемент ИЖ 96 уменьшает на единицу. После этого устройство входит в режим ожидания. По мере поступления сигнала готовности из сдвигателя цикл повто- , ряется. Этот цикл продолжается до тех пор, пока содержимое счетчика 11А не станет равным нулю. После обнуления счетчика формируетс:я сигнал в устройство управления о прием очередного кода команды и осуществл ется обнуление всех элементов памяти, входящих 1а устройство местного упрвления. Сигнал в устройство управления формируется следующим обра зом. Если содержимое счетчика 11А станет равным нулю, то на инверсном выходе элемента ИЛИ 80 появляется сигнал, который через элемент ИЛИ 8 формирует сигнал сброса, а через элемент ИЛИ 85 поступает на элемент И 97. На другой вход этого элемента поступает сигнал с блока выходных регистров по входу управления выдачей информации. Этот сигнал являетс сигналом контроля состояния блока выходных регистров. Если блок выход ных регистров свободен, то сигнал с четвертого выхода 100 устройства поступает в устройствоуправления как сигнал разрешения приема очеред ного кода команды. При выполнении этой микропрограммы код Запись воспринимает только та строка операционного блока, которая возбуждена выходом дешифратора 119, хотя код параллельно поступает во все строки. Возбужденными могут быть от одной до всех строк одновременно в зависимости от программы. Рассмотрим микропрограмму записи текущего значения лингвистической п ременной параллельно во все строки операционного блока. 1.Прием, сигнала выполняемой операции на одни из входов соответс вующих элементов Н группы 81 ( - 81 управляющим входам 98 и запись значения единицы в первый разряд регис ра 77, которое поступает по входу пуска устройства. 2.Запись кода выполняемой опера ции в операционный блок и кода коли чества загружаемых информационных слов в операционный блок на соответствующие разряды входного регист ра 121. Код количества загружаемых операндов в операционный блок в данной операции равен единице. Запи осуществляется с помощью управляющего сигнала, который формируется регистром 77. Срответствзтощие коды из устройства управления: по управ824ляющим входам 122 поступают на информационные входы регистра 121. 3. Передача кода количества загружаемых операндов в операционный блок на счетчик 14Д и установка триггера 84 в единичное состояние. Сигнал записи на счетчик 114 и сигнал установки триггера 84 формируют соответствующие элементы И группы 81(- 81 совместно с элементами ИЛИ 83;(- 83. После выполнения этих действий устройство переходит в режим ожидания до тех пор, пока сдвигатель не сформирует информационное слово необходимой разрядности (текущее значение лингвистической переменной). 4. По сигналу готовности из сдвигателя устройство местного управления формирует сигнал разрешения выдачи информационного слова в сдвигатель и осуществляет вьщачу.кода записи текущего значения в операционный блок. Сигнал готовности из сдвигателя, который поступает по входу управления сдвигом 66, устанавливает триггер 78 в единичное состояние. Сигнал разрешения вьщачи информационного слова, который формируется с помощьюэлементов И ,, и 87|- 87, ИЛИ 92 и 93, по управляюгдему входу сдвигателя 72 поступает в сдвигатель, одновременно разрешая вьщачу кода операции с входного регистра 121 через соответст128,- 128, вующие группы элементов И 131,- 131, 136h блока 76 селекторов, причем эти группы элементов И охватывают первые и последние столбцы операционного блока. Для промежуточных столбцов можно расширить аналогично. Одновременно сигнал разрешения вьщачи через элементы задержки 91 и ИЛИ 96 уменьшает содержимое счетчика 114 на единицу. 5. В конце предьщущего такта после обнуления счетчика 114 элементы ШШ 80 и 82 формируют сигнал сброса для устройства местного управления, а также совместно с элементом ИЛИ 85 по четвертому выходу 100 этот же сигнал поступает в устройство управления как сигнал приема очередного кода команды. Этот же сигнал также поступает в другие устройства как сигнал сброса. Микропрограмма загрузки блока памяти значением базовых команд. 1.Прием сигнала выполняемой операции по управляющим входам 98 на один из входов соответствующих элементов И группы 81ц и запуск сдвигающего регистра 77 по сигналу из устройства управления. 2.Запись на соответствующие разряды входного регистра 121 кода начального адреса ячеек памяти и ко да количества последовательно загружаемых ячеек памяти (число операндов 3. Передача кода начального адреса на счетчик 113 и кода количества записываемых операндов на счетчик М14. Эти действия выполняются аналогич но микропрограмме последовательной загрузки строк операционного блока. 4.На очередном такте регистра 77 устройство входит в режим ожидания для подготовки входного слова. По сигналу готовности из сдвигателя устройство осуществляет В14дачу в блок памяти (БП) следующей информации: сигнала записи в БП, адреса ячейки записи и информационного слова из сдвигателя. По мере исступления сигнала готовности из сдвигателя устройство местного управ лекия формирует для сдвигателя сигнал 72.разрешения вьщачи. По этому сигналу сдвигатель пересьтает инфор. мационное слово в блок памяти. Сигнал формируется аналогично сигналу при последовательной загрузке строк операционного блока. Вьщача адреса ячеек блока памяти осуществляется со счетчика 113с помощью групп элементов И 1164- 116 по управляющим входам 123 блока памяти. Сигнал записи в блок памяти поступает по первым управляющим входам 102. 5.После завершения действия предьщущего такта осуществляется увеличение содержимого счетчика 113 на единицу, а содержимое счетчика 114 уменьшается на единицу, работа сдвигающего регистра 77 прекращается, триггер 78 обнуляется, и устройство входит в режим ожидания с новьм адресом блока памяти. По сигналу готовности из сдвигателя повторяются действия п. 4. Этот цикл продолжается до обнуления счет1826 чика -114. После обнуления этого счетчика формируются сигналы сброса и готовности в устройство управления для приема очередного кода команды аналогично, как и для предьздущих микропрограмм. Микропрограмма установки значения порога в блоке сравнения. 1.-Вьшолняется аналогично первым шагом предьщущих микропрограмм, 2.Запись значения порога на соответствующие разряды входного регистра 121. Запись осущест вляется по сигналу, сформированному в регистг. ре 3.Сигнал с второго такта сдвигающего регистра 77 совместно с входным сигналом кода выполняемой операции через соответствующие элементы И группы 81,- 8 Ц формирует сигнал записи значения порога с регистра 121 на счетчик 114. На этом же такте ос5пцествляется вьщача значения порога в блок сравнения и сигнала разрешения значения степени эквивалентности ( jUji) из операционного блока. Значениепорога поступает в блок сравнения по информационным выходам 46 устройства местного управления через группу элементов И 120ц . Сигнал разрешения вьщачи значения ij в блок сравнения поступает по первому управляющему входу 45 блока сравнения. В формировании этого сигнала участвуют элементы И и ИЛИ 89. На следующем такте регистра 77 осуществляется опрос ячеек блока сравнения. Сигнал опроса поступает по второму управляющему входу 48 блока сравнения на все ячейки блока параллельно. В процессе формирования сигнала onpioса участвуют следующие элементы: группа И 81|- 81 , счетчик 114, ИЛИ 80, И 86, После выполнения этих действий устройство входит в режим ожидания в пределах этого такта, пока не поступит сигнал сравнения с одной из ячеек блока сравнения. Этот сигнал, который поступает на вход 49 управления сравнением устрой ства местного управления, подготавливает устройство местного управления для анализа состояния блока выходных регистров. При этом если блок выходных регистров свободен, то по входу синхронизации блока Поступает сигнал записи, осуществля ет сброс всех элементов памяти и формирует сигнал в устройство управ ления о приеме очередного кода команды; если блок выходных регистров занят, то работа устройства прекращается и входит в режим ожидания до освобождения блока выходны регистров. Эти действия выполняются аналогично предыдупщм микропрограммам. В случае отсутствия такого сигнала на очередном такте регистра 77 триггер 84 устанавливается в едийич ное состояние и тем самым разрешает поступление сигналов синхронизации на счетчик 114.которое осуществляется с помощью элементов И 90, ИЛИ 96. В резул4 тате на каждом такте содержимое счетчика 114 уменьшается на единицу и соответствующий, код со счетчика 114 поступает в блок сравнения. Параллельно с кодом со счетчика 114 в блок сравнения посту пает сигнал разрешения выдачи /У:,-. Этот цикл продолжается до появления сигнала на выходе элемента ИЛИ 79 или до обнуления счетчика 114. Вход элементов ИЛИ 79 соединены с выходами блока сравнения. После завер.шения микропрограммы формируется си нал в устройство управления о прием очередного кода команды и сигнала сброса, как и в предьщущих микропрограммах. Появление более чем одного значения на выходах блока сравнения алгоритмически невозможн Если появится такая ситуация, то э означает, что операционньй блок некорректно загружен значениями эталонных ситуаций, т.е. ошибка в исходных данных, а также неисправны операционный блок, устройство мест ного управления или блок сравнения . . Микропрограмма, выбора минималь;., ного значения степени принадлежнос ти параллельно по всем строкам. 1. Вьтолняется аналогично предыдущим микропрограммам. 2. Запись на соответствующие ра ряды входного регистра 121 кода начального столбца операционного б :ка и кодов операции в блоке Запис Считывание и Конъюнкция. Сигна записи формирует сдвиговый регистр 77, а коды поступают по вторым управляющим входам устройства местного управления из устройства управления .: 3.Запись кода начального столбца на счетчик 114. Запись осуществляется аналогично, как в предыдущих микропрограммах. 4.На этом такте осуществляется дешифрация кода столбца и выдача соответствующих кодов в операционный блок. В реализации этих действий участвуют: триггер 84 которьй устанавливается в единичное состояние сигналом, сформированным элементами И В, t 115„, дешифратор 117; элементы блока селекторов 127,- 127, И 128,- 128,, 129,- 129 130,- 130, 131,- 131„, 132,- 132,, 133,- 133, 136,- 136, ИЛИ 134,134, 135f). Причем выходы элементов И 136,,- 136 соединены с входами последнего столбца, выходы ИЛИ 135(|- 135 соединены с входами второго столбца, а выходы ИЛИ 134|- 134j, - с входами первого столбца. Сигнал с единичного выхода триггера 84 разрешает поступление кода номера столбца на дешифратор 117. Последний дешифрирует первоначальный код и осуществляет коммутацию элементов И 128,- 128„, 129,- 129 и 130j, так, чтобы обеспечить считывание с k столбца, далее запись в k-1 столбец операционного блока и выполнение на этом столбце операции конъюнкции. В таблице показан порядок коммутации столбцов операционного блока. По горизонтали в таблице показаны столбцы так, как они расположены в операционном блоке. По вертикали показаны сигналы синхронизации, которые поступают на счетчик 114 для последующего формирования адресов столбцов. На первом сигнале тактовой частоты осуществляется считывание значений Ш с k-ro столбца и запись этих значений в k-1 столбец. После записи через время . которое определяется элементами задержки 127,- 127„, осуществляется вьщача кода операции конъюнкции. Эти действия укладьшаются во времени в один период синхронизации.

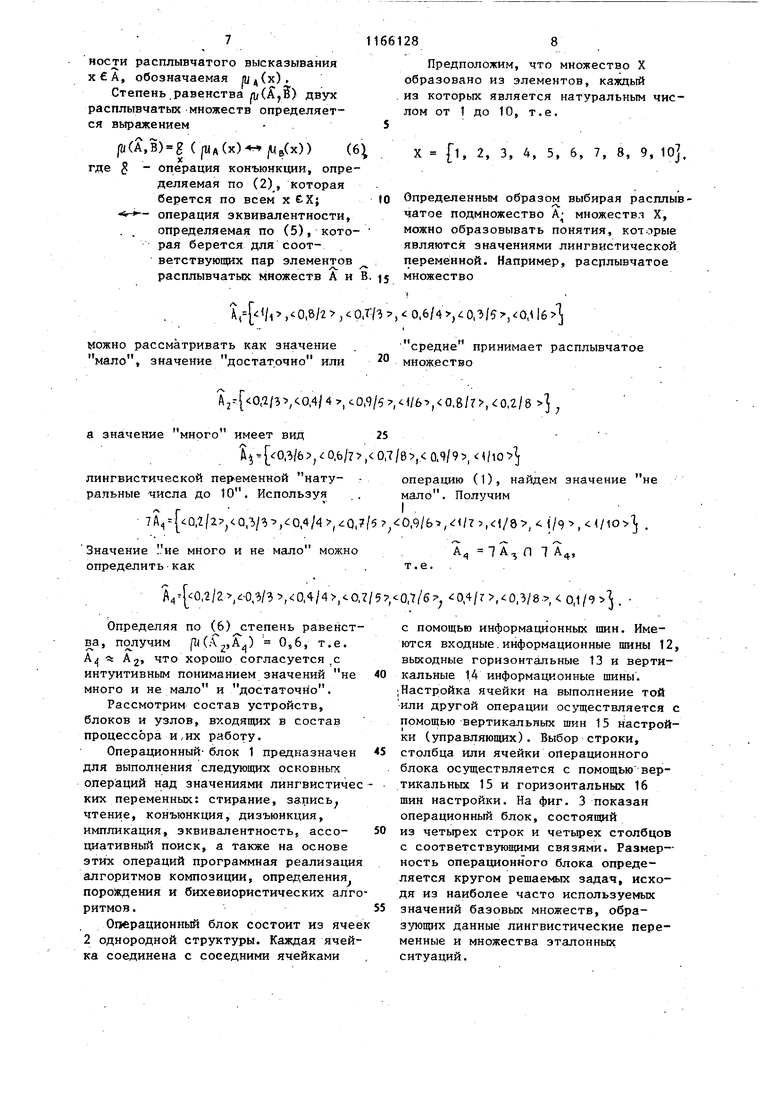

то/)5цо6

k-1

k-2 mottmi

f

СУШ.

зап.

конъюн.

счит.

Сигналы с выходов дешифратора 117 через группу элементов ИЛИ 126,126 и задержки 127 осущест- вляют необходимые коммутации. Этот цикл продолжается до обнуления счети чика 114. После обнуления счетчика 114 формируется сигнал приема очередного кода команды в устройство управления.

В данном примере реализации устройства местного .управления рассмот| ен последовательный принцип сравяекия содержимого столбцов. Воз можно реализовать и другой вариантпараллельный. В этом случае функциональная схема устройства местного управления будет сложнее почти в 2 раза , но при этом увеличится быстродействие примерно в 5-6 раз. При реализации этогоспособа на ; первом такте осуществляется попарjHoe параллельное сравнение содержиJMoro столбцов, а на втором такте (передача с одних столбцов на другие, Например, на первом такте сравнивается содержимое столбцов k с k-1; k-2 с k-3i k-4 с k-5 и т.д., а на втором такте передается содераммое k-1 столбца на k-3,k-5 столбца на k-7 и т.д., и выполняется опе рация конъюнкции.

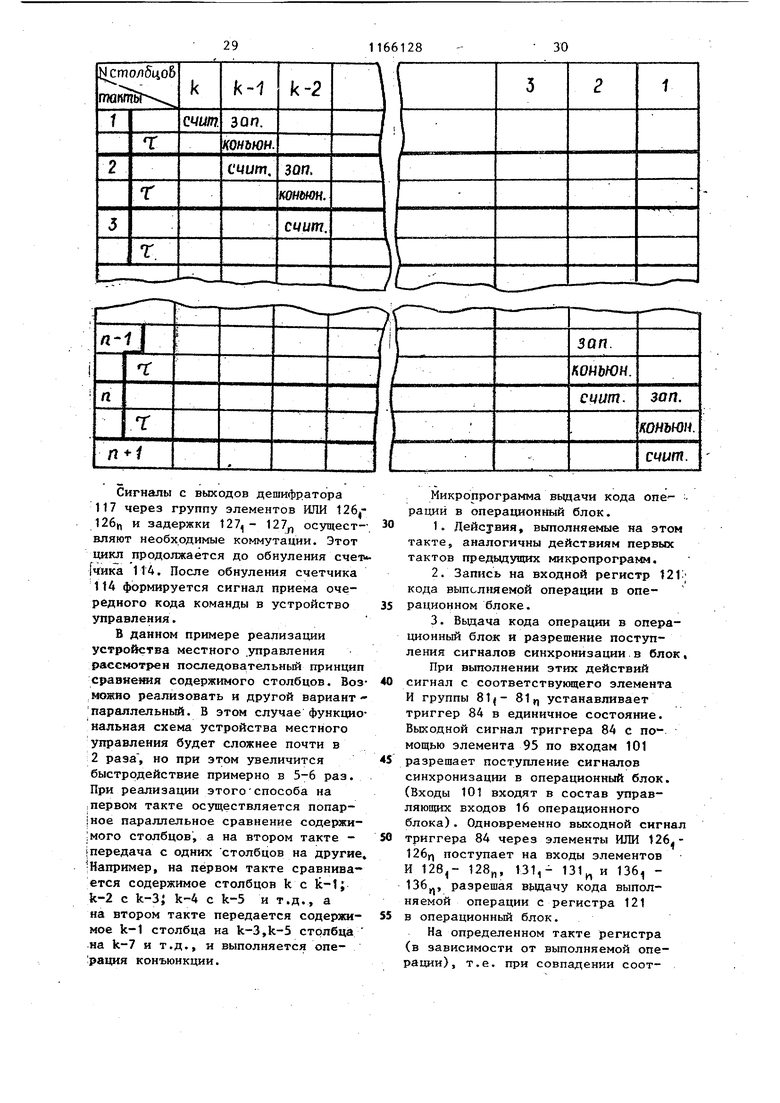

Микропрограмма вьщачи кода one раций в операционный блок.

При выполнении этих действий сигнал с соответствующего элемента И группы 81J- 81 устанавливает триггер 84 в единичное состояние. Выходной сигнал триггера 84 с помощью элемента 95 по входам 101 разрешает поступление сигналов синхронизации в операционный блок. (Входы 101 входят в состав управляющих входов 16 операционного блока). Одновременно выходной сигна триггера 84 через элементы ИЛИ 126,126f поступает на входы элементов

И 128,- 128„,

136 131,131„и

136, разрешая вьщачу кода выполняемой операции с регистра 121 в операционный блок.

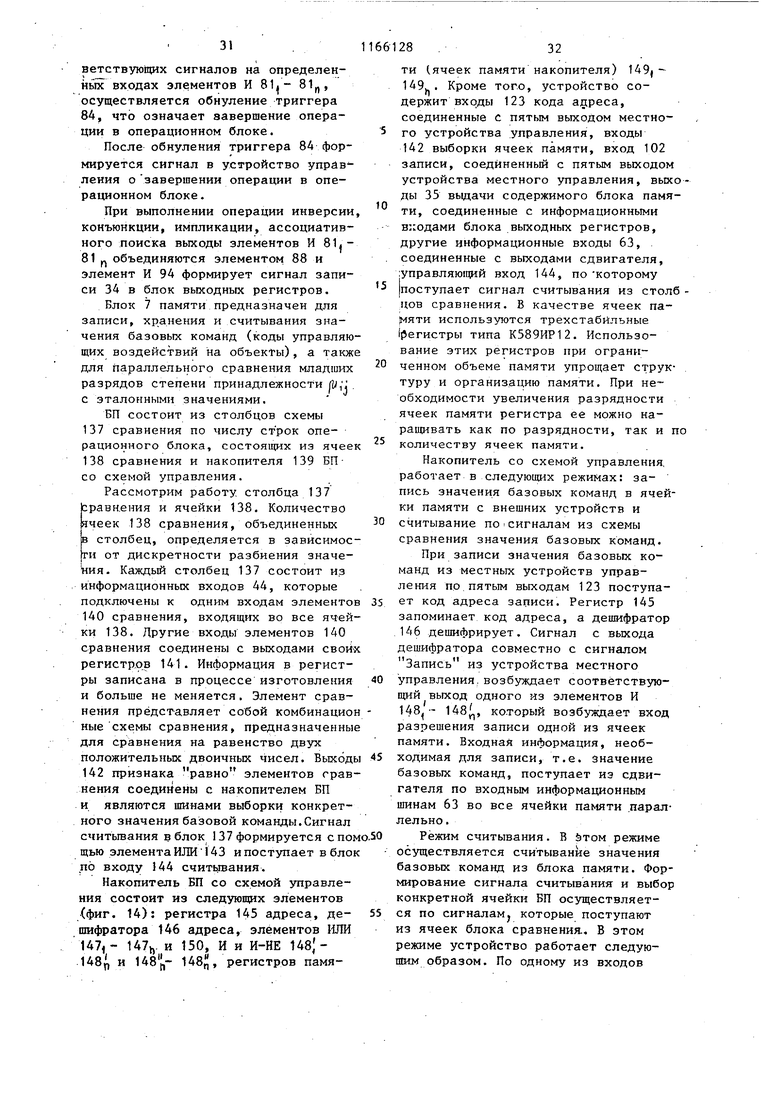

На определенном такте регистра (в зависимости от выполняемой операции), т.е. при совпадении соответствующих сигналов на определенных входах элементов И 81, осуществляется обнуление триггера 84, что означает завершение операции в операционном блоке. После обнуления триггера 84 формируется сигнал в устройство упрйв ления о завершении операции в операционном блоке. При выполнении операции инверсии конъюнкции, импликации, ассоциативного поиска выходы элементов И 81j81 „ объединяются элементом 88 и элемент И 94 формирует сигнал записи 34 в блок выходных регистров. Блок 7 памяти предназначен для записи, хранения и считывания значения базовых команд (коды управляю щих воздействий на объекты), а такж для параллельного сравнения младших разрядов степени принадлежности гУ;; с эталонными значениями. БП состоит из столбцов схемы 137сравнения по числу строк операционного блока, состоящих из ячее 138сравнения и накопителя 139 БПсо схемой управления. Рассмотрим работу столбца 137 сравнения и ячейки 138. Количество ячеек 138 сравнения, объединенных в столбец, определяется в зависимос ти от дискретности разбиения значения. Каждый столбец 137 состоит из информационных входов 44, которые подключены к одним входам элементо 140 сравнения, входящих во все ячей ки 138. Другие входы элементов 140 сравнения соединены с выходами свои регистров 141. Информация в регистры записана в процессе изготовления и больше не меняется. Элемент сравнения представляет собой комбинацио ные схемы сравнения, предназначенны для сравнения на равенство двух положительных двоичных чисел. Выход 142 признака равно элементов срав нения соединены с накопителем БП и являются шинами выборки конкретного значения базовой команды. Сиг нал считывания в блок 137 формируется спо щью элемента ИЛИ 43 и поступает в бло по входу 144 считьлвания. Накопитель БП со схемой управления состоит из следующих элементов (фиг. 14): регистра 145 адреса, дешифратора 146 адреса, элементов ИЛИ 147,- 147|,. и 150, И и И-НЕ 148,148 и ,- 148, регистров памя28 .32 ти (ячеек памяти накопителя) 149j 149. Кроме того, устройство содержит входы 123 кода адреса, соединенные с пятым выходом местного устройства управления, входы 142 выборки ячеек памяти, вход 102 записи, соединенный с пятым выходом устройства местного управления, вькоды 35 выдачи содержимого блока памяти, соединенные с информационными входами блока выходных регистров, другие информационные входы 63, соединенные с выходами сдвигателя, управляющий вход 144, покоторому поступает сигнал считывания из столб цов сравнения. В качестве ячеек используются трехстабйльные (регистры типа К589ИР12. Использование этих регистров при ограниченном объеме памяти упрощает структуру и организацию памяти. При необходимости увеличения разрядности ячеек памяти регистра ее можно наращивать как по разрядности, так и по количеству ячеек памяти. Накопитель со схемой управления, работает в следующих режимах: запись значения базовых команд в ячейки памяти с внешних устройств и считывание по сигналам из схемы сравнения значения базовых команд. При записи значения базовых команд из местных устройств управления по пятым выходам 123 поступает код адреса записи. Регистр 145 запоминает код адреса, а дешифратор 146 дешифрирует. Сигнал с выхода дешифратора совместно с сигналом Запись из устройства местного управления,возбуждает соответствующий выход одного из элементов И 148, который возбуждает вход разрешения записи одной из ячеек памяти. Входная информация, необходимая для записи, т.е. значение базовых команд, поступает из сдвигателя по входным информационным шинам 63 во все ячейки памяти параллельно . Режим считывания. В йтом режиме осуществляется считывание значения базовых команд из блока памяти. Формирование сигнала считывания и выбор конкретной ячейки БП осуществляется по cигнaлaмJ которые поступают из ячеек блока сравнения, В этом режиме устройство работает следующим образом. По одному из входов 142 поступает сигнал с возбужденног выхода ячейки 138 столбца 137. Сигнал с возбужденного входа 1Д2 через соответствующий элемент ИЛИ группы 147 - 1А7у. возбуждает один из входов соответствующего элемента И-НЕ группы 148J- . Тем самым осуществляется выбор ячейки памяти. Сигнал считывания поступает по одному из выходов 144 столбцов срав нения и элемента ИЛИ 150, который возбуждает вторые входы всех элемен тов И-НЕ 14Я,- 143. Тот элемент fl К группы 148 J- 148, у которого возбуждены оба входа, переводит соо ветствующую ему ячейку памяти в рабочее состояние. Ячейка памяти в ра бочем состоянии осуществляет выдачу на информационные выходы 35 блока памяти содержимого ячейки. Однако одновременное возбуждение двух и более выходов 142 не допускается. Реализация считывания по-принципу равенства какому-то заранее заданному значению позволяет получить преимущества АПП не тол ко при выполнении операций в оперн ционном блоке, но и при обращении . к накопителю блока памяти, повысить быстродействие БР при одновременном упрощении блока памяти. Устройство управления предназначено для группового управления не- . сколькими операционными блоками и обеспечивает прием входной управляющей информации с различных устройств ввода, дешифрирует и распред ляет эту входную управляющую информацию между сдвигателем и устройством местного управления. Кроме этог устройство управления согласует работу во времени всех остальных блоков и устройств процессора. Управляющая информация, которая проступает в устройство управления с блока ввода, имеет формат, состоя ;щий из 7 зон: И-я зона содержит код, указывающий на формат команды 2-я зона - код порядкового номера используемых опе рационного блока, блока сравнения и блока памяти 3-я зона - код, указывающий на разрядность используемого информационного слова; 4-я зона - код выполняемой операции; 5зона - код признака операционного 2834 блока или блока памяти; 6-я зона код количества последовательно загружаем1)1Х операндов в операционный блок или в блок памяти; 7-я зона код логической операции, выполняемой в операционном блоке. В зависимости от конкретной реализации системы команд некоторые зоны управляющего слова могут отсутствовать или нести другую информацию. Устройство управления (фиг. 15) содержит: сдвиговый регистр 151, дешифраторы 153 и 160, выходные регистры 154 и 155, триггер 158, группы элементов И 156,-156„, 157, т 157 и 161(- 16Ц, ИЛИ 159, генератор 15 синхроимпульсов, группу селекторов 152,- 15.,, вход 11 кода операции процессора, выход 68 сигналов выборки операционного блока или блока памяти, выходной сигнал 69 записи управляющей информации в сдвигатель, выходы 70 сигналов кодов длины информационных слов, выходы 71 синхронизации, выходные сигналы 73 выборки операционного блока и блока памяти, выходы 98 для передачи кода команды в устройство местного управления, выход 99 сигналов запуска устройства местного управления, входные сигналы 100 о завершении выполнения операции в устройстве местного управления, выходы 122 сигналов кодов операций. Рассмотрим работу устройства управления в основных режимах обработки входной управляющей информации. Перед началом работы с пульта управления осуществляется сброс процессора. Цепи сброса на функциональных схемах не показаны, как принято для регулярных цепей. После сброса осуществляется запуск процессора, для чего по сигналу с пульта управления осуществляется запуск генератора 150 синхронизации и через группу элементов И разрешает поступление на дешифратор 160 первой зоны кода команды. Дешифратор 160 дешифрирует первую зону кода команды и осуществляет запись единицы в соответствующий разряд регистра 151. В зависимости от разряда, куда записана единица, осуществляется считывание необходимого количества зон кода команды, входящих в данную команду. На своем первом такте регистр 151 формирует сиг

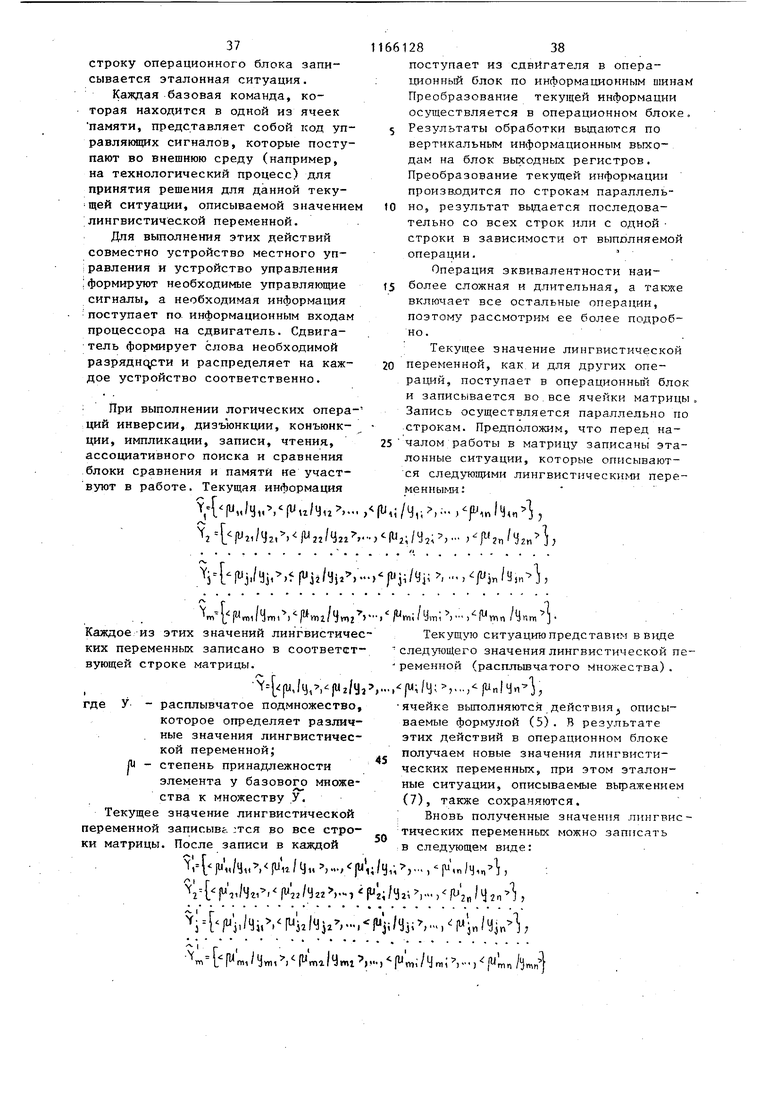

нал разрешения передачи второй зоны кода команды на дешифратор 153. Передача второй зоны кода команды осуществляется с помощью элементов 152j. Дешифратор дешифрирует код и регистр 154 запоминает на одном из своих выходов признак выбранных операционного блока и блока памяти.

На втором такте регистр 151 форм рует сигнал, Который поступает на первые входы всех элементов И 156| 156,, тем самым разрешая выдачу третьей зоны кода команды в сдвигатель. Код поступает по выходам 70 о Очередной такт регистра 151 формирует сигнал, который поступает на селекторы 152;|- 152yj, и тем рамьм разрейает поступление четвертой зоны кода команды на дешифратор. Одновременно этот же сигнал с выхода регистра 151 разрешает запись на регистр 155 признака кода выполняемой операции. С-выхода 98 регистра 155 признак кода поступает в устройство местного управлет- я для формирования иеобходимьпс управляющих сигналов для даннорз операции. Регистры154 и 155 запоминают соответст-вующие признаки кодов до завершения данной операции

На четвертом такте регистр 151 формирует сигнал, который возбуждает один из входов группы элемен™ тов И tS7|j- 157, На другие входы элементов И поступает значение ;пятой зоны кода команды, т.е , начального адреса операционного блока или блока памяти. Один из разрядов этой зоны осуществляет выбор операционного блока или блока памяти и в зависимости от этого разряда тригге 158 принимает единичное или нулевое значение. Сигналы с выходов триггера 158 по., вьгходам 68 поступают в сдвигатель, как сигналы выдачи входного информационного слова в. операционньй блок или в блок памяти

На последующих двух тактах регистр 151 формирует сигналы для выдачи в устройство местного управления шестой и седьмой зон кода команды. Шестая и. седьмая зоны кода команды, т.е. код количества последовательно загружаемых операндов в операционный блок или в блок памяти и;:код логической операции

В операционном блоке, пересыпаются в устройство местного управления через элементы И 157,- 157 через выходы 122,

5 После выполнения этих действий регистр 151 обнуляется. Дальнейший запуск регистра 151 осуществляется по сигналам из местных устройств управления, которые поступают по входам 100, Одновременно при вьщаче соответствующих кодов в местные устройства управления и в сдвигатель по выходам 99 и 69 соответственно поступают сигналы записи. Схема fS сравнения, или элемент сравнения, которая используется во многих устройствах процессора, предназначена для параллельного сравнения двух кодов п-разрядных двоичных положительных чисел на равенство, больше или меньше, т.е. реализует следующие функции: если А и В два положительных числа, то

н,(А,в) р д: 1 с, при ,

н Сд Р О, при А«св;

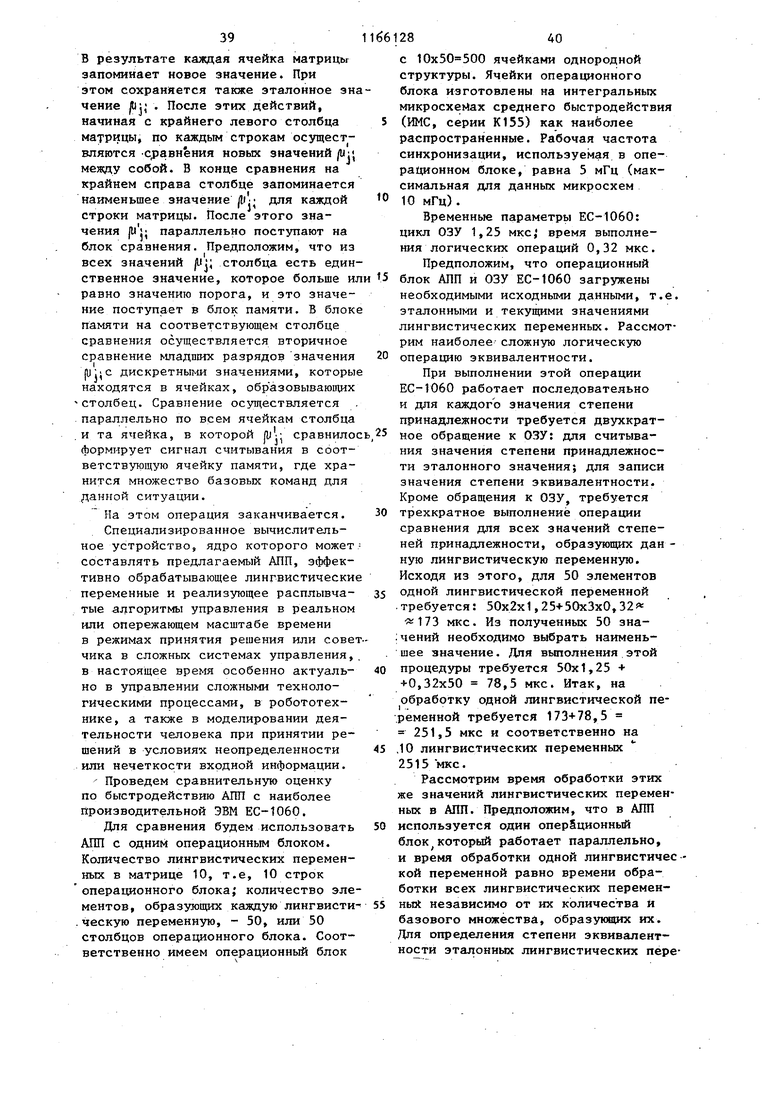

Узел построен как классическая схема сравнения на комбинационных элементах (фиг, 16) 162„, 163,- 163, 164j- 164f,, 165;,- 165„, 166 и имеет входные 167 i л п}и выходные 168 (Н, Н,) и 169 (Н,) шины. По входам А и В поступают соответствующие коды входных чисел, на выходе имеющие признаки Н, Hj или Н,, Е и поступающие в соответст вующие элементы устройств. Работу схемы несложно проследить по схеме, представленной на фиг. 16, задавая различные коды чисел.

Схема сравнения в конкретных устройствак имеет- необходимое количество разрядов;

Рассмотрим работу процессора в целом. Перед началом работы необходимо установить в нулевое состояние весь процессор , Для этого

устройство управления формирует.специальный сигнал сброса. После сбро- са необходимо осуществить предварительную запись информации. Для вначале загружаются блоки памяти значением множества базовых команд, устанавливается значение порога на блоке сравнения и в кажду строку операционного блока записывается эталонная ситуация. Каждая базовая команда, которая находится в одной из ячеек памяти, представляет собой код уп равлякицих сигналов, которые посту пают во внешнюю среду (например, на технологический процесс) для принятия решения для данной теку щей ситуации, описываемой значени ;лингвистической переменной. Для выполнения этих действий совместно устройство местного упIравления и устройство управления I формируют необходимые управляющие сигналы, а необходимая информация поступает по. информационным входа процессора на сдвигатель. Сдвигатель формирует слова необходимой разряднцрти и распределяет на каж дое устройство соответственно. : При выполнении логических опера ций инверсии, дизъюнкции, конъюнкции, импликации, записи, чтения, ассоциативного поиска и сравнения блоки сравнения и памяти не участвуют в работе. Текущая информация ,,,fUn/4u 2(У21/Ч2,

V f j- i- PJ2/4il -)

Vt(,.JJm,| mz/4 n2-./ iyii - r«j4nm l.

Каждое из этих значений лингвистичес- Текущую ситуацию представим в виде ких переменных записано в соответст- следующего значения лингвистической П вующей строке матрицы. ременной (распльшчатого множества).

.,/4,,-jU2/yi,...,fW;/4; -.-; pnHn1,

где У- - расплывчатое подмножество, -ячейке выполняются действияj описыкоторое определяет различные значения лингвистической переменной; AJ - степень принадлежности

элемента у базового множества к множеству У. Текущее значение лингвистической переменной записывь :тся во все строки матрицы. После записи в каждой

г .. un/УК7-л f i;/y,) , И Р /Чг1Р22/Чгг)--,К;/Чг; - И 2„142п,

,Pi2lЧJz,.м l Ji/Чji.-м(lJ JinЪ l PU/yrr,,/(mj4mi -,fumi/4mi,.

ваемые формулой (5). В результате этих действий в операционном блоке получаем новые значения лингвистических переменных, при этом эталонные ситуации, описываемые выражением (7), также сохраняются.

Вновь полученные значения лингвистических переменных можно записать в следующем виде: 2838 поступает из сдвйгателя в операционный блок по информационным шинам Преобразование текущей информации осуществляется в операционном блоке. Результаты обработки вьздаются по вертикальным информационным выходам на блок выходных регистров. Преобразование текущей информации производится по строкам параллельно, результат выдается последовательно со всех строк или с одной строки в зависимости от выполняемой операции,° . Операция эквивалентности наиболее сложная и длительная, а также включает все остальные операции, поэтому рассмотрим ее более подробно. Текущее значение лингвистической переменной, как, и для других операций, поступает в операционный блок и записывается во.все ячейки матрицы , Запись осуществляется параллельно по строкам. Предположим, что перед началом работы в матрицу записаны эталонные ситуации, которые описываются следующими лингвистическими пере мeнны м:У,)p1nfУ nl, гпУгп ;/У2; 39 В результате каждая ячейка матрицы запоминает новое значение. При этом сохранйется также эталонное эн чение |4j, . После этих действий, начиная с крайнего левого столбца матрицы, по каждым строкам осуществляются c зaвнeния новых значений jU- между собой. В конце сравнения на крайнем справа столбце запоминается наименьшее значение ; для каждой строки матрицы. После этого значения (uj параллельно поступают на блок сравнения. Предположим, что из всех значений |U:; столбца есть един ственное значение, которое больше и равно значению порога, и это значение поступает в блок памяти. В блок памяти на соответствующем столбце сравнения осутдествляется вторичное сравнение младших разрядов значения |U;;c дискретными значениями, которы находятся в ячейках, образовывающих столбец. Сравнение осуществляется параллельно по всем ячейкам столбца и та ячейка, в которой Ш- сравнило формирует сигнал считывания в соответствующую ячейку памяти, где хранится множество базовых команд для данной ситуации. На этом операция заканчивается. Специализированное вычислительное устройство, ядро которого может составлять предлагаемый АПП, эффективно обрабатывающее лингвистически переменные и реализующее расплывчатые алгоритмы управления в реальном или опережающем масштабе времени в режимах принятия решения или сове чика в сложных системах управления, в настоящее время особенно актуально в управлении сложными технологическими процессами, в робототехнике, а также в моделировании деятельности человека при принятии решений в условиях неопределенности или нечеткости входной информации. Проведем сравнительную оценку по быстродействию АПП с наиболее производительной ЭВМ ЕС-1060. Для сравнения будем использовать АПП с одним операционным блоком. Количество лингвистических переменных в матрице 10, т.е, 10 строк операционного блока; количество эле ментов, образующих каждую лингвисти .ческую переменную, - 50, или 50 столбцов операционного блока. Соответственно имеем операционный блок 2840 с 10x50 500 ячейками однородной структуры. Ячейки операционного блока изготовлены на интегральных микросхемах среднего быстродействия (ИМС, серии К155) как наиболее распространенные. Рабочая частота синхронизации, используемая в операционном блоке, равна 5 мГц (максимальная для данных микросхем 10 МГц). Временные параметры ЕС-1060: цикл ОЗУ 1,25 мкс; время выполнения логических операций 0,32 мкс. Предположим, что операционный блок АПП и ОЗУ ЕС-1060 загружены необходимыми исходными данными, т.е. эталонными и текущими значениями лингвистических переменных. Рассмотрим наиболее сложную логическую операцию эквивалентности. При выполнении этой операции ЕС-1060 работает последовательно и для каждого значения степени принадлежности требуется двухкратное обращение к ОЗУ: для считывания значения степени принадлежности эталонного значения; для записи значения степени эквивалентности. Кроме обращения к ОЗУ, требуется трехкратное выполнение операции сравнения для всех значений степеней принадлежности, образующих данную лингвистическую переменную. Исходя из этого, для 50 элементов одной лингвистической переменной требуется: 50x2x1,25+50x3x0,32 МКС. Из полученных 50 значений необходимо выбрать наименьшее значение. Для выполнения этой процедуры требуется 50x1,25 +0,32x50 78,5 мкс. Итак, на обработку одной лингвистической переменной требуется 173+78,5 - 251,5 мкс и соответственно на ,10 лингвистических переменных 2515 мкс. Рассмотрим время обработки этих же значений лингвистических переменных в АПП. Предположим, что в АПП используется один опер5ционньй блок который работает параллельно, и время обработки одной лингвистичес кой переменной равно времени обработки всех лингвистических переменный независимо от их количества И базового множества, образующих их. Для определения степени эквивалентности эталонных лингвистических пере41 1

менных с текущим значением лингви сти ческой переменной требуется три рабочих.такта, или 3x0,,6 мкс.

Выбор наименьшего значения степени эквивалентности для всех лингвистических переменньЕХ возможен двумя способами, которые зависят от реализации устройства местного управления: последовательный и последовательно-параллельный способы.

При последовательном способе реализации затрачивается время 50x0, МКС. При последовательно6612842

параллельном способе 7x0,,4 мкс. И в зависимости от этого общее

время, затрачиваемое операционным блоком, 10+0,,6 11 мкс и 1,4-t5 +0,6 2 мкс. По сравнению с ЕС-1060:

11

2515

-1,3-103 ра«2,27 -102 раза и за.

Эффективность- растет вместе с 10 ростом количества элементов базового множества, образукицих лингвистические переменные, и число лингвистических переменных.

1

/

J

w

Ji 73

/3

мг/wwV

/ /

5

«

/5

Ж

/2

тГ

-li

M.

T 7/ П

/

57V

/О

/ /

35

w

v

/ v7 W V / Г

SJf

/

ж

fZJ

7

/ / 9H22

Jf

63

7J 6

fl

0f/e.2

«

If S КJ5 nJ5 12

W

Фи&З

IS

ФпЛ

Л лл

гя р9

72 J4 5 №2

у. f

Ю2

///

no

J7

107

74

Ш ЮЗ

W9

TW

47 48 т т

Ipute

122

IS

4S

2P

т

f2S

fS

76 -

щ

ко

Hf

.

;e$

5

Xfff

raJ

.

nt

-

Kk

fJ8

«J

J«L

т

7ТГ

QJut.fS

Vi/t.fS

| Ассоциативный параллельный процессор | 1973 |

|

SU495664A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Роликовый вращатель | 1987 |

|

SU1540996A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Ассоциативный параллельный процессор | 1973 |

|

SU479114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1981-01-11—Подача