315

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, в которых используется мажоритарное резерви- рование на уровне ячеек памяти.

Цель изобретения - повьппение надежности устройства.

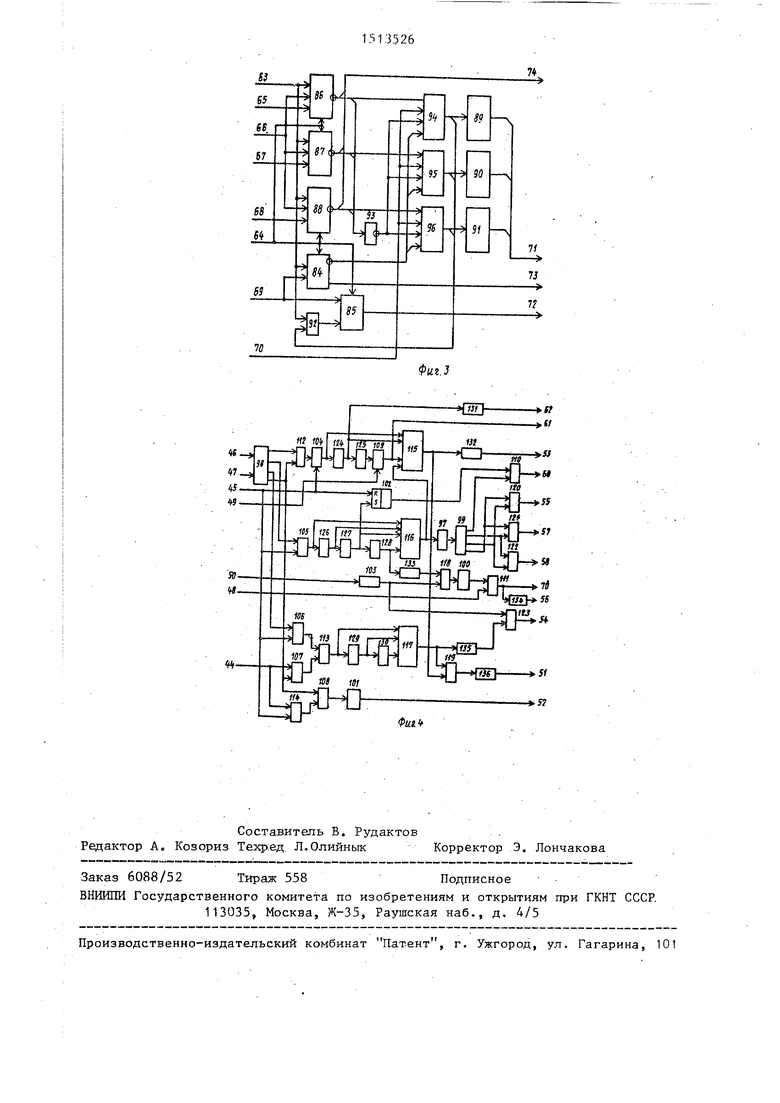

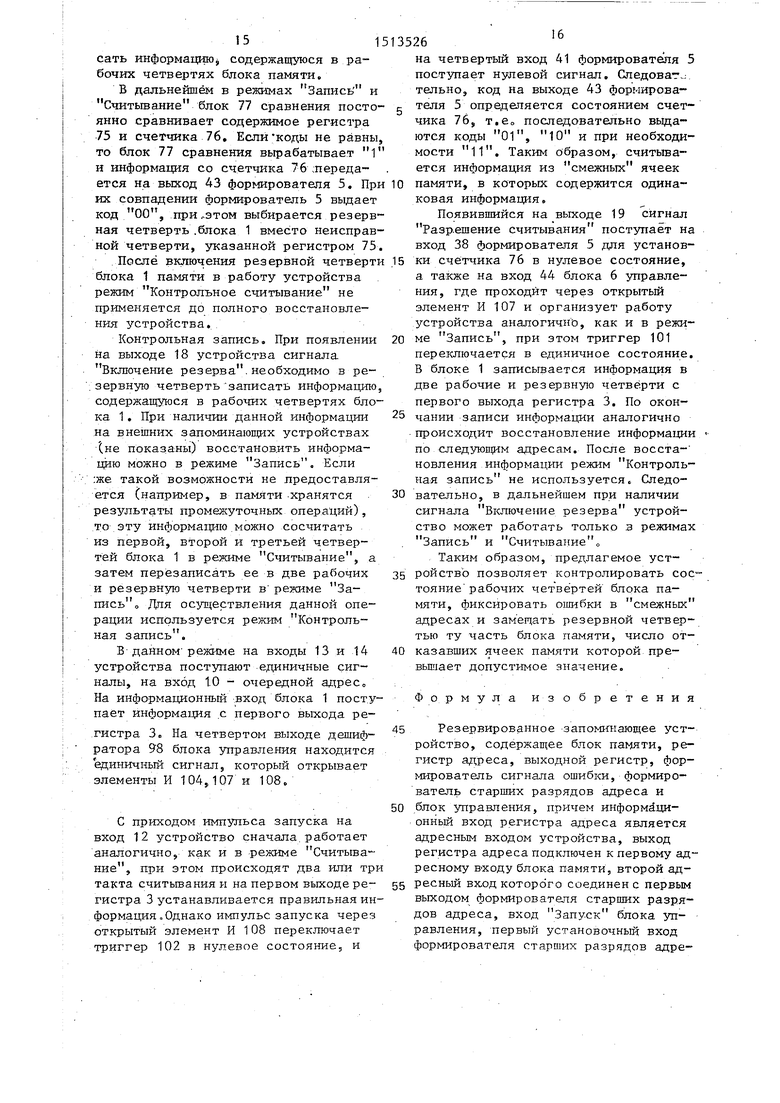

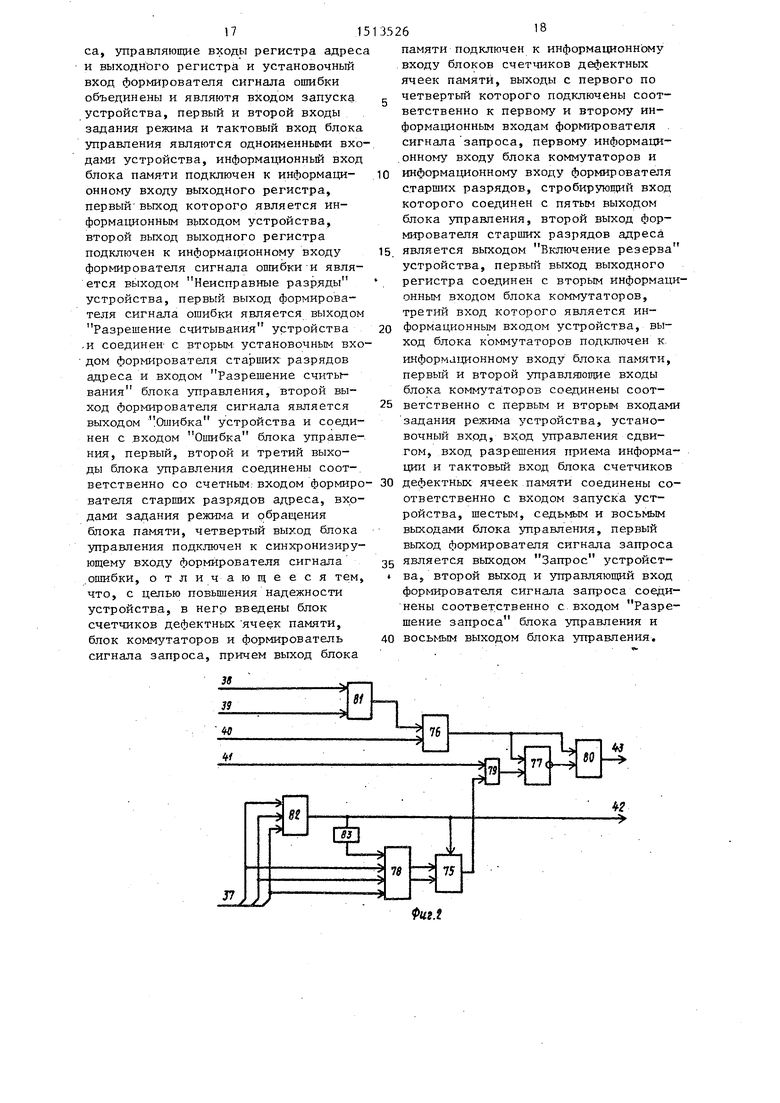

На фиг. 1 представлена структзФ- ная схема предлагаемого устройства; на фиг. 2 - стрзтстурная схема формирователя старших разрядов адреса; на фиг. 3 - структурная схема блока счетчиков дефектных ячеек памяти; на фиг. 4 - структурная схема блока управления о

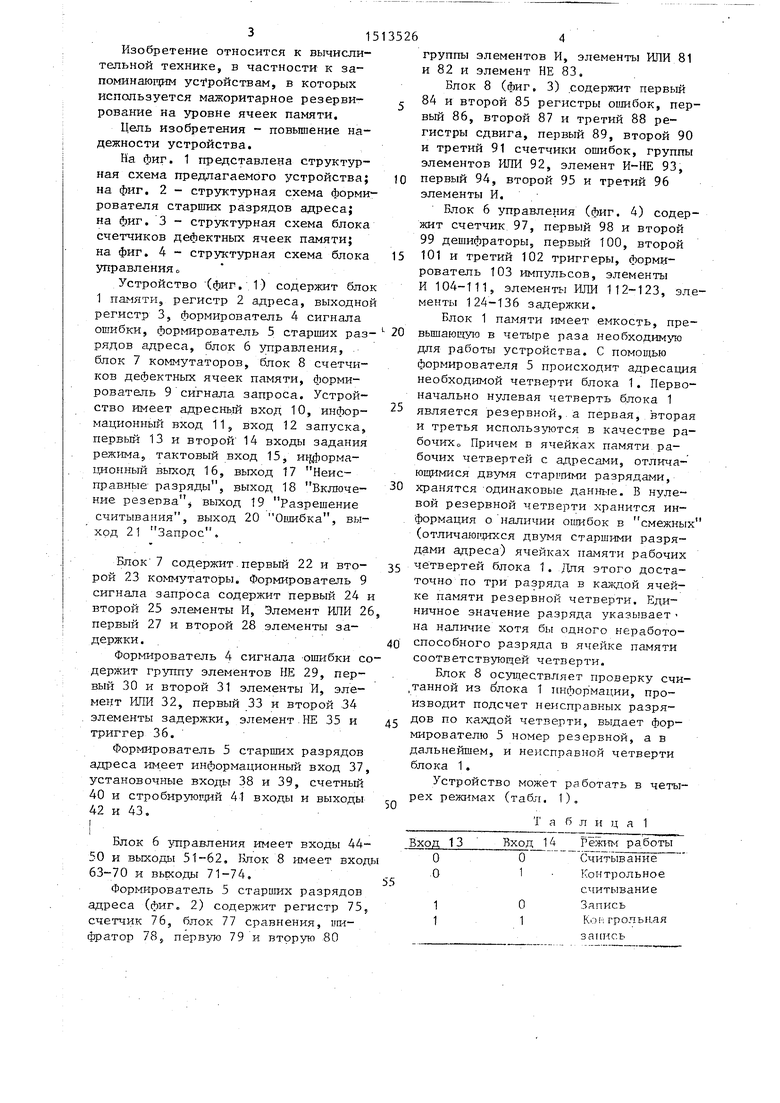

Устройство (фиг..1) содержит блок 1 памяти, регистр 2 адреса, выходной регистр 3, формирователь 4 сигнала ошибки, формирователь 5 старших разрядов адреса, блок 6 управления, . блок 7 коммутаторов, блок 8 счетчиков дефектных ячеек памяти, формирователь 9 сигнала запроса. Устройство имеет адреснь.гй вход 10, информационный вход 11, вход 12 запуска, первый 13 и второй 14 входы задания режима, тактовый вход 15, И1 орма- ционный выход 16, выход 17 Неисправные разряды, выход 18 Включе- ние резерва, выход 19 Разрешение считывания, выход 20 Ошибка, вы- ход 21 Запрос.

Блок 7 содержит.первый 22 и второй 23 коммутаторы. Формирователь 9 сигнала запроса содержит первый 24 и второй 25 элементы И, Элемент ИЛИ 26 первый 27 и второй 28 элементы задержки. ,

Формирователь 4 сигнала -ошибки содержит группу элементов НЕ 29, первый 30 и второй 31 элементы И, элемент ИЛИ 32, первый 33 и второй 34 элементы задержки, элемент НЕ 35 и триггер 36.

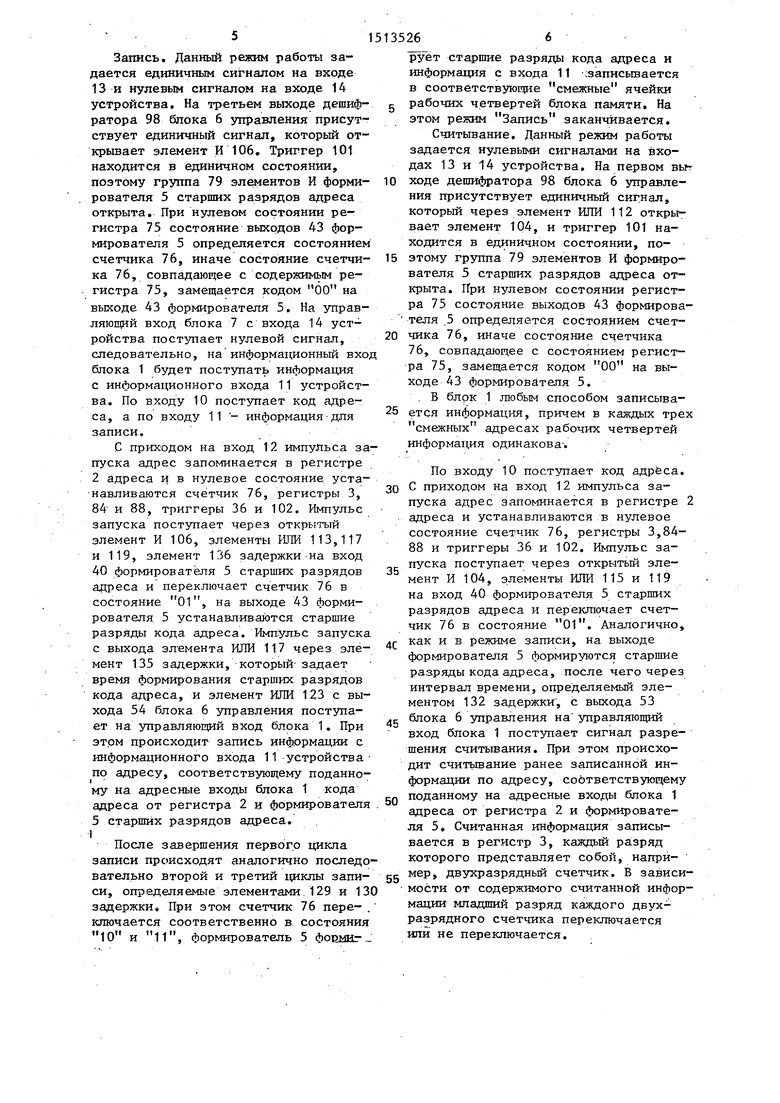

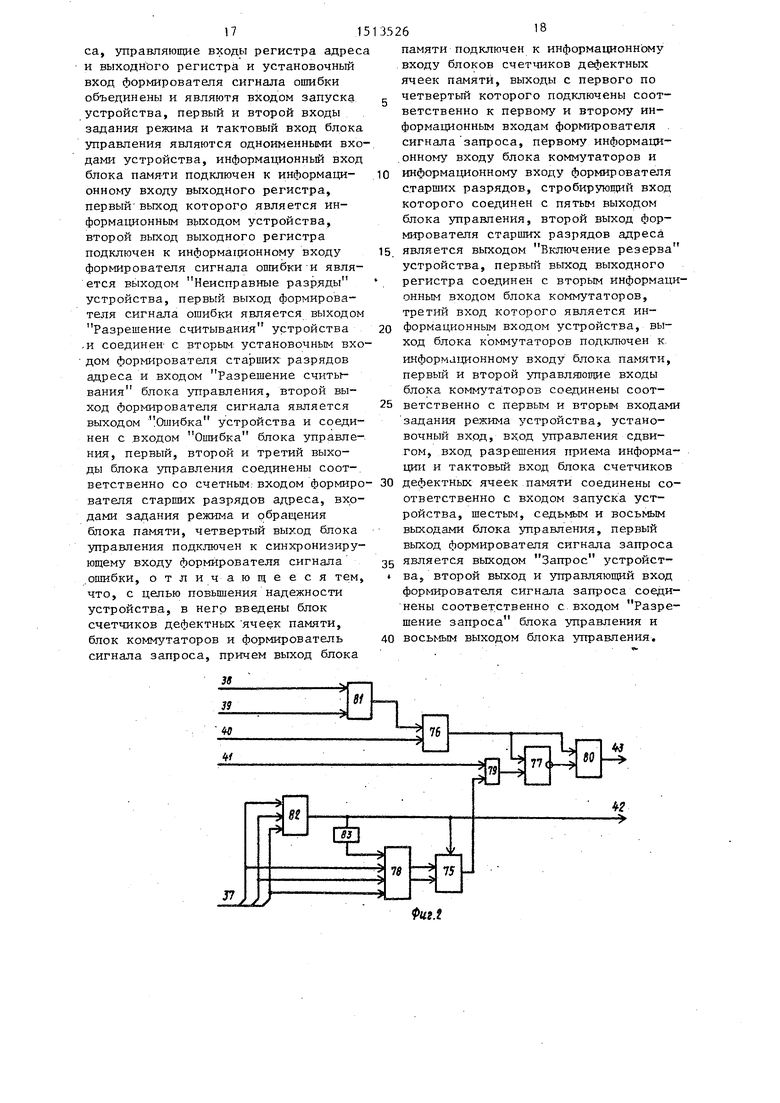

Формирователь 5 старших разрядов адреса имеет информационный вход 37, установочные входы 38 и 39, счетный 40 и стробируюгщй 41 входы и выходы 42 и 43,

Блок 6 управления имеет входы 44- 50 и выходы 51-62. Влок 8 имеет вход

0 5

0

5

5

0

5

0

группы элементов И, элементы ИЛИ 81 и 82 и элемент НЕ 83.

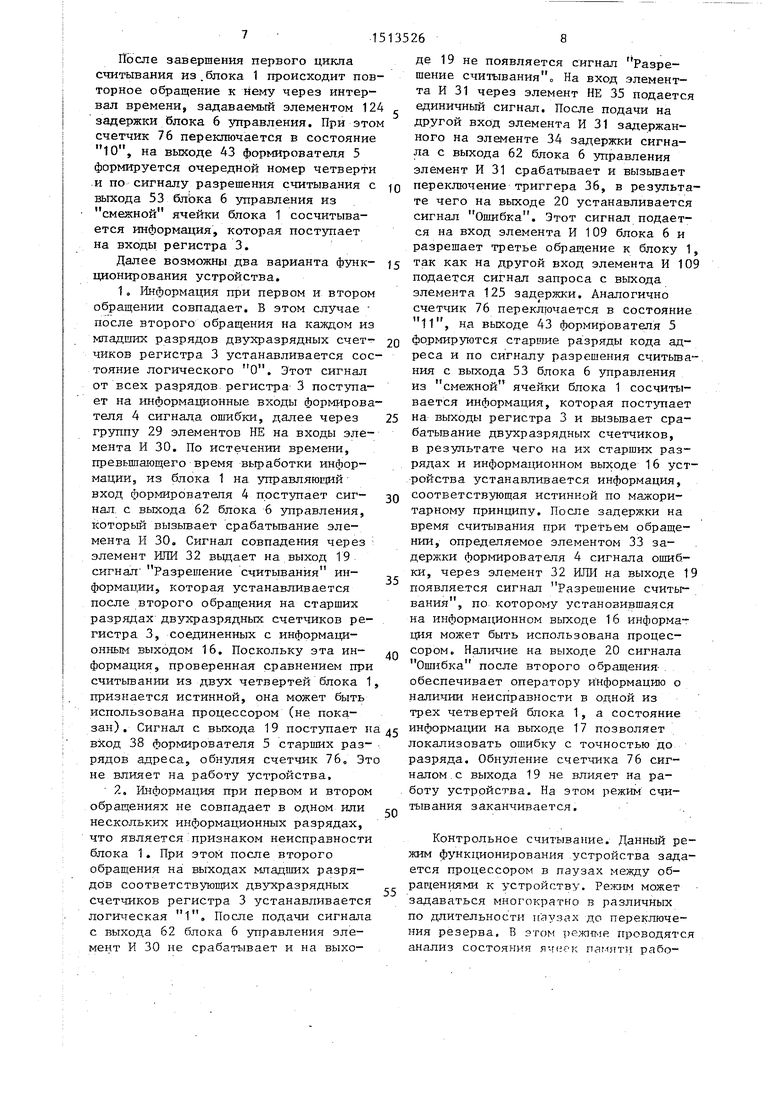

Блок 8 (фиг. 3) содержит первый 84 и второй 85 регистры ошибок, первый 86, второй 87 и третий 88 регистры сдвига, первый 89, второй 90 и третий 91 счетчики ошибок, группы элементов ИЛИ 92, элемент И-НЕ 93, первый 94, второй 95 и третий 96 элементы И.

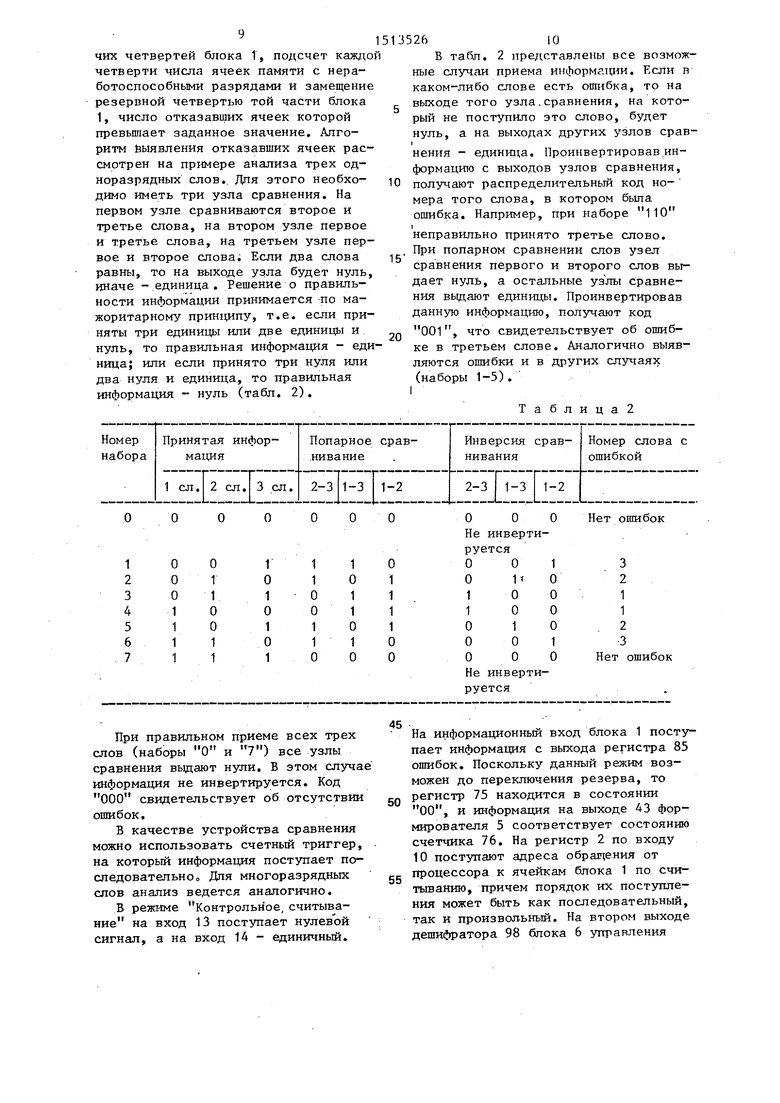

Блок 6 управления (фиг, 4) содержит счетчик 97, первый 98 и второй 99 дешифраторы, первый 100, второй 101 и третий 102 триггеры, формирователь 103 импульсов, элементы И 104-111, элементы ИЛИ 112-123, элементы 124-136 задержки.

Блок 1 памяти имеет емкость, пре- вьш1аюсгу10 в четыре раза необходимую для работы устройства. С помощью формирователя 5 происходит адресация необходимой четверти блока 1. Первоначально нулевая четверть блока 1 является резервной,. а первая, вторая и третья используются в качестве рабочих Причем в ячейках памяти рабочих четвертей с адресами, отлкча- юшдмися двумя старишми разрядами, хранятся одинаковые данга-ге. В нулевой резервной четверти хранится ин- формация о наличии ошибок в смежных (отличшогаихся двумя старшими разрядами адреса) ячейках памяти рабочих четвертей блока 1. Для этого достаточно по три разряда в каж,п;ой ячейке памяти резервной четверти. Единичное значение разряда указывает - на наличие хотя бы одного неработоспособного разряда в ячейке памяти соответствующей четверти.

Блок 8 осзпцествляет проверку считанной из блока 1 пнфор мации, производит подсчет неисправных разрядов по кащюй четверти, выдает формирователю 5 номер резервной, а в дальнейшем, и неисправной четверти блока 1.

Устройство может работать в четырех режимах (табл. 1),

Т а б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Устройство для поиска информации в памяти | 1986 |

|

SU1392579A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, в которых используется мажоритарное резервирование на уровне ячеек памяти. Цель изобретения - повышение надежности устройства. Устройство содержит блок 1 памяти, ячейки которого разделяются на четыре сегмента, регистр 2 адреса, выходной регистр 3, формирователь 4 сигнала ошибки, формирователь 5 старших разрядов адреса, блок 6 управления, блок 7 коммутаторов, блок 8 счетчиков дефектных ячеек памяти, формирователь 9 сигнала запроса. В устройстве контролируется состояние трех рабочих четвертей блока 1 памяти, фиксируются ошибки в "смежных" адресах и замещается резервной четвертью на часть блока 1 памяти, в которой число дефектных ячеек памяти превышает допустимое значение. 4 ил., 2 табл.

63-70 и вькоды 71-74.

Формирователь 5 старших разрядов адреса (фиг. 2) содержит регистр 75, счетчик 76, блок 77 сравнения, им- фратор 78, первую 79 и вторую 80

55

5

Запись. Данный режим работы задается единичным сигналом на входе 13 и нулевым сигналом на входе 14 устройства. На третьем выходе дешифратора 98 блока 6 управления присут ствует единичный сигнал, который открывает элемент И 106, Триггер 101 находится в единичном состоянии, поэтому группа 79 элементов И формирователя 5 старших разрядов адреса открыта. При нулевом состоянии регистра 75 состояние выходов 43 формирователя 5 определяется состояние счетчика 76, иначе состояние счетчика 76, совпадающее с содержимьм регистра 75, замещается кодом 00 на выходе 43 формирователя 5. На управляющий вход блока 7 с входа 14 устройства поступает нулевой сигнал, следовательно, на информационный вх блока 1 будет поступать информация с информационного входа 11 устройства. По входу 10 поступает код адреса, а по входу 11 - информация для записи.

С приходом на вход 12 импульса зпуска адрес запоминается в регистре 2 адреса и в нулевое состояние устанавливаются счетчик 76, регистры 3, 84 и 88, триггеры 36 и 102. Импульс запуска поступает через открытый элемент И 106, элементы ИЛИ 113,117 и 119, элемент 136 задержки на вход 40 формирователя 5 старших разрядов адреса и переключает счетчик 76 в состояние 01, на выходе 43 формирователя 5 устанавпивазотся старшие разряды кода адреса. Импульс запуск с выхода элемента ИЛИ 117 через элемент 135 задержки, который- задает время формирования старших разрядов кода адреса, и элемент ИЛИ 123 с выхода 54 блока 6 управления постзша- ет на управляющий вход блока 1. При этом происходит запись информации с информационного входа 11 устройства по адресу, соответствующему поданному на адресные входы блока 1 кода адреса от регистра 2 и формировател 5 старших разрядов адреса.

I

После завершения первого цикла записи происходят аналогично последовательно второй и третий циклы запи- 55 си, определяемые элементами.129 и 130 задержки. При этом счетчик 76 пере- . кпючается соответственно в состояния 10 и 11, формирователь 5 фосыиг

рует старшие разряды кода адреса и информация с входа 11 ;записьшается в соответствующие смежные ячейки рабочих четвертей блока памяти. На этом режим Запись заканчивается. Считывание. Данный режим работы задается нулевыми сигналами на входах 13 и 14 устройства. На первом выт ходе дешифратора 98 блока 6 управления присутствует единичный сигнал, который через элемент ШШ 112 открывает элемент 104, и триггер 101 находится в единичном состоянии, поэтому группа 79 элементов И формирователя 5 старших разрядов адреса открыта. При нулевом состоянии регистра 75 состояние выходов 43 формирова- теля .5 определяется состоянием счетчика 76, иначе состояние счетчика 76, совпадающее с состоянием регистра 75, замещается кодом 00 на выходе 43 формирователя 5. . В блрк 1 любым способом записывается информация, причем в каждых трех смежных адресах рабочих четвертей информация одинакова-.

0

5

С

5

0

5

По входу 10 поступает код адреса. С приходом на вход 12 импульса запуска адрес запоминается в регистре 2 адреса и устанавливаютсй в нулевое состояние счетчик 76, регистры 3,84- 88 и триггеры 36 и 102. Импульс запуска поступает через открытый элемент И 104, элементы РШИ 115 и 119 на вход 40 формирователя 5 старших разрядов адреса и переключает счетчик 76 в состояние 01. Аналогично, как и в режиме записи, на выходе формирователя 5 формируются старшие разряды кода адреса, после чего через интервал времени, определяемьй элементом 132 задержки, с выхода 53 блока 6 -управления на управляющий вход блока 1 поступает сигнал разрешения считывания. При этом происходит считывание ранее записанной информации по адресу, собтветствутощему поданному на адресные входы блока 1 адреса от регистра 2 и формирователя 5, Считанная информация записывается в регистр 3, каждый разряд которого представляет собой, например, двухразрядный счетчик. В зависимости от содержимого считанной информации младший разряд каждого двухразрядного счетчика переключается или не перекшочается.

После завершения первого цикла считывания из.блока 1 происходит повторное обращение к нему через интервал времени, задаваемый элементом 124 задержки блока 6 управления. При этом счетчик 76 переключается в состояние 10, на выходе 43 формирователя 5 формируется очередной номер четверти и по сигналу разрешения считывания с выхода 53 блЬка 6 управления из смежной ячейки блока 1 сосчитывается информация, которая поступает на входы регистра 3.

Далее возможны два варианта функционирования устройства.

1, Информация при первом и втором обращении совпадает, В этом случае после второго обращения на каждом из младших разрядов двухразрядных счетчиков регистра 3 устанавливается состояние логического О. Этот сигнал от всех разрядов регистра 3 поступает на информационные входы формирователя 4 сигнал.а ошибки, далее через группу 29 элементов НЕ на входы элемента И 30. По истечении времени, превьшхающего время выработки информации, из блока 1 на зтфавляюг ий вход формирователя 4 поступает сигнал с выхода 62 блока 6 управления, который вызьшает срабатьшание элемента И 30. Сигнал совпадения через элемент ИЛИ 32 выдает на выход 19. сигнал Разрешение считывания информации, которая устанавливается после второго обращения на старших разрядах двухразрядных счетчиков регистра 3, соединенных с информационным выходом 16. Поскольку эта информация, проверенная сравнением при считьшании из двух четвертей блока 1, признается истинной, она может быть использована процессором (не пока10

15

20

25

30

35

40

де 19 не появляется сигнал Разрешение считывания о На вход элемент та И 31 через элемент НЕ 35 подает единичный сигнал. После подачи на другой вход элемента И 31 задержан ного на элементе 34 задержки сигна ла с выхода 62 блока 6 управления элемент И 31 срабатывает и вызьшае переключение триггера 36, в резуль те чего на выходе 20 устанавливает сигнал Ошибка. Этот сигнал подае ся на вход элемента И 109 блока 6 разрешает третье обращение к блоку так как на другой вход элемента И подается сигнал запроса с выхода элемента 125 задержки. Аналогично счетчик 76 переключается в состоян 11, на выходе 43 формирователя 5 формирзтотся старшие разряды кода а реса и по сигналу разрешения счить ния с выхода 53 блока 6 управления из смежной ячейки блока 1 сосчит вается информация, которая на выходы регистра 3 и вызьгоает ср батывание двухразрядных счетчиков, в результате чего на их старших ра рядах и информационном выходе 16 у ройства устанавливается информация соответствующая истинной по мажори тарному принципу. После задержки н время считывания при третьем обращ нии, определяемое элементом 33 задержки формирователя 4 сигнала оши ки, через элемент 32 ИЛИ на выходе появляется сигнал Разрешение счит вания, по которому установившаяся на информационном выходе 16 информ ция Может быть использована процес сором. Наличие на выходе 20 сигнал Ошибка после второго обращения- обеспечивает оператору информацию наличии неисправности в одной из трех четвертей бпока 1, а состояни

зан), Сигнал с выхода 19 поступает а 45 информации на выходе 17 позволяет

вход 38 формирователя 5 старших раз- - рядов адреса, обнуляя счетчик 76, Это не влияет на работу устройства.

2, Информация при первом и втором обращениях не совпадает в одном или нескольких информационных разрядах, что является признаком неисправности блока 1. При этом после второго обращения на выходах младших разрядов соответствз/ющих двухразрядных счетчиков регистра 3 устанавливается логи1теская 1. После подачи сигнала с выхода 62 блока 6 управления элемент И 30 не срабатывает и на выхо-

50

55

локализовать ошибку с точностью до разряда. Обнуление счетчика 76 сиг налом .с выхода 19 не влияет на работу устройства. На этом режим счи тывания заканчивается.

Контрольное считывание. Данный жим функционирования .устройства за ется процессором в паузах между об ращениями к устройству. Режим може задаваться многократно в различных по длительности паузах до переключ ния резерва, В этом рело-гме проводя анализ состояния ячеек паг-иттн рабо

0

5

0

5

0

5

0

де 19 не появляется сигнал Разрешение считывания о На вход элемент- та И 31 через элемент НЕ 35 подается единичный сигнал. После подачи на другой вход элемента И 31 задержанного на элементе 34 задержки сигнала с выхода 62 блока 6 управления элемент И 31 срабатывает и вызьшает переключение триггера 36, в результате чего на выходе 20 устанавливается сигнал Ошибка. Этот сигнал подается на вход элемента И 109 блока 6 и разрешает третье обращение к блоку 1, так как на другой вход элемента И 109 подается сигнал запроса с выхода элемента 125 задержки. Аналогично счетчик 76 переключается в состояние 11, на выходе 43 формирователя 5 формирзтотся старшие разряды кода адреса и по сигналу разрешения считьта- ния с выхода 53 блока 6 управления из смежной ячейки блока 1 сосчитывается информация, которая на выходы регистра 3 и вызьгоает срабатывание двухразрядных счетчиков, в результате чего на их старших разрядах и информационном выходе 16 устройства устанавливается информация, соответствующая истинной по мажоритарному принципу. После задержки на время считывания при третьем обращении, определяемое элементом 33 задержки формирователя 4 сигнала ошибки, через элемент 32 ИЛИ на выходе 19 появляется сигнал Разрешение считывания, по которому установившаяся на информационном выходе 16 информация Может быть использована процессором. Наличие на выходе 20 сигнала Ошибка после второго обращения- обеспечивает оператору информацию о наличии неисправности в одной из трех четвертей бпока 1, а состояние

информации на выходе 17 позволяет

локализовать ошибку с точностью до разряда. Обнуление счетчика 76 сигналом .с выхода 19 не влияет на работу устройства. На этом режим считывания заканчивается.

Контрольное считывание. Данный режим функционирования .устройства задается процессором в паузах между обращениями к устройству. Режим может задаваться многократно в различных по длительности паузах до переключения резерва, В этом рело-гме проводятся анализ состояния ячеек паг-иттн рабочих четвертей блока Т, подсчет каждо четверти числа ячеек памяти с неработоспособными разрядами и замещение резервной четвертью той части блока 1, число отказавших ячеек которой превьшшет заданное значение. Апго- ритм Ёыявления отказавших ячеек рассмотрен на примере анализа трех одноразрядных слов.. Дпя этого необходимо иметь три узла сравнения. На первом узле сравниваются второе и третье слова, на втором узле первое и третье слова, на третьем узле первое и второе слова; Если два слова равны, то на выходе узла будет нуль, иначе -единица. Решение о правильности информации принимается по мажоритарному пришщпу, т.е. если приняты три единицы или дв е единицы и нуль, то правильная информация - единица; или если принято три нуля или два нуля и единица, то правильная информация - нуль (табл. 2).

При правильном приеме всех трех слов (наборы О и 7) все узлы сравнения вьщают нули. В этом случа информация не инвертируется. Код 000 свидетельствует об отсутствии ошибок.

В качестве устройства сравнения можно использовать счетный триггер, на который информация поступает последовательно Дпя многоразрядных слов анализ ведется аналогично.

В режиме Контрольное, считывание на вход 13 поступает нулевой сигнал, а на вход 14 - единичный.

1352610

В табл. 2 представлены все возможные случаи приема инфopмг лц и. Если в каком-либо слове есть ошибка, то на выходе того узла.сравнения, на который не поступило это слово, будет

нуль, а на выходах других узлов сравI

нения - единица. Проинвертировав информацию с выходов узлов сравнения, 0 получают распределительный код но- мера того слова, в котором бьша

ошибка. Например, при наборе 110

I

неправильно принято третье слово.

При попарном сравнении слов узел сравнения первого и второго слов выдает нуль, а остальные уз лы Сравнения выдают единицы. Проинвертировав данную информацию, получают код 001, что свидетельствует об ошибке в третьем слове. Аналогично выявляются ошибки и в других случаях (наборы 1-5).

15

0

I

Таблица2

Не инвертируется

На информационный вход блока 1 поступает информация с выхода регистра 85 ошибок. Поскольку данный режим возможен до переключения резерва, то регистр 75 находится в состоянии 00, и информация на выходе 43 формирователя 5 соответствует состоянию счетчика 76. На регистр 2 по входу 10 поступают адреса обралцения от процессора к ячейкам блока 1 по счи- тьгоанию, причем порядок их поступления может быть как последовательный, так и произвольный. На втором выходе дешифратора 98 блока 6 управления

111513526

присутствует единичный сигнал, прч

этому открыт элемент И 105, Счетчик 97 и триггер 1-00 находятся в нулевом состоянии,

С приходом импульса запуска на вход 12 устройства в регистр 2 записывается адрес обращения, устанавливаются счетчик 76, регистры 3, 84-88 и триггеры 36 и 102. Импульс запуска через открытый элемент И 105, элемент РШИ 116 поступает на вход счетчика 97 и переключает его в состояние 01. На втором выходе дешифратора 99 находится сигнал логической 1, который поступает на один из входов элементов ИЛИ 121 и 122. Следовательно, на выходах 57 и 58 присутствуют единичные сигналы, которые разрешают запись информации соответственно в регистры 87 и 88 сдвига. С выхода элемента ИЛИ 116 импульс запуска поступает на вход элемента ИЛИ 115, Аналогично, как и в режиме Считывание, происходит считывание информации, при этом формирователь 5 выдает код 01.

Считанное из первой рабочей четверти блока 1 слово записьшается в регистры 87 и 88, так как в них разрешается запись.

Через некоторое время, определяе-с мое элементом 126 задержки, происходит повторное считывание информации. При этом счетчик 97„ переключается в состояние 10, на выходах 55 и 58 присутствуют единичные сигналы, формирователь 5 формирует код 10, и слово, считанное из второй рабочей четверти блока 1, поступает на счетные входы регистров 86 и 88 сдвига, в которые разрешена запись.

Аналогично происходит третье обращение к блоку 1 через время, определяемое элементом 127 задержки. При этом счетчик 97 переключается в состояние 11, на выходах 55 и 57. присутствуют единичные сигналы, формирователь 5 формирует код 11, и слово, считанное из третьей рабочей четверти блока 1, постзшает на счетные входы регистров 86 и 88. С выхода элемента 127 задержки импульс запуска постзшает на второй управляющий вход триггера 102, переключает его в единичное состояние, открьгоая элемент И 110.

Через некоторое время, определя- элементом 128 задержки, проис12

ходит четвертое .ооращение к блоку 1. При этом счетчик 97 перекшочается в состояние 00, на выходе 60 присут- ствует единичный сигнал, формирователь 5 формирует код 00, и слово, считанное из резервной четверти блока 1, записывается в регистр 84, и через группу 92 элементов ИЛИ в ре

гистр 85. Единица на выходе 60 блока 6 управления хранится до тех пор, пока не обнулится триггер 102 очередным импульсом запуска.

Следовательно, в регистре 86 сдвига поразрядно сравнивается информация при втором и третьем считывании, |В регистре 87 сдвига при первом и третьем считывании, в регистре 88 сдвига - при первом и втором считы вании. В регистры 84 и 85 ошибок заносится информация об оп ибках.

После записи в регистры 84 и 85 информации, определяемой элементом 133 задержки, импульс запуска через

элемент ИЛИ 118 поступает на вход триггера 100 и переключает его в единичное состояние. При этом открывается элемент И 111 и тактовые импульсы с входа 15 устройства поступают на выход 70 блока 6 управления. Элемент 133 за.держки должен быть выбран так, чтобы элемент И 111 открывался в момент паузы между двумя соседними тактовыми импульсами.

. Мпадшие разряды регистров 86-88 сдвига поступают на соответствующие входы элементов И 94-96 и на входы элемента И-НЕ 98.

Из табл. 2 следует, что после по-

парного сравнения слов информация инвертируется, кроме наборов О и 7. В устройстве информация с регистров 86-i88 считывается с инверсных выходов. При коде 111 элемент И-НЕ 98

.вырабатывает нуль и закрьщает элементы И 94-96, На выходе элементов И 94- 96 получается код 000, т.е. информация не инвертируется. При любом другом коде на выходе регистров 86-88

сдвига элемент И-НЕ 98 вырабатывает 1, и информация через элементы И 94-96 проходит без изменений.

Информация, которая снимается с инверсных выходов регистра 84 ошибок,

поступает на четвертые; входы соответствующих элементов И 94-96, наличие О на любом инверсном выходе регистра 84 свидетельствует о том, что в соответствующей четверти блока 1 по

ны ошибки, которые уже учтены в соответствующем счетчике 89,90 или 91 ошибок и повторно их учитывать не на- g до. Поэтому О с инверсного выхода регистра 84 закрывает соответствующий элемент И 94, 95 или 96, Единида с инверсного выхода регистра 84 разрешает прохождение информации об ошиб-10 ках через соответствующий элемент И 94,95 или 96. Прохождение информации через элементы И 94-96 разрешается по тактовому импульсу с входа 70

сных выходах регистров 86-88 сдвига свидетельствует о том, что в дальнейшем элемент И-НЕ 98 будет закрывать элементы И 94-96, и счетчики 89-91 не изменяет своего состояния, Поэтому можно закончить контроль блока 1 по данному адресу. Элемент И 24 выдает 1, С переключением сигнала на входе 50 блока 6 управления из нулевого состояния в единичное формирователь 103 импульса вырабатывает одиночньй

импульс, которьш через элемент блока 8, который поступает на вторые 15 ИЛИ 118 поступает на счетный вход

триггера 100 и переключает его в нулевое состояние, которое запрещает вьщачу тактовых импульсов на выход 70, а также через элемент ИЛИ 123 20 поступает на выход 34, после чего прибавляет единицу к содержимому со- осуществляется запись содержимого ответствующего счетчика 89,90 или 91 регистра 85 через блок 7 в резервную ошибок. При появлении первой едини- четверть блока 1, так как формиро- цы на каждом выходе элементов И 94-96 ватель.5 выдает код 00 на выходе рна записывается через группу 92 эле, 25 43, По окончании записи информации ментов ИЛИ в соответствующий разряд i

входы элементов И 94-96с

Таким образом, на выходе элементов И 94-96 находится либо код 000, либо на одном из выходов 1, которая

в резервную четверть блока .1 на выходе 21 устройства появляется сигнал Запрос, который оповещает процессор о том, что устройство готово при- 30 нять следующий адрес в регистр 2 и обработать запрос в одном из режимовс В дальнейшем при обращении в ре- Контрольное считывание по

регистра 85 ошибок. Запись в регистр 85 разрешена, так как выход 60 блока 6 управления находится в единичном состоянии.

После анализа младших разрядов регистров 86-88, определяемого элементом 134 задержки по тактовому

в резервную четверть блока .1 на выходе 21 устройства появляется сигнал Запрос, который оповещает процессор о том, что устройство готово при- 30 нять следующий адрес в регистр 2 и обработать запрос в одном из режимовс В дальнейшем при обращении в ре- Контрольное считывание по

жиме

этому же адресу используется инфор- сигналу,.-поступающему на вход 66 бло- 35 .Ц резервной четверти блока 1, ка 8, происходит сдвиг содержимого

Счетчики 89-91 проводят подсчет

ошибок, обнаруженных в трех рабочих

четвертях блока 1, При достижении карегистров 86-88 в сторону младшего разряда. После этого осуществляется анализ очередной группы младших разрядов регистров 86-88 сдвига по так- 40 ким-либо счетчиком определенного

товому импульсу с выхода 70 блока 6 управления.

Для повышения производительности устройства используется формирователь 9 сигнала запроса. По окончании переключения триггера 100 в единичное состояние единичный сигнал с . выхода 60 блока 6 управления, задержанный на элементе 27 задержки, поступает на первые входы элементов И 24 и 25, При наличии кода 111 на прямых выходах регистра 84 ошибок отсутствует необходимость анализи- ровать информацию об ошибках, так ка во всех трех рабочих четвертях блока 1 ранее в режиме Контрольное считывание уже обнарз жены ошибки, , и они учтены в счетчиках 89-91. В этом элемент И 25 вьздаат 1,

сных выходах регистров 86-88 сдвига свидетельствует о том, что в дальнейшем элемент И-НЕ 98 будет закрывать элементы И 94-96, и счетчики 89-91 не изменяет своего состояния, Поэтому можно закончить контроль блока 1 по данному адресу. Элемент И 24 выдает 1, С переключением сигнала на входе 50 блока 6 управления из нулевого состояния в единичное формирователь 103 импульса вырабатывает одиночньй

триггера 100 и переключает его в нулевое состояние, которое запрещает вьщачу тактовых импульсов на выход 70, а также через элемент ИЛИ 123 поступает на выход 34, после чего осуществляется запись содержимого регистра 85 через блок 7 в резервную четверть блока 1, так как формиро- ватель.5 выдает код 00 на выходе 43, По окончании записи информации

в резервную четверть блока .1 на выходе 21 устройства появляется сигнал Запрос, который оповещает процессор о том, что устройство готово при- нять следующий адрес в регистр 2 и обработать запрос в одном из режимовс В дальнейшем при обращении в ре- Контрольное считывание по

жиме

уровня этот счетчик вьфабатывает единичный сигнал. Следовательно, на вы- ходе 71 блока 8 находится либо код 000, либо в одном из разрядов при45- сутствует единичный сигнал. При наличии на входе 37 формирователя 5 кода, отличного от 000, элемент 82 IfflH вьщает единичный сигнал, который открывает регистр 75, На входе шифра50 тора 78 присутствует распределительный код номера неисправной четверти блока 1, который после шифрации записывается в регистр 75, Выход элемента ИЛИ 82 подключен к выходу 18

55 устройства и является сигналом Включение резерва, который сообщает процессору о том, что в работу устройства включена резервная четверть блока памяти, в которую необходимо запи-

151513526

сать информацию содержащуюся в ра- на четвертый вход 41 формироватапя 5

бочих четвертях блока памяти.

В дальнейшем в режимах Запись и

поступает нулевой сигнал, Следоваг.; тельно, код на выходе 43 формирователя 5 определяется состоянием счетчика 76, т.е последовательно вьща- ютея коды 01, 10 и при необходимости 11. Таким образом, считьгеается информация из смежных ячеек

Считьшание блок 77 сравнения посто- g янно сравнивает содержимое регистра 75 и счетчика 76, Если коды не равны, то блок 77 сравнения вырабатывает 1 и информация со счетчика 76 передается на выход 43 формирователя 5. При 10 памяти, в которых содержится одина- их совпадении формирователь 5 выдает кован информация

код 00, при .этом выбирается резерв- Появившийся на выходе 19 сигнал ная четверть .блока 1 вместо неисправ- Разрешение считывания поступает на ной четверти, заказанной регистром 75. вход 38 формирователя 5 для установ- Послё включения резервной четверти .15 ки счетчика 76 в нулевое состояние.

блока 1 памяти в работу устройства режим Контрольное считывание не применяется до полного восстановления устройства..

Контрольная запись. При появлении на выходе 18 устройства сигнала Включение резерва.необходимо в ре- .нервную четверть записать информацию содержащуюся в рабочих четвертях блока 1. При наличии данной информации на внешних запоминающих устройствах (не показаны) восстановить информа- цяю можно в режиме Запись. Если :же такой возможности не предоставляется (например, в памяти -хранятся результаты промежуточных операций), то.эту информацию.можно сосчитать из первой, второй и третьей четвертей блока 1 в режиме Считывание, а затем перезаписать ее в две рабочих и резервную четверти в режиме Запись Для осуществления данной операции используется режим Контрольная запись.

Б-данном режиме на входы 13 и 14 устройства поступают единичные сигналы, на вход 1.0 - очередной адрес На информационный .вход блока 1 поступает информа1.1я .с первого выхода ре.гистра 3. На четвертом выходе дешифратора 98 блока управления находится единичный сигнал, который открывает элементы И 104,107 и 108.

С приходом импульса запуска на вход 12 устройство сначала, работает аналогично, как и в режиме Считывание, при этом происходят два или три

такта считьгоания и на первом выходе ре- 55ресный вход которого соединен с первым

гистра 3 устанавливается правильная ин-выходом формирователя старших разряформация.Однако импульс запуска черездов адреса, вход Запуск блока употкрытый элемент И 108 переключаетравления, первый установочный вход

триггер 102 в нулевое состояние, иформирователя старших разрядов адрепоступает нулевой сигнал, Следоваг.; тельно, код на выходе 43 формирователя 5 определяется состоянием счетчика 76, т.е последовательно вьща- ютея коды 01, 10 и при необходимости 11. Таким образом, считьгеается информация из смежных ячеек

памяти, в которых содержится одина- кован информация

а также на вход 44 блока 6 управления, где проходит через открытый элемент И 107 и организует работу устройства аналогично, как и в режиме Запись, при этом триггер 101 переключается в единичное состояние. В блоке 1 записывается информация в две рабочие и резервну1о четверти с первого выхода регистра 3. По окончании: записи информации аналогично происходит восстановление информации по следующим адресам. После восста- новления информации режим Контрольная запись не используется. Следовательно, в дальнейшем при наличии сигнала Включение резерва устройство может работать только з режимах Запись и Считывание о

Таким образом, предлагемое устройствЬ позволяет контролировать состояние рабочих чет вёртей блока памяти, фиксировать О1.шбки в смежных адресах и замещать резервной четвертью ту часть блока памяти, число отказавших ячеек памяти которой пре- вьшает допустимое значение.

Формула изобретения

Резервированное запомршающее устройство, содержащее блок памяти, регистр адреса, выходной регистру, формирователь сигнала ошибки, формирователь старших разрядов адреса и

блок управления, причем информйци- онный вход регистра адреса является адресным входом устройства, выход регистра адреса подключен к первому яд- ресному входу блока памяти, второй ад17

са, управляющие входы регистра адрес и выходн ого регистра и установочный вход формирователя сигнала ошибки объединены и являютя входом запуска устройства, первый и второй входы задания режима и тактовый вход блока управления являются одноименными входами устройства, информационньм вход блока памяти подключен к информационному входу выходного регистра, первый выход которого является информационным вькодом устройства, второй выход выходного регистра подключен к информагщонному входу формирователя сигнала ошибки И является выходом Неисправные разряды устройства, первый выход формирователя сигнала ошибки является выходом Разрешение считывания устройства ,и соединен- с вторым, установочным вхо дом формирователя старших разрядов адреса и входом Разрешение счить - вания блока управления, второй выход формирователя сигнала является выходом Ошибка устройства и соединен с входом Ошибка блока управления, первый, второй и третий выходы блока управления соединены соответственно со счетным, входом формирователя старших разрядов адреса, входами задания режима и обращения блока памяти, четвертый выход блока управления подключен к синхронизирующему входу формирователя сигнала ошибки, отличающееся тем что, с целью повьш1ения надежности устройства, в негр введены блок счетчиков дефектных ячеек памяти, блок коммутаторов и формирователь сигнала запроса, причем выход блока

13526

памяти подключен к информационному входу блоков счетчиков дефектных ячеек памяти, выходы с первого по четвертый которого подключены соответственно к первому и второму информационным входам формирователя сигнала запроса, первому информационному входу блока коммутаторов и

10 информационному входу формирователя старших разрядов, стробирующий вход которого соединен с пятым выходом блока управления, второй выход формирователя старших разрядов адреса

15 является выходом Включение резерва

устройства, первьй выход выходного регистра соединен с вторым информационным входом блока коммутаторов, третий вход которого является ин20 формационным входом устройства, выход блока коммутаторов подключен к. информационному входу блока памяти, первый и второй управляющие входы блока коммута;торов соединены соот25 ветственно с первым и вторым входами задания режима устройства, установочный вход вход управления сдвигом, вход разрешения приема информации и тактовый вход блока счетчиков - 30 дефектных ячеек памяти соединены соответственно с входом запуска устройства, шестым, седьмым и восьмым выходами блока управления, первый выход формирователя сигнала запроса

35 является выходом Запрос устройст- ва, второй выход и управляющий вход формирователя сигнала запроса соединены соответственно с входом Разрешение запроса блока управления и

40 восьмым выходом блока управления.

Фпi

| Электроника, 1978, № 21, с | |||

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1989-10-07—Публикация

1987-08-18—Подача