Предложена система модулей струйной техники, предназначенная для построения приборов и устройств контроля, отличающаяся тем, что с целью согласования характеристик элементов в модулях и самих модулей и введения их в нужный режим в системе использованы дроссели, образованные сужением соответствующих участков коммуникационных каналов или изменением их глубин, а также элементы одного функционального значения различной глубины и проходного сечения.

Для выполнения операции двоичного вычитания в системе применен модуль, в котором комбинированный логический элемент с двумя входами - уменьшаемого и вычитаемого - и тремя выходами, выполняющими операции отрицания импликации, конъюнкции и отрицания обратной импликации, соединен выходами, выполняющими операции отрицания импликации и отрицания обратной импликации, с двумя входами усилителя, выполняющего операцию дизъюнкции, а выход комбинированного логического элемента, выполняющий операцию конъюнкции, соединен с атмосферой. Выход усилителя, -выполняющего операцию дизъюнкции, соединен с одним из входов второго комбинированного логического элемента, вторым входом -которого служит сигнал переноса из предыдущего разряда. Выход конъюнкции соединен с атмосферой, а выходы отрицания

импликации и отрицания обратной импликации соединены с двумя входами второго усилителя, выполняющего операцию дизъюнкции, выход которого служит выходом разности, полученной в данном разряде. От выхода отрицания обратной импликации обоих комбинированных логических элементов сделаны ответвления, соединяемые двумя входами трегьего элемента, выполняющего операцию дизъюнкции, выход которого служит -выходом переноса в последующем разряде, причем для формирования входных сигналов к трем внешним входам обоих комбинированных элементов своими выходами, выполняющими операцию повторения, подсоединены три релейных усилителя с одпим входом у каждого усилителя.

Для выполнения операции сравнения двух л-разрядных двоичных чисел в системе применен модуль ячейки сравнения, выполняющий операцию сравнения двух двухразрядных чисел, на которые последовательно разделены сравниваемые л-разрядные числа. В модуле старшие разряды двух сравниваемых двухразрядных чисел подключены на входы комбинированного логического элемента, у которого выход, выполняющий операцию конъюнкции, соединяется с атмосферой, а выходы, выполняющие операции отрицания импликации и отвхода:ми соответственно -первого и .второго релейных усилителей. В этих усилителях выходы, выполняющие операцию повторения, соединены с одним из входов соответственно первого и Второго усилителей с двумя входами, выполняющих операцию дизъюнкции, а выходы, -выполняющие операцию инвертирования, соединены с одним из двух входов соответственно второго и первого элементов, выполняющих операцию конъюнкции, вторыми входами которых служат младшие разряды сравниваемых двухразрядных чисел, а выходы соединены со вторыми входами соответственно второго и первого усилителя с двумя входами, выходы которых, осущетвляющие операцию дизъюнкции входов, служат выходами модуля.

С целью выполнения операции округления двоичного числа, а также операции перевода из обратного в дополнительный код, применен двухразрядный модуль последовательного сумматора, в котором выходы первого комбинированного логического элемента, выполняющие операции отрицания импликации и отрицания обратной импликации, соединены со входами усилителя, выполняющего операцию дизъюнкции, выход которого служит выходом младшего разряда. Выход комбинированного элемента, выполняющий операцию конъюнкции, соединен одновременно с обоими входами второго усилителя с двумя входами, выполняющего операцию повторения. Выход второго усилителя соединен с одним из входов второго комбинированного элемента, второй вход которого служит внешним, а выходы, выполняющие операции отрицания .импликации и отрицания обратной импликации, соединены с обоими входами третьего усилителя с двумя входами, осуществляющего операцию, дизъюнкции, выхОд которого служит выходам старшего разряда.

Выход второго комбинированного логического элемента, осуществляющий операцию конъюнкции, соединен одновременно с обоими входами четвертого усилителя с двумя входами, выполняющего операцию повторения. Выход четвертого усилителя служит выходом переноса в следующий разряд, а на три внешних входа комбинированных логических элементов для формирования входных сигналов подсоединены релейные усилители с одним входом.

Для выполнения операции перевода из дополнительного кода в обратный, а также осуществления реверсивного двоичного счета с записью по различным адресам в системе применен двухразрядный модуль последовательного вычитателя, в котором выходы первого комбинированного логического элемента, выполняющие операции отрицания импликации и отрицания обратной импликации, соединены со входами усилителя, выполняющего операцию дизъюнкции. Выход усилителя служит выходом младщего разряда, а выход комбинирова.нного элемента, выполняющий Операцию конъюнкции, соединен с атмосферой, причем

от выхода комбинированного элемента, выполняющего операцию отрицания импликации, сделано ответвление, подсоединенное ко входу релейного усилителя. Выход релейного усилителя, выполняющий операцию повторения, соединен с одним из входов второго комбинированного элемента, второй вход которого служит внешним. Выход, выполняющий операцию конъюнкции, соединен- с атмосферой, а выходы, выполняющие операции отрицания импликации и отрицания обратной импликации,соединены со входами усилителя с двумя входами, выполняющего операцию дизъюнкции, выход которого служит выходом старшего разряда. От выхода второго комбинированного элемента, выполняющего операцию отрицания обратной импликации, сделано ответвление, подаваемое на вход релейного усилителя, выход которого, выполняющий операцию повто0 рения, служит выходом переноса в следующий разряд, а три внешних входа комбинированных струйных логических элементов соединены с релейными усилителями с одним входОМ. Для выполнения операции записи и хранения одного разряда двоичного числа и построения матричных запоминающих устройств, не нуждающихся в схемах регенерации информации при считывании, устройств со многими устойчивыми состояниями, обегающих устройств и других в системе применен модуль элементарной ячейки памяти, в котором выход комбинированного логического элемента, выходы которого служат для подачи записываемого числа и команды на запись, выполняющий операцию конъюнкции, соединен с записывающим входом элемента памяти. Выход комбинированного логического элемента, ВЫПОЛНЯЮЩИЙ операцию отрицания импликации, соединен со стирающим входом элемента

0 памяти, а третий выход комбинированного логического элемента соединен с атмосферой; или выход KOMi6HHHpOBaHHoro логического элемента, выполняющий операцию конъюнкции, соединен с записывающим входом элемента

5 памяти, а два остальных выхода соединены с атмосферой, причем выход элемента памяти, выполняющий операцию инвертирования запоминающего сигнала, служит выходом модуля.

0 С целью Выполнения операции записи, хранения и выдачи одного разряда двоичного числа и построения статических сдвигающих и запоминающих регистров применен модуль ячейки регистра памяти, в котором входной

5 Сигнал команды на запись поступает на вход первого усилительного элемента с одним входом, инверсный выход которого соединен с одним из входов первого комбинированнОго логического элемента, второй вход служит для

Подачи числового сигнала. Выход первого комбинированного логического элемента, выполняющий операцию конъюкции, соединен со стирающим входом первого элемента памяти, выход первого комбинированного логического

импликации, соединен с записывающим входом первого элемента иамяти, выход которого, выполняющий онерацию инвертирования запоминаемого сигнала, соединен с одним из входов второго логического элемента, второй вход соединен с выходом нервого усилительного элемента, выполняющим операцию повторения. Выход второго комбинированного логического элемента, выполняющий операцию конъюнкции, соединен со стирающим входом второго элемента намяти, а выход второго комбинированного логического элемента, выполняющий онерацию отрицаиия импликации, соединен с занисывающим входом второго элс:лс11га памятн, выход которого, выполняющий операцию инвертироваиия заноминаемого сигнала, служит выходом модуля. Выходы обоих комбинированных логических элементов, выполняющие операции отрицания обратной импликации, соединены с атмосферой, на числовой вход первого комбинироваиного элемента для формироваиия сигнала подключен релейный усилитель с одиим входом, а на выход модуля - релейный усилитель с одним входом.

Для построения различных счетных цифровых и логических схем применен модуль триггера со счетным входом, в котором для подачи входного сигнала служит вход первого релейного усилителя, иа выходе которого, выполняющем онерацню повторения входного снгнала, включено дросселирующее сопротивление, а вь1ход, выполняющий операцию инвертирования входного сигнала, служнт для питания первого элемента памяти, выход которого, выполняющий онерацию повторения запомненного сигнала, через дросселирующее сопротивление соединен с занисывающим входом второго элемента намяти. Выход элемента памяти, выполняющий операцию инвертирования запоминаемого сигнала, служнт выходом триггера, а также служит для питания второго релейного усилителя с одним входом, на вход которого и на стирающий вход второго элемента памяти подключен сигнал с выхода, выполняющего операцию инвертирования запоминаемого сигнала первого элемепта памяти. Выход второго усилителя, выполняющий операцию инвертирования, соедииен с записывающим входом первого элемента памяти; на выходах второго релейного усилителя и второго элемента памяти, выполняющих операцию повторения, подключены дросселирующие сопротивления и релейный усилитель с одним входом и двумя взаимно инверсными выходами.

С целью переключения триггера в исходное положение предусмотрен вход для подачи сигнала на канал стирания первого элемепта памяти.

Для выполнения линейных непрерывных операций в системе применен модуль, содержащий цепочку усилительных элементов непрерывного действия, в которой давление питания через дросселирующие сопротивления.

устанавливающие нужные уровнн давлений, соединены с питающими каналами всех элементов, составляющих усилительную цепочку, за исключением выходного элемента, к пнтающему каналу которого давление подведено без дросселирующего соиротивления. Инверсные выходы предыдущих элементов соединены со входами последующих элементов, вход первого элемента служит для подачи входного

сигнала, выход последнего элемента - для снятия выходного сигнала, а для нолучения на выходе инвертирования входного сигнала усилительная цепочка выполнена из нечетного числа инверсных элементов.

С целью выполнения типовых нелинейных онераций иснользован модуль, реализующий непрерывным способом операцию возведения в квадрат положительиых значений одного аргумента, задаваемого давлением, который выполней на двух элементах ненрерывпого действия, одии из которых аппроксимирует квадратичную параболу, а второй служит для поьышения точиости аипрокснмироваиия, причем давление питания нодведено к нитающему каналу нервого элемента и через дросселирующее сопротивление - к управляющему 1 аиалу второго элемента. Инверсный выход второго элемента соединен с одним из управляющих каналов первого элемента, другой унрапляющнй канал первого элемепта соединен с нитающим каналом второго элемента, место соединения служнт для подачп входпого сигнала, а выходом модуля служнт выходной канал нервого элемента.

Для перехода от д :скретного сигнала диапазона низких давлений к дискретному сигналу в диапазоне высоких давлеиий использован модуль струйного дискретного усилителя мощности, в котором каскады элементов

соединены последователь 10 в усилительную цепочку, обеспечивая нужный коэффициент усиления по .дющности, причел давление питания к каждому из элементов подведено через соответствующие дросселирующие сопротивлсния, обеснечивающие нужный уровень давления питания, за исключеиием последнего г:аскада, к которому подведено полное давление питания модуля.

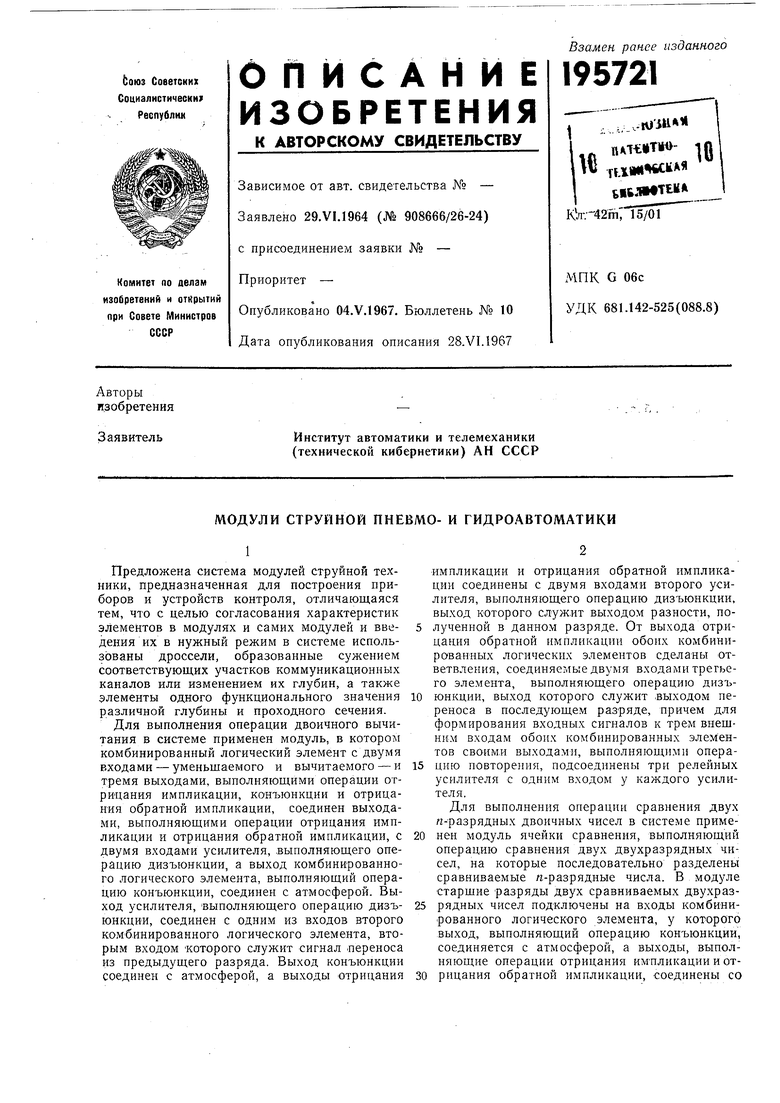

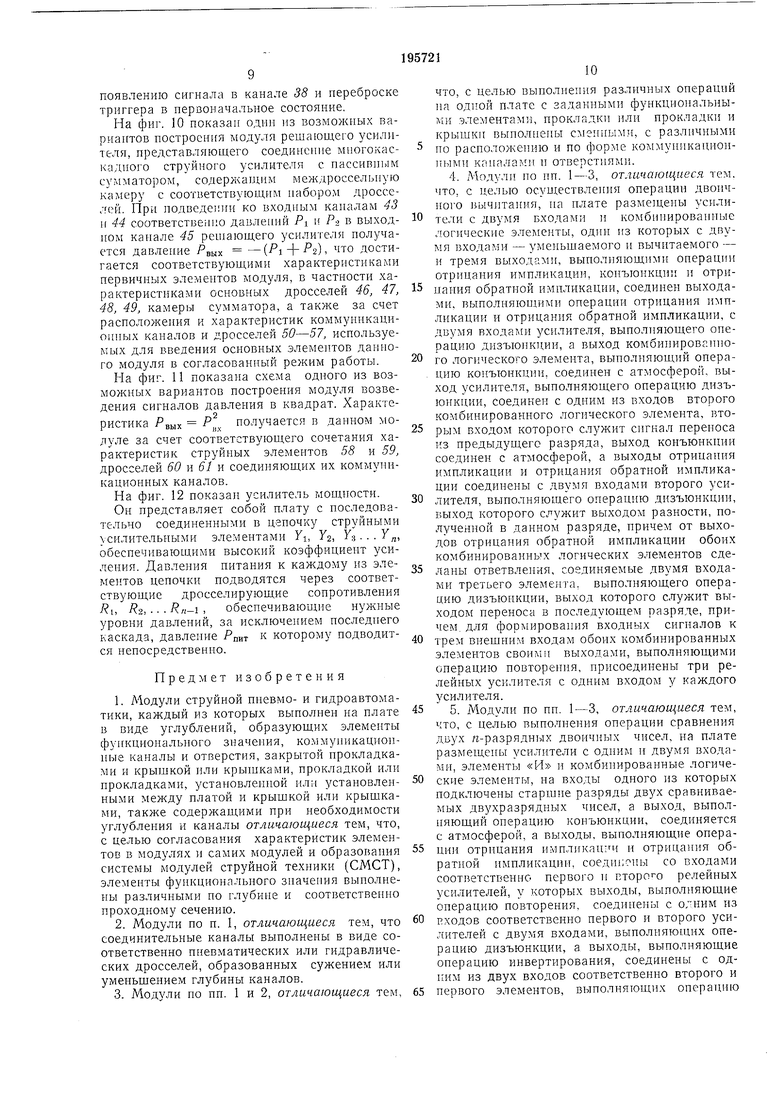

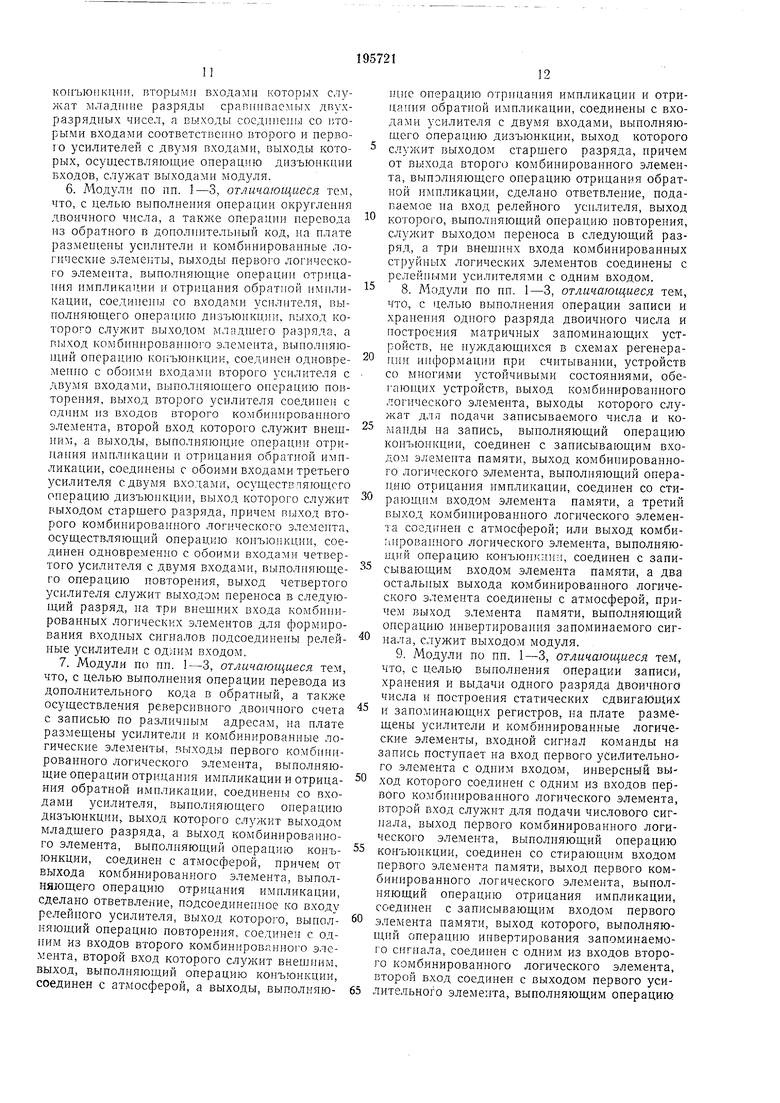

На фиг. 1 показан модуль, выполняющий

логическую операцию «ИЛИ при нескольких входах (собирательная схема).

При выполнении данног-о модуля с жесткой программой, определяемой расноложением коммуннкационных каналов (снлошные линии

на фиг. 1) образуются две группы элементов, в которые входят соответственно струйные элементы /, 2, 3 и 4, 5, 6, каждым из которых реализуется онерация «ИЛИ для двух входных сигналов, нричем каждой из грунп элементов выполняется логическая операция «ИЛИ для четырех входиых сигпалов. Для первой группы элементов входными сигпаламн являются давления и расходы рабочей среди, создаваемые на входах .i, Х-, Х, а

бочей среды, создаваемые на выходе }. Для второй группы элементов входами являются соответственно Х, Хд, Х-; и д, а выходом - YZ. В некоторых случаях целесообразно вынолнение указанной операции нрн возможно большем в пределах одного модуля количестве входов. Это достигается с помощью дополнительного канала 7, иоказаниого на фиг. 1 штрихпунктирной лнннем. При таком соединении элементов осуш,ествляется операция «ИЛИ для семи входов (Al, А ., Лз, Xi, Х, Х, Х-;), нричем выходиым является сигнал на выходе YZ.

Первичная операция «ИЛИ для двух входов выполняется струйными элементами, показанными на фиг. 1, где, например, в элементе / входные сигналы проводятся но каналам 8 и 9 (10 - капал нитаиия, И - канал обратной связи, 12 - выходной канал элемента). Струя, выходяндая из канала 10, поступает к рабочему выходному каналу тогда, когда созданы давления в каналах 5 плн 9, а при отсутствии давления в этих каналах струя проходит к нерабочему выходному каналу 13, & в канале 12 давленне не создается.

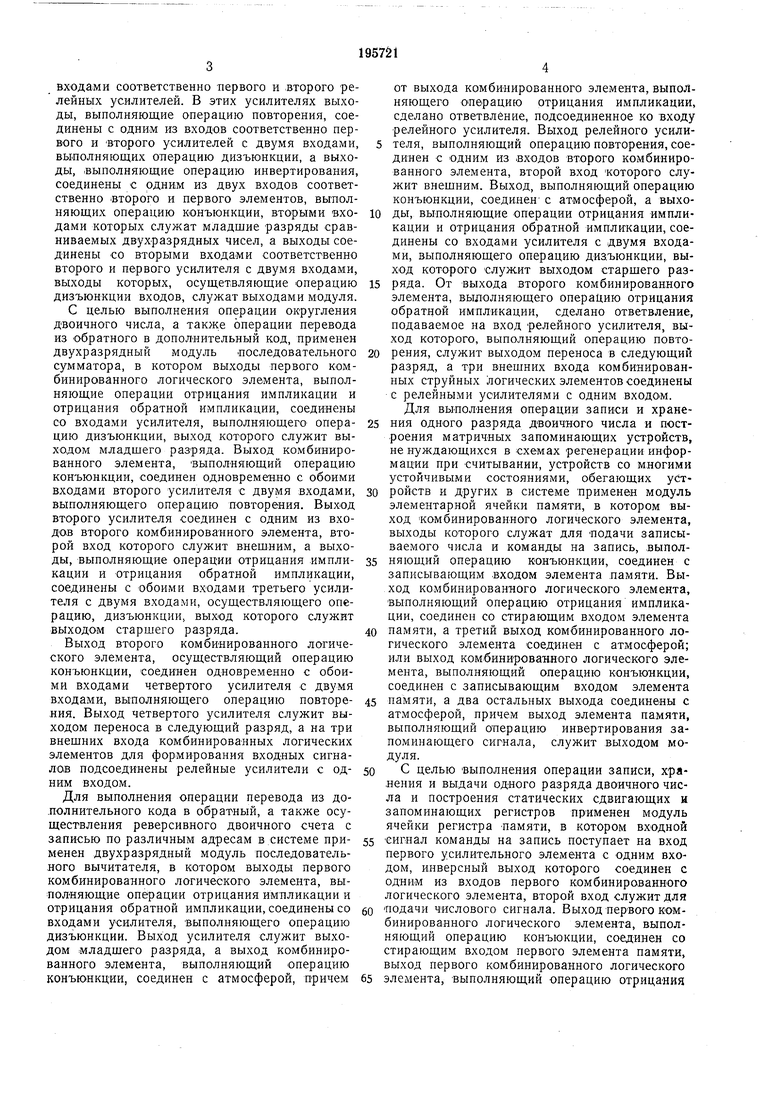

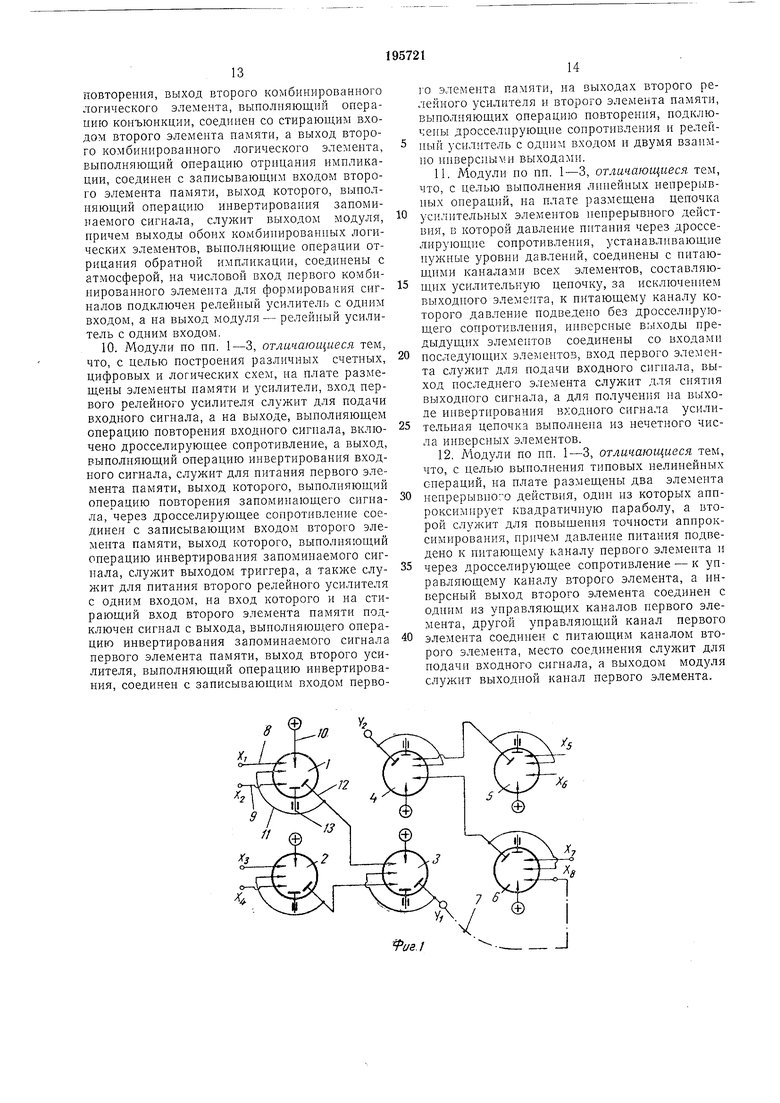

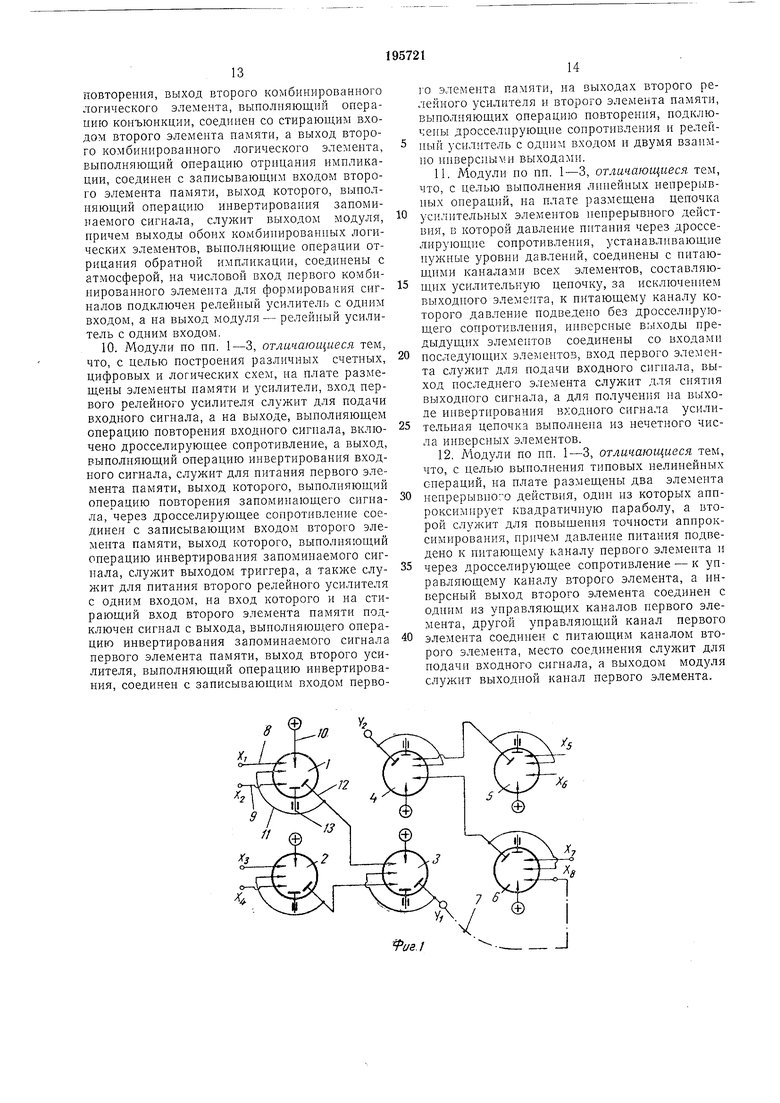

На фиг. 2 ноказано одно из возможных выполнений модуля полного одноразрядного сумматора. Здесь: а и 6/- складываемые разряды двух чисел, ct-i - перенос из предыдун1,его разряда, 0/ - результат суммирования, С; -перенос в следующнй разряд. Направлення струй на выходе каналов показаны на фиг. 2 стрелками.

Для введения отдельных элементов в нормальный режим работы в схему введены перепускные дроссели 14 и 15.

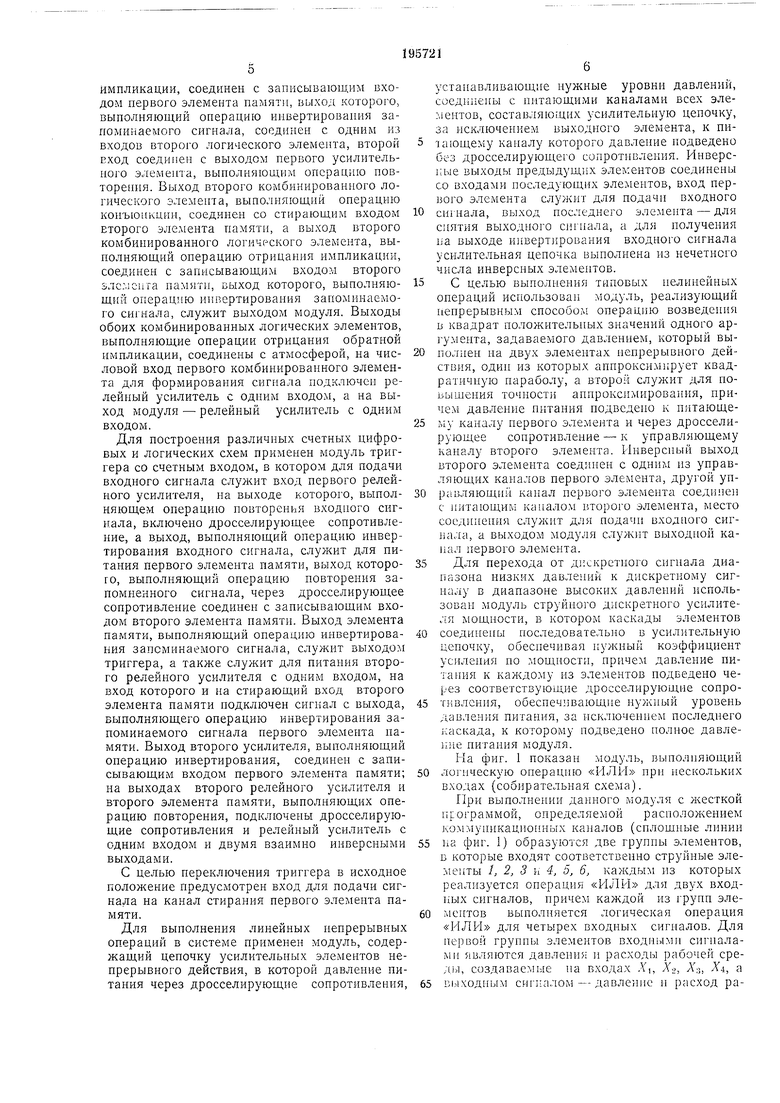

На фиг. 3 показан один на возмо кных вариантов полного одноразрядного вычислителя, позБОЛяюш,ий выполнять онерацню вычитания в прямом коде и эффективно строить специализированные блоки деления. Здесь: Xi - разряд уменьшаемого числа. У/ - разряд вычитаемого числа, - передача сигнала в следуюш,ий разряд о том, что в нем сделан заем.

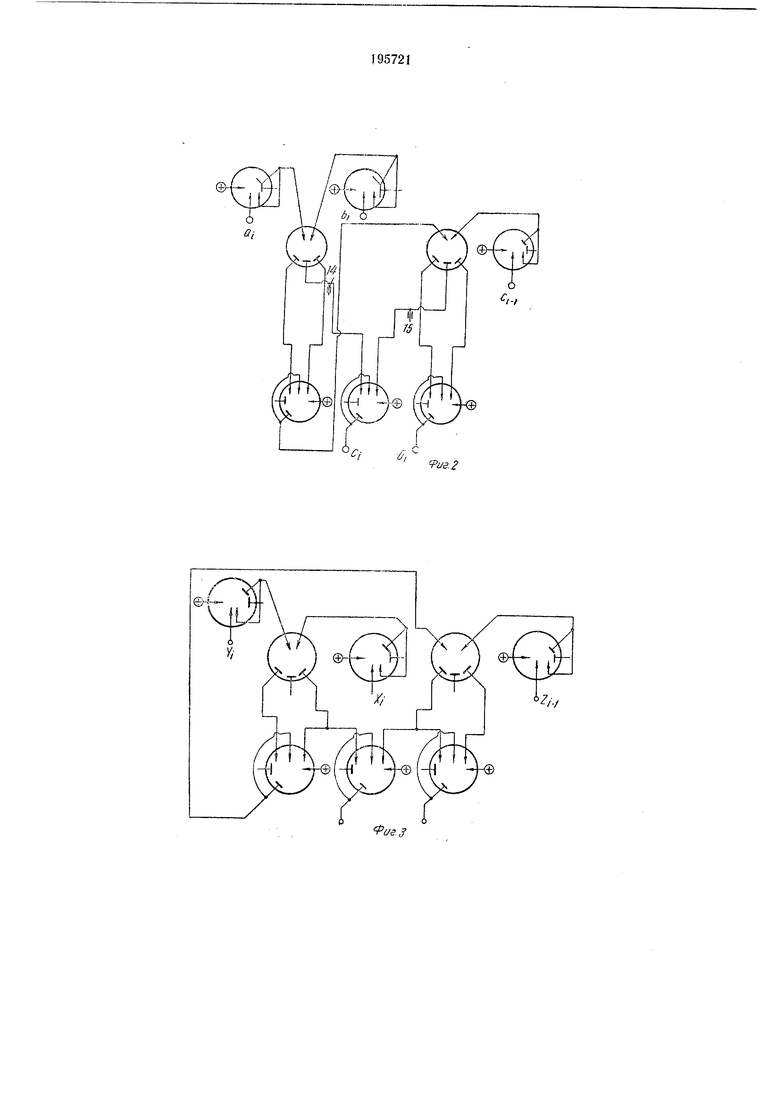

На фиг. 4 показан один из возможных вариантов выполнения модуля поразрядного сравнения чисел. В данном модуле производится сравнение сразу двух разрядов двух чисел Л I Go, «1) и В I &2, & I, и на выходах 16 и 17 модуля получаются следуюгцие сигналы: У 1, , еслиЛ В; У 0, , если У Z, если А В.

На фиг. 5 один из возможных вариантов построения модуля последовательного сумматора. Здесь: а и ai-i - параллельно вводимые два разряда числа; -вход переноса из предыдущего однотипного модуля (при объединении микромодулей этого типа в макромодули), или если ячейка, представляемая данным модулем, младшая, то ввод нмпульсов, прибавляемых к данному числу; о,- н Of-i - выводы соответствующих разрядо суммы, bi+i -перенос в следуюидий одиоТ1 п ый модуль (при объединении мнкромодулей этого тина в макромодули).

На фиг. 6 представлеи один из возможных вариантов ностроения модуля последовательного вычитателя. Здесь: Х vi X i- - параллельно вводимые два разряда числа X и YI- -ввод заема из предыдущего однотипного модуля (при объединеиии микромодулей этого тина в макромодули), если ячейка, представляемая данным модулем младшая, то ввод импульсов, вычитаемых из числа Х б,и - выводы соответствующих разрядов разности, Уi - вывод заема в следующий однотипный модуль (при объединеннн микромодулей этого тииа в макромодули).

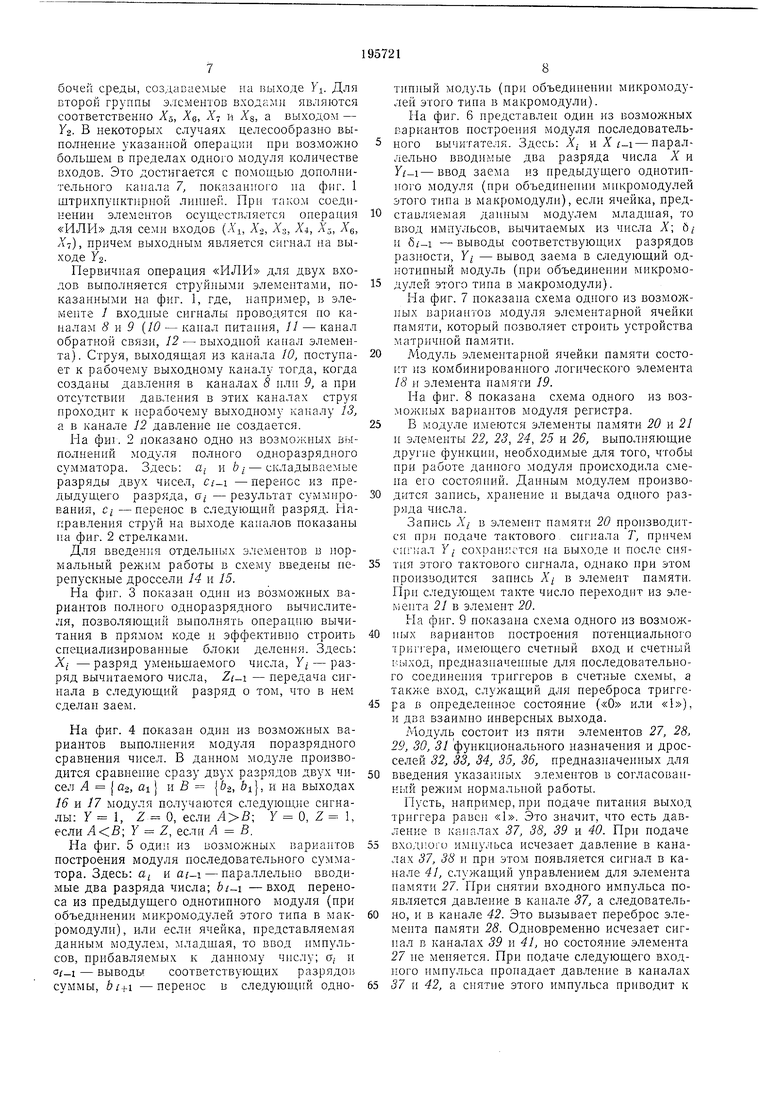

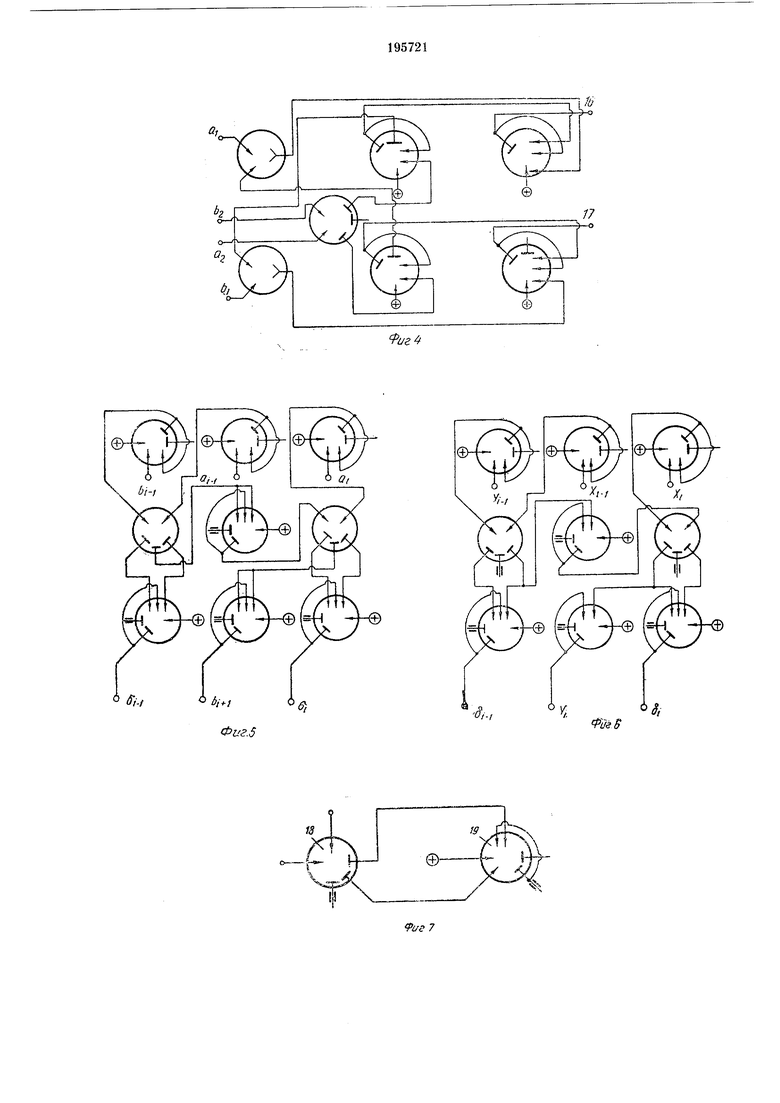

На фиг. 7 иоказаиа схема одного из возможных вариантов модуля элементарной ячейки памяти, который иозволяет строить устройства матричной памяти.

Модуль элементарной ячейки памяти состо т из комбинированного логического элемента 18 и элемента намяти 19.

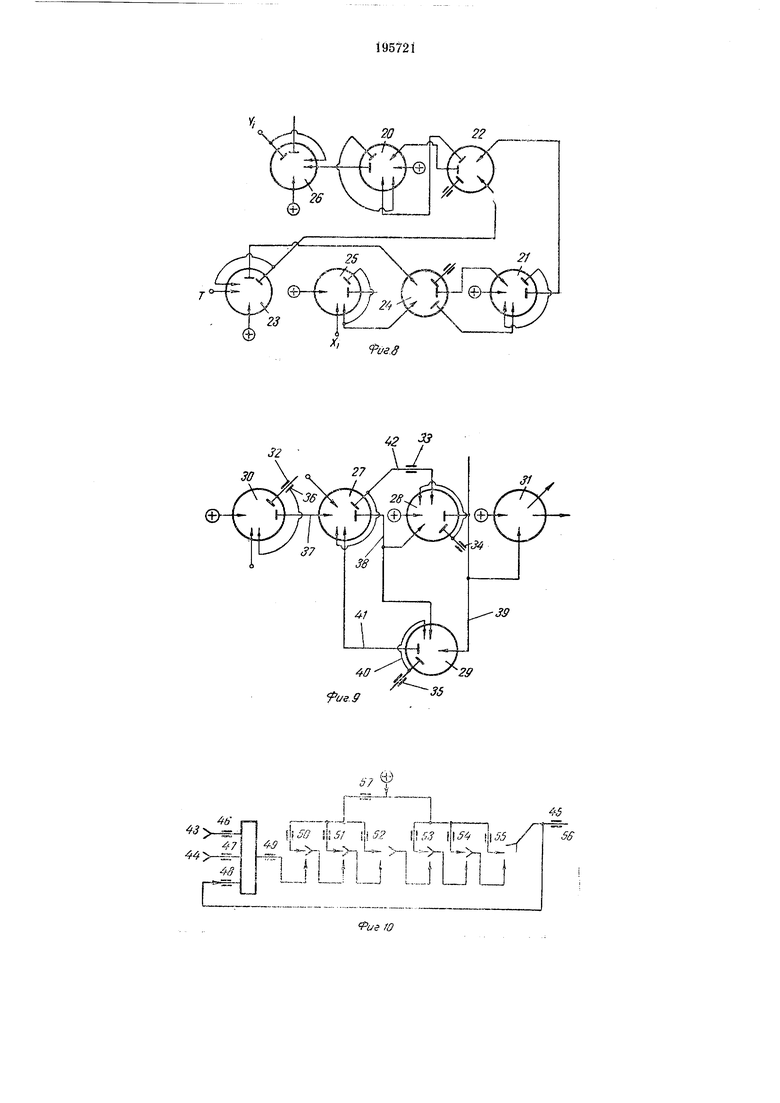

На фиг. 8 показана схема одного из возможных варнантов модуля регистра.

В модуле имеются элементы намятн 20 и 21 и элементы 22, 23, 24, 25 и 26, выполняющие другие функции, необходимые для того, чтобы нри работе данного модуля происходила смеиа его состояний. Данным модулем производится заннсь, хранение н выдача одного разряда числа.

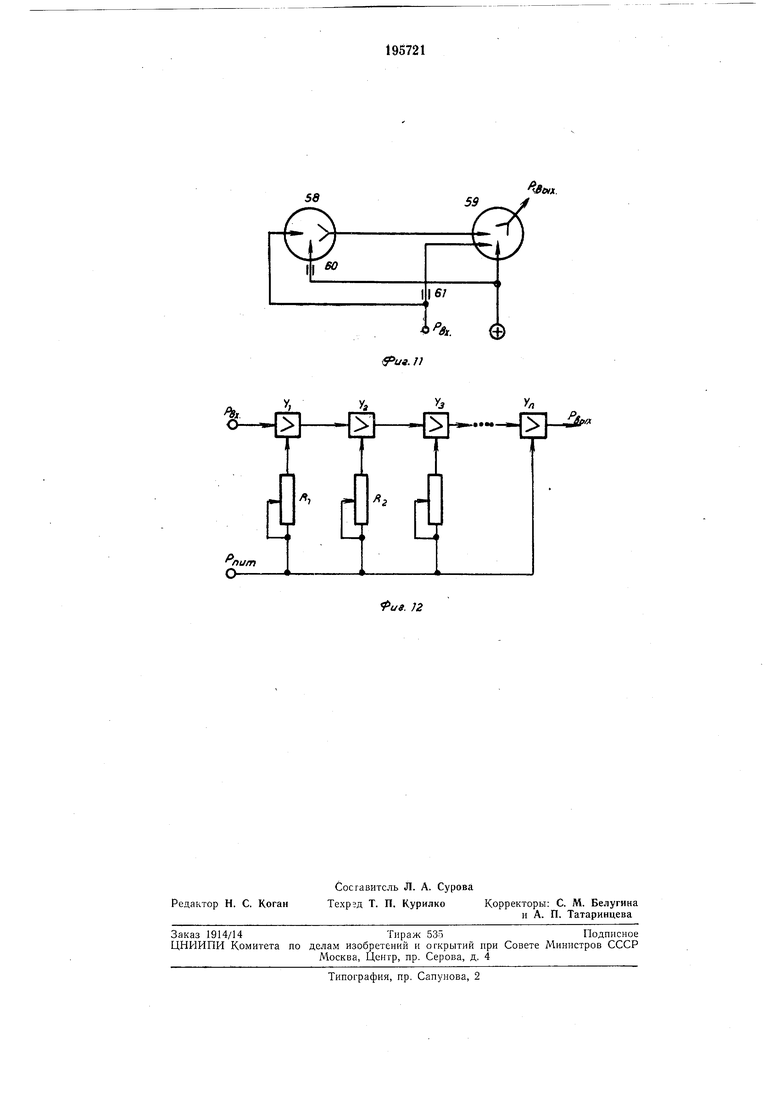

Запись А; в элемент памяти 20 нроизвод1ггся при подаче тактового сигнала Т, причем сигнал У,- сохран5;стся на выходе н после снятня этого тактового снгнала, однако при этом производится запись Aj в элемент памяти. Нрн следующем такте чис.то переходит из элемента 21 в элемент 20. На фиг. 9 ноказапа схема одного из возможпых вариантов ностроения потенциальиого трипера, имеющего счетный вход и счетный Гыход, предназначенные для последовательного соединения триггеров в счетные схемы, а также вход, служащий для нереброса триггера в определенное состояние («О или «1), и два взаимно инверсных выхода.

Модуль состоит из пяти элементов 27, 28, 29, 30, 31 функцнонального назначения и дросселей 32, 33, 34, 35, 36, предназначенных для

введения указанных элементов в согласованный нормальной работы.

Нусть, например, при подаче питания выход триггера равен «1. Это значит, что есть давление в каналах 37, 38, 39 и 40. Нри подаче

входного импульса исчезает давление в каналах 37, 38 н прн этом появляется сигнал в канале 41, служащий управлением для элемента памяти 27. Нри снятии входного импульса появляется давление в канале 37, а следовательно, и в канале 42. Это вызывает переброс элемента памяти 28. Одновременно исчезает сигпал в каналах 39 н 41, но состояние элемента 27 не меняется. Нри нодаче следующего входного импульса пропадает давленне в каналах

появлению сигнала в канале 38 и переброске триггера в первоначальное состояние.

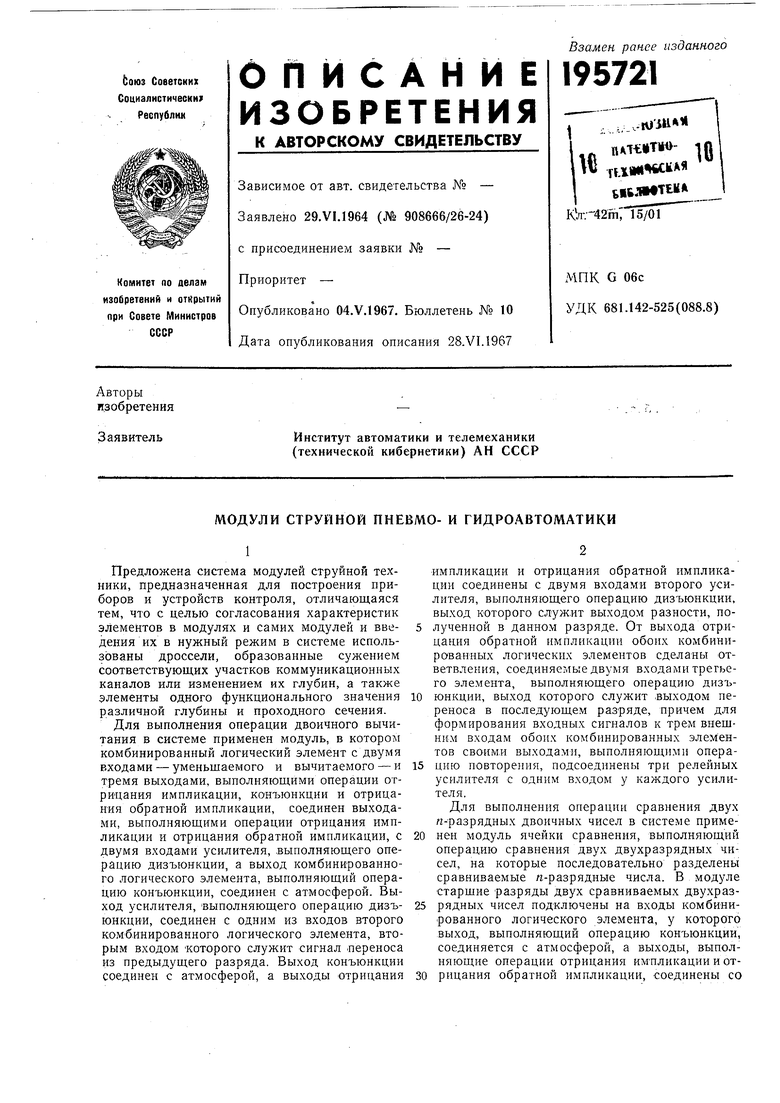

На фиг. 10 показан один из возможных вариантов иостроення модуля решающего усилителя, представляющего соединеиие многокаскадного струйного усилителя с пассивным сумматором, содержаи.им междроссельную камеру с соответствующим набором дросселей. При подведе1;ни ко входным каналам 43 и 44 соответственно давлений PI и Ро в выходном канале 45 решающего усилителя получается давление РВЫХ -(-Pi+ 2), что достигается соответствующими характеристиками первичных элементов модуля, в частности характеристиками основных дросселей 46, 47, 48, 49, камеры сумматора, а также за счет расиоложеиия и характеристик коммуникационных каналов и дросселей 50-57, используемых для введения основных элементов данного модуля в согласованный режим работы.

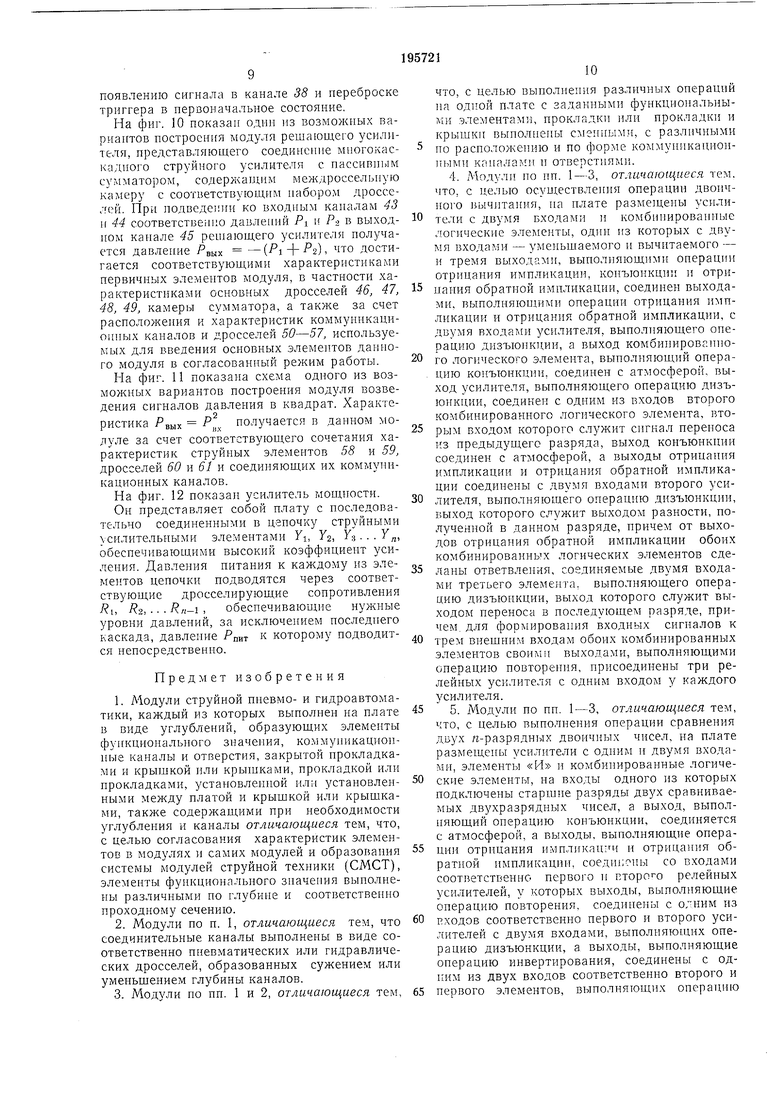

На фиг. 11 показана схема одного из возможных вариантов построения модуля возведения сигналов давления в квадрат. Характеристика /вых Р получается в данном модуле за счет соответствующего сочетания характеристик струйных элементов 58 и 59, дросселей 60 и 61 и соединяющих их коммуникационных каналов.

На фиг. 12 показан усилитель мощности.

Он представляет собой плату с последовательно соединенными в цепочку струйными усилительными элементами Y-i, Y, Yf,. . . Y„, обеспечивающими высокий коэффициент усиления. Давления питания к каждому из элементов цепочки подводятся через соответствующие дросселирующие сопротивления RI, R2,.--Rri-i, обеснечиваюнхие нужные уровни давлений, за исключением последнего каскада, давление РПИТ к которому подводится непосредственно.

Предмет изобретения

1.Модули струйной пневмо- и гидроавтоматики, каждый из которых выполиен на плате в виде углублений, образующих элементы функционального значения, коммуникашюнные каналы и отверстия, закрытой ирокладками и крышкой или крышками, прокладкой или прокладками, установленной или установленными между платой и крышкой или крышками, также содержащими при необходимости углубления и каналы отличающиеся тем, что, с целью согласования характеристик элементов в модулях и самих модулей и образования системы модулей струйной техники (СМСТ), элементы функционального значения выполнены различными по глубине и соответственно проходному сечению.

2.Модули по п. 1, отличающиеся тем, что соединительные каналы выполнены в виде соответственно пневматических или гидравлических дросселей, образованных сужением или уменьшением глубины каналов.

что, с целью выполнения различных операций на одной плате с заданными функцнональными элементам;-, прокладки или прокладки н крышки вынолиены сменными, с различными 5 но расноложению и по форме коммуникацио)нымн каналами и отверстиями.

4. Модули но ип. 1-3, отличающиеся тем. что, с целью осуществления операции двоичного 15ычита11ня, на нлате размещены усили10 тсли с двумя входами и комбинированные логические элементы, один из которых с двумя входами - уменьшаемого и вычитаемого - и тремя выходами, выполняющттн оиерации отрицания импликации, конъюнкции и отри5 нания обратной импликации, соедииен выходами, вынолняющими операции отрицания импликации и отрицания обратной импликации, с двумя входами усилителя, выполняюшего операцию днзъюнкции, а выход комбинированно0

го логического элемента, выиолняющии операцию конъюнкции, соединен с атмосферог, выход усилнтеля, выполняющего операцию дизъюнкции, соединен с одним из входов второго комбинированного логического элемента, вторым входом которого служит сигнал перепоса из предыдущего разряда, выход коиъюнкпии соединен с атмосферой, а выходы отринация импликации и отрицания обратной импликации соединены с двумя входами второго усилителя, выполняющего операцию дизъюнкции, выход которого служит выходом разности, полученной в данном разряде, нричем от выходов отрицания обратной импликации обоих комбинированных логических элементов сде5 лапы ответвления, соединяемые двумя входами третьего элемента, выполняющего операцию дизъюнкции, выход которого служит выходом переноса в последующем разряде, причем, для формирования входных сигналов к

0 трем внешним входам обонх комбинированных элементов своимii выходами, выполняющими операцию повторения, нрисоединены три релейных усилителя с одним входом у каждого усилителя.

5 5. Модули по пп. 1-3, отличающиеся тем, что, с целью выполнения операции сравнения двух п-разрядных двоичных чисел, па плате размещены усилители с одним н двумя входами, элеА1енты «И н комбинированные логические элементы, на входы одного из которых подключены старшие разряды двух сравниваемых двухразрядных чисел, а выход, выполняющий операцию конъюнкции, соединяется с атмосферой, а выходы, выполняющие операции отрицания импликации и отрицания обратной импликации, соеди1;оны со входами соответственио первого п второго релейиых усилителей, у которых выходы, выполняющие операцию повторения, соединены с олним из

входов соответственно первого и второго усилителей с двумя входами, выполияющнх операцию дизъюнкции, а выходы, выполняющие оиерацию инвертирования, соедииены с одним из двух входов соответственно второго и

11

конъюнкции, вторым входамн которых служат младшие разряды срапиипасмых дпухразрядиых чисел, а выходы соедпиепы со I;TOрыми входами соответственно второго и первого усилителей с двумя входами, выходы которых, осуществляющие операцию дизъюнкции входов, служат выходами модуля.

6.Модули по пп. 1-3, отличающиеся тем, что, с целью выполнения операции округлеиия двоичиого числа, а также операции перевода из обратного в доцолиительиый код, на плате размещеиы усилители и комбииированные логические элементы, выходы первого логического элемента, выполняющие операции отрицания импликации и отрицаиия обратной имнликации, соединены со входами уснлнтеля, вынолняющего операцию дизъюнкции, выход которого служит выходом младшего разряда, а выход комбинированного элемента, вынолияющнй онерацию конъюнкции, соединен одновременно с обоими входами второго усилителя с 71,вумя входами, выполняющего операцию новтореиия, выход второго усилителя соедииен с одним из входов второго комбинированного элемента, второй вход которого служит внещним, а выходы, выполняющие операции отрицания имиликацни и отрицания обратной имнликации, соедипеиы с обоими входами третьего усилителя с двумя входами, осуществляющего операцию дизъюнкции, выход которого служит выходом старщего разряда, причем выход второго комбипированного логнческого элемента, осуществляющий онерацию конъюнкции, соединен одиовременно с обоими входами четвертого усилителя с двумя входами, выполняющего операцию повторения, выход четвертого усилителя служит выходом нереноса в следующий разряд, на три виещиих входа комбинированных логических элементов для формирования входиых сигналов подсоединены релейные усилители с одиим входом.

7.Модули ц() пи. 1-3, отличающиеся тем, что, с целью выполнения операции перевода из дополнительного кода в обратный, а также осуществления реверсивного двоичного счета с записью по различным адресам, на нлате размещены усилители и комбиинроваиные логические элементы, выходы первого комбииированного логического элемента, выполняющие операции отрицания импликации и отрицания обратной импликации, соедииеиы со входами усилителя, выполняющего онерацию дизъюнкции, выход которого служит выходом младщего разряда, а выход комбинированного элемента, выполняющий операцию конъюнкции, соединен с атмосферой, причем от выхода комбинированного элемента, выполняющего операцию отрицания имнликацни, сделано ответвление, подсоединенное ко входу релейного усилителя, выход которого, вынол няющий операцию повторения, соединен с одиим из входов второго комбинированного элемента, второй вход которого слзжит внещним, выход, выполняющий операцию конъюнкции, соединен с атмосферой, а выходы, вынолняющие операцию отрицацня импликации и отригхания обратной импликации, соединены с входами усилителя с двумя входами, выполняющего операцию дизъюнкции, выход которого служит выходом старщего разряда, причем от выхода второго комбинированного элемента, выполняющего операцию отрицания обратной импликации, сделано ответвле ше, подаваемое на вход релейного усилителя, выход которого, выполняющий операцню повторения, служит выходом нереноса в следующий разряд, а трн внещних входа комбинированных струйных логических элементов соединены с релейными усилителями с одним входом.

8.М.одули по ип. 1-3, отличающиеся тем, что, с целью выполнения операции записи н хранения одного разряда двоичного числа и иостроення матричных запоминающих устройств, не нуждающихся в схемах регенерации ииформации при считывании, устройств со многими устойчивыми состояниями, обегающих устройств, выход комбинированного логического элемента, выходы которого служат ДЛЯ: подачи записываемого числа и команды на запись, вынолняющнй операцию конъюнкции, соединен с зацисывающнм входом элемецта памяти, выход комбинированного логического элемента, выполняющий операцию отрицания импликации, соединен со стирающим входом элемента памяти, а третий выход комбинированного логического элемента соединен с атмосферой; или выход комбинированного логического элемента, выполняющий операцию конъюнкнии, соединен с записывающим входом элемента памяти, а два остальных выхода комбинированного логического элемента соединены с атмосферой, причем выход элемента памяти, выполняющий операцию инвертирования запоминаемого сигнала, служит выходом модуля.

9.Модули по пн. 1-3, отличающиеся тем, что, с целью вынолнения операции записи, хранения н выдачи одного разряда двоичного числа и построения статических сдвигающих и запоминающих регистров, на нлате размещены усилители и комбинированные логические элементы, входной сигнал команды на запись поступает на вход первого уСйЛительного элемента с одним входом, инверсный выход которого соединен с одним из входов первого комбинированного логического элемента, второй вход служит для подачи числового сигнала, выход первого комбинированного логического элемента, выполняющий операцию конъюнкции, соединен со стирающим входом нервого элемента памяти, выход первого комбинированного логического элемента, выполняющий операцию отрицания импликации, соединен с записывающим входом первого элемента памяти, выход которого, выполняющий операцию инвертирования запоминаемого сигнала, соединен с одним из входов второго комбинированного логического элемента, второй вход соединен с выходом первого усилительного элемента, выполняющим операцию

13

повторения, выход второго комбинированного логического элемента, выполняющий операиию конъюнкции, соединен со стирающим входом второго элемента памяти, а выход второго комбинированного логического элемента, выполняющий операцию отрицания импликации, соединен с записывающим входом второго элемента памяти, выход которого, выполняющий операцию инвертирования запоминаемого сигнала, служит выходом модуля, причем выходы обоих комбинированных логических элементов, выполняющие операции отрицания обратной импликации, соединены с атмосферой, на числовой вход нервого комбинированного элемента для формирования сигналов подключен релейиый усилитель с одним входом, а на выход модуля - релейный усилитель с одним входом.

10. Модули но пп. 1-3, отличающиеся тем, что, с целью построения различных счетных, цифровых и логических схем, на плате размещены элементы памяти и усилители, вход первого релейного усилителя служит для подачи входного сигнала, а на выходе, выполняющем операцию повторения входного сигиала, включено дросселирующее сопротивление, а выход, выполняющий операцию инвертирования входного сигнала, служит для питания первого элемента памяти, выход которого, выполняющий операцию повторения запоминающего сигнала, через дросселирующее сопротивление соединен с записывающим входом второго элемента памяти, выход которого, выполняющий операцию инвертирования запоминаемого сигиала, служит выходом триггера, а также служит для питания второго релейного усилителя с одним входом, иа вход которого и на стирающий вход второго элемента памяти подключен сигнал с выхода, выполняющего операцию инвертирования запоминаемого сигнала первого элемента памяти, выход второго усилителя, выполняющий операцию иивертирования, соединен с записывающим входом перво)(,

14

го элемента памяти, на выходах второго релейного усилителя и второго элемента памяти, выполняющих операцию повторения, подключены дросселирующие сопротивления и релейный усилитель с одним входом и двумя взаимно инверсными выходами.

11.Модули по пп. 1-3, отличающиеся тем, что, с целью выполнения линейных непрерывных онераций, иа плате размещена цепочка

0 усилительных элементов непрерывного действия, в которой давление питания через дросселирующие сопротивления, устанавливающие иужные уровни давлений, соедииены с питающими каиаламн всех элементов, составляю5щих усилительную цепочку, за исключением выходного элемента, к питающему каналу которого давление подведено без дросселирующего сопротивления, инверсные выходы предыдущнх элементов соединены со входами

0 последующих элементов, вход первого элемента служит для подачи входного сигнала, выход последнего элемента служит для снятия выходного сигнала, а для получения на выходе инвертирования входного сигнала усили5тельиая цепочка вынолиена из нечетного числа инверсных элементов.

12.Модули но пн. 1-3, отличающиеся тем, что, с целью выполнения типовых нелинейных онераций, на плате размещены два элемента

0 непрерывного действия, одии из которых аппроксимирует квадратичную параболу, а второй служит для повышения точности аппроксимироваиия, причем давление питания подведено к питающему каналу первого элемента и через дросселирующее сопротивление - к управляющему каналу второго элемента, а инверсный выход второго элемента соединен е одним из унравляющих каналов первого элемента, другой управляющий канал первого элемента соединен с питающим каналом второго элемента, место соединения служит для нодачн входного сигнала, а выходом модуля служит выходной канал нервого элемента.

Cf6,

fue-Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| Логическое запоминающее устройство | 1972 |

|

SU464017A1 |

| Устройство для анализа нечетких данных | 1989 |

|

SU1683004A1 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Арифметико-логическое устройство | 1974 |

|

SU509870A1 |

| Устройство для автоматического управления производственными процессами | 1974 |

|

SU547727A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| СПОСОБ ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ НА ЗАПОМИНАЮЩЕМ ЭЛЕМЕНТЕ | 1966 |

|

SU224160A1 |

tJs.J

fPliaS

13

32

30

4ti

I iLw Hi 5/ }л52 Ц 53 ip 1|Л5

i i . , L V. l-.

47

48

...«}

из.д

29

35

...1

6S

А.

ия. //

Даты

1967-01-01—Публикация