Предлагаемая схема относится к области вычислительной техники.

Известны схемы, обладающие двумя устойчивыми состояниями (бистабильные схемы или триггеры), в которых роль управляемой обратной связи выполняют диодные логические схемы.

Для известных бистабнльных схем характерно наличие двух парафазных выходов, что облегчает их использование в логических схемах. Однако часто бистабильные схемы выполняют только функцию хранения информации, когда второго инверсного выхода не требуется.

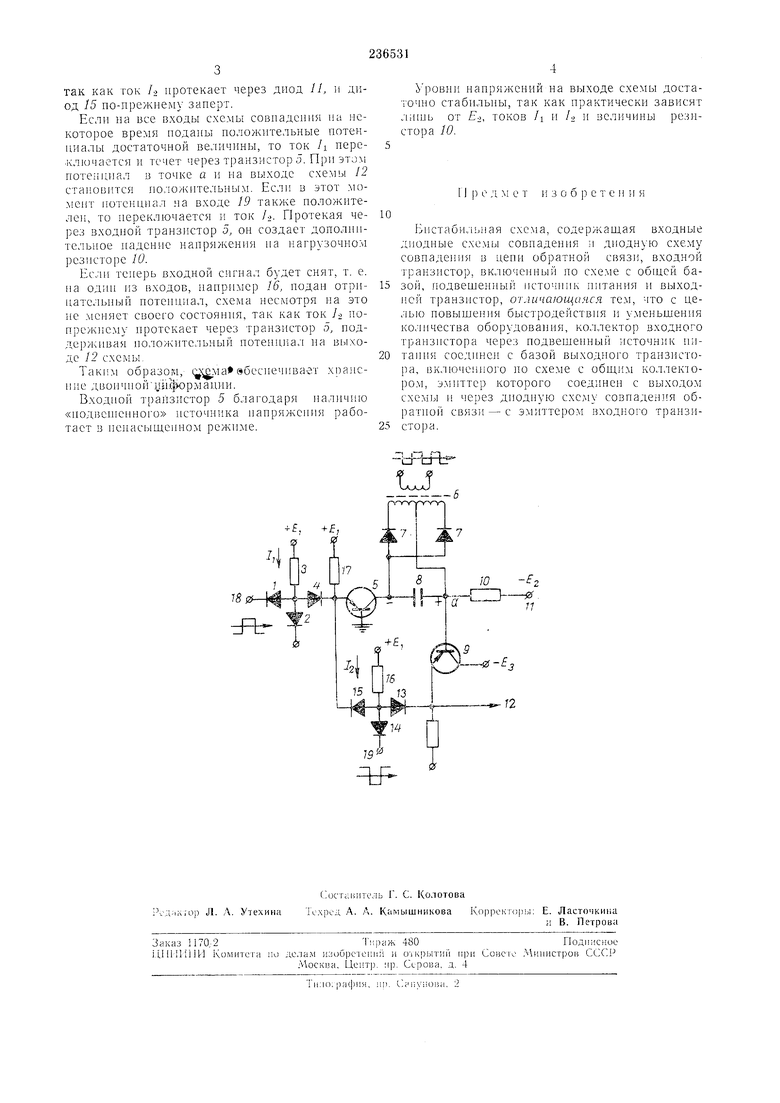

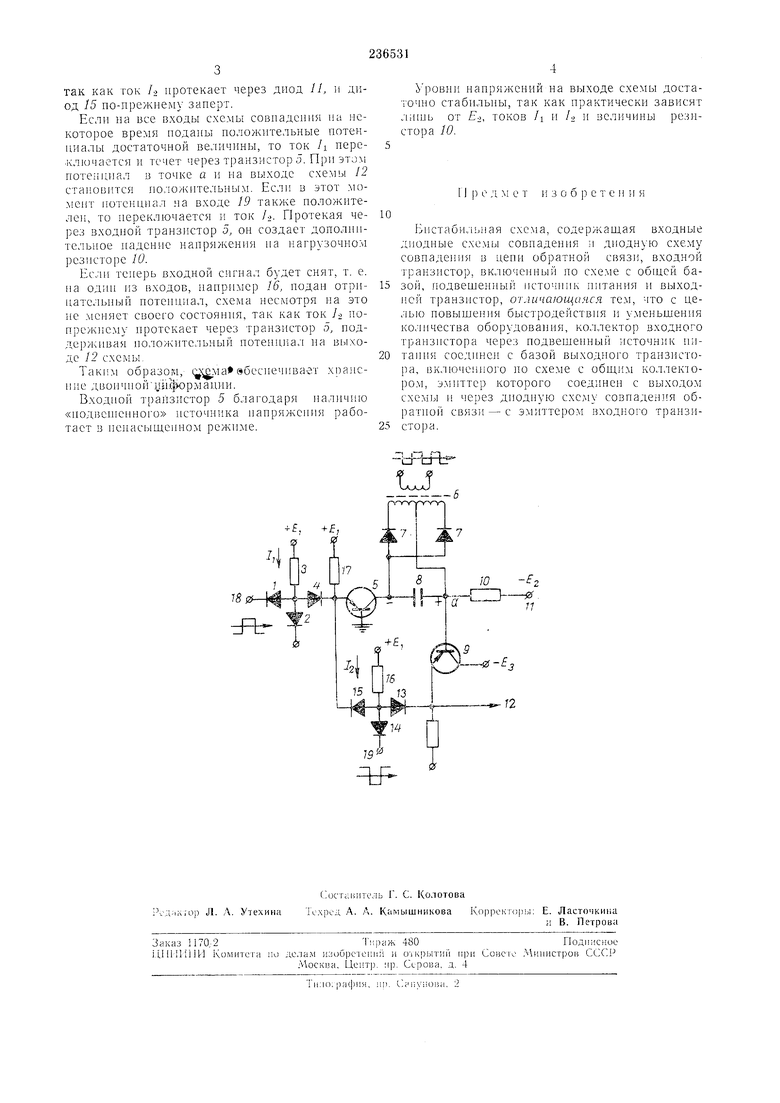

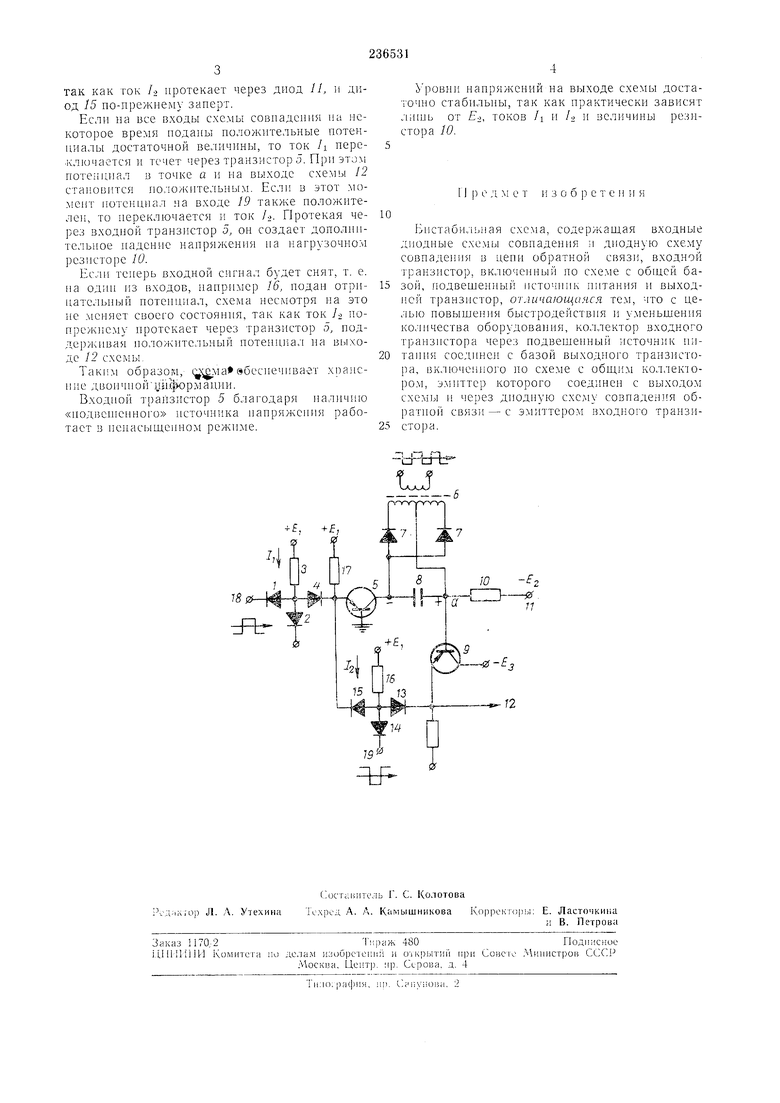

Предлагаемая бистабильная схема с управляемой обратной связью имеет только один выход (прямой). Схема обладает высоким быстродействием и позволяет осуществить запоминание двоичной информации при использовании небольшого количества оборудования. Это достигнуто тем, что коллектор входного транзистора через подвешенный источник питания соединен с базой выходного транзистора, включенного ло схеме с общий коллектором, эмиттер которого соединен с выходом схемы и через диодную схему совпадения обратной связи - с эмиттером входного транзистора.

Она состоит из входной диодной схемы совпадения на диодах / и 2, аноды которых соединены с резистором 3 и через сборочный диод - с эмиттером входного транзистора 5, включенного по схеме с общей базой, коллектор которого через подвешенный источник питания, состоящий из трансформатора 6, диодов 7 и конденсатора 8, подключен к базе выходного транзистора 9 и через резистор }0 к

источнику коллекторного питания 11 (--Е.2). Эмиттер транзистора 9, включенного по схеме с общим коллектором, соединен с выходом схемы 12 и через диодную схему совпадения цепи обратной связи на диодах 13 и

15 и резисторе 14 - с эмиттером транзистора 5 и резистором 17.

Схема имеет два устойчивых состояния. Если потенциалы на входах 18 и 19 диодных

схем совпадения таковы, что ток Л, задаваемый резистором 3, проходит через диод 2, а ток /9, задаваемый резистором 16, проходит через диод 14, то сборочные диоды 4 и 15 закрыты, и через транзистор 5 протекает лишь

небольшой ток /s, задаваемый резистором 17. При этом потенциал в точке а, а следовательно, и на выходе 12 схемы в основном определяется величиной - Е-. Если теперь на вход 19 будет подан положительный потак как ток / протекает через диод //, и диод 15 по-прежиему заперт.

Если на все входы схемы совпадепия па некоторое время поданы положптельные потенциалы достаточной величины, то ток /i пере.ключается и течет через транзистор 5. При этом потеп1 иал а точке а и иа выходе схемы 12 становится положительным. Если в этот люмеит потенциал па входе 19 также положителен, то иереключается и ток . Протекая через входной транзистор 5, оп создает донолпптельное падение напряжения па нагрузочном резисторе 10.

Если теперв входной сигнал будет снят, т. е. па один из входов, папример 16, подай отрипательиый потепппал, ехема песмотря па это не .меняет своего состояипя, так как ток /-2 ноарежпе.му протекает через транзистор 5, поддерживая положптельпый потеппна; на BBIXOде 12 схемы,

Так1.1 образок, (ма вбеспечпвает хоапеиие двоичпойиы юрмапнн.

Входной транзистор 5 благодаря наличию «подвепшииого псточника нанряжения работает в пенасв1щеппом режиме.

f, ,

l4a

2X

Уровни напряжений на выходе ехемв достаточно стабильиы, так как ирактнчееки зависят ;пипв от Е-,, токов /i и - и величины резнстора 10,

II ре л м е т и 3 о о р е т е и и я

Бистабпльная схе.ма, содержащая входнв1е диодные схемы совпадения и диодную схему совпадения в пепи обратной связи, входной транзнстор, включеннви по схе.ме с общей базой, подвещенный источппк пптания и выходной транзистор, отличающаяся те.м, что с целью повынтенпя быстродействия и уменьшения количества оборудования, коллектор входного транзнстора через подвешенный источник иитаипя соединен е базой выходного транзистора, включенного но схелш с общим коллекторо.м, э.миттер которого соединен с выходом схемы и через диодиую ехему совпадентя обратпой связи - е эмиттером входного транзистора.

iFtFtr

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| ИМПУЛЬСНЫЙ ДВУХФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ/И—ИЛИ—НЕ» | 1971 |

|

SU304698A1 |

| ВСЕСОЮЗНАЯ ПЛТгеТ1Ш-ТГШ:^;Е;л?= | 1973 |

|

SU363194A1 |

| Универсальный логический элемент | 1973 |

|

SU446950A1 |

| Линейный пропускатель сигналов | 1974 |

|

SU539375A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1972 |

|

SU341128A1 |

| МОДУЛЯЦИОННОЕ УСТРОЙСТВО | 1970 |

|

SU268490A1 |

| ГЕНЕРАТОРЧАСТОТНО-МОДУЛИРОВАННЫХ КОЛЕБАНИЙ | 1971 |

|

SU432659A1 |

| ТРИГГЕР | 1973 |

|

SU399051A1 |

Даты

1969-01-01—Публикация