В известном устройстве для деления частоты следования и формирования импульсов, содержащем входной усилитель-олраничитель, одну или две емкостные накопительные ячейки, диодные компараторы, цепи сброса, генератор сбрасывающего и выходного импульсов, быстродействие и надежность понижены при коэф фициенте деления, большем скважности выходных импульсов.

В предлагаемом устройстве аналогичного назначения повышение быстродействия и надежности при коэффициенте деления, большем скважности выходных импульсов, достигается тем, что оно снабжено триггером, вход установки «О которого подключен к выходу первого, а вход установки «1 - к выходу второго диодного компаратора, входы которых подключены соответственно и раздельно .к выходам первой и второй емкостных накопительных ячеек; входы ячеек .подключены к выходу входного усилителя-ограничителя, при этом к выходам первой и второй емкостных накопительных ячеек подключены соответственно аноды первого и второго диодов сброса, катоды .которых подключены соответственно к первому и второму выходам триггера.

при этом к выходу емкостной накопительной ячейки подключены совместно катоды первого и второго диодов сброса, аноды которых подключены через разрядные емкости соответственно к первому и второму выходам триггера и чарез резисторы к отдельному источнику постоянного напряжения. Аноды диодов первого и второго компараторов подключены соответственно к выходам первого и второго резисторных делителей, включенных в цепи коллекторов транзисторов триггера между его соответствующими выходами и источником постоянного напряжения. Такое выполнение устройства позволяет пооысить быстродействие и надежность при коэффициенте деления К, в п раз большем

скважности выходных импульсов, равной- ,

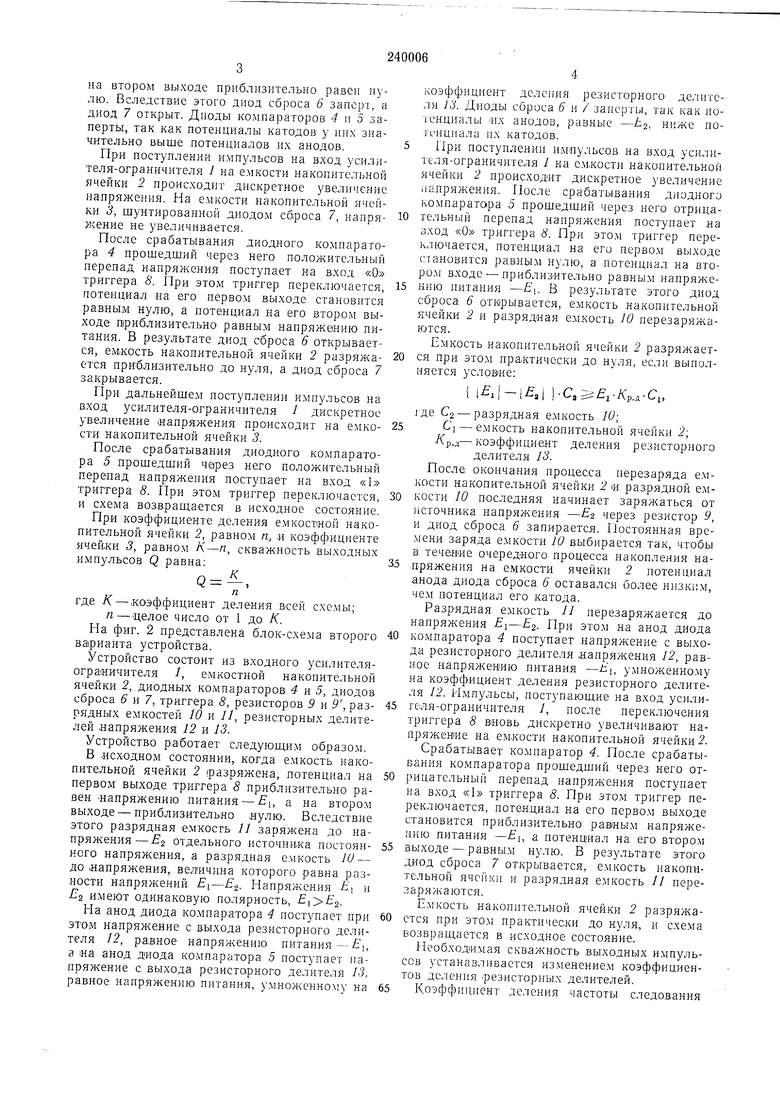

где п - целое число от 1 до К. На фиг. 1 представлена блок-с.хел1а описываемого устройства (первый вариант).

Устройство состоит из входного усилителяограничителя /, емкостных накопительных ячеек 2 и 3, диодных компараторов 4 н 5, диодов сброса 5 и 7 и триггера 8.

Устройство работает следующим образом. В исходном состоянии, когда емкости обеих накопительных ячеек разряжены до нуля, потенциал на первом выходе триггера 8 приблизительно равен напряжению питания , а

на втором выходе приблизительно равеи нулю. Вследствие этого диод сброса 6 занорт, а диод 7 открыт. Диоды компараторов 4 м 5 заперты, так как потенциалы катодов у них значительно выше потенциалов их анодов.

При поступлении импульсов на вход усилителя-ограничителя / на емкости накопительной ячейки 2 происходит дискретное увеличение напряжения. На емкости накопительной ячейки 3, шунтированной диодом сброса 7, напряжение не увеличивается.

После срабатывания диодного компаратора 4 прошедший через него положительный перепад напряжения поступает на вход «О триггера 8. При этом триггер переключается, потенциал на его первом выходе становится равным нулю, а потенциал на его втором выходе приблизительно равным напряжению питания. В результате диод сброса 6 открывается, емкость накопительной ячейки 2 разряжастоя приблизительно до нуля, а диод сброса 7 закрывается.

При дальнейшем поступлении импульсов на вход усилителя-ограничителя 1 дискретное увеличение напряжения происходит на емкости накопительной ячейки 3.

После срабатывания диодного компаратора 5 прошедший чарез него положительный перепад напряжения поступает на вход «1 триггера 8. При этом триггер переключается, и схема возврашается в исходное состояние.

При коэффициенте деления емкостной накопительной ячейки 2, равном п, и коэффициенте ячейки 3, равном Л-л, скважность выходных импульсов Q равна:п X 0. -,

где К - .коэффициент деления всей схемы; п - целое число от 1 до К.

Па фиг. 2 представлена блок-схе.ма второго варианта устройства.

Устройство состоит из входного усилителяограничителя /, емкостной накопительной ячейки 2, диодных компараторов 4 к 5, диодов сброса 5 и 7, триггера 8, резисторов 9 и 9, разрядных емкостей 10 и 11, резисторных делителей .напряжения 12 и 13.

Устройство работает следующим образом.

В исходном состоянии, когда емкость накопительной ячейки 2 (разряжена, потенциал на первом выходе триггера 8 приблизительно равен Напряжению литания - Е, а на втором выходе - приблизительно .нулю. Вследствие этого разрядная емкость // заряжена до напряжения- Е отдельного источника постоянного напряжения, а разрядная емкость Ю - до .напряжения, величина которого равна разности напряжений .,. Напряжения E н EZ имеют одинаковую полярность, .

На анод диода компаратора 4 поступает при этом напрял ение с выхода резисторного делителя 12, равное напряжению питания - ь а на анод диода компаратора 5 поступает )iaпряжение с выхода резистарного делителя 13, равное напряжению питания, умноженному на

коэффициент деления резисторного делителя 13. Диоды сброса 6 и / заперты, так как потенциалы ИХ анодов, равные -Ь, ниже потенциала их катодов.

При поступлении импульсов на вход усилителя-ограничителя 1 на ем кости накопительной ячейки 2 происходит дискретное увеличение напряжения. После срабатывания диодного компаратора 5 прошедший через него отрицательный перепад напряжения поступает на аход «О триггера 8. При этом триггер переключается, потенциал на его перво.м выходе становится равным нулю, а потенциал на втором входе - приблиЗИтельно равным напряжению иитания . В результате этого диод сброса 6 открывается, емкость накопительной ячейки 2 и разрядная емкость Ю перезаряжаются.

Емкость накопительной ячейки 2 разряжается при этом практически до нуля, если выполняется условие:

1 Е, Е, ).С,.д-С1,

где Cg - разрядная емкость 10;

С - емкость накопительной ячейки 2; /Ср.д-коэффициент деления резисторного делителя 13.

После окончания процесса перезаряда емкости накопительной ячейки 2 и разрядной емкости 10 последняя начинает заряжаться от источника напряжения через резистор 9 и диод сброса 6 запирается. Постоянная времени заряда емкости 10 выбирается так, чтобы в течение очередного процесса накопления напряжения на емкости ячейки 2 потенииал анода диода сброса 6 оставался более низким, чем потенциал его катода.

Разрядная емкость 11 перезаряжается до напряжения -Е. При этом на анод диода компаратора 4 поступает напряжение с выхода резисторного делителя напряжения 12, равное напряжению питания --tl, умноженно.му на коэффициент деления резисторного делителя 12. Импульсы, поступающие на вход усилигеля-ограничителя 1, после переключения триггера 8 виовь дискретно увеличивают напряжение на ем.кости накопительной ячейки 2.

Срабатывает комиаратор 4. После срабатывания компаратора прошедший через него отрицательный перепад напряжения поступает на вход «1 триггера 8. При этом триггер переключается, потенциал на его перво.м выходе становится приблизительно равным напряжению питания -, а потенциал на его втором выходе - равным нулю. В результате этого диод сброса 7 открывается, емкость накопительной ячейки и разрядная емкость // перезаряжаются.

Емкость накопительной ячейки 2 разряжается при этом практически до нуля, и схема возвращается в исходное состояние. импульсов всей схемы равен при одинаковых коэффициентах деления резисторных делителей напряжения удвоенному коэффициенту деления накопительной ячейки 2. В обоих вариантах устройства допускается разброс величины емкостей накопительных ячеек больший, чем в известном устройстве, при одинаковых коэффициентах деления частоты. По данным эксперимента быстродействие устройства при использовании в триггере Т ранзисторов типа IT 311 и IT 313 превышает 20 Мгц при изменении величины напряжения питания от 7 до 21 в. Предмет .изобретения 1. Устройство для деления частоты следования и формирования импульсов, содержаш,ее входной усилитель-ограничитель, одну или две емкостные накопительные ячейки, диодные компараторы, цепи сброса, генератор сбрасываюш,его и выходного импульсов, отличающееся тем, что, с целью повышения быстродействия и надежности при коэффициенте деления, большем скважности выходных импульсов, устройство снабжено триггером, вход установки «О которого подключен к выходу первого. ;: пход установки «1 - к выходу второго дподного компаратора, входы которых подключены соответственно и раздельно к выходам первой и второй емкостных накопительных ячеек, входы которых подключены к выходу входного усилителя-ограничителя, при этом квыходам первой и второй емкостных накопительных ячеек подключены соответственно аноды первого и второго диодов сброса, катоды которых подключены соответственно к первому и второму выходам триггера. 2. Устройство по п. 1, отличающееся тем, что входы первого и второго диодных компараторов подключены совместно к выходу емкостной накопительной ячейки, при этом к выходу емкостной накопительной ячейки подключены совместно катоды первого и второго диодов сброса, аноды которых подключены через разрядные ем.кости соответственно к первому и второму выходам триггера и через резисторы к отдельному источнику постоянного напряжения, ,а аноды диодов первого и второго компараторов подключены соответственно к выходам первого и второго резисторных делителей, включенных в цепи коллекторов транзисторов триггера между его соответствуюн ими выходами и источником постоянного напряжения.

jLf-1кцттги.тЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ЧИСЛА ИМПУЛЬСОВ | 1972 |

|

SU353357A1 |

| Способ преобразования перемещения в напряжение и устройство для его реализации (его варианты) | 1981 |

|

SU1026081A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| ДИАПАЗОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1967 |

|

SU224668A1 |

| Импульсная лазерная установка для обработки материалов | 1989 |

|

SU1683937A1 |

| Ячейка памяти | 1975 |

|

SU624292A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| АМПЛИТУДНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 2001 |

|

RU2190230C1 |

| Интегратор | 1986 |

|

SU1376107A1 |

Вх.

Ч

Даты

1969-01-01—Публикация