(54) ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881864A1 |

| Фазоимпульсный счетчик | 1975 |

|

SU524323A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Измеритель динамических характеристик | 1987 |

|

SU1532901A1 |

| Устройство для задержки импульсных сигналов | 1980 |

|

SU921047A1 |

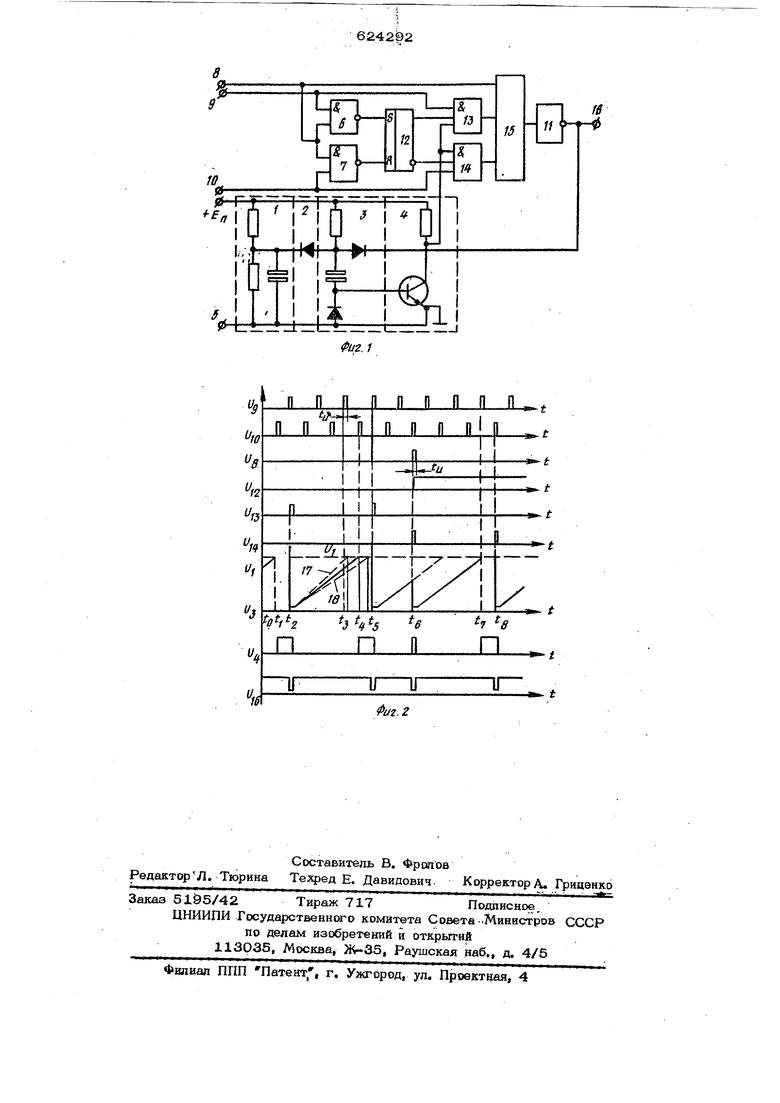

Изобретение относится к вычислительной технике и может использовать- f ся в устройствах автоматики и телемеханики. Известны ячейки памяти с фазоимпульо ным представлением информадии, построе ные на базе релаксационного генератора. Одна из известных ячеек памяти содержит емкостный накопитель, диодный компаратор, источник опорного напряжения, транзисторный ключ и инвертор сброса p Для получения большого числа, устойчивых состояний питание емкостного накопителя осуществляется от высоковольтног источника питания или от низковольтного источника через стабилизатор тока. Это затрудняет реализацию ячейки памяти на интегральных схемах. Кроме того, наден нiзя работа такой ячейки памяти обеспе чивается. в сравнительно узком диапазоне дестабилизирующих факторов (температуры и частоты.синхронизации). Из извесгных ячеек памяти наиболее близкой к изобретению по технической сущности я&ляется ячейка памяти, содержащая последовательно соединенные элемент коррекции, компаратор, накопительный элемент и ключ, подключенные к шине нулевого потенциала, элементы И-НЕ, одни аходы которых соединены с одной из управляющих шин, другие входы - с другими управляющими шинами, и инвертор, соединенный с накопительным зяементом |Г2, Формирование выходных импульоов с ф&зой, соответствующей записанному в ячейку памяти числу, производится транзисторным ключом на - синхроимпульсах, частота следования которых равна опорной последовательности импульсов. При этом каждому h -выходному импульсу должно предшествовать сравнение напряжений на емкостном накопителе и цепи самонастройки, т. е. момент компарацИй по времени должен попадать на паузу |:| между (n-l )--синхроимпульсом Ьп -Чгде Т - период следования импульсов син:: фонизации; fc ц - длительность синхроимпульса В этой- ячейке памяти выполнение указанного условия соблюдается только в узком диапазоне изменений внешней температуры, питаюишх напряжений и частоты импуп сов синхронизации. Это ограничивает применение известной ячейки памяти в про мьшшенных устройствах вычислительной техники, автоматики и телемеханики, работающих , как правило, в усповиях интенсивных помех и одновременном во&действии различного рода дестабилизирующих факторов. Целью изобретения является повь шение надежности за счет расширения области компарадии. В описываемой ячейке это достигается тем, что она содержит триггер, элементы И и элемент ИЛИ, которото соединен с инвертором, вхехды - одной из управляющих шин и вы ходами элементов И, первые входы котфых подключены к другим управляющим шинам, вторые входы - к ключу, а чретьн входы - к В1лходам триггера, входы которого соединены с выходами алемевтов И-НЕ.. На фиг. 1 представлена принципиальная схема описываемсй ячейки; на фиг. 2 временные диаграммы, поясняющие ее работу, Ячейка памяти содержит последователь но соединенные элемент 1 коррекции, f.ot/ паратор 2, накопительный элемент 3 я ключ 4, подключенные к щине 5 нулевого потенциала, элементы И-НЕ 6 и 7, одни входы которых соединены с одной из утфав ляющих ШИН; 8, а другие входы - с гими управляющими шинами 9 и 1О, инвертор 11, соединенный с накопительным элементом 3, триггер 12 , элементы И 13 в 14 и элемент ИЛИ 15, вь1ход которого соединен с инвертором 11, входы с од1шй из управляющих шин 8 и выходами элементов И 13 и 14, первые входы которыхподключены к другим управляющим шинам 9 и 10, вторые входы - к ключу 4, а третьи входы - к выходам Триггера i2, входы которого соединены с выходами элементов И-4{Е 6 и 7. На выход 16 ячейки памяти подается периодическая последовательность импульсов с фазой, соответствующей хранимому На фиг. 2 приняты обозначения: ч н LL-нечетные и четные импульсы J -to опорной частоты, подаваемые на шины 9 и 10} (JQ - импульсы записи информации, син: ронизированныв импульсами опорной частоты; напряжение на инверсном выходе тригтера 12; M(jH U/i выходные импульсы элементов И 13 и 14; и - напряжение делителя элемента 1 коррекции; напряжение на накопительном элементе 3; 0л - напряжение на выходе ключа 4i импульсы на выходе 16 ячейки памяти; ti. Т - длительность импульса записи и период следования импульсов частоты (частота синхронизации); 17 и is - предлагаемые эпюры напряжений на накопительном элементе 3 при наличии дестабилизирующих факторов. Работа ячейки памяти с щестыо устойчивыми состояниями { П 6) , в KOTt ptrii предварительно записано число . При отсутствии сигналов на шине 8 записи информации элементы И-НЕ 6 и 7 - заперты, а импульсы с фазами це Четной и фазами четней последовательностей опар ной частоты, поступающие на щнны 9 и 10, не измешдат состояния триггера 12. На прямом выходе этого триггеров 12 присутствует высокий положительный потенциал, а на инверсном - нулевой, благодаря элемент . И 13 подготовлен, а элемент И 14 заперт по втч)ым входам. Пусть в момент времени о вапряжение U на накопительном зиемевте 3 линейно нарастает, тогда на выходе ключа 4 формируется нулевой псхгевцнал. который в свою очередь по cojy ветствующим входам элементы И 13 и 14, и следовательно, предотвращает iiocтупление импульсов частоты через элемент ИЛИ 15 на вход инвертора 11, В момент врекюни t напряжение Цд достигает уровняй делителя эдв мента 1 коррекции, заряд накшительнрго элемента 3 прекращается и на выходе ключа 4 появляется потещиал. При этом элемент И 13 подготавливает ся к пропуску импульса с фазой нечетной оследовательности, так как на Bftopcu erg вход ранее был подан разрешающий П1Й«ициал с триггера 12, а элемент И 14 остается запертым. Импульс с фазой нечетной последовательности с шины 9, пройдя через алемвнты 13 и 15, в моменту времени i2 .вызывает появление отрЕцательного импульса ва выходе инвертора 11, В результате емкость Н19копител1гного элемента 3 раздражается до поте циала, близкого к нулю, а по истечении 56 времени i:и действия этого импульса снова начинвется ее линейный заряд. Запись информации осуществляется подачей на шину 8 импульса, синхрониэ рованного опорной частотой. Этот импуль проходит через элемент ИЛИ 15 к инвертор 11 на выход 16 ячейки памяти и одновременно разряжает емкость накопительного элемента 3, При этом в зависимости от совпадения сигналов на входах апементовИ-НЕ 6 или 7 триггер 12 устанавливается в единичное или нулевое состояние, обеспечивая в дальнейшем про хождение нечетных или четных импульсов опорной частоты на разряд накопительного элемента 3 через апементы 13 иян 14, 15 и инвертф 11. В качестве примера на фиг. 2 в момент времени i: показана запись числа в ячейку памяти. Начиная с момента времени все процессы в схеме проиоходят с тем отличием, что триггер 12 выдает высокий уровень напряжения с инверсного выхода, а и разряд накопительного элемента 3 осуществляются соответственно в моменты t и X одновременно с появлением импульсов опорной частоты с фазами нечетной и чет ной последовательностей. При повышении-или пониженвн темпе- ратуры внешней среды параметры векопительн( элемента, ключа 4 в дфугнх элементов схемы могут изменяться так, что участок заряда 1шксшительного зпемента оказьюается либо выше (эпюра 17), либо ниже (эпюра 18) гpaфнкa UJ и соответственно моменты крмпаратшсдви нутся относительно метки -t aneBo(tj) или BnpaBo(tf). Из временных диаграмм видно, что ячейка памяти сохраняет записанное в нее число при условии попадания моментов компараоии между двумя соседни1Л1 импульсами четной или нечетв1Я1 после2довательности. Продолжительность этого интервала составляет 2Т- t,, , т. е. ревышает на один период интервал (Т- t4f) компарации в известной ячейке. Таким образом, необходимым и достаточным условием надежной работы ячейки памяти является первоначальная установка . такого уровня напряжения - делителя элемента 1 коррекции, чтобы заряд накопительного элемента 3 прекращался в области (ti-l) - TaKTOBWO импульса опц йой частоты, начиная с момента заряда. .Формула изобретения Ячейка памяти, содержаишя последовательна соединенные элемент коррекции, компаратор, накопительный элемент и ключ, пощшюченные к шине нулевого потенциа да, элементы И-НЕ, одни входы которых соединены с одной из управляющих шин, другие входы - с друтами управляющими шинами, и инвертсф , соединенный с накопительным элементом, отличающаяся тем, что, с целью повышения надежности ячейки, она содержит триггер, элементы И и элемент ИЛИ, выход которого соединен с инвертором, входы - с одной из управляющих шин и выходами элементов И, первые входы подключены к другим управляющим шинам, вторые входы - к ключу, а третьи входык выходам триггера, входы которого соединены с выходами элементе И-НЕ. Источники ннфсфмшхии, принятые во внимание при экспертизе: 1.Журнал Механизация и автоматизация управления , 1970, М 3, с. 34-35. 2.Ситников Л. С. Многоустойчнвые элементы в цифровой измерительной текинке, Киев, Наукова думка , 1970, с. 48-49.

Авторы

Даты

1978-09-15—Публикация

1975-12-30—Подача