с

СО

О)

0Uil

ки 2-5, 11, 12, пары 6, 7 последовав тельно соединенных ключей, дополнительные ключи 8-10, генератор 13 импульсов, распределитель 14 импульсов делитель 15 частоты, дифференцирующую КС-цепь 16, инвертор 17, элемент ИЛИ 18, элемент РШИ-НЕ 19, элемент И 20, разделительные диоды 21, 22, накопительные конденсаторы 23-30. Изобретение позволяет повысить точность процесса интегрирования при

периодических режимах работы за счет устранения паразитных зарядов на накопительных конденсаторах 23, 24 за- рядно-разрядных ячеек 2, 3, обусловленных билинейными свойствами последних. Введение дополнительньк ключей 8 - 10 зарядно-разрядных ячеек 11, 12, накопительных конденсаторов 29, 30 позволяет устранить влияние паразитных зарядов на всех накопитель- ш,х конденсаторах. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Интегратор | 1985 |

|

SU1251112A1 |

| Устройство для геоэлектроразведки | 1985 |

|

SU1343378A1 |

| Устройство для усреднения импульсной последовательности | 1988 |

|

SU1524071A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Интегратор с весовым усреднением сигналов | 1987 |

|

SU1583859A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Гидрологический измеритель скорости звука | 1985 |

|

SU1255871A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в различных устройствах в качестве базового узла при построении, например, электрических фильтров. Цель изобретения - повьшение точности интегрирования ;.; при изменении интегрируемой функции.. Интегратор содержит операционный усилитель 1, зарядно-разрядные ячей

Изобретение относится к автоматике и вычислительной технике и может найти применение в различных устройствах в качестве базового-узла при построении, например, электрических фильтров.

Цель изобретения - повьшение точности интегрирования при изменении интегрируемой функции.

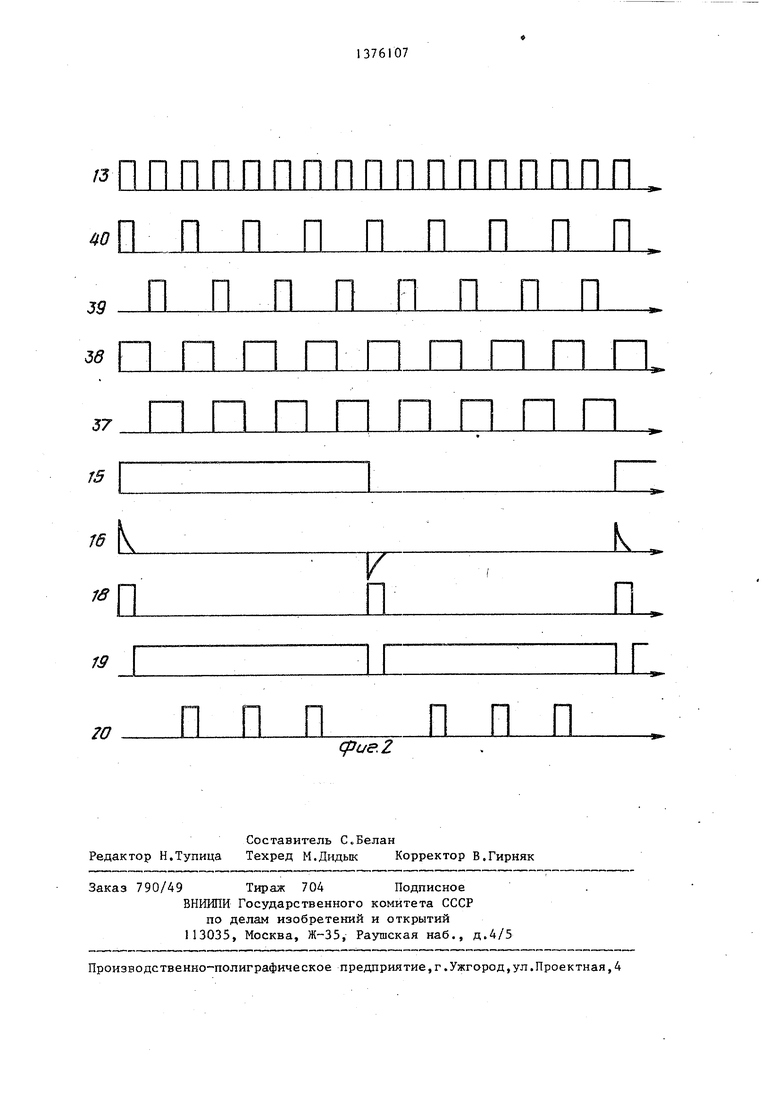

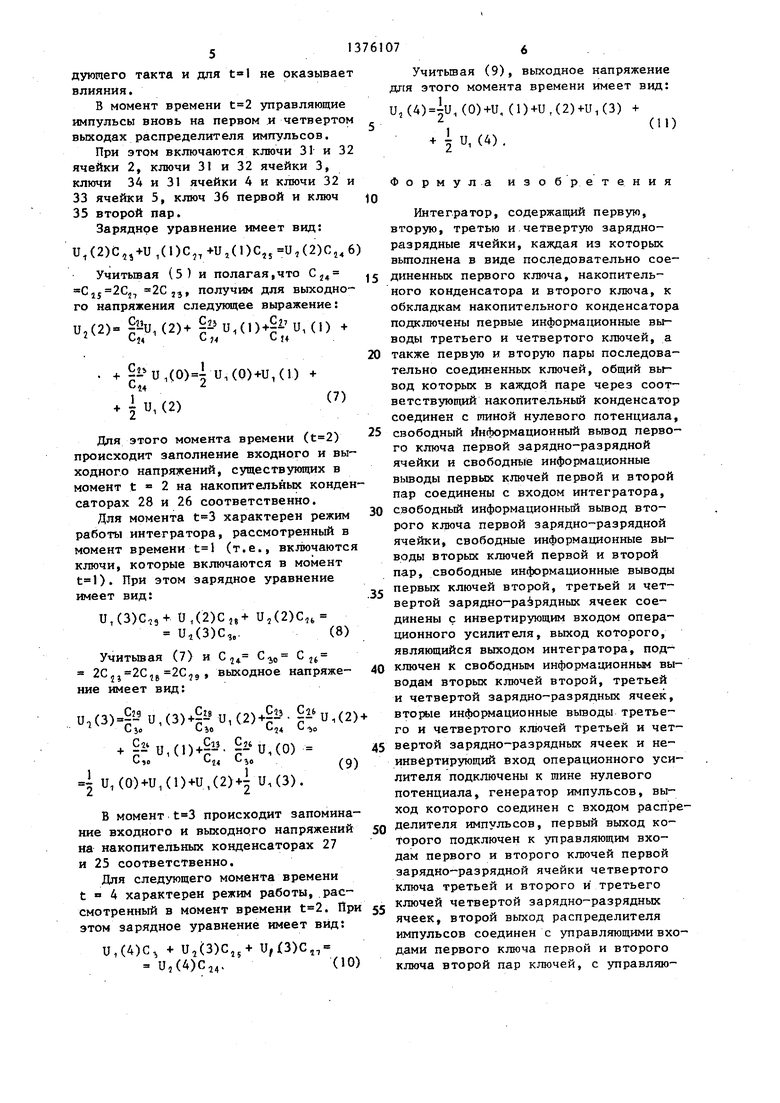

На фиг.1 представлена схема ин- тегратора; на фиг.2 - временная диаграмма его работы.

Интегратор (фиг.1) содержит операционный усилитель 1, зарядно-раз- рядныб ячейки 2-3, первую 6 и вторую 7 пары последовательно соединенных ключей, три дополнительных ключа В - 10, дополнительные зарядно-разрядные ячейки 11 и 12, генератор 13 импульсов, распределитель 14 импульсов, де литель 15 частоты (на триггерах), дифференцирующую RC-цепь 16, инвертор 17, элемент ИЛИ 18, элемент ИЛИ- НЕ 19, элемент И 20, разделительные диоды 21 и 22, накопительные конденсаторы 23-30.

Каждая зарядно-разрядная ячейка 3-5 и 11 и 12 содержит первый 31, второй 32, третий 33 и четвертый 34 ключи, каждая пара 6 и 7. последовательно соединенных ключей состоит из ключей 35 и 36. .

Распределитель 14 импульсов содержит триггеры 37 и 38 и элементы И 39 и 40.

Интегратор работает следующим образом.

15

5

0

. 5

20

25

30

На вход интегратора подается сигнал, подлежащий интегрированию. Распределитель 14 импульсов представляет из себя регистр сдвига на тактируемых фронтом триггерах 37 и 38, которые изменяют свое первоначальное состояние при изменении переднего фронта тактового импульса, поступающего на их первые входы в соответствии с уровнем потенциала, находящимся на их вторых входах. На выходах первого и второго элементов И 39 и 40, а также на выходах первого 37 и второго 38 триггеров сформируются соответственно противофазные управляющие импульсы (фиг.1 и 2).

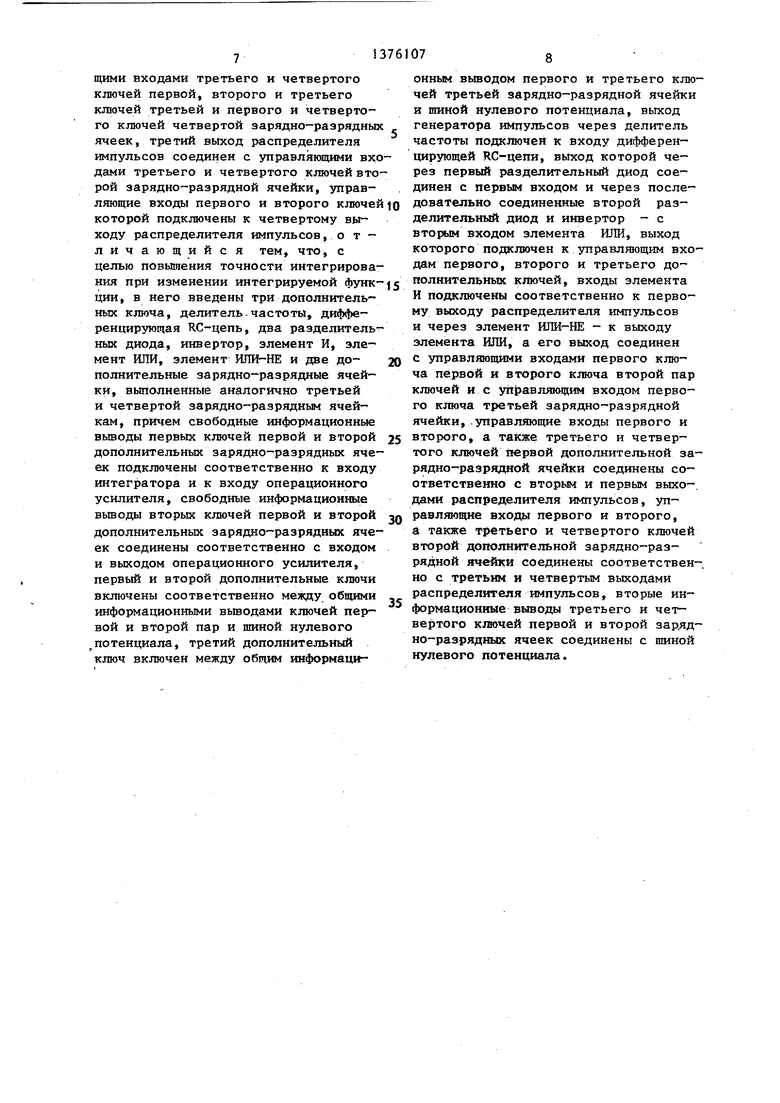

Длительности импульсов на первом и втором выходах распределителя 14 равны длительности тактовых импульсов с выхода генератора 13 импульсов, а длительность импульсов на третьем и четвертом выходах равна периоду импульсов генератора 13 (фиг.2).

В момент t О тактовый импульс генератора 13 по переднему фронту включает делитель 15 частоты, на выходе которого сформирован высокий уровень, длительность которого определяется коэффициентом деления делителя 15, Сигнал с выхода делителя 15 частоты поступает на вход дифферен- и 1рующей КС-цепи 16, которая формирует положительный импульс, по длительности не превосходящий длитель- кюсть импульса с генератора 13 (фиг.2), который через разделительный диод 21 поступает на один из входов элемента

ИЛИ 18, с выхода которого в момент t О снимается короткий управляющий импульс, поступающий на входы элемента ИЛИ-НЕ 19, на выходе которого в этом режиме сигнал отсутствует. Выход элемента ИЛИ-НЕ 19 соединен с одним иэ входов элемента И 20 (фиг.1), на другой вход которого поступает сигнал с первого выхода рас- пределителя 14, причем этот сигнал в момент t О имеет высокий уровень Таким образом, в момент t О на входы элемента И 20 поступают сигналы О, 1, а на его выходе сигнал отсутствует.

Импульс с первого выхода распределителя 14 поступает на управляющие входы ключей 31 и 32 ячейки 2, ключа 34 ячейки 4, ключей 32 и 33 ячейки 5 а также ключей 33 и 34 ячейки I1. №тульс с выхода элемента ИЛИ 18 включает дополнительные ключи 8-10. Ключи 35 и 36 в этот момент не вклю- чены, так как на выходе элемента И 20 низкий уровень напряжения. Управляющие импульсы с выхода триггера 38 включают ключи 31 и 32 ячейки 3 и ключи 33 и 34 ячейки 12. Включение в момент t О дополнительных ключей 8-10 приводит к разряду накопительных конденсаторов 27, 28 и 25, а также конденсаторов 29 и 30. Таким образом, в момент t О заряды на накопительных конденсаторах 27, 28, 25, 29 и 30 равны нулю и готовы к работе в соответствующем изменении входной функции, не внося искажений в выходные значения сигнала.

Для этого момента времени () можно записать зарядное уравнение

С„и,(0) C,4Ui(0), (1) где и(0) - напряжение на входе

интегратора (при ); и5(0) - напряжение на выходе

интегратора;

2 -14 емкости конденсаторов 23 и 24.

В этот момент времени () заряд образовавшийся на конденсаторе 26, запоминается и не оказывает влияния на выходной сигнал.

На выходе интегратора в момент будет напряжение .

и,(0) U,(0)

bj

Полагая 2С5 С, получим

и,(0) 1Т,(0) .

(3)

/ 2

В следующий момент времени с приходом второго тактового импульса с выхода генератора 13 импульсов управляющий импульс на первом и четвертом выходах распределителя 14 отсутствует, а появляются импульсы на втором и третьем его выходах. При этом, на выходе дифференцирующей RC- цепи 16 сигнал отсутствует, на выходе элемента ИЛИ 18 сигнал нулевого уровня, на выходе элемента ИЛИ-НЕ 19 сигнал высокого уровня. Этот импульс поступает на первый вход третьего элемента И 20, на второй вход которого в этот момент времени импульс не поступает (фиг.1), т.е. на выходе элемента И 20 нулевой уровень.

Начиная с момента t 1 и до момента окончания сигнала с выхода делителя 15 частоты, т.е. до окончания длительности первого периода входной периодической функции, подлежащей интегрированию, на первый вход элемента И 20 всегда поступает импульс высокого уровня с выхода элемента ИЛИ- НЕ 19, тем самьм синхронизируя работу элемента И 20 с работой элемента И 40. Таким образом, в момент управляющие импульсы существуют на втором и третьем выходах распределителя 14. При этом включаются ключи 33 и 34 ячеек 2 и 3, ключ 35 и ключ 36 соответственно пары 6 и 7, ключи 32 и 33 ячейки 5, ключи 31 и 32 ячеек П и 12.

В этот момент времени заряды, накопленные в момент в накопительных конденсаторах 23 и 24, полностью разряжаются и готовы для работы в следующем такте. Это полностью устраняет билинейный эффект.

Зарядное уравнение для этого момента времени следующее:

иЛОс„+ и,,(0)с,с u,(i)Cjo. (4)

Учитывая,что ил(0)иХО) - , и поЬ ц

лагая, что С„ С, 0,, 1/2 С 1/2 Cjj , выходное напряжение для момента t 1 имеет вид:

, 50

55

U(l)

,(1) -ь u,(o) i

Ct

Clo

I ило) -н I и, (1),

74

го

(5)

Заряд, образовавшийся на конденсаторах 25 и 27, запоминается до еле-

дующего такта и для t не оказывает влияния.

В момент времени управляющие импульсы вновь на первом и четвертом выходах распределителя импульсов.

При этом включаются ключи 31 и 32 ячейки 2, ключи 31 и 32 ячейки 3, ключи 34 и 31 ячейки 4 и ключи 32 и 33 ячейки 5, ключ 36 первой и ключ 35 второй пар.

Зарядное уравнение имеет вид:

U,(2)C,j+U,(l)C,,+U,(l)C,,(2)Cj,6

Учитьгоая (5) и полагая,что Cj 2Cjj, получим для выходного напряжения следующее выражение:

и,(2) рЧ(2)-ь ,(l), (О +

С}4 С л с 4

Сг

+ и,(0) и,(0)+и,(1) +

«

+ 5 Л2)

(7)

Для этого момента времени () происходит заполнение входного и выходного напряжений, существующих в момент t 2 на накопительных конденсаторах 28 и 26 соответственно.

Для момента характерен режим работы интегратора, рассмотренный в момент времени (т.е., включаются ключи, которые включаются в момент ). При этом зарядное уравнение имеет вид:

и,(3)С,з+ UX2)Cjj+ U,(2)C,t

U,(3)C,.. (8)

С,. 0.. С

It

выходное напряже- 40

U,(3) - и,(3) и,(2)Ф- ,(2)-ь

Ljo Ijie 14 Ьс

+ p2- U,(l)+pi- ) -ч1 г - го /gN

1 U,(0)+U,(1)U,(2)+| и,(3).

В момент происходит запоминание входного и выходного напряжений на накопительных конденсаторах 27 и 25 соответственно.

Для следующего момента времени t 4 характерен режим работы, рассмотренный в момент времени . Йри этом зарядное уравнение имеет вид:

иХ4)с, + u,(3)Cj5+ и,О)с,,

и,(4)С24.(10)

Учитьшая (9), выходное напряжение для этого момента времени имеет вид:

и, (4)4иЛО)+и, (1)+и,(2)4-иДЗ) +

%(11)

+ и, (4) .

f

0

5

0 5

0

5

0

5

Формула изобретения

Интегратор, содержащий первую, вторую, третью и четвертую зарядно- рг13рядные ячейки, каждая из которых вьшолнена в виде последовательно соединенных первого ключа, накопительного конденсатора и второго ключа, к обкладкам накопительного конденсатора подключены первые информационные выводы третьего и четвертого ключей, а также первую и вторую пары последовательно соединенных ключей, общий вывод которых в каждой паре через соответствующий накопительный конденсатор соединен с тиной нулевого потенциала, свободный Информационный вывод первого ключа первой зарядно-разрядной ячейки и свободные информационные вьшоды первых ключей первой и второй пар соединены с входом интегратора, свободный информационный вьшод второго ключа первой зарядно-разрядной ячейки, свободные информационные выводы вторых ключей первой и второй пар, свободные информационные выводы первых ключей второй, третьей и четвертой зарядно-разрядных ячеек соединены с инвертирующим входом операционного усилителя, выход которого, являющийся выходом интегратора, подключен к свободным информацнонньм выводам вторых ключей второй, третьей и четвертой зарядно-разрядных ячеек, вторые инфОЕ 1ационные вьтоды третьего и четвертого ключей третьей и четвертой зарядно-разрядных ячеек и не- инвбртирующий вход операционного усилителя подключены к шине нулевого потенциала, генератор импульсов, выход которого соединен с входом распределителя импульсов, первый выход которого подключен к управляющим входам первого и второго ключей первой зарядно-разрядной ячейки четвертого ключа третьей и второго и третьего ключей четвертой зарядно-разрядных ячеек, второй выход распределителя импульсов соединен с управляющими входами первого ключа первой и второго ключа второй пар ключей, с управляющими входами третьего и четвертого ключей первой, второго и третьего ключей третьей и первого и четвертого ключей четвертой зарядно-разрядных ячеек, третий выход распределителя импульсов соединен с управляющими входами третьего и четвертого ключей второй зарядно-разрядной ячейки, управляющие входы первого и второго ключей которой подключены к четвертому выходу распределителя импульсов(Отличающийся тем, что, с целью повышения точности интегрирования при изменении интегрируемой функции, в него введены три дополнительных ключа, делитель-частоты, дифференцирующая RC-цепь, два разделитель- ных диода, инвертор, элемент И, элемент ИЛИ, элемент ШТИ-НЕ и две до- полнительные зарядно-разрядные ячейки, вьтолненные аналогично третьей и четвертой зарядно-разрядным ячейкам, причем свободные информационные выводы первых клочей первой и второй дополнительных зарядно-разрядных ячеек подключены соответственно к входу интегратора и к входу операционного усилителя, свободные информационные

ВЬШОДЫ вторых ключей первой и второй

дополнительных зарядно-разрядных ячеек соединены соответственно с входом и выходом операционного усилителя, первый и второй дополнительные ключи включены соответственно между общими информационными вьюодами кгаочей первой и второй пар и шиной нулевого потенциала, третий дополнительный ключ включен между общим информационным выводом первого и третьего ключей третьей зарядно-разрядной ячейки и шиной нулевого потенциала, выход генератора импульсов через делитель частоты подключен к входу дифференцирующей RC-цепи, выход которой через первый разделительный диод соединен с первым входом и через последовательно соединенные второй разделительный диод и инвертор - с вторым входом элемента ИЛИ, выход которого подключен к управляющим входам первого, второго и третьего дополнительных ключей, входы элемента И подключены соответственно к первому выходу распределителя импульсов и через элемент ИЛИ-НЕ - к выходу элемента ИЛИ, а его выход соединен с управляющими входами первого ключа первой и второго ключа второй пар ключей НС управляющим входом первого ключа третьей зарядно-разрядной ячейки,.управляющие входы первого и второго, а также третьего и четвертого ключей 1{ервой дополнительной зарядно-разрядной ячейки соединены соответственно с вторьм и первым выхо-. дами распределителя импульсов, управляющие входам первого и второго, а также третьего и четвертого ключей второй дополнительной зарядно-разрядной ячейки соединены соответственно с третьим и четвертым выходами распределителя импульсов, вторые информационные выводы третьего и четвертого ключей первой и второй зарядно-разрядных ячеек соединены с шиной нулевого потенциала.

зППППППППППППППППП

но

п п п п п п

cpae.Z

п п

| Решающий усилитель | 1983 |

|

SU1144122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-07-14—Подача