Предложенное устройство относится k средствам приборостроения, автоматики, вычислительной техники и предназначено для обработки информации, поступающей от частотных датчиков и других объектов, выходным параметром которых служит частота электрических сигналов.

Известен умножитель частоты, содержащий блок калиброванных частот, блок формирования выходной частоты, блок переключения пределов, коммутатор, формирующее устройство, дифференцирующий усилитель, регистр, счетчики, схемы совпадения и сборки.

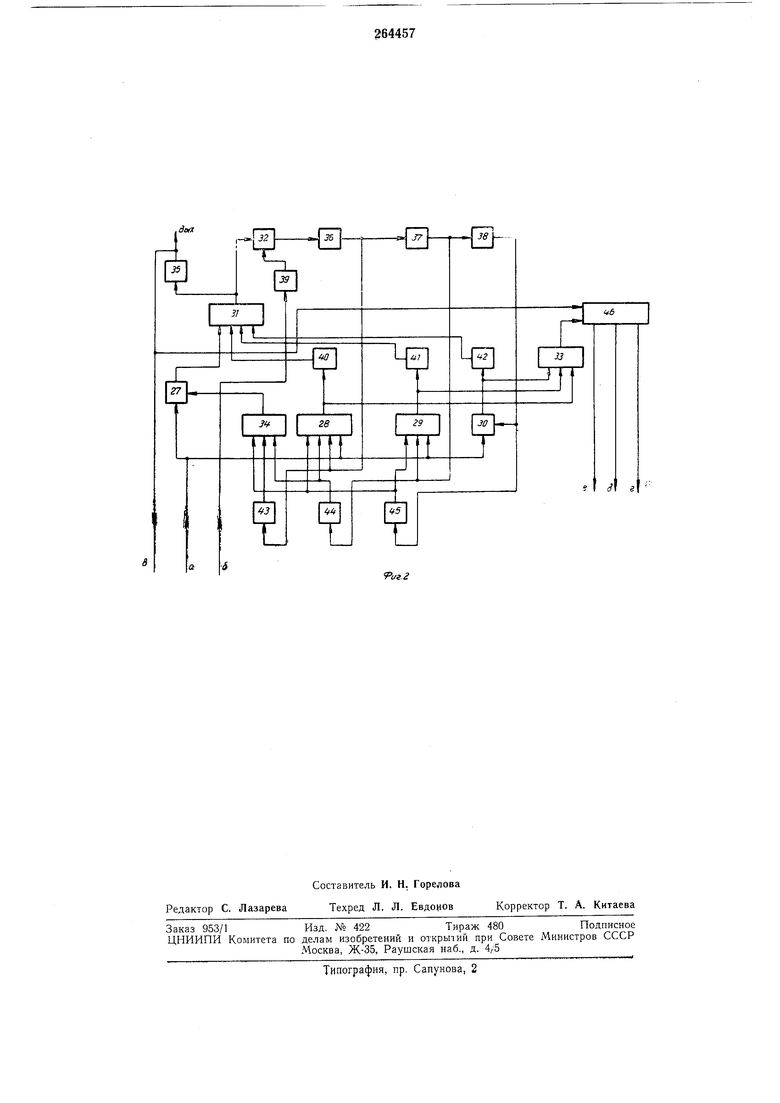

Предложенное устройство отличается тем, что блок формирования выходной частоты содержит логические схемы, коммутатор, одновибратор и последовательно соединенные делители частоты, выходы первого из которых через схему сборки, второй вход которой также через схему сборки, соединенную со схемами исключения первого, двух первых и трех первых импульсов, и через схему совпадения соединен со входом блока формирования выходной частоты. Выходы делителей подключены через инверторы к схеме сборки, соединенной со схемой совпадения, расположенной на входе блока формирования выходной частоты, а также к схемам совиадения, ко входам которых также нодключены выходы делителей частоты и вход блока формирования выходной

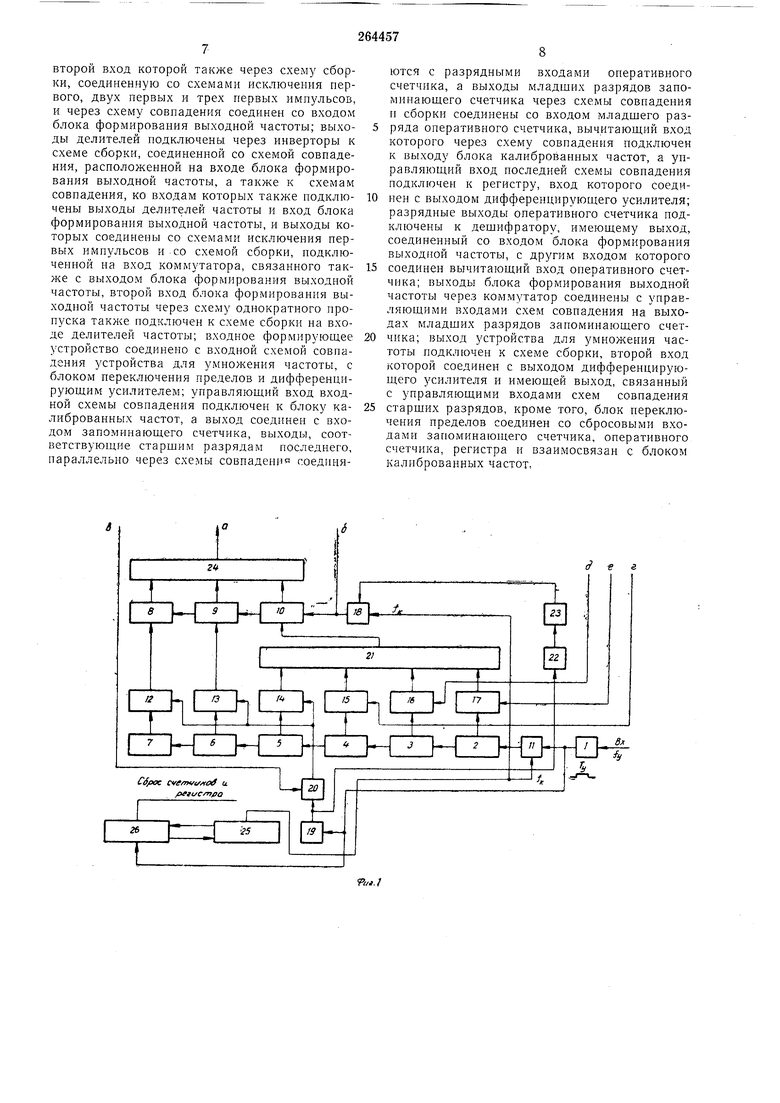

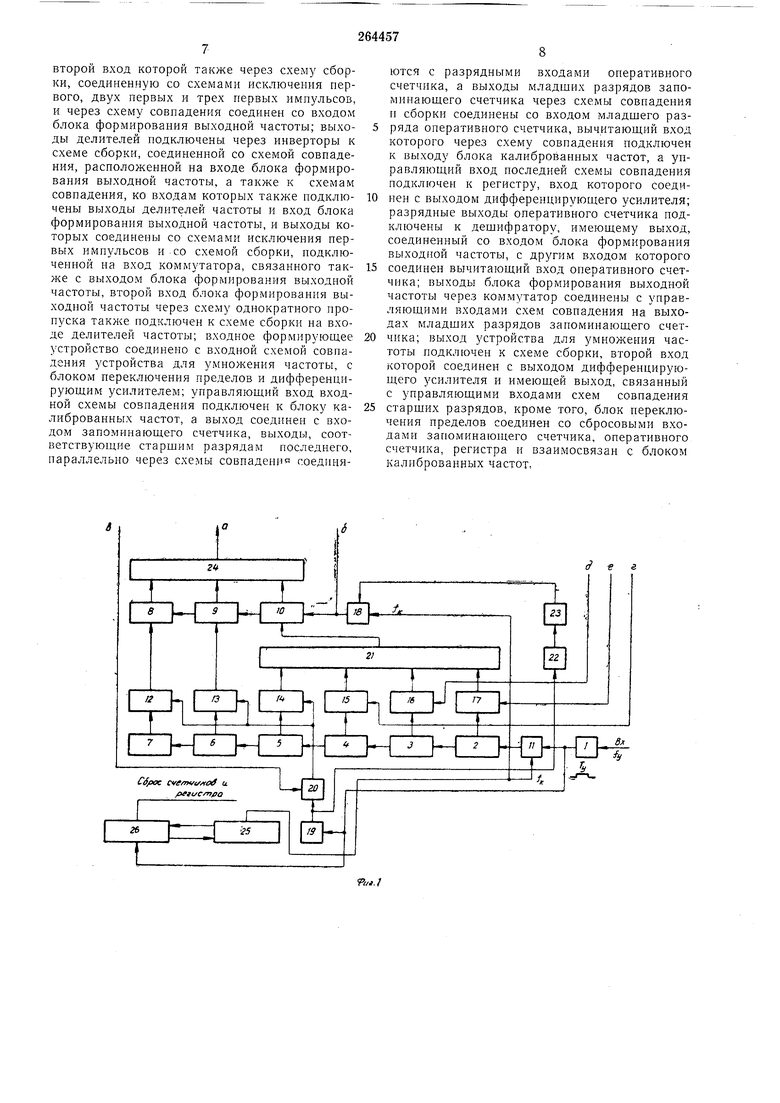

частоты, и выходы которых соединены со схемами исключения первых импульсов и со схемой сборки, подключенной на вход коммутатора, связанного также с выходом блока формирования выходной частоты, второй вход блока формирования выходной частоты через схему однократного пропуска таклсе подключен к схеме сборки на входе делителей частоты. Входное формирующее устройство соединено с входной схемой совпадения устройства для умножения частоты, с блоком переключения пределов и дифференцирующим усилителем. Управляющий вход входной схемы совпадения иодключен к блоку калиброванных частот, а выход соединен с входом запоминающего счетчика, выходы, соответствующие старшим разрядам последнего, параллельно через схемы совпадения соединяются с разрядными входами оперативного счетчика. Выходы младших разрядов запоминающего счетчика через схемы совпадения и сборки соединены со входом младщего разряда оперативного счетчика, вычитающий вход которого через схему совнадения подключен к выходу блока калиброванных частот, а управляющий вход пследпей схемы совпадения подключен к регистру, вход которого соединен с выходом дифференцирующего усилителя. Разрядные выходы оперативного счетчика иодключены к дешифратору, имеформирования выходной частоты, с другим входом которого соединен вычитающий вход оперативного счетчика. Выходы блока формирования выходной частоты через коммутатор соединены с управляющими входами схем совпадения на выходах младших разрядов запоминающего счетчика. Выход устройства для умножения частоты подключен к схеме сборки, второй вход которой соединен с выходом дифференцирующего усилителя, и имеющей выход, связанный с управляющими входами схем совпадения старших разрядов. Кроме того, блок переключения пределов соединен со сбросовыми входами запоминающего счетчика, оперативного счетчика, регистра и взаимосвязан с блоком калиброванных частот. Это позволяет уменьшить погрешность умножения и снизить частотные требования к элементам схемы. На фиг. 1 изображено предложенное устройство; на фиг. 2 показан блок формирования умноженной частоты. Описываемое устройство содержит формирующее устройство 1, счетные декады 2-7 запоминающего счетчика и декады 8-10 оперативного счетчика, схемы 11-18 совпадения, дифференцирующий усилитель 19, схемы 20 и 21 сборки, линию 22 задержки, регистр 23, дешифратор 24, блок 25 калиброванных частот, и блок 26 переключения пределов. Блок формирования умноженной частоты состоит из схем 27--30, совпадения, схем 31-34 сборки, одновибратора 35, делителей 36-38 частоты, схем 39 однократного пропуска, схем 40 исключения первого импульса, схем 41 исключения двух первых импульсов, схем 42 исключения трех первых импульсов, инверторов 43-45 и коммутатора 46. Устройство работает следующим образом: Предположим, что необходимо спроектировать умножитель со следующими техническими параметрами: . Диапазон умножаемых частот от 1 до 1000 гц. Погрешность умножения, %: 0,001-для поддиапазона от 1 - 10 гц 0,01-для поддиапазона 10-100 гц 0,01 -для поддиапазона от 100-1000 гц. Исходя из заданной величины коэффициента умножения , принимаем десятичную систему исчисления, так как /(тз 1000. Положение запятой выбирается между третьим и четвертым разрядами. Поскольку погрешность умножения определяется ошибкой ± 1 импульс, при заполнении периода умножаемой частоты импульсами калиброванной частоты /к, то /к будет равна 1 мгц для двух первых поддиапазонов и 10 мгц для третьего поддиапазона. Формирующее устройство / вырабатывает прямоугольный сигнал, длительность которого равна ГУ, последний заполняется импульсами калиброванной частоты. Количество импульсов, прошедших за время, равное А, фиксируется запоминающим счетчиком, состоящим из двоично-десятичных декад 2-7. По заднему фронту сигнала Гу срабатывает дифференцирующий усилитель 19, и на общие входы разрядных схем 12-14 совпадения подается сигнал, обеспечивающий перепись числа, хранящегося в декадах 5-7, в декады 8-10 оперативного счегчика. В результате заполнения в запоминающем счетчике будет зафиксировано число, которое в общем виде может быть представлено, как N abcdef, где латинскими буквами обозначены значения чисел каждого отдельного разряда десятичного числа. Период умножаемой частоты может быть представлен в виде Ty(abcdef)rK для 1 мксек Ty {abcdef) мксек. Теоретическое значение периода выходной частоты при /(1000. TBbix.teop. fibc,def мксек. Необходимо осуществить формирование неравномерной последовательности импульсов, в которой каждый десятый период равен Тиык (abc + d) мксек, каждый сотый -Гвых (abc+d e) мксек и каждый тысячный - (abc + + f) мксек, а все остальные Твых (аЬс) мксек. Устройство осуществляет следующую последовательность операций. Период умножаемой частоты заполняется импульсами калиброванной частоты, количество последних фиксируется запоминающим счетчиком, основание системы счисления которого и положение фиксированной запятой определяют значение коэффициента умножения, а выходная частота формируется с помощью импульсов той же калиброванной частоты методом последовательного считывания информации с оперативного счетчика, в результате чего вырабатывается последовательность импульсов, в которой длительность периодов, имеющих номер, равный степени основания системы счисления при показателе степени, отличном от нуля, соответствует числу, записанному в разрядах, расположенных слева от запятой, плюс сумма чисел, записанных в разрядах, лежащих справа от занятой; количество членов суммы, начиная с нервого разряда, равно показателю степени основания, определяющей номер периода, а все остальные периоды соответствуют информации, записанной в левых разрядах запоминающего счетчика. Сигнал, снимаемый с выхода дифференцирующего усилителя 19, пройдя через линию 22 задержки, взводит регистр 23, который открывает схему 18 совпадения. Импульсы калиброванной частоты поступают на вычитаюЧерез время, равное 7с(аЬс)тк, оперативный счетчик устанавливается в нулевое состояние, а дешифратор 24 вырабатывает сигнал, поступающий по цеии а через схему 27 совпадения и схему 31 сборки на вход одновибратора 35 и параллельно через схему 32 сборки на вход делителя 36 частоты (на вход делителя 36 частоты подается первый импульс с выхода схемы 18 совпадения по цепи б).

Делители 36-38 частоты имеют коэффициент деления, равный основанию принятой системы исчисления (в данном случае 10), а подача дополнительного импульса на вход делителя 36 обеспечивает сдвиг на один импульс. Другими словами, с выхода делителя частоты снимается сигнал после девятого импульса выходной частоты, с выхода делителя 37 - после девяносто девятого импульса, а с выхода делителя 38 - после девятьсот девяносто девятого импульса.

Последнее необходимо для того чтобы десятые, сотые и тысячные периоды имели нужную длительность.

Имиульс с выхода одновибратора 35 будет первым сигналом выходной частоты, который по цепи b через схему 20 сборки подается на входы схем 12-14 совпадения, чем обеспечивается перепись числа аЪс в оперативный счетчик. Оиисанные операции повторяются девять раз.

После девятого импульса выходной частоты делитель 36 вырабатывает сигнал, открывающий схему 28 совпадения и блокирующий с помощью инвертора 43 схему 27 совпадения.

Формирование десятого периода выходной частоты производится в два этапа.

I.Аналогично формированию первых девяти периодов отсчитывается время, равное t (а&с) TK, при этом сигнал, снимаемый с дещифратора 24, поступает параллельно через схему 28 совпадеиня на вход схемы 40 исключения первого импульса (последняя первый сигнал не пропускает) и через схему 33 сборки - на вход коммутатора 46.

II.Коммутатор 46 вырабатывает сигнал, который по цепи г с помощью схем 15 и 21 осуществляет перепись числа в декаду 10 оперативного счетчика. После этого операция считывания повторяется, и второй импульс с дешифратора 24 по цепи: схема 28, схема 40 и схема 31 поступает на вход выходного одновибратора 35.

Таким образом, длительность десятого периода Гвых ( Тк.

Дальнейщие операции осуществляются аналогично.

Формирование сотого периода выходной частоты сходно с операцией отсчета десятого периода, но осуществляется с помощью схем 29, 41 и 31. После девяносто девятого импульса fsbix делитель частоты вырабатывает сигнал, блокирующий (с помощью инвертора 44) схемы 27 и 28 совпадения и открывающий схему 29 совпадения. Сначала производится считывание числа аЬс, переписанного из декад 5-7

в оперативный счетчик, затем коммутатор 46 вырабатывает сигнал, который переписывает число, равное d, из декады 4 в оперативный счетчик, и операция считывания повторяется.

Во время осуществления этих операций оперативный счетчик дважды устанавливается з нулевое положение, и дешифратор 24 вырабатывает два сигнала, которые не пропускаются схемой 41.

Под действием второго сигнала с дещифратора коммутатор выдает имплльс, поступаюпдпй по цепп g на вход схемы 16 совпадения и число е, записанное в декаде 3, гтереписывается в декаду 10. По окончании третьей операции считывания дещифратор 24 вырабатывает третий сигнал, который по цепи: схема 29 совпадения, схема 41 и схема 31 постугшет па вход выходного одновибратора 35. В результате сотый период будет равен Гцых (abc-{-d- -e).

Формирование тысячного периода /вых производится аналогично.

Для того чтобы исключить возможность срабатывания коммутатора от последнего импульса, с дешифратора при формировании десятого, сотого и тысячного периодов сигнал с выхода одиовибратора 35 подается на входы выходных схем совпадения коммутатора 46 и блокирует их.

Быстродействие предложенного устройства

будет определяться временем ожидания (интервал времени от момента запуска умножителя до момента появления сигналов /вых) и равно

0Ж 1 ,5 / иЫХ.

Для осуществления операций переключения калиброванной частоты, значение которой определяет величину погрешности умножения, введен блок выбора пределов, который производит оцепку значения входной частоты, и, если последняя более 100 гц, вырабатывается сигнал, обеспечивающий переключение калиброванной частоты с 1 до 10 мгц.

Поскольку операция оценки частоты и операция заполнения производятся одновременно, то в запоминающем и оперативном счетчиках накапливается ненужная информация, которая гасится (декады 2-7, 8-10 счетчиков и регистр 23 сбрасываются).

,-,

Предмет изобретения

Устройство для умножения частоты для электронно-счетных частотомеров, содержащее блок калиброванных частот, блок формирования выходной частоты, блок переключения пределов, коммутатор, формирующее устройство, дифференцирующий усилитель, регистр, счетчики, схемы совпадения и сборки, отличающееся тем, что, с целью уменьшения погрешности умножения и снижения частотных тре бований к элементам устройства, блок формирования выходной частоты содержит логичес кие схемы, коммутатор, одновибратор и последовательно соединенные делители частоты, вывторой вход которой также через схему сборки, соединенную со схемами исключения нервого, двух первых и трех первых импульсов, и через схему совпадения соединен со входом блока формирования выходной частоты; выходы делителей подключены через инверторы к схеме сборки, соединенной со схемой совпадения, расположенной на входе блока формирования выходной частоты, а также к схемам совпадения, ко входам которых также подключены выходы делителей частоты и вход блока формирования выходной частоты, и выходы которых соединены со схемами исключения первых импульсов и со схемой сборки, подключенной на вход коммутатора, связанного также с выходом блока формирования выходной частоты, второй вход блока формирования выходной частоты через схему однократного пропуска также подключен к схеме сборки на входе делителей частоты; входное формирующее устройство соединеио с входной схемой совпадения устройства для умножения частоты, с блоком переключения пределов и дифференцирующим усилителем; управляющий вход входной схемы совпадения подключен к блоку калиброванных частот, а выход соединен с входом запоминающего счетчика, выходы, соответствующие старшим разрядам последнего, параллельно через схемы совпадени соединяются с разрядными входами оперативного счетчика, а выходы младщих разрядов запоминающего счетчика через схемы совпадения и сборки соединены со входом младшего разряда оперативиого счетчика, вычитающий вход которого через схему совпадения подключен к выходу блока калиброванных частот, а управляющий вход последней схемы совпадения подключен к регистру, вход которого соедипен с выходом дифференцирующего усилителя; разрядные выходы оперативного счетчика подключены к дешифратору, имеющему выход, соединенный со входом блока формирования выходной частоты, с другим входом которого соединен вычитающий вход оперативного счетчика; выходы блока формирования выходной частоты через коммутатор соединены с управляющими входами схем совпадения на выходах младших разрядов запоминающего счетчика; выход устройства для умножения частоты подключен к схеме сборки, второй вход которой соединен с выходом дифференцирующего усилителя и имеющей выход, связанный с управляющими входами схем совпадения старщих разрядов, кроме того, блок переключения пределов соединен со сбросовыми входами запоминающего счетчика, оперативного счетчика, регистра и взаимосвязан с блоком калиброванных частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ СИГНАЛОВ | 1969 |

|

SU235107A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU259150A1 |

| ИНТЕРПОЛЯТОР | 1970 |

|

SU272415A1 |

| Электронные вторичные часы с цифровой индикацией | 1983 |

|

SU1170417A1 |

| Цифровые первичные часы | 1976 |

|

SU600508A1 |

| Цифровой низкочастотный частотомер | 1975 |

|

SU636553A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1972 |

|

SU425315A1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

| Устройство для вибросейсморазведки | 1987 |

|

SU1444687A1 |

| Кодовый трансмиттер для рельсовых цепей | 1987 |

|

SU1527062A1 |

tf е г

Даты

1970-01-01—Публикация