Известны устройства для умножения-частоты низкочастотных сигналов, содержащие входной блок, блок калиброванных частот, блок автоматического переключения коэффициента умножения, коммутатор, оперативный и запоминающие счетчики, блок формирования змноженной частоты, собирательные схемы и схемы совпадения.

Предложенное устройство отличается от известных тем, что в нем входной блок иодключен к двум схемам совпадения, выходы которых присоединены ко входам запоминающих счетчиков, а управляющие входы соединены с одним из входов входного блока, со входом блока автоматического переключения коэффициента умножения и с одним из выходов блока калиброванных частот, остальные выходы которого через коммутатор подключены к оперативному счетчику и ко входу блока формирования умноженной частоты, соединенного другими входами с выходами оперативного счетчика. Разрядные входы этого счетчика через матрицу сборок и схем совпадения подключены к выходам запоминающих счетчиков; выход схемы формирования умноженной частоты соединен с блоком калиброванных частот и со входами одноразрядного счетчика и схем совпадения, включенных между управляющими входами матрицы схем совпадения и выходами одноразрядного счетчика; выход

входного блока подключен ко входу блока автоматического переключения коэффициента умножения, выходы которого соединены с запоминающими и оперативными счетчиками и блоком калиброваиных частот.

Это позволило расщирить диапазон умножаемых частот, увеличить коэффициент умножения и повысить быстродействие устройства.

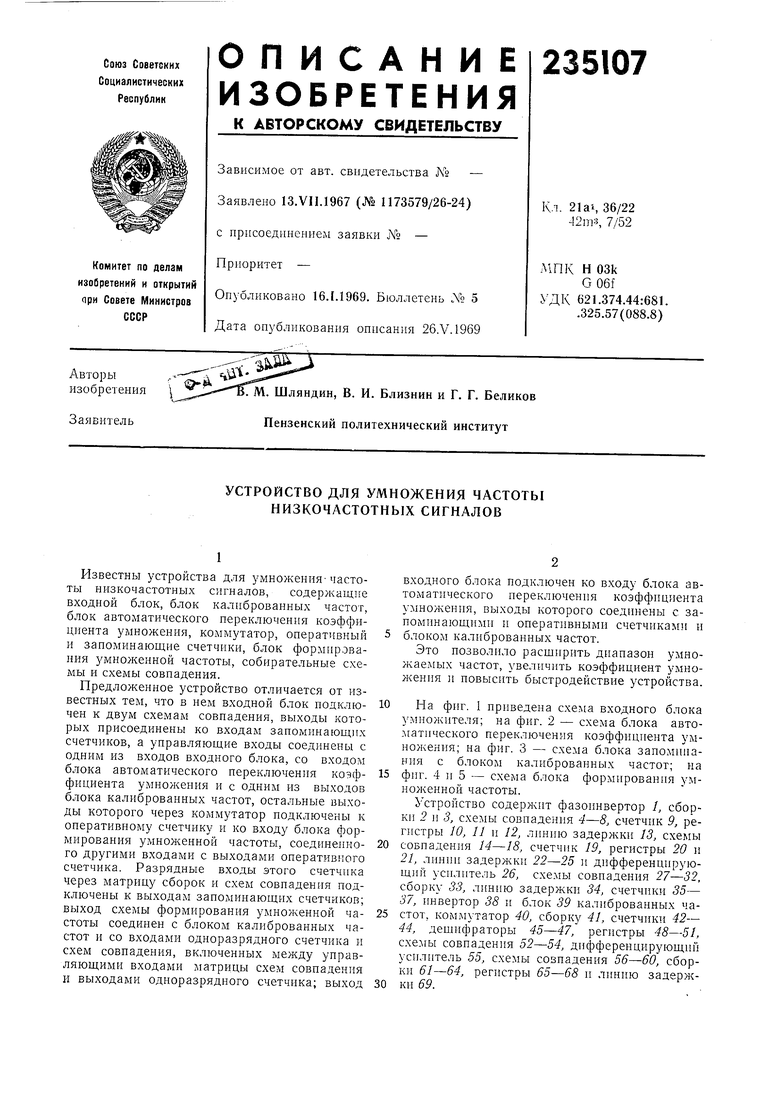

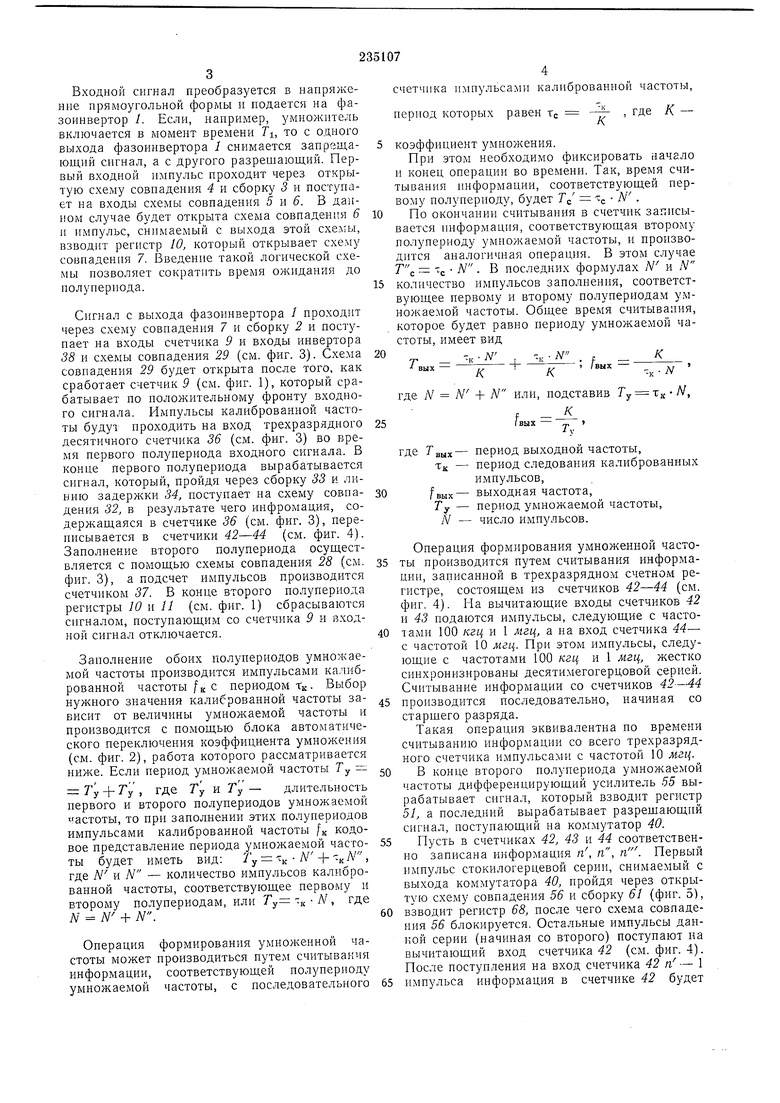

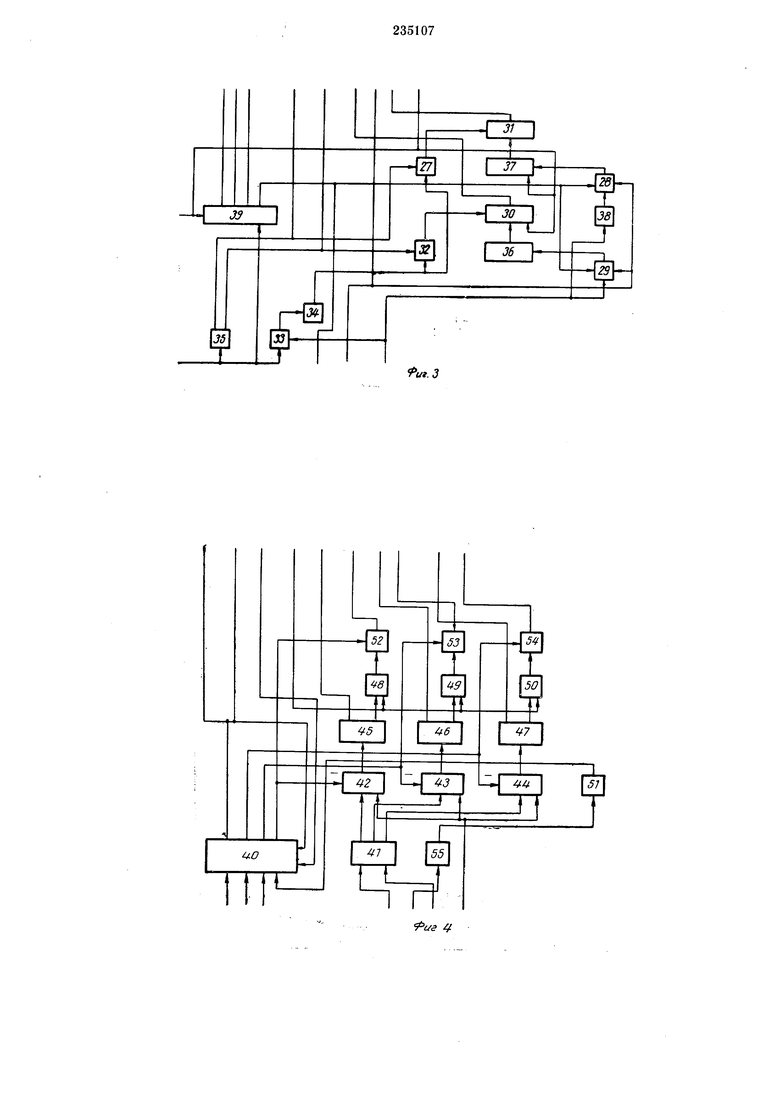

На фиг. 1 приведена схема входного блока умножителя; на фиг. 2 - схема блока автолгатического переключения коэффициента умножения; на фиг. 3 - схема блока запоминания с блоком калиброванных частот; на

фиг. 4 и 5 - схема блока формирования умноженной частоты.

Устройство содержит фазоинвертор 1, сборки 2 и 3, схемы совпадения 4-8, счетчик 9, регистры 10, 11 и 12, линию задерн ки 13, схемы

совиадеиия 14-18, счетчик 19, регистры 20 и 21, линии задерл ки 22-25 и дифференцирующий усилитель 26, схемы совиадения 27-32, сборку 33, линию задержки 34, счетчики 35- 37, инвертор 38 и блок 39 калиброванных частот, коммутатор 40, сборку 41, счетчики 42- 44, дещифраторы 45-47, регистры 48-51, схемы совиадения 52-54, дифференцирующий усилитель 55, схемы совпадения 56-60, сборки 61-64, регистры 65-68 и линию задержВходной сигнал преобразуется в напряжение прямоугольной формы и подается на фазоинвертор I. Если, например, умножитель включается в момент времени TI, то с одного выхода фазоинвертора 1 снимается запрещающий сигнал, а с другого разрешающий. Первый входной импульс проходит через открытую схему совпадения 4 и сборку 3 и поступает иа входы схемы совпадения 5 и б. В данном случае будет открыта схема совпадения 6 н импульс, снимаемый с выхода этой схемы, взводит регистр 10, который открывает схему сониадеиня 7. Введение такой логической схемы иозволяет сократить время ожидания до нолуперпода.

Спгнал с выхода фазоинвертора / проходит через схему совпадения 7 и сборку 2 и поступает на входы счетчика 9 и входы инвертора 38 и схемы совпадения 29 (см. фиг. 3). Схема совпадения 29 будет открыта после того, как сработает счетчик 9 (см. фиг. 1), который срабатывает по положительному фронту входного сигнала. Импульсы калиброванной частоты будут, проходить на вход трехразрлдного десятичного счетчика 36 (см. фиг. 3) во время первого полупериода входного сигнала. В коние первого полупериода вырабатывается сигнал, который, пройдя через сборку 33 и линию задержки 34, иоступает на схему совпадения 32, в результате чего иифромация, содержащаяся в счетчике 36 (см. фиг. 3), перенисывается в счетчики 42-44 (см. фиг. 4). Заполнение второго полупериода осуществляется с помощью схемы совпадения 28 (см. фиг. 3), а подсчет импульсов производится счетчиком 37. В конце второго полупериода регистры 10 и 11 (см. фнг. 1) сбрасываются сигналом, поступающим со счетчика 9 и входной сигнал отключается.

Заполнение обоих полупериодов умножаемой частоты производится импульсами калиброванной частоты/к с периодом ts- Выбор нужного значения калиброванной частоты зависит от величины умножаемой частоты и производится с помощью блока автоматического переключения коэффициента умножения (см. фиг. 2), работа которого рассматривается ниже. Если иериод умножаемой частоты Ту Ту , где Ту vi Ту - Длительность первого и второго полупериодов умножаемой «астоты, то при заполнении этих полупериодов импульсами калиброванной частоты /к кодовое представление периода умножаемой частоты будет иметь вид: 7у -« Л где N и Л - количество импульсов калиброванной частоты, соответствующее первому и второму полупериодам, или Ту к Л где N N + N.

Операция формирования умноженной частоты может производиться путем считывания информации, соответствующей полупериоду умножаемой частоты, с последовательного

счетчика импульсами калиброванной частоты.

, где Я период которых равен TC

коэффициент умножения.

При этом необходимо фиксировать начало и конец операции во времени. Так, время считывания информации, соответствующей первому полупериоду, будет .-т. N .

По окончании считывания в счетчик записывается информация, соответствующая второму полупериоду умножаемой частоты, и производится аналогичная операция. В этом случае (. - Л . В последних формулах N и .V

количество импульсов заполиения, соответствующее первому и второму полуперподам умножаемой частоты. Общее время считывания, которое будет равио иериоду умножаемой частоты, имеет вид

- . w-

т -, I n.-N . .

- к I -к -V . f А

I вмх .., /ВЫХ

вых

к к

где N N + N или, нодставив Гу т Л, . К

TV

где Г вых- период выходной частоты,

Тд - период следования калиброванных

импульсов, fflbix- выходная частота,

ГУ - период умножаемой частоты, N - число импульсов.

Операция формирования умноженной частоты производится путем считывания информации, зацисаниой в трехразрядном счетном регистре, состоящем из счетчиков 42-44 (см. фиг. 4). На вычитающие входы счетчиков 42 и 43 иодаются импульсы, следующие с частотами 100 кгц и 1 мгц, а на вход счетчика 44- с частотой 10 мгц. При этом импульсы, следующие с частотами 100 кгц и 1 мгц, жестко сиихронизированы десятнмегогерцовой серией. Считывание информации со счетчиков 42-44

ироизводится последовательно, начиная со старшего разряда.

Такая операция эквивалентна по времени считыванию информации со всего трехразрядного счетчика импульсами с частотой 10 мгц.

В конце второго цолупериода умножаемой частоты дифференцирующий усилитель 55 вырабатывает сигнал, который взводит регистр 51, а последний вырабатывает разрешающий сигнал, поступающий на коммутатор 40.

Пусть в счетчиках 42, 43 и 44 соответственно записана информация п , п, . Первый импульс стокилогерцевой серии, снимаемый с выхода коммутатора 40, пройдя через открытую схему совпадения 56 и сборку 61 (фиг. 5),

взводит регистр 68, после чего схема совпадения 56 блокируется. Остальные импульсы дайной серии (начиная со второго) поступают па вычитающий вход счетчика 42 (см. фиг. 4). После поступления на вход счетчика 42 п- 1 равна 1 и с выхода дешифратора 45 вырабатывается сигнал, взводящий регистр 48, который открывает схему совпадения 52. Следующий сигнал сбрасывает счетчик 42 в нулевое состояние, и, нройдя через схему совпадений 52, взводит регистр 65 (см. фиг. 5). Сигнал с последнего поступает через сборку 62 (на коммутатор 40), в результате чего блокируются сигналы, поступающие на счетчик 42, и включаются сигналы, подаваемые на счетчик 43. Кроме того, сигнал с регистра 65 (см. фиг. 5) поступает на вход схемы совпадения 59. Последняя будет закрыта по двум остальным входам, так как дешифраторы 45, 46 н 47 (см. фиг. 4) вырабатывают сигнал на левом выходе в случае нулевой информации в счетчиках 42-44. Операции считывания со счетчиков 42 и 43 и переключения частот считывающих сигналов производятся аналогично первому случаю. Последний сигнал, устанавливающий счетчик 44 в нулевое состояние, проходит через схему совпадения 54, сборку 64, схему совпадения 58 и сбрасывает регистр 68 (см. фиг. 5). С выхода регистра 6S снимается сигнал, равный по длительности первому полупериоду умноженной частоты. Сигнал, вырабатываемый по заднему фронту последнего, сбрасывает регистры 48-50 (см. фиг. 4), регистры 65-66 (фиг. 5) и поступает на RXOды счетчика 35, сборки 33 и блока 39 (см. фиг. 3). В результате этого перебрасывается счетчик 35, а сигнал по цепи: сборка 33, линия задержки 34, схема совпадения 27 поступает на вход схемы совпадения 31, чем обеспечивается перепись информации из счетчика 57 в счетчики 42-44 (см. фиг. 4). После окончания операции считывания информации, соответствующей первому полуиериоду умноженной частоты, сигнал, снимаемый с выходного регистра (см. фиг. 5), поступает на вход блока калиброванных частот и сбрасывает счетчики делителя частоты, чем обеспечивается начало отсчета длительности второго полупериода до конца первого полупериода. Операция формирования второго полупериода умноженной частоты осуществляется аналогично первому случаю, только сигнал конца операции считываиия поступает через схему совпадения 57 и сборку 61 (см. фиг. 5) на левый выход регистра 68. Операция переключения коэффициента умнол ения осуществляется с помощью блока, схема которого представлена на фиг. 2. Значение коэффициента умножения определяется соотнощением периодов импульсов заполнения и импульсов считывания. При этом наибольшее время тратится при заполнении периода низкочастотных сигналов, поэтому первые два полупериода умножаемой частоты заполняются импульсами с частотой 10 кгц. Если значение измеряемой частоты больще 100 гц, то производится переключение заполняющей частоты. Последнее необходимо, так как при обратном порядке переключения заполияющих частот операция заполнентш будет осуществляться за время, равное 4,5 периода умножаемой частоты (низкочастотного поддиапазона), что резко снижает быстродействие умножителя. Очевидно, что при заполнении периодов, соответствующих граничным частотам поддиапазонов (100 гц, 1 кгц и 10 кгц - заполняющие частоты соответственно 10 кгц, 100 кгц и 1 мгц, число зафиксированных импульсов равно 100 ± 1. Если умножаемая частота будет меньше граничной, то количество заполняющих импульсов будет больще 100. Признаком переключения заполняющей частоты может служить временное соотношение двух сигналов: 100-го импульса заполняющей частоты и сигнала, совпадающего по времени с концом периода умножаемой частоты. При этом возможны три случая: импульс конца сигнала проходит после 100-го импульса заполняющей частоты, оба импульса проходят одновременно, импульс конца сигнала проходит раньше 100-го импульса. В первых двух случаях переключение заполняющей частоты не производится, так как в первом случае умножаемая частота меньше граничной, а во втором - равна граничной. В третьем случае умножаемая частота больше, чем граничная частота поддиапазона, и блок переключения вырабатывает сигнал, обеспечивающий необходимое переключеиие частоты заиолняющих сигналов. Рассмотрнм работу блока переключения коэффициента умножения (см. фиг. 2) более подробно. Па вход схемы совпадения 14 от счетчика 9 поступает сигнал, равный по длительности одному периоду умнон аемой частоты. На другой вход иодаются импульсы заполнения с частотой в 10 кгц, которые запоминаются счетчиком 19. Счетчик 19 состоит из двух двоичнодесятичных декад. В первом случае 100-й импульс заполняющей частоты взводит регистр 20, который блокирует схемы совпадения 16 и 17, поэтому сигнал переключения не вырабатывается, в случае, когда 100-й импульс и сигнал периода умножаемой частоты приходят одновременно, возможно появление сигнала на выходе схемы совпадения 17. При этом уиомяиутый имиульс взводит регистр 21, который, в свою очередь, открывает схему совпадения 14. Па схемы совпадения 16 и 18 поступают задержанные линией задержки 25 импульсы заполняющей частоты. Время задержки таково, что к моменту появления сигнала на входах схем совпадения 16 и 18 регистр 20 блокирует схему совпадения 16 и открывает схему совпадения 18. В результате через схему совпадения 14 сигнал не проходит и переключение заполняющей частоты не осуществляется, а с выхода схемы совпадения 18 снимается сигнал, сбрасывающий регистр 21. В третьем случае дифференцирующий уси литель 26 вырабатывает сигнал, совпадаьпций

стоты, который сбрасывает счетчик 19, и, пройдя через открытую схему совпадения 17, взводит регистр 21. Открывается схема совпадепия 14, и задерл аппый импульс заполняющей частоты сбрасывает счетчики 36 и 37 (см. фиг. 3) и счетчики 42-44 (см. фиг. 4), так как в указанных счетчиках зафиксирована неправильная информация. Одновременно сигнал с выхода схемы совпадения 14 (см. фиг. 2) поступает на блок 39 (см. фиг. 3), чем обеспечивается переключение заполняющей частоты. Кроме того, сигнал со схемы совпадения 14 (см. фиг. 2) поступает на схемы совпадения 5 и 6 (см. фиг. 1), вызывая повторное срабатывание входного блока. После чего операция заполнения повторяется. Если умнол аемая частота 1 кгц.1, 10 кгц, то переключение заполняющей частоты происходит дважды.

Предмет изобретения

Устройство для умножения частоты низкочастотных сигналов, содержащее входной блок, блок калиброванных частот, блок автоматического переключения коэффициента умножения, коммутатор, оперативный и запоминающие счетчики, блок формирования умложенной частоты, собирательные схемы и схемы совпадения, отличающееся тем, что, с

целью расширения диапазона умножаемых частот, увеличения коэффициента умножения и новыщения быстродействия устройства, в нем входной блок подключен к двум схемам совиадения, выходы которых присоединены ко входам запоминающих счетчиков, а управляющие входы соединены с одним из входов входного блока, со входом блока автоматического переключения коэффициента умножения

и с одним из выходов блока калиброванных частот, остальные выходы которого через коммутатор подключены к оперативному счетчику и ко входу блока формирования умноженной частоты, соединенного другими входами с

выходами оперативного счетчика, причем ра.чрядные входы этого счетчика через матрицу сборок и схем совпадения подключены к выходам запоминающих счетчиков; выход схемы формирования умноженной частоты соединен

с блоком калиброванных частот и со входами одноразрядного счетчика и схем совпадения, включенных между управляющими входами матрицы схем совпадения и выходами одноразрядного счетчика; выход входного блока

подключен ко входу блока автоматического переключения коэффициента умножения, выходы которого соединены с запоминаюп1,ими и оперативными счетчиками и блоком калиброванных частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU259150A1 |

| Умножитель частоты | 1973 |

|

SU714634A1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| Умножитель частоты | 1984 |

|

SU1257642A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1972 |

|

SU354517A1 |

| Умножитель частоты следования им-пульСОВ | 1979 |

|

SU839031A1 |

| СИСТЕМА ЦИФРОВОГО СТЕРЕОФОНИЧЕСКОГО РАДИОВЕЩАНИЯ | 1991 |

|

RU2019041C1 |

| Умножитель частоты | 1984 |

|

SU1238070A1 |

9V.J

Даты

1969-01-01—Публикация