Предложенное устройство относится к средствам приборостроения, автоматики, вычислительной техники и предназначено для обработки информации, поступающей от частотны: датчиков и других объектов, выходным параметром которых служ.ит частота электрических сигналов в вычислительных системах автоматической .обработки данных.

Известно устройство для умножения частоты, содержащее блок калиброванных частот, блок переключения коэффициента умножения, блок реверсивных счетчиков, блок формирования выходной частоты, счетчики и логические схемы.

Предложенное устройство отличается тем, что содержит блок переключения режима работы, содержащий счетчик, выходы которого подключены к схемам совпадения, две из которых связаны с переключателями режима работы, а третья, выход которой через линию задержки подключен ко входу счетчика, соединена с входной схемой совпадения устройства. Блок следящего режима содержит счетчик и логические схемь, причем выход входной схемы совпадения соединен со входом блока переключения режима работы и со схемой совпадения, другой вход которой подключен к выходу блока переключения режима работы, а выход соединен со счетчиком блока следящего режима. Выход входной схемы совпадения

связан со входами блока калиброванных частот и одноразрядного счетчика, выходы последнего соединены с двумя схемами совпадения, другие входы которых соединены параллельио с одним выходом блока калиброванных частот и выходом блока переключения режима работы, а выходы через схемы сборки подключены к суммирующим входам реверсивных счетчиков заполнения (выходы счетчиков заполнения и оперативного счетчика соединены с блоком формирования выходной частоты). Вычитающие входы реверсивиых счетчиков подключены через схемы совнадения к другому выходу блока калиброванных частот;

управляющий вход схемы совпадения, связанной с онеративным счетчиком, подключен к одному выходу блока формирования выходной частоты, а управляющие входы схе.м совпадения, связанных с вычитающими входами счетчиков заполнения, подключены параллельно к другому выходу блока формирования выходной частоты и к коммутирующим выходам блока следящего режима. Вычитающие входы счетчиков заполнения через схему сборки соединены с суммирующим входом оперативного счетчика, а вячитающий вход последнего связан через схемы совпадения, управляющие входы которых соединены с коммутирующими выходами блока следящего режима, и схемы

Заполнения. Сбросовые выходы блока следящего режима соединены отдельно с каждым из сбросовых входов счетчиков заполнения и вместе через схему сборки - со сбросовым входом оперативного счетчика. Блок переключения коэффициента умножения взаимосвязан с блоком калиброванных частот, и его выход соединен со сбросовы.ми входами всех счетчиков.

Предложенное устройство обеспечивает возможность работы как в следящем, так и в циклическом режи1ме П1ри сохранении значения остальных технических параметров и меньшем объеме оборудования.

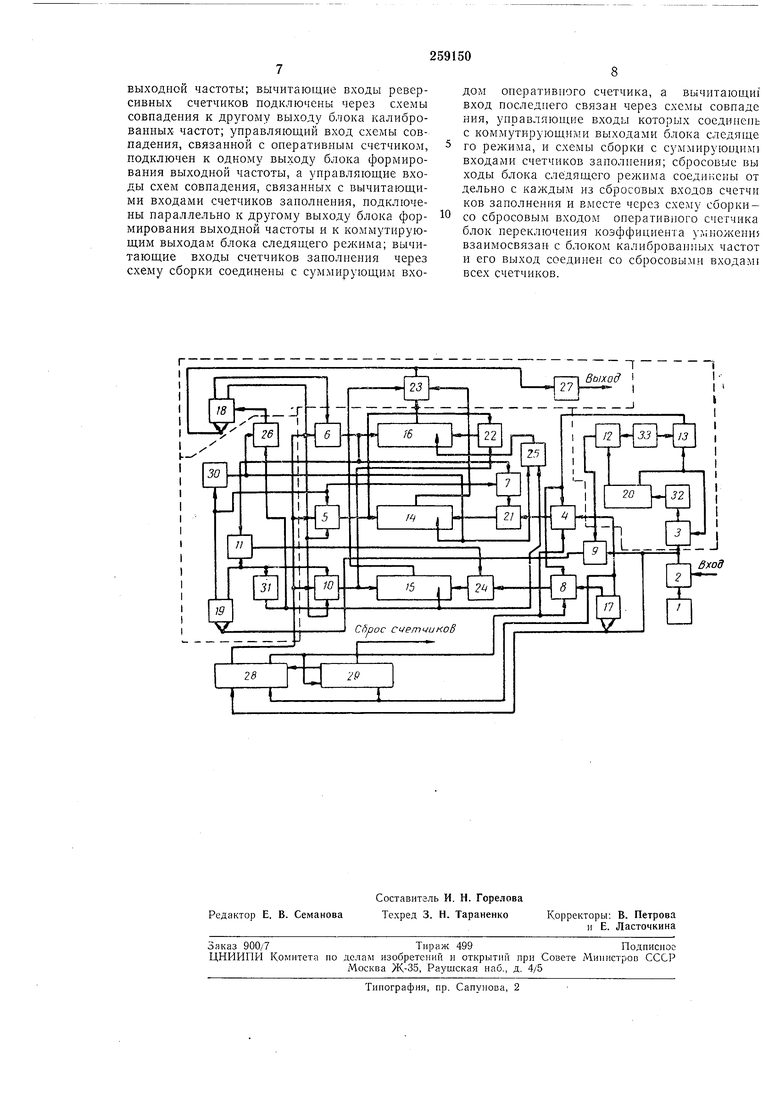

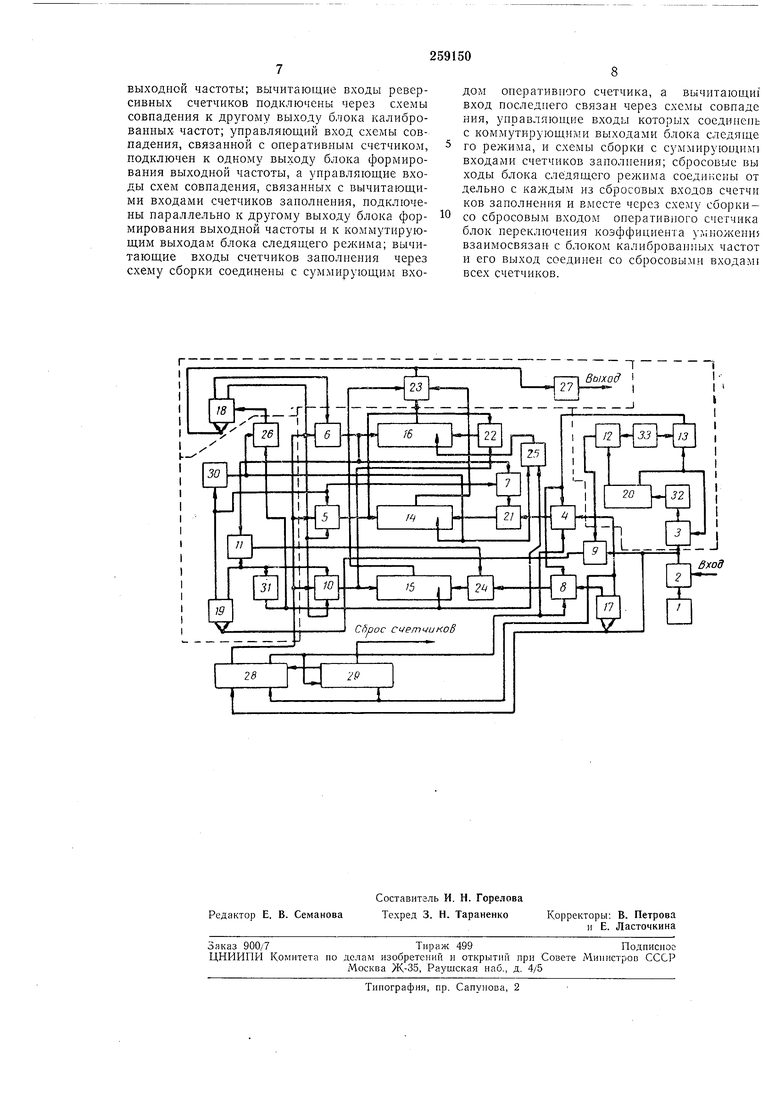

На чертеже приведена функциональная схема описываемого устройства.

Устройство состоит из схемы пуска /, схем совпадения 2-13, блоков 14 и 15 реверсивных счетчиков заполнения, блока 16 реверсивного оперативного счетчика, счетчиков 17-20, схем сборки 21-26, одповибратора 27, блока калиброванных частот 28, блока переключения коэффициента умножения 29, дифференцирующих усилителей 30 и 31, линии задержки 32 и переключателя режима работы 33.

Блок переключения режима работы состоит из схем совпадения 3, 12 и 13, линии задержки 32, двухразрядного счетчика 20 и переключателя режима работы 33. Блок следящего режима включает в себя схему совпадения 11, счетчик 19, дифференцирующие усилители 30 и 31 и схему сборки 26. Блок формирования выходной частоты состоит из счетчика 18, схемы сборки 23 и одновибратора 27.

При срабатывании схемы пуска / сигналы умножаемой частоты /у поступают через схему совпадения 2 параллельно на входы счетчика 17, блока калиброванных частот 28 и схем совпадения 9, 3, первая из которых заблокирована, а вторая пропускает сигналы, поступающие через линию задержки 32 на вход счетчика 20. С выходов счетчика 17 снимаются прямоугольные сигналы, сдвинутые по фазе па 180, частота которых равна /у/2, а длительность - периоду входной частоты Ту. В результате действия сигнала входной частоты /у срабатывает схема управления в блоке калиброванных частот, и на входы схем совпадения 4 и 8 начинают поступать импульсы с частотой.

/к -.(1)

K

где TK - период следования сигналов калиброванной частоты.

В первый момент разрешающий сигнал, снимаемый с правого выхода счетчика 17, открывает схему совпадения 4 на время, равное длительности первого периода частоты /у, чем обеспечивает заполнение первого периода умножаемой частоты импульсами калиброванной частоты /к ,

Кодовое представление периода умножаемой частоты имеет вид:

ГУ .VT,,(2)

где N - число импульсов, прошедших за время, равное Ту,

Сигнал, вырабатываемый в момент заднего

фронта импульса, сбрасывает триггер в блоке

калибровапных частот 28, открывая выходную

схему совпадения, и на схемы совпадения 5, 6

и 10 нодается серия импульсов с частотой

f 1

/с -

с

Значения периодов частот /с и /,; связаны соотношением:

(3)

где /С - коэффициент умножения.

В этот момент открыта только схема совпадения 5. Импульсы с частотой /с через открытую схему совпадения 5 поступают на вычитающий вход реверсивного счетчика блока 14, последовательно уменьшая информацию, записанную в последнем от N до нуля. Одновременно импульсы с выхода схемы совпадения 5 через схему сборки 22 поступают на суммирующий вход реверсивного счетчика

блока 16.

Для того, чтобы уменьшить информацию в реверсивном счетчике блока 14 от N до нуля, необходимо подать па его вычитающий вход N импульсов. При этом точно такое же количество импульсов будет записано в реверсивный счетчик блока 16, а время, за которое происходит этот процесс, равно:

Тс Nr,.(4)

В момент нрихода Л-го импульса (нриводящсго счетчик в нулевое состояние) с выхода блока 14 снимается сигнал, который, пройдя через схему сборки 23, вызывает срабатывание одновибратора 17 я счетчика 18. Одновибратор вырабатывает первый импульс умноженной частоты, а счетчик блокирует схему совпадения 5 и открывает схему совпадения 6. После этого импульсы, следующие с частотой /с, начинают поступать на вычитающий вход

реверсивного счетчика блока 16, и операция повторяется с той лишь разницей, что сигналы перениси через схему совпадения и схему сборки 21 поступают на суммирующий вход реверсивного счетчика блока 14.

Через время, равное Т с, одновибратор 27 вырабатывает второй сигнал, а счетчик 18 переключает схемы совпадения 5 и 6.

Если принять время Гс за период выходной (умноженной) частоты Гс , то легко

можно ноказать, что

/ ВЫХ А -/у. 3 /вых - так как Ту ЛЧк, то /вых ) /вых - /у с выхода одновибратора 27 будет сниматься непрерывная последовательность импульсов умпожеппой частоты, так как описанные операции непрерывно повторяются. Одновременно с операцией формирования умноженной частоты осуществляется операция заполнения второго периода умноженной частоты. Во время второго периода умножаемой частоты с левого выхода счетчика 17 снимается сигнал, открывающий схему совпадения. 8, на другой вход которой поступают импульсы калиброванной частоты /,;. Количество импульсов, прошедших за время Т , фиксируется реверсивным счетчиком блока 15. Счетчик 20 состоит из двух триггеров, включенных последовательно, так что последний триггер срабатывает в момент прихода второго задержанного импульса умножаемой частоты. В результате срабатывания счетчика 20 блокируется схема совпадепия 3, а открывается схема совпадения 9; следующие сигналы умножаемой частоты перебрасывают счетчик 19. Сигнал, снимаемый с выхода счетчика 19, блокирует cxeMrj совпадения 5 и 7 и вызывает срабатывание дифференцирующего усилителя 30, который заставляет срабатывать реверсивные счетчики в блоках М, 16 и счетчик 18. Сигнал, снимаемый с правого выхода счетчика 19, открывает схемы совпадения 10 и 11, а схема совпадения 6 блокируется счетчиком 18. После этого операция формирования умноженной частоты производится аналогично первому случаю, только с помощью реверсивных счетчиков блоков 16 и 15, схем совпадения 10 и 11, схем сборки 22 и 24 и счетчика 18. Значение умноженной частоты будет соответствовать длительности второго периода умножаемой частоты. Заполнение третьего периода умножаемой частоты будет производиться аналогично заполнению первого периода и т. д. Таким образом, выходная частота будет изменяться в зависимости от изменения входной частоты с задержкой всего на один период умножаемой частоты. Предложенная схема умножителя частоты может работать и в циклическом режиме, для чего переключатель режима работы устанавливается в положение «циклический режим. Переключатель , работы 33 блокирует схему совпадения 12 и открывает схему совпадения 13 (открытая схема совпадения 13 пропускает сигналы отрицательной полярности) . Импульсы умножаемой частоты, сннмаемые с выхода схемы совпадения 2, поступают параллельно на вход, счетчика 17, на входы схем совпадения 5 и Р. депия 4. Счетчик 17 сбрасывается вторым импульсом умнол аемой частоты. Таким образом, схема совпадения 4 будет открыта на время, равное длительиости периода умнолсаемой частоты, который заполняется импульсами калиброванной частоты (количество прошедших импульсов фиксируется реверсивным счетчиком блока 14). Второй задержанный нмпульс входной частоты взводит второй триггер счетчика 20; сигнал, снимаемый с правого выхода, блокирует схему совпадения 3 и, пройдя через схему совпадения 13, запрещает прохождение импульсов через схемы совпадения 4 и 8. Сигнал, снимаемый с левого выхода счетчика 20, не проходит через схему совпадения 12 и схема совпадения 9 остается заблокированной. Операция формирования умнол енной частоты осуществляется так же, как и в следящем режиме, только в данном случае постоянно работают реверсивные счетчики блоков 14 и 16. Для повторного запуска умножителя необходимо произвести сброс реверсивных счетчиков блоков 14, 16 и 15, а счетчиков и регистров управления в блоке калиброванных частот и блоке переключения коэффициента умножения. Предмет изобретения Устройство для умножения частоты низкочастотных сигналов, содержащее блок калиброванных частот, блок переключення коэффициента умнол ения, блок реверсивных счетчиков, блок формирования выходной частоты, счетчики и логические схемы, отличающееся тем, что, с целью обеспечения возмолчностн работы как в следящем, так и в циклическом , оно содержит блок переключения работы, содерлчащий счетчик, выходы которого подключены к схемам совпадення, дзе из которых связаны с переключателями режима работы, а третья, выход которой через линию задержки подключен ко входу счетчика, соединена с входной схемой совпадения устройства, а также блок следящего , содержащий счетчик и логические схемы, причем выход входной схемы совпадения соединен со входом блока переключения работы и со схемой совпадения, другой вход которой подключен к выходу блока переключения режима работы, а выход соединен со счетчиком блока следящего релхима; выход входной схемы совпадения связан со входами блока калиброванных частот и одноразрядного счетчика, выходы последнего соединены с двумя схемами совпадения, другие входы которых соединены параллельно с одним выходом блока калиброванных частот и выходом блока переключения работы, а выходы через схемы сборки подключены к суммирующим входам реверсивных счетчиков заполнения, выходы счетчиков заполнения и оперативного

выходной частоты; вычитающие входы реверсивных счетчиков подключены через ехемы совпадения к другому выходу блока калиброванных частот; управляющий вход схемы совпадения, связанной с оперативным счетчиком, подключен к одному выходу блока формирования выходной частоты, а управляющие входы схем совпадения, связанных с вычитающими входами счетчиков заполнения, подключены параллельно к другому выходу блока формирования выходной частоты и к коммутирующим выходам блока следящего режима; вычитающие входы счетчиков заполнения через схему сборки соединены с суммирующим входом оперативного счетчика, а вычитающи вход последнего связан через схемы совпаде ния, управляющие входы которых соединепь с коммутирующими выходами блока следяще го режима, и схемы сборки с суммирующилп входами счетчиков заполнения; сбросовые вы ходы блока следящего режима соединены от дельно с каждым из сбросовых входов счетчи ков заполнения и вместе через схему сборкисо сбросовым входом оперативного счетчика блок переключения коэффициента улпюжени5 взаимосвязан с блоком калиброванных частот п его выход соединен со сбросовыми входам всех счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ СИГНАЛОВ | 1969 |

|

SU235107A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ и ДЕЛЕНИЯ ЧАСТОТНО- ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU333564A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1973 |

|

SU404173A1 |

| ЦИФРОВОЙ НУЛЬ-ОРГАНВСЕСОЮЗНАЯ, -.^.,-..J-ir--"!,.-!ШЕШ№'5=^/.^-^--- BHEfsHOrn^ | 1972 |

|

SU335685A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

| Цифровой частотомер | 1980 |

|

SU918873A1 |

| Преобразователь частота-код | 1980 |

|

SU884133A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU312373A1 |

Даты

1970-01-01—Публикация