(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Запоминающее устройство | 1979 |

|

SU858094A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| Запоминающее устройство | 1979 |

|

SU809364A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

I

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах (ЦВМ) и устройствах автоматики .

Известно запоминающее устройство (ЗУ).содержащее накопитель, регистр адреса, дешифратор, координатные ключи X и У, выходные усилители слабых сигналов со стробированием от общего формирователя строба р.

Данное ЗУ менее помехоустойчиво и надежно, чем другие подобные ЗУ из-за наличия помех в фазе с полезным сигналом и усложнения схем накопителя и выходных усилителей. Для различения выходных сигналов О и 1 приходится применять амплитудные и временные селекторы, пороговые схемы и специальные схемы стробирования, однако это приводит к усложнению схем устройства, особенно рабо- . такнцих в широком диапазоне механи- . ческих и климатических воздействий. ,

Наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее регистр адреса, один из входов которого подключен к кодовой шине Установка . О , другие входы - к кодовым шинам адреса, а выходы подключены соответственно к входам дешифратора и формирователя адресных токов, соответствующий вход формирователя

10 адресных токов подключен к одной из кодовых шин, а выходы соединены с вхо дами накопителя, усилители считывания, одни входы которого соединены с входами формирователя строба и блок

15 управленияiZj.

Однако в данном устройстве из-за наличия паразитных индуктивностей и емкостей, а также помех питания входной сигнал О представляет со20бой не отсутствие импульса, а импульс в фазе с полезным сигналом 1, что может привести к ложному срабатыванию - фиксации сигнала I вместо

О

Аналогичная ситуа сигнала

ция может возникнуть как в ОЗУ , так и ПЗУ трансформаторного типа с прямой прошивкой (когда при записи О провод обходит ферритовый сердечник) , в которых наиболее существенны помехи из-эа наличия паразитных емкостей и индуктивностей между прошивающими проводами. Наличие этих Iпомех значительно ухудшает помехоустойчивое трансформаторных ПЗУ, а следовательно и их надежность

Цель изобретения - повьшение надежности устройства за .счет подавления помех и фазового различия выходш,1х сигналов О и 1.

Поставленная цель достигается тем что в запоминающее устройство введены дополнительный формирователь адресных токов, дополнительный накопитель блок задержки, триггер запуска, блок элементов И, элемент ИЛИ, элементы И, причем входы первого элемента И подключены к соответствующим кодовым шинам, выход первого элемента И соединен с входом триггера запуска, первый и второй выходы которого подключены соответственно к первым входам второго и третьего элементов И, вторые входы которых toeдинeны с одними выходами блока задержки, другие выходы которого соединены с первыми входами блока элементов И, вторые входы которого подключены к одному из выходов дешифратора, другой выход дешифратора и выход второго элемента И подключены к соответствующим входам дополнительного формирователя адресн токов, выход которого соединен с одн из входов дополнительного накопителя выходы третьего элемента И и блока 5.Пментов И соединены с входами зйемвнта ИЛИ, выход которого подключен к входу формирователя строба, выходы ссяовного накопителя соединены с другими входами дополнительног накопителя, выходы которого подключены к другим входам усилителя считывания , выходы блока управления подключены к соответствующему входу дополнительного формирователя адресных токов.

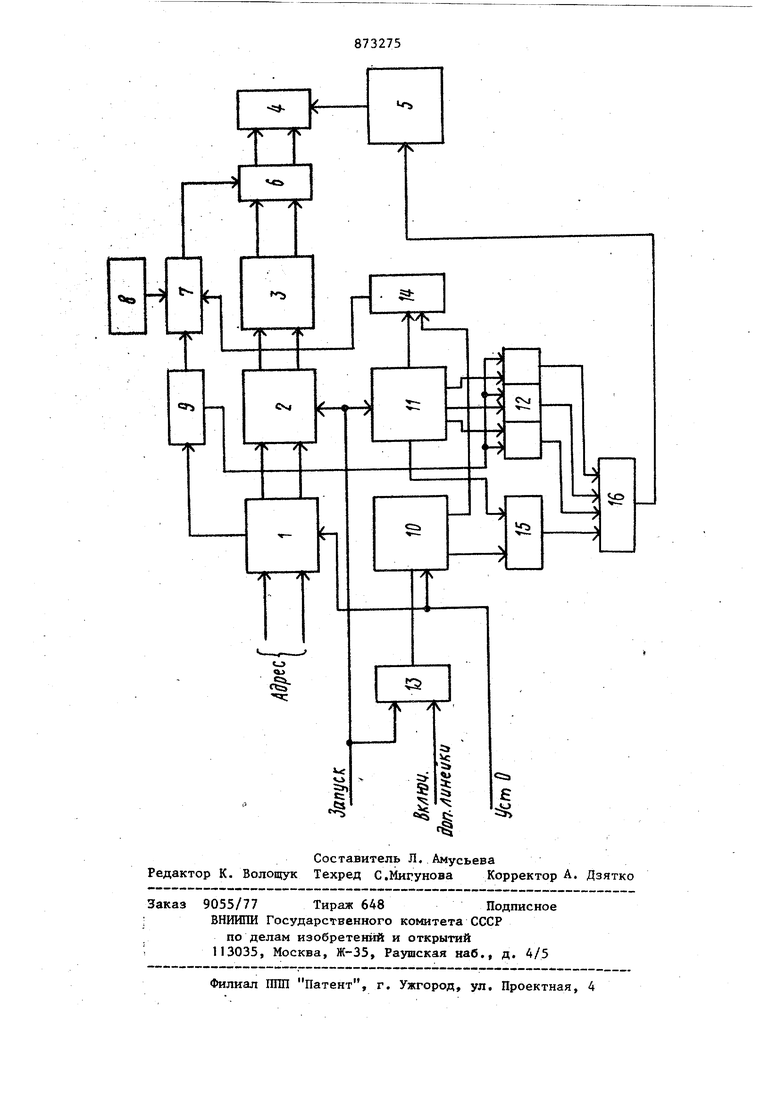

На чертеже представлена структурная схема запоминакяцего устройства.

Запоминающее устройство содержит регистр адреса I, формирователь 2 адресных токов, .накопитель 3, усилитель считывания 4, формировател

;5 строба, дополнительные накопитель 6 и формирователь 7 адресных токов, блок 8 управления, дешифратор 9, триггер 10 запуска, блок 1I задержки,

блок 12 элементов И, элементы 13-15 И, элемент 16 ИЛИ.

Работа данного запоминающего устройства существенно отличается от известных при считывании информации

из накопителя, так как в данном устройстве производится опрос не только . числовой линейки по выбранному адресу в накопителе 3 с помощью регистра 1 и формирователя 2, но и . дополнительным накопителем 6 с помощью дополнительного формирователя 7 и дешифратора 9. Полученттые выходные сигналы суммируются на выходных разрядных шинах,.и на входы усилителя 4 считывания поступают сигналы о и 1, различающиеся по фазе. Это значительно упрощает селекцию выходных сигналов, повышает помехоустойчивость усилителя 4 и надежность

запоминающего устройства.

В режиме считывания из других устройств ЦВМ на кодовые шины поступают сигналы кода адреса, Запуск, УстановкаО. , Включение дополнительногр накопителя. Сигнал Установка О подготавливает к работе триггеры регистра 1 и устанавливает в исходное состояние триггер 10 запуска дополнительного накопителя 6. Сигналы кода адреса через регистр адреса поступают на дешифратор и формирователь 2 адреснь1х токов, и по сигналу Запуск в выбранной числовой линейке накопителя 3 протекает ток опроса, формируя в выходных шинах, накоп ителя сигналы О и 1. Эти сигналы из-за помех могут значительно . отличаться друг от друга, что затрудняет их надежное различение. В случае поступления из кодовой шины сигнала Включение дополнительного накопителя сигнал Запуск также через первый элемент 13 И вызывает срабатьюание триггера 10 запуска дополнительного накопителя 6 и . поступает на блок 11 задержки 11. Через блок 11 и элеме.нт 14 И по сигналу разрешения с триггера 10 задержанный сигнал Запуск запускает дополнитель-ный формирователь 7 с

5 задержкой по времени, определяемой дешифратором 9. Амплитуда и фронт тока опроса дополнительного накопителя 6, поступакяцего с формироватег 5 ля 7, регулируется с. помощью блока 8 управления (по амплитуде тока и фрон ту импульса тока определяется амплит да дополнительнь1х выходных сигналов в разрядных тинах ).Фаза тока в накопителе 6 от формирователя 7 выбира ется таким образом, чтобы выходные сигналы от накопителя 6 в разрядных /шинах быпи противоположны сигналу 1 /. В накопитель 6 записывается одинак вая информация во всех разрядах (например, все 1). В результате опроса числовой линейки в накопителе 3 и дополнительной числовой линейки в на копителе 6 в разрядных шинах формиру ется по два сигнала, которые алгебра ически суммируются. При этом выходные сигналы I числовой линейки накопителя 3 несколько уменьшаются по амплитуде, а выходные сигналы О становятся противоположными по фазе. Место и амплитуду дополнительных выходных сигналов определяется дешифратором 9 и блоком 8 управления. Запуск формирователя 5 строба автома тически определяется по месту дополнительного сигнала с дешифратора 9 и сигналу с блока 11 задержки через элементы 12 И и элемент 16 ИЛИ. Такой запуск формирователя строба необходим из-за возникающего сдвига выходных сигналов О и 1 при их суммировании с сигналами дополнительной числовой линейки накопителя 6, при отсутствии сигнала Включение дополнительного накопителя цепь опроса дополнительного накопителя не работает, и формирователь строба чжпускается обычным путем через элемент 15 И и по сигналу разрешения с триггера 10, находящемуся в этом случае в нулевом состоянии. Таким об разом, подбирая необходимую амплиту- ду и длительность тока опроса числовой линейки в дополнительном накопителе 6, можно обеспечить заданныепараметры выходных сигналов 1 и О на входе усилителя считывания. Использование данного ЗУ позволяет подавлять возникающие помехи и по лучать фазовое различие сигналов О и 1, следовательно значительно упрощаются схемы усилителей считывания расширяются пределы работоспособности устройства при климатических и механических воздействиях и изменениях питающих напряжений. Формула изобретения Запоминающее устройство, содержащее регистр адреса, один из входов которого подключен к кодовой шине Установка О, другие входы - к кодовым шинам адреса, а выходы подключены соответственно к входам дешифра- . тора и формирователя адресных токов j .соответствующий вход формирователя адресных токов подключен к одной |из кодовых шин, а выходы соединены с входами накопителя, усилитель считывания, одни входы которого соединены с входами формирователя строба и блок управления, отличающеес я тем, что, с целью повышения надежности запоминающего устройства, в него введены дополнительный накопитель, дополнительный формирователь адресных токов, блок зарержки, триггер запуска, блок элементов И, элемент ИЛИ, элементы И, причем входы первого элемента И подключены к соответствующим кодовым шинам, выход первого элементя И соединен с входом триггера запуска, первый и втооой выг ходы которого подключены соответственно к первым входам второго и-третьего элементов И, вторые входы соединены с опними выхолгами блока задержки, дpvгиe выходы которого соединены с первыми вхопами элементов И, втооые входы котооого попключены к одгому из выходов пешифратопа, другой выход дешифоатора и выход втооого элемента И подключены к соответствующим входам дополнительного Формирователя адресных токов, выход которого соединен с одним из входов дополнительного накопителя, выходы трётье о элемента И и блока элементов И соединены с входами элемента ИЛИ, выход котооого подключен к ВХОДУ фоомирователя строба.выходы основного накопителя соединены с другими входами дополнительного накопителя, выходы которого подключены к другим вхо,-; дам усилителя считывания, выходы блока управления по;|ключены к соответствующему входу дополнительного формирог вателя адресных токов. Источники информации, принятые во внимание при экспертизе . Брик Е. А. Техника постоянных запоминающих устройств. М., Советс кое радио, 1975, с. II. 2. Шигин А. Г., Дерюгин А. А. Цифровые вычислительные машины. М., Энергия, 1975, с. 74 (прототип).

Авторы

Даты

1981-10-15—Публикация

1980-03-03—Подача