1

Изобретение относится к вычислительной технике и может быть применено в системах постоянной памяти.

Известны постоянные запоминаюидае устройства. (ПЗУ) , которые для повышения информационной емкости содержат дополнительные узлы и блоки, например сумматоры и соответствуюЙие схемы управления Щи 2.

Все ПЗУ разбито на части, при ЭТОМ требуемые коды чисел ф.ормируются на выходе сумматора как сумма нескольких слагаемых,считанных из разных частей накопителя. Понижение быстродействия устройства,объясняемое дополнительными задержками выходных сигналов, например при выполнении операции сложения в сумматоре, существенно ограничивает область применения устройства и снижает его надежность.

Известно также ПЗУ, которое, с целью расширения информационной емкости, содержит дополнительные схемы, такие как счетчик, схемы И, ИЛИ, НЕ, узел сравнения и др. З.

Однако в этом устройстве осуществляют плотное заполнение накопителя при наличии нулей в последовательности поступления информации при

вводе и выводе. Поэтому быстродействие и область применения такого ПЗУ также ограничены.

Известны постоянные запоминающие устройства, построенные по классическому принципу 4 .

Наиболее близким по технической сущности к изобретению является устройство, содержащее первый деOшифратор, входы которого соединены с выходами соответствующих млад.ших разрядов регистра адреса, а выходы с соответствующими входами блока накопителя, второй дешифратор,

5 входы которого подключены к выходам соответствующих старших разрядов регистра адреса, регистр числа, коммутатор, содержащий вентили по числу выходных шин блока накопителя, информационные входы которого подсоединены к выходным шинём блока накопителя, а управляющие входы подключены к соответствующим выходам второго дешифратора, причем выходы коммутатора подключены к соответствующим входам регистра слова, первые входы всех вентилей подключены к информационным входам коммутатора, а вторые входы вентилей, относящиеся к каждому числовому блоку, объединены и подключены к соответствующим управляющим входам коммутатора, выходы одноименных вентилей, относящиеся ко всем числовым блокам, объединены между собой и подключены к соответствующим выходам коммутатора з.

Известное устройство обладает следующими недостатками. Это, вo-пepвыx

малое быстродействие, так как при хранении большого массива слов количество числовых блоков, как правило, велико, при этом входное сопротивление каждой адресной шины, содержащей активную и реактивную составляющие, также велико, что требует формирования импульса тока опроса достаточно большой длительности и, следовательно, большого времени цикла работы устройства.

В постоянных запоминающих устройствах на ферритовыхсердечниках при применении метода шунтирования се.рдечников невыбранных числовых линеек или метода задания противотока входное сопротивление ч;исловой шины хотя и уменьшается, однако максимальное значение этого сопротивления также будет существенньгм, так как оно в большой степени зависит от величины разрядности хранимых слов. Во-вторых, это невысокая надежность, так как количество элементов связи памяти в каждом числовом блоке определяется количеством единиц нулей хранимой информации, что сказывается не только на количестве отказов устройства, но и на соотношении сигнал-помеха в выходных шинах каждого числового блока.

Цель изобретения - повышение быстродействия и надежности устройства. Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее регистр адреса, входы которого соединены с кодовыми шинами адреса, первый дешифратор, информационные входы которого соединены с соответствующими первыми выхол;ами регистра адреса, накопитель, входы которого соедиНЗны с соответствующими выходами первого дешифратора, второй дешифратор, информационные входы которого соединены с соответствующими вторыми выходами регистра адреса, коммутатор, первые информационные входы которого соединены с соответствующими выходами иа1|Ьпителя, а управляющие входы - с соответствующими выходами второго дешифратора, регистр слова, информационные входы которого соединены с соответствующими выходами коммутатора, блок управления, вход которого соединен с шиной обращения, причем управляющие входы дешифраторов и регистра слова соединены с соответствующими выходами блока управле-ния/ введен дополнительный накопитель, причем входы дополнительного

накопителя подключены к соответствущим выходам второго дешифратора, а выходы - к соответствующим вторым информационным входам коммутатора.

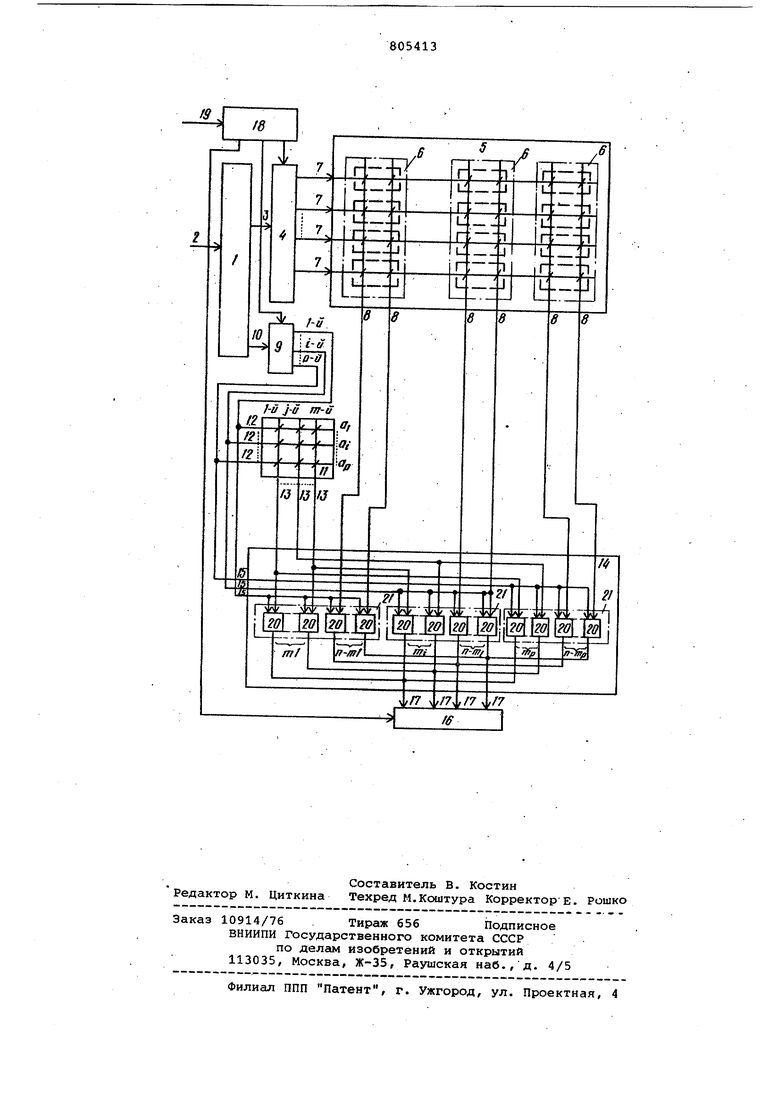

На чертеже схематически показано устройство.

Устройство содержит регистр 1 адреса, входы которого подключены к кодовым шинам 2 адреса, а выходы 3 младших ра зрядов - к соответствующим входам первого дешифратора 4, первый накопитель 5, содержащий числовые блоки 6, адресные входы 7 и выходы 8, второй дешифратор 9, входы которого подключены к соответствующим выходам 10 старших разрядов регистра 1 адреса, дополнительный накопитель 11 с адресными вХодами 12 и выходами 13, коммутатор 14, вторые информационные входы которого подключены к соответствующим выходам 13 дополнительного накопителя 11, а первые информационны входы - к соответствующим выходам 8 Первого накопителя 5.При этом управляющие входы 15 коммутатора 14 подключены к соответствующим адресн входам 12 и одноименньлм выходам второго дешифратора 9.

Кроме того,, устройство, содержит регистр 16 слова, входы 17 которого подключены к соответствующим выхода коммутатора 14, блок 18 управления, вход которого подключен к шине 19 обращения, а выходы соответственно подключены к управляющим входам регистра 1 адреса, первого дешифратор 4, второго дешифратора 9 и регистра 16 слова.

Регистр 1 адреса, регистр 16 слова, первый дешифратор-4, второй дешифратор 9 могут быть выполнены по известным классическим принципам 4 Накопитель 5 также может быть выполнен по известньам классическим принципам (см. Брик Е. А. Техника ПЗУ, М., Советское радио, 1973) и содержать числовые баеки, причем каждая адресная шина накопителя проходит последовательно через одноименные числовые линейки всех числовых блоков и подключена к соответствующему адресному входу 7 накопителя 5 (на чертеже числовые линейки условно обозначены пунктирными, а числовые блоки штрихпунктирными линиями). Каждый числовой блок б обладает выходными шинами (по количеству разрядов числового блеска) , которые подключены к соответствующим выходам 8 накопителя 5. Дополнительный накопитель 11 также может быть выполнен по известным классическим принципам. Количество адресных входов 12 (а следовательно, ячеек памяти) дополнительного нако-пителя 11 соответствует количеству числовых блоков б накопителя 5, причем первый по порядку адресный вход

12 второго блока накопителя 11 соответствует первому числовому блоку 6 первого блока накопителя 5, второй адресный вход 12 - второму числовому блоку .6 и т.д.

Кроме того, количество разрядов каждой ячейки памяти дополнительного накопителя 11 поставлено в однозначное соответствие с количеством разрядов, а следовательно, с количеством выходов 8 соответствующего числового блока 6 накопителя 5, так что если количество разрядов слов, подлежащих хранению в ПЗУ (следовательно, и количество разрядов регистра 16 слова равно И , а количество разрядов i -и по порядку ячейки хранимвго слова второго блока накопителя 11 равно , то соответствую11лее ему количество разрядов i-го числового блока б первого блока накопителя 5 равно К И - ю.

Накопители 5 и 11 могут быть выполнены с применением любых элементов связи (элементов памяти, которые на чертеже условно обозначены наклонными черточками) , при этом существо изобретения не изменяется.

Коммутатор 14 предназначен для подключения к соответствующим входам 17 регистра 16 слова () выходов 8 выбранного в соответствии с кодом адреса -j -го числового блока 6 первого блока накопителя 5 и одновременно к другим соответствующим входам 17 этого же регистра 16 MI выходов 13 дополнительного н копителя 11. При этом каждый из управляющих сигнало,в, поступающих на вход

15коммутатора 14, поставлен по номеру в однозначное соответствие с номером адресного входа 12 блока накопителя 11, номером числового блока 6 накопителя 5 и номером выхода iS roporo дешифртора 9. Так, например, нгшичие управляющего сигнала на первом по порядку входе 15 коммутатора

4 соответствует наличию выходного сигнала на первом выходе второго дешифратора 9, а также наличию этого же сигнала на первом по порядку адресном входе 12 дополнительного накопителя 11, который считывает на его выходы 13 слово с количеством разрядов Ш . При этом коммутатор 14 при дейтствии управляющего сигнаша на первом входе 15 подключает на соответсвующие входы 17 регистра

16слова W выходов 13 второго бЛока накопителя 11 и одновременно иа остальные соответствующие входы 17 H,(-yvi выходов 8 первого числового блока 6 первого блока накопителя 5, так что на регистр 16 заносится Vi-разрядное слово, подлежащее хранению в ПЗУ.

Коммутатор 4 может быть выполнен на вентилях 20, объединенных в группы 21, количество которых равно количеству числовых блоков б накопителя 5. Количество вентилей 20 в каждой группе 21 равно количеству разрядов регистра 16 слова и, следовательно, количеству разрядов слова, подлежащих хранению в ПЗУ.

Устройство работает следующим образом.

Пусть имеется множество М слода разрядностью ri , подлежащих хранению , в постоянном запоминающем устройс 0ве. В этом множестве всегда можно отыскать слова подмножества A.J (i 1,2,...р), в каждом из которых значения Ш разрядов из h ( совпадают со значениями одноименных

5 разрядов всех слов подмножества, т.е. в каждом подмножестве А i разрядов являются общими для всех слов подмножетства A-j . Вьоделенные разряды KHj образуют слово 01, кото0рому присваивают индекс подмножества, из которого оно образ овано. Из кгикдого подмножества А образуют подмножество & с разрядностью слов (() / которое хранят в 1-ом числовом блоке, а соответствующее ему

5 слово с количеством разрядов хранят в дополнительном накопителе 11, причем i-ому числовому блоку 6 соответствует i-oe слово в дополнительном накопителе 11, т.е.

0 i-й адресный вход 12.Таким образом максимальное количество слов в дополнительном накопителе 11 равно количеству числовых блоков 6,содержащих подмножества а коли5чество разрядов (выходов 13) второго блока накопителя 11 равно максимальному значению величины ht. При этом всегда .

При обращении к постоянному запоминающему устройству на шине 19

0 выставляют сигнал обращения, который поступает на соответствующий вход блока 18 управления. Блок 18 управления вырабатывает на своих выходах управляющие сигналы, которые

5 в соответствующие моменты времени поступают на управляющие входы регистра 1 адреса первого дешифратора 4, второго дешифратора 9 и регистра 16 слова, разрешая их функциониро0вание.

Код адреса, поступающий по кодовым шинам 2 адреса, заносят на регистр 1 адреса,при этом младшие разряды кода адреса с выходов 3 регистра 1 адреса поступают на соответствующие входы первого дешифратора 4, а старшие разряды с выходов 10 этого же регистра поступают соответственно на входы второго дешифратора 9.

Первый дешифратор 4 на одном из своих выходов в соответствии с коом адреса вырабатывает сигнал опроса, который поступает на соответт

ствующий адресный вход 7 и воздействует на элементы связи (памяти ) последовательно включенных числовых линеек, по одной в каждом числовом блоке 6.

На выходах 8 первого блока накопителя 5 появляются выходные сигналы, соответствующие кодам слов подмножества В, записанных в выбранных числовых линейках всех числовых блоков 6. Эти выходные сигналы поступают на соответствующие первые входы коммутатора 14. Второй дешифратор 9 вырабатывает в соответствии со значениями старших разрядов кода адреса на одном из своих 1-Ых выходов сигнал, который поступает на соответствующий выбранному i -ому числовому бло.ку 1 -и адресный вход 12 дополнительного накопителя 11 для считывания слова , Щ разрядов которого являются общими для всех слов подмножества В, находящихся в выбранном числовом блоке.

Этот же сигнал с выхода второго дешифратора 9 поступает также на соответствующий управляющий вход 15 коммутатора 14, разрешая прохождение через коммутатор 14 соответствующих сигналов как с выходов 8 выбранного числового блока 6, так и с выходов 13 дополнительного накопителя 11.

При этом на входы регистра 16 .слова поступает нужное слово исходного множества М, сформированное путем пристыковки соответствующих () разрядов, считанных из 1-го числового блока 6, и разрядов, считанных из дополнительного накопителя 11.

Выходные сигналы, считанные с остальных числовых блоков б, на выходы регистра 16 слова не проходят, так как на остальных управляющих входах коммутатора 14 сигналы разрешения отсутствуют.

По сравнению с известным устройством при той же информационной емкости входное сопротивление адресно шины уменьшается, так как уменьшается количество элементов памяти, принадлежащих выбранной адресной шине. При этом соответственно уменьшается и длина каждой адресной шины, а акже общее количество элементов памяти накопителя. Все это приводит к уменьшению времени переходных процессбв во входных цепях накопителя, к уменьшению различного рода наводок и, следовательно, к повы1иению быстродействия и надежности устройства.

Так как емкость памяти второго блока накопителя чрезвычайно мала, а. возбуждение его адресных входов осуществляют от второго дешифратора, не связанного с первым дешифратором, то применение дополнительного накопителя 11 не сказывается на снижении положительного эффекта.

Формула изобретения

Постоянное запоминающее устройство, содержащее регистр адреса, входы которого соединены с кодовыми шинами адреса, первый дешифратор, информационные входы которого соединены с соответствующими первыми выходами регистра адреса, накопитель, входы которого соединены с соответствующими выходами первого дешифратора, второй дешифратор, информационные входы которого соединены с

5 соответсвующими вторыми выход ми

регистра адреса, коммутатор, первые информационные входы которого соединены с соответствующими выходами накопителя, а управляющие входы - с

соответствующими выходами второго де шифратора,регистр слова,информационные входы которого соединены с соответствующими выходами коммутатора, блок управления,вход которого соединено шиной обращения,причем управляющие входы дешифраторов и регистра слова соединены с соответствующими выходами блока управления,, о т л и ч а ю щ е е с я тем,что,с целью повышения быстродействия и надежности

0 устройства, в него введен дополнительный накопитель,причем входы дополнительного накопителя подключены к соответствующим выходам второго дешифратора, а выходы - к соответствуюс щим вторым ин-формациокным входам коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 490184, кл. G 11 С 17/00, 1975.

2.Авторское свидетельство СССР № 468304, кл. G 11 С 17/00, 1975.

3.Авторское свидетельство СССР № 488255, кл. G 11 С-9/00, 1975.

4.Брик Е. А. Техника ПЗУ. К., 5 Советское радио., 1973.

5.АвторскО свидетельство ЕССР 461451, кл. G 11 С 17/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устрой-CTBO | 1979 |

|

SU809379A1 |

| Постоянное запоминающее устройство для многоместных симметричных функций | 1979 |

|

SU873277A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

Авторы

Даты

1981-02-15—Публикация

1978-11-30—Подача