поминающим устройствам, и может быт:.. применено в системах сложной логической обработки данных. Целью изобретения является расширение функциональных возможностей устройства за счет выполнения операции уплотнения информации в матрице запоминающих элементов. Устройство содержит матрицу I запоминающих элементов 2, например тероидальных ферритовых сер- дечников с прямоугольной петлей гистерезиса, организованных в горизонтальные 4 и вертикальные 3 числовые линейки с разрядными 5 и числовыми 7 пинами выборки, разрядными 6 и числовыми 8 шинами считьшания, две группы 9 , 12 формирователей сигналов записи, две группы 10, 11 формирователей сигналов считывания, усилители 13 считывания числа, усилители 15 считьгоания разряда, регистры 17 и 20 числа, регистр 23 информации разряда, группы элементов ИЛИ 26, 27, 35, 63, 70, 76, элемент ИЛИ 29, регистр 36 номера разряда нулевых значений, регистр 38 номера разряда единичных значений, счетчик 43, регистры 47 и 51 адреса, предназначенные для хранения соответственно кода адреса верхней и нижней границ сте1

Изобретение относится к тельной технике, в частности к запоминающим устройствам, и может быть использовано в системах сложной логической обработки данных.

Целью изобретения является расширение функциональных возмо кностей устройства за счет вьтолнения операции уплотнения информации в матрице запоминающих элементов.

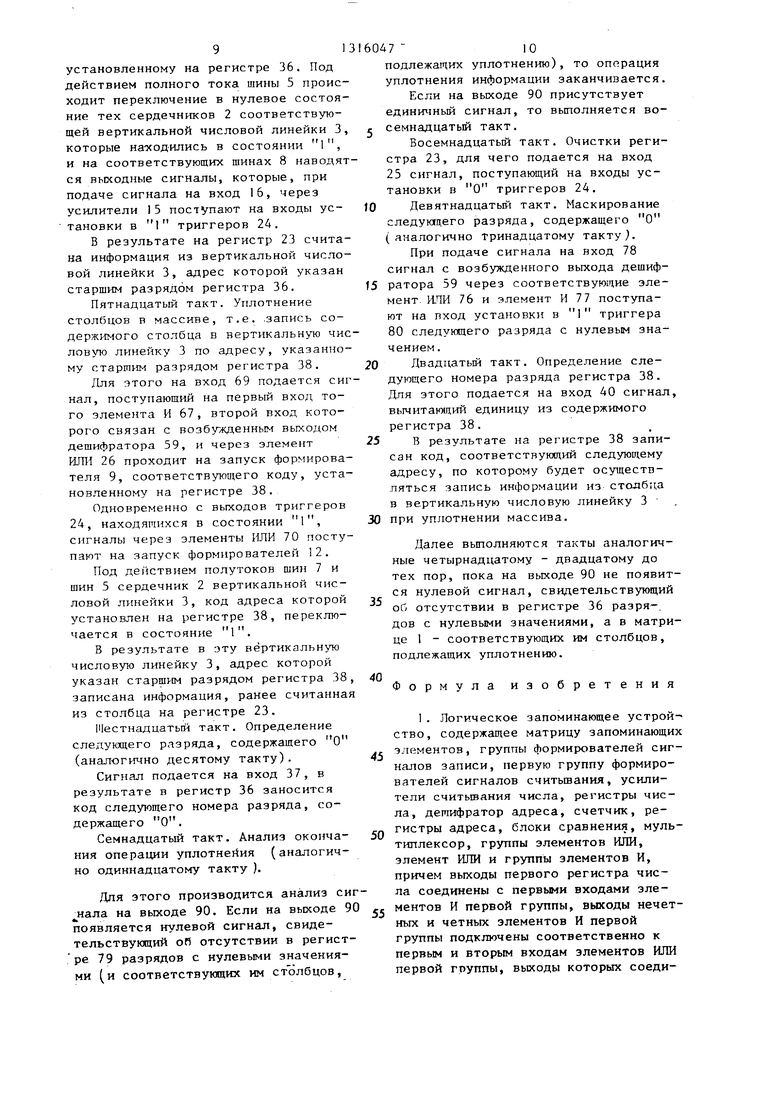

На чертеже представлена функциональная схема предложенного уст. ройства.

Устройство содержит матрицу 1 запоминающих элементов 2, организованных в вертикальные числовые линейки 3 и горизонтальные числовые линейки 4, с разрядными шинами 5 выборки, разрядными шинами 6 считьгеания,

ка, блоки 50, 55-57 сравнения, мультиплексор 58, дешифратор 59 адреса, логический блок 71, группы элементов И 60, 61, элементы И 62, 64 третьей группы элементов И 66, 67, 77 с четвертой по шестую, регистр 79 информации стека, шифраторы 82 и 83. Часть числовых линеек 4 используется для хранения результатов обработки массива информации и называется стеком. После определения совпадающих по содержимому числовых линеек 3 ( столбцов ) в линейках 4 стека записаны слова, количество которых равно числу групп совпадающих столбцов, а количество единиц в каждом слове равно количеству совпавших столбцов, причем единицы стоят в разрядах, сооветствующих этим столбцам. Слова из стека считьтаются поочередно в регис 79, на основании содержимого которог вьшолняется уплотнение информации совпавших столбцов в обрабатьшаемом массиве, т.е. перемещение информации из всех совпавших столбцов группы в один, адрес которого определяется номером старшего разряда, содержащего единицу,врегистре 79.1 з.п. ф-лы, 1 ил.

числовыми шинами выборки 7 и считывания 8, первую группу формирователей 9 сигналов записи, первую 10 и вторую 11 группы формирователей

сигналов считывания, вторую группу формирователей 12 сигналов записи, усилители 13 считьтания числа с управляющими входами 14, усилители 15 считывания разряда с управляющими

входами 16, первый регистр 17 числа, выполненный из триггеров 18, с входом 19 сброса, второй регистр 20 числа, выполненный из триггеров 21, с входом 22 сброса, регистр 23 информации

разряда, выполненный из триггеров 24, с входом сброса 25, первую группу элементов ИЛИ 26, вторую группу элементов ИЛИ 27 с информационными входами 28 устройства, первый элемент

RriH 29. На чертеже обозначены первый 30 и нторой 31 входы обращения, вход 32 регенерации, первый числово вход 33 считьшания, третий вход 34 обращения.

Устройство содержит также третью группу элементов ИЛИ 35, регистр 36 номера разряда нулевых значений с входом 37 управления, регистр 38 номера разряда единичных значений с входами управления 39-41 и входом сброса 42, счетчик 43 с входами сброса 44 и управления 45 и адресными входами 46, первый регистр 47 адреса с входами 48 и 49 управления предназначенный для хранения прямого кода адреса и являюг(егося прямым указателем стека, первый блок 50 сравнения, второй регистр 51 адреса предназначенный для хранения инверсного кода адреса, являющегося инверсным указателем стека, с входами 52 и 53 управления и входом 54 сброса, блоки 55-57 сравнения с второго по четвертый, мультиплексор 58, дешифратор 59 адреса, первую 60 и вторую 61 группы элементов И, одни из элементов И 62 третьей группы, четвертую группу злементов ИЛИ 63, другие злементы И 64 третьей группы с входами 65, четвертую 66 и пятую 67 группы -чпементов И с разрядными входами 68 считьюания и 69 записи устройства, пятую группу элементов ИЛИ 70, логический блок 71, выполненный из группы элементов ИЛИ 72, элемент НЕ 73. группы элементов РШИ 74 и элементов И 75.

I

Устройство содержит также шестую

группу элементов ИЛИ 76, шестую группу элементов И 77 с входом 78 опроса, регистр. 79 информации стека, выполненный из триггеров 80, с входом 81 сброса, первьв 82 и второй 83 шифраторы. Fia чертеже обозначены информационные выходы 84 и 85 и индикаторные выходы 86-90 с первого по пятьп1 устройства. В качестве запо минающих элементов 2 могут быть применены тороидальные сердечники с прямоугольной петлей.

Устройство работает следующим образом,

в процессе функционирования устройства часть числовых линеек 4 матриц I используются для хранения результатов обработки массива инфор

мании и назьшаются в дальнейшем стеком .

После окончания операции нахождения совпадающих числовых линеек 3, с т.е. столбцов в чис:ювых линейках 4 стека записаны слова, количество которых соответствует количеству групп совпадаюп;их столбцов, а количество I в каждом слове равно количеству

0 совпадающих столбцов, npiweM 1 стоят в разрядах, соответствующюс этим столбцам.

Слова из числовых линеек 4 стека считываются в регистр 79, на основаi НИИ содержимого которого осуществляется операция уплотнения информации из столбцом в матрице 1. Разряды регистра 79, содержащие О, которые соответствуют несовпадающим

0 столбцам в матрице I, необходимо

оставить, а разряды, содержащие 1, которые соответствуют совпадающим столбцам, подлежат удалению.

5

0

5

0

д

г

Однако в каждой из групп совпадающих столбцов первые (левые) столбцы, которым в регистре 79 соответствуют также единичные разряды, необход1тмо сохранить для идентификации информации в матрице 1.

Поэтому при считывании слов в регистр 79, старщие (левые) разряды, имеюи1ие всегда значения, равные 1, проходя через блок 71 инвертируются, изменяя свои значения на нулевые, остальные же разряды проходят без изменений.

Далее в регистре 79 посредством шифратора 82 определяется номер старшего разряда, содержащего I. Ло- скольку впереди него всегда имеются разряды с нулевыми значениями, то они маскируются, т.е. в них заносятся 1. При помощи шифратора 83 опре- j деляется номер старшего разряда,

содержащего О. В матрице 1 по адресу, соответствующему данному номеру, из вертикальной числоBOI I линейки 3 (столбца )происходит считывание ин- Лормации и запись ее по адерсу, соответствующему номеру разряда с единичным значением, т.е. осуществляется перемещение содержимого столбца влево, в сторону первых столбцов матрицы.

Далее номер разряда единичных значений уменьшается на единицу, маскируется номер старшего разряда с нулевым значением и определяется номер

следующего разряда, содержащего О. Осуществляется считьшание информации из столбца по адресу, соответствующему иомеру следующего разряда с нулевым значением и запись его по адресу, , соответствующему уменьшенному на единицу значению номера старшего разряда, содержащего 1 и т.д.

Г- и

Таким образом, осуществляется уплотнение информации из столбцов ffl в матрице 1.

При реализации операции уплотнения столбцов выполняются следующие такты.

Первый такт. Определение кода адре- 5 мент РШИ 35 и элемент И 6 происхо- са последней числовой линейки 4 сте - дит запуск формирователя 12, соотустановки в 1 триггеров 21 регист ра 20.

В результате выполнения второго такта в регистр 79 заносится считан ное из стека слово.

Третий такт. Восстановление слов считанного из стека. На вход 32 подается сигнал, поступаюпщй через те из элементов И 62, входы которых связаны с выходами триггеров 21 регистра 20, находящихся в состояни 1, и далее через соответствующие элементы Ш1И 26 для запуска формиро вателей 9. Одновременно через элека.

После окончания операции нахождения совпаджощих столбцов в массиве на регистре 47 (или на регистре 51 - в зависимости от выполняемого шага) записан код, совпадающий с кодом адреса числовой линейки 4 на едини цу большим (или на единицу меньшим) того, в которой записано последнее слово .

Для определения этого кода адреса на вход 49 (или на вход 52 - в звисимости от вьтолняемого щага) подается сигнал, уменьшающий содержимое регистра 47 на единицу (или увеличивающий содержимое регистра 51 на единицу).

В результате выполнения первого такта на регистре 47 (или на регистре 51) записан код адреса числовой линейки 4 стека, в которой находится последнее слово стека.

Второй такт. Считьшание слова из стека на регистр 79,для чего на вход 33 подается сигнал, поступающий через элемент ИЛИ 35 и элемент И 61 , второй вход которого связан с возбужденным входом дешифратора 59 для запуска формирователя I1, соответствующего коду, установленному на регистре 47 (или регистре 51).

Под действием полного тока горизонтальной шины 7 выборки происходит переключение в нулевое состояние тех сердечников 2 первой числовой лииейки стека в матрице I, которые находились в состоянии 1, и на соответствующих шинах 6 наводятся выходные с 1гналы, которые при подаче сигнала на вход 14, через усилители 13 одновременно поступают на вход

установки в 1 триггеров 21 регистра 20.

В результате выполнения второго такта в регистр 79 заносится считанное из стека слово.

Третий такт. Восстановление слова считанного из стека. На вход 32 подается сигнал, поступаюпщй через те из элементов И 62, входы которых связаны с выходами триггеров 21 регистра 20, находящихся в состоянии 1, и далее через соответствующие элементы Ш1И 26 для запуска формирователей 9. Одновременно через элеветствующего числовой линейке 4 стека, из которой бьшо считано слово. При этом те сердечники 2 числовой линейки 4, на которые воздействуют полутоки горизонтальных 7 и вертикальных 5 щин выборки, переключаются в состояние 1.

В результате в числовой линейке 4 стека восстановлено слово.

Четвертый такт. Пересылка слова из регистра 20 на регистр 79.

Для этого подается сигнал на вход 81, в результате с прямых выхо30 дов триггеров 2 регистра 20 сигналы поступают на первые входы элементов ИЛИ 72 блока 71, сигналы с выходов элементов И 75 которого, инвертируя значение самого старшего j разряда, через элементы ИЛИ 76 и

элементы И 77 поступают на входы установки в 1 триггеров 80.

Пятый такт. Очистки регистра 20, 40 для чего сигнал подается на вход 22 для установки в О триггеров 21.

Шестой такт. Анализ слова, записанного на регистре 20.

45 Л-пя этого производится анализ сигнала на выходе 87 блока 50 (ипи на выходе 88 блока 55 - в зависимости от вьтолняемого шага).

Единичный сигнал на выходе 87

5Q (или 88) появляется только в том случае, если код, установленный на регистре 47, совпадает с кодом адреса верхней границы стека (или код на регистре 51 - с кодом адреса нижней

55 границы стека), для чего на блок 50 (или на блок 55) из внешнего блока управления устройством (не показанном) , поступает значение соответствующего кода адреса границы стека.

71

Если на выходе 87 (или на выходе 88 i присутствует единичный сигнал, свидетельствующий о том, что из стека считано последнее слово, го , осуществляется переход к седьмому такту, в противном случае - к первому такту.

Седьмой такт. Определение номера самого старпшго разряда, содержащего 1.

Сигнал подается на вход 41, в результате с выходов щифратора 82 в регистр 38 заносится номер самого старшего разряда, содержащего 1.

Восьмой такт. Маскирование самого старшего разряда слова, записанного на регистре 79.

Номер самого старшего разряда регистра 79 заносится в счетчик 43.

Код номера самого старшего разряда через мультиплексор 58 поступает на дешифратор 59, сигнал с соответ- ствукицего возбужденного выхода которого через элемент ИЛИ 76 и элемент И 77 при подаче сигнала на входы 78 поступает на вход установки в 1 триггера ВО самого старшего разряда регистра 79.

В результате в самый старший разряд регистра 79 заносится 1.

Девятый такт. Анализ результатов сравнения содержимого счетчика 43 и регистра 38 и уменьшение на единицу кода, записанного на счетчике 43

Для этого производится анализ сигнала на выходе 89. Если на выходе 89 присутствует О, то на вход 45 подается сигнал, вьгчитающий единицу из содержимого счетчика 43. На счетчике 43 устанавливается код номера разряда, находящегося справа от самого старшего, и осуществляется его маскирование (аналогично восьмому такту) .

Маскирование следующих разрядов регистра 79 будет осуществляться до тех пор (аналогично восьмому и девятому тактам), пока содержимое счетчика 43 не станет равным содержимому регистра 38, о чем свидетельствует единичньй сигнал на выходе 89.

Десятый такт. Определение номера старшего разряда, содержащего О.

Сигнал подается на вход 37, в результате с выходов шифратора 83 в регистр 36 заносится номер старшего разряда, содержащего О, так

6047g

как разряды с нулевыми значениями, находящиеся до первого единичного разряда, замаскированы единицами.

Одиннадцатьш такт. Анализ на на- 5 личие в регистре 36 разрядов, содержащих О.

Для этого производится анализ сигнала на выходе 90, причем на одни из входов блока 57 поданы сигналы 10 с выходов регистра 36, а на другие поданы значения О.

Если на выходе 90 появляется сигнал, свидетельствующий об отсутствии в регистре 79 разрядов с нулевы- )5 ми значениями и соответствующим столбцам в массиве, подлежащих уплотнению, то вьшолняется двенадцатый такт.

Если на выходе 90 присутствует 0 едиштчный сигнал, то выполняется тринадцатый такт.

Двеналцатый такт. Определение н1И(ней границы уплотненного массива. Для этого подается сигнал на вход 39,

25

уБел1гчивающий на единицу содержимое

регистра 38. В результате на регисре 38 записан код, соответствующий последнему адресу уплотненного массива .

30 После этого операция уплотнения закаьгчивается.

Верхняя граница массива (первый адрес) определяется номером самого старшего разряда слова.

35 Тринадцатый такт. Маскирование старшего разряда, содержащего О.

Код номера старшего разряда, содержащего О, записанный на регистре 79, с выхода регистра 36 че40 рез мультиплексор 58 поступает на дешифратор 59, сигнал с соответствующего возбужденного выхода которого через элемент ШШ 76 и элемент И 77 (при подаче сигнала на вход 78

45 поступает на вход установки в 1 триггера 80 старшего разряда с ну- левыь значением.

Четырнадцатый такт. Уплотнение столбцов в массиве, т.е. считьшание

50 информации из столбца по адресу, указанному старшим разрядом регистра 36, на регистр 23.

Для зтого подается на вход 68 сигнал, поступающий на второй вход того элемента И 67, первый вход которого связан возбужденным выходом дешифратора 59, для запуска формирователя 10, соответствующего коду.

913

установленному на регистре 36. Под действием полного тока шины 5 происходит переключение в нулевое состояние тех сердечников 2 соответствующей вертикальной числовой линейки 3, которые находились в состоянии 1, и на соответствующих шинах 8 наводятся выходные сигналы, которые, при подаче сигнала на вход 16, через усилители 15 поступают на входы установки в 1 триггеров 24.

В результате на регистр 23 считана информация из вертикальной числовой линейки 3, адрес которой указан старшим разрядом регистра 36.

Пятнадцатый такт. Уплотнение столбцов в массиве, т.е. .запись содержимого столбца в вертикальную числовую линейку 3 по адресу, указанному старшим разрядом регистра 38.

Для этого на вход 69 подается сигнал, поступающий на первый вход того элемента И 67, второй вход которого связан с возбужденным выходом ешифратора 59, и через элемент Р1ПИ 26 проходит на запуск формирователя 9, соответствующего коду, установленному на регистре 38.

Одповременно с выходов триггеров 24, находяиихся в состоянии 1, сигналы через элементы ИЛИ 70 поступают на запуск формирователей 12.

Под де1 1ствием полутоков шин 7 и шин 5 сердечник 2 вертикальной числовой линейки 3, код адреса которой установлен на регистре 38, переключается в состояние 1.

В результате в эту вертикальную числовую линейку 3, адрес которой указан старшим разрядом регистра 38, записана информация, ранее считанная из столбца на регистре 23.

|11естнадцатыи такт. Определение следующего разряда, содержащего О (аналогично десятому такту).

Сигнал подается на вход 37, в результате в регистр 36 заносится код следующего номера разряда, содержащего О.

Семнадцатый такт. Анализ окончания операции уплотнейия (аналогично одиннадцатому такту ).

Для этого производится анализ сиг- нала на выходе 90. Если на выходе 90 оявляется нулевой сигнал, свидеельствующий of5 отсутствии в регист- ре 79 разрядов с нулевыми значениями (и соответствующих им столбцов,

47 10

подлежащих уплотнению), то операция уплотнения информации заканчивается.

Если на выходе 90 присутствует единичный сигнал, то выполняется восемнадцатый такт.

Восемнадцатый такт. Очистки регистра 23, для чего подается на вход 25 сигнал, поступающий на входы установки в О триггеров 24.

Девятнадцатый такт. Маскирование следующего разряда, содержащего О (аналогично тринадцатому такту). При подаче сигнала на вход 78 сигнал с возбужденного выхода дешифратора 59 через соответствующие элемент. ИЛИ 76 и элемент И 77 поступают на вход установки в I триггера 80 следующего разряда с нулевым значением.

Двадцатый такт. Определение следующего номера разряда регистра 38. Для этого подается на вход 40 сигнал, вьгчитакяций единицу из содержимого регистра 38.

В результате на регистре 38 записан код, соответствующий следующему адресу, по которому будет осуществляться запись информации из столбца в вертикальную числовую линейку 3

при уплотнении массива.

Далее выполняются такты аналогичные четырнадцатому - двадцатому до тех пор, пока на вьгходе 90 не появится нулевой сигнал, свидетельствующий об отсутствии в регистре 36 разря-. дов с нулевыми значениями, а в матрице 1 - соответствующих им столбцов, подлежащих уплотнению.

40

Формула изобретения

1 . Логическое запоминающее устрой- ство, содержащее матрицу запоминающих

элементов, группы формирователей сигналов записи, первую группу формирователей сигналов считьшання, усилители считьшания числа, регистры числа, дешифратор адреса, счетчик, регистры адреса, блоки сравнения, мультиплексор, группы элементов ИЛИ, элемент ИЛИ и группы элементов И, причем вьрсоды первого регистра числа соединены с первыми входами элементов И первой группы, выходы нечетных и четных элементов И первой группы подключены соответственно к первым и вторым входам элементов ИЛИ первой группы, выходы которых соедии1

йены с входами формирователей сигналов записи первой группы, выходы которых подключены к разрядным шинам выборки матрицы, разрядные шины считьгоания которой соединены с информационными входами усилителей считывания числа, выходы которых подключены к информационным входам второго регистра числа, выходы элементов ИЛИ второй группы соединены с информационными входами первого регистра числа, выход одного из элементов ИЛИ третьей группы соединен с первыми входами четных элементов И второй группы, выход элемента НИИ подключен к вторым входам четных элементов И первой группы и первому входу другого элемента 1ПИ третьей- группы, выход которого соединен с первыми входами нечетных элементов И второй группы, выходы формирователей записи второй группы подключены к числовым шинам выборки матрицы, вторые входы элементов И второй группы соединены с выходами дешифратора адреса, входы которого соединены с выходами мультиплексора, одни из входов которого подключены к од- ним из выходов первого и второго регистров адреса и счетчика, другие выходы которых соединены соответственно с одними из входов блоков сравнения с первого по третий, выходы второго регистра числа подключены к первым входам элементов И третьей группы, выходы четных элементов И третьей группы соединены с третьими входами элементов ИЛИ первой группы, первые входы первого элемента И четвертой группы и первого элемента ИЛИ четвертой группы подключены к первому выходу, а вторые входы - к второму выходу второго регистра числа, первые входы каждых последующих элемента И и элемента ИЯИ четвертой группы соединены соответственно с выходом предьдущего элемента ИЛИ и с выходом предыдущего элемента И, а вторые входы - с последующим выходом второго регистра числа, второй вход последнего элемента И четвертой группы подключен к выходу предыдущего элемента И четвертой группы, выходы нечетных элементов И третьей группы соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых являются информационными входами устройства, одними из информационных выходов которого яв47 12

ляются выходы усилителей считывания числа, первый вход элемента ПНИ является первым входом выборки устройства, вторые входы нечетньгх элементов И первой группы соединены с вторым входом другого элемента Ш1И третьей группы и являются вторым входом выборки устройства, первый вход одного из элементов ИЛИ третьей

группы является первым числовым входом считьшания устройства, а второй вход одного из элементов ИЛИ третьей группы соединен с вторым входом элемента ИЛИ и является третьим входом обращения устройства, третий вход другого элемента ИЛИ третьей группы подключен к вторым входам четных элементов И третьей группы и является входом регенерации устройства, одними из входов сброса которого являются управляющие входы регистров числа, вторые входы нечетньгх элементов И третьей группы, установочные входы регистров адреса и вход

сброса счетчика, управляющие входы усилителей считьшания первой группы объединены и являются вторым числовым входом считывания устройства, управляющие входы регистров адреса

являются управляющими входами устройства, информационные и счетный входы счетчика являются адресными входами устройства, первым индикаторным выходом которого является выход последнего элемента И четвертой группы, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения операции уплотнения информации в матрице, в устройство введены вторая группа формирователей сигналов считьтания, усилителей считьшания разряда, регистр информации разряда, регистр номера разряда нулевых значений, регистр номера разряда единичных значений, логический блок, пятая и шестая группы элементов И, третий и четвертый блоки сравнения, пятая и шестая группы элементов ИЛИ, шифраторы и регистр информации стека, причем входы логического блока соединены с выходами второго регистра слова, а выходы логического блока - с первыми входами элементов ИЛИ шестой группы, кроме первого, первый вход которого подключен к шине нулевого потенциала, выходы элементов ИЛИ шестой группы соединены с первыми входами элементов И шее131

той группы, выходы которых подключены к информационным входам регистра информации стека, прямые выходы которого соединены с входами первого шифратора, а инверсные выходы - с входами второго шифратора, выходы первого и второго шифраторов подключены соответственно к информационным входам регистра номеров разрядов единичных значент и регистра номеров разрядов нулевых значений, одни из выходов которых соединены соответственно с одними из входов третьего и четвертого блоков сравнения, другие выходы регистра номеров разрядов единичных значений и регистра номеров разрядов нулевых значений,подключены к входам мультиплексора, другие входы третьего блока сравнения соединены с другими выходами счетчика, первые входы элементов ИПН пятой группы подключены к выходам нечет- ньк элементов И второй группы, а выходы - к входам формирователей сигналов записи второй группы, входы формирователей сигналов считьгоания второй группы соединены с выходами четных элементов И второй группы, а выходы - с числовыми шинами выборки матрицы, числовые шины считьтания которой подключены к информационным входам усилителей считывания разряда выходы которых соединены с информационными входами регистра информации разряда, выходы которого подключены к вторым входам злементов ИЛИ пятой группы, вторые входы элементов ПНИ шестой группы соединены с выходами дешифратора адреса и первыми входами элементов И пятой группы, выходы нечетных элементов И пятой группы подключены к четвертым входам элементов ИЛИ первой группы, а выходы чет- тта элементов И пятой группы - к входам формирователей сигналов считьша- ния, выходы которых соединены с разСоставитель Т.Зайцева Редактор Г.Гербер Техред Л.Олийньж Корректор Г.Регаетник

Заказ 2369/54 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-З), Раушская наб. , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

714

рядными тинами выборки матрицы, вторые входы четных элементов И пятой группы объединены и являются первым разрядным входом считьшания устрой- ства, вторым разрядным входом считывания которого являются объединенные управляющие входы усилителей считывания чисел, выходы которых являются другими информационными выходами

устройства, вторые входы нечетных элементов И пятой группы являются разрядным входом записи устройства, индикаторными выходами с второго по пятый которого являются выходы блоков сравнения с первого по четвертый, вторые входы элементов И шестой группы являются входом опроса устройства, управляющие входы регистра информации стека, регистра номеров

разрядов единичных значений и регистра номеров разрядов нулевых значений являются входами сброса устройства . I

2. Устройство по п.1, о т л и - чающееся тем,что логический блок содержит первую и вторую группы элементов ИЛИ, элементы НЕ и элементы И, выходы которых являются выхо- дами блока, причем первые входы первых элементов ИЛИ первой и второй групп объединены и являются одним из входов блока, выход каждого элемента ИЛИ первой группы подключен к первым входам последующих элементов ИПИ первой и второй групп и входу одноименного элемента НЕ, выход которого соединен с вторым входом одноименного элемента ИЛИ второй груп- пы, выход которого подключен к первому входу одноименного элемента И, второй вход которого соединен с вторым входом одноименного элемента ИЛИ первой группы, вторые входы элемен- тов ИЛИ первой группы являются другими входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Логическое запоминающее устройство | 1987 |

|

SU1566411A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к вычис- лительяой технике, в частности к заi (Л оо О5 о 4:;

Авторы

Даты

1987-06-07—Публикация

1986-01-06—Подача