Изобретение может быть использовано для подсчета суммарного числа импульсов нескольки.х иотоков, не синхронизирова,ниых между собой.

Известны многовходовые счетчики импульсов для суммарного подсчета числа импуль сов, поступающих одновременно но нескольким входам, содержащие счетный регистр, Нс. триггерах и запоминающие ячейки с параллельным вводом информации. В случаях, когда вероятность совпадения импульсов в различных потоках мала или при низких требованиях к точности счета, все входы подключаются ко входу счетного регистра через собирательную схему «ИЛИ. Ир.и повышенной точности счетчики обычно снабжены по каждомуканалу запоминающей ячейкой. Содержимое ячеек выявляется при номощИ устройства последовательного опроса, а импульсы, появившиеся в результате опроса, также через собирательную схему отправляются в собственно счетчик (счетный регистр).

Иедостатком такого счетчика является низкая частота, с которой могут следовать импульсы но каждому входу. В самом деле, при заданной максимальной скорости счета регистра период следования импульсов но любому входу очевидно должен не менее чем в п раз превыщать разрешающее время регистра, где п - число входов.

Цель изобретения - повыщение предельной частоты следования импульсов по каждому входу. Эта цель достигается тем, что предлагаемый МНОГОВХОДОВОЙ счетчик импульсов содержит однорядные двоичные сумматоры, разделенные на стуиени, причем выходы сумматоров «изщей ступени подключены ко входам сумматоров высщей ступени, выходы сумматоров последней ступени связаны со счетными

входами триггеров счетного регистра, а входы сумматоров младщей стуиени соединены с выходами запоминающих ячеек.

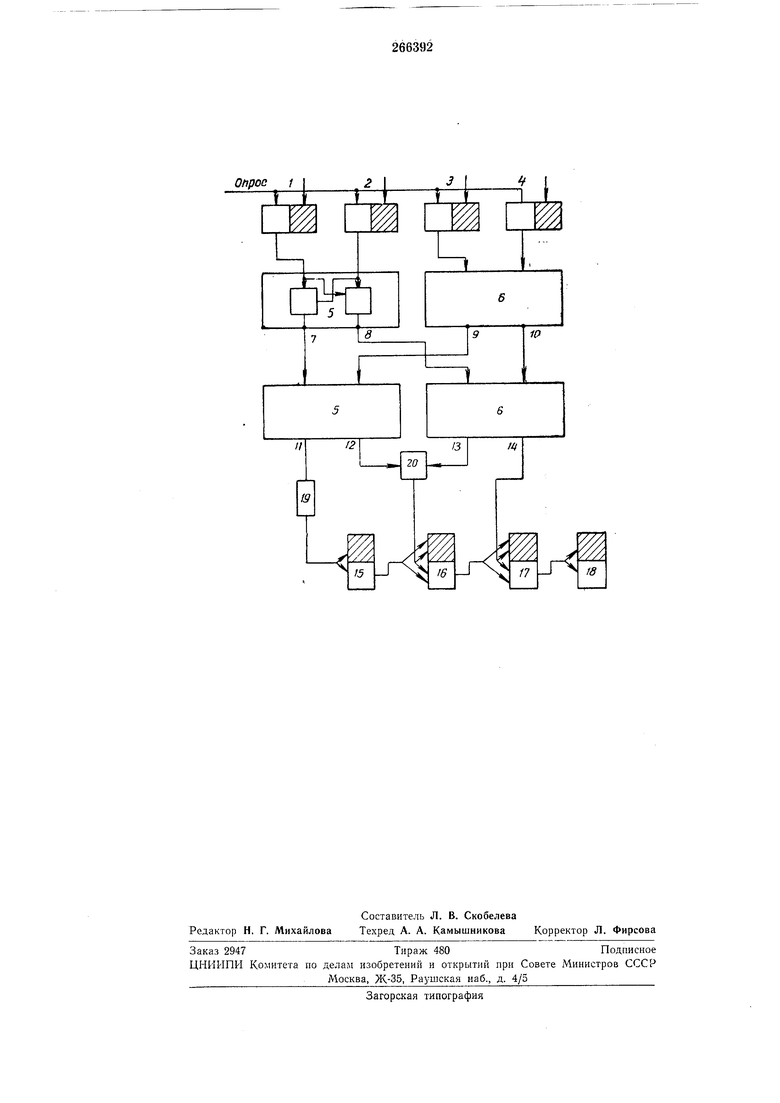

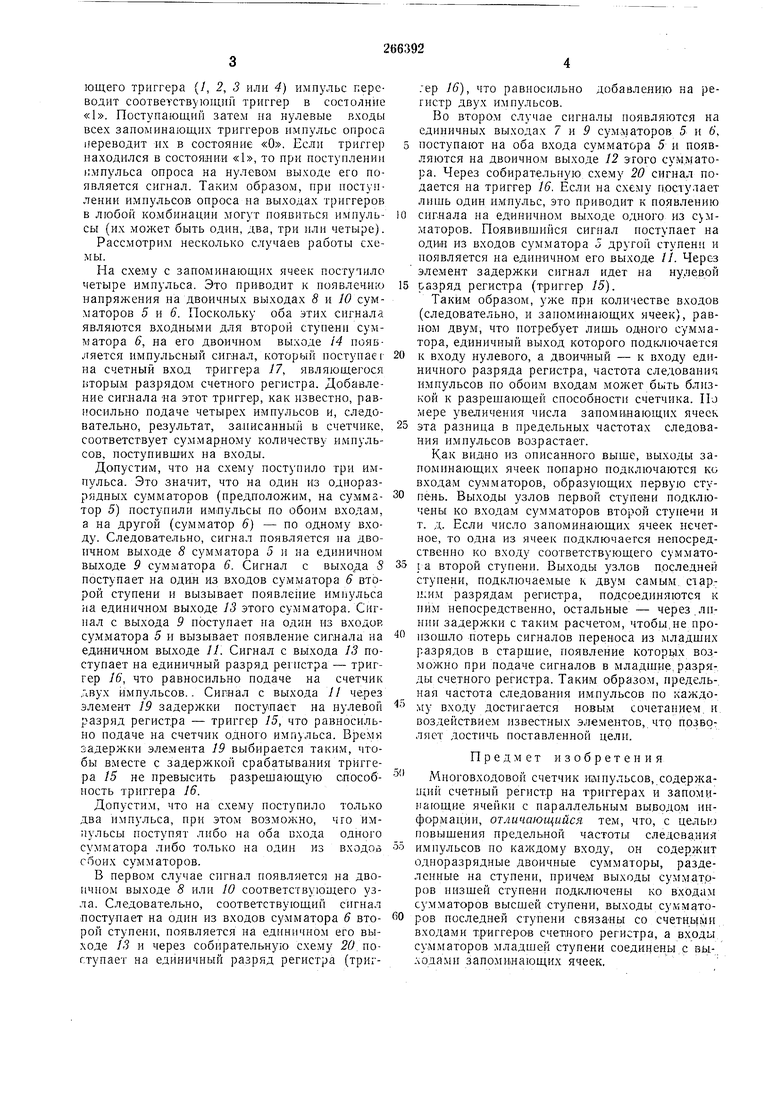

На чертеже показана схема счетчика. Счетчик содержит запомииающие ячейки,

выполненные в данном случае на триггерах /-4. Единичные входы этих триггеров ЯРЛЯ ются входами счетчика, а нулевые их входы связаны с щиной, на которую подаются импульсы опроса.

Нулевые выходы триггеров связаны с одноразрядными двоичными сумматорами 5 и 6, разделенными на ступени, причем выходы 7-10 сумматоров низгией ступени подключены ко входам сумматоров высщей ступени, выхоДЫ //-14 сумматоров последней ступени связаны со счетными входами триггеров 15-18 счетного регистра, а входы сумматоров младшей ступени соединены с выходами заиомкнйюищх ячеек.

ющего триггера {/, 2, 3 или 4) импульс переводит соответствующий триггер в состо/тние «1. Поступающий затем на нулевые входы всех запоминающих триггеров импульс опроса переводит их в состояние «О. Если триггер находился в состоянии «1, то при поступлении импульса опроса на нулевом выходе его появляется сигнал. Таким образом, при постунvieHHH импульсов опроса на выходах триггеров в любой комбинации могут появиться имиульсы (их может быть один, два, три или четыре).

Рассмотрим несколько случаев работы схемы.

На схему с запоминаЕОЩИх ячеек ностутило четыре импульса. Это приводит к ноявлен.ию напряжения на двоичных выходах 8 и 10 сумматоров 5 к 6. Поскольку оба этих сигнала являются входными для второй ступени сумматора 6, на его двоичном выходе i4 появляется импульсный сигнал, который поступает на счетный вход триггера 17, являющегося нторым разрядом счетного регистра. Добавление сигнала «а этот триггер, как известно, равносильно нодаче четырех импульсов и, следовательно, результат, записанный в счетчике, соответствует суммарному количеству имиульсов, поступивщих на входы.

Допустим, что на схему поступило три импульса. Это значит, что на один из одноразрядных сумматоров (предположим, на сумматор 5) поступили имоульсы по обоим входам, а на другой (сумматор 6) - по одному входу. Следовательно, сигнал появляется на двоичном выходе 8 сумматора 5 и на единичном выходе 9 сумматора 6. Сигнал с выхода S поступает на один из входов сумматора 6 второй ступени и вызывает появле11ие импульса на единичном выходе 13 этого сумматора. Сигпал с выхода 9 поступает на один из входов сумматора 5 и вызывает появление сигнала на единичном выходе //. Сигнал с выхода 13 поступает на единичный разряд регистра - триггер 16, что равносильно подаче на счетчик двух импульсов.. Сигнал с выхода 11 через элемент 19 задержки поступает на нулевой разряд регистра - триггер 15, что равносильно подаче на счетчик одного импульса. Время задержки элемента 19 выбирается таким, чтобы вместе с задержкой срабатывания триггера 15 не превысить размещающую способность триггера 16.

Допустим, что на схему иоступило только два импульса, при этом возможно, чго импульсы поступят либо на оба входа одного сумматора либо только на один из входов обоих сумматоров.

В первом случае сигнал появляется на двоичном выходе в или 10 соответствующего узла. Следовательно, соответствующий сигнал постуиает на один из входов сумматора 6 второй ступени, появляется на единичном его выходе 13 и через собирательную схе.му 20 поступает на единичный разряд регистра (триг.-ер 16), что равносильно добавлению на регистр двух импульсов.

Во втором случае сигналы появляются на единичных выходах 7 и Р сумматоров 5 и 6, поступают на оба входа сумматора 5 и появляются на двоичном выходе 12 этого сумматора. Через собирательную схему 20 сигнал подается на триггер 16. Если на схему поступает лищь один имнульс, это приводит к появлению

сигнала на единичном выходе одного из с мматоров. Появивщийся сигнал поступает на одигН из входов сумматора 5 другой ступени и появляется на единичном его выходе 11. Через элемент задержки сигнал идет на нулевой разряд регистра (триггер 15).

Таким образом, уже при количестве входов (следовательно, и заноминающих ячеек), равном двум, что потребует лищь одного сумматора, единичный выход которого подключается

к входу нулевого, а двоичный - к входу единичного разряда регистра, частота следования импульсов но обоим входам быть близкой к разрещающей способности счетчика. По мере увеличения числа запоминающих ячеек

эта разнипа в иредельных частотах следования имнульсов возрастает.

Как видно из описанного выще, выходы запоминающих ячеек попарно подключаются ко входам сумматоров, образующих первую ступень. Выходы узлов первой ступени подключены ко входам сумматоров второй ступени и т. д. Если число запоминающих ячеек нечетное, то одна из ячеек подключается непосредственно ко входу соответствующего сумматоt а второй ступени. Выходы узлов последней ступени, подключаемые к двум самым, стар 1;им разрядам регистра, подсоединяются к ним непосредственно, остальные - через,лпнии задержки с таким расчетом, чтобы,не про1130ЩЛО потерь сигналов переноса из младщих разрядов в старщие, появление которых возможно при подаче сигналов в младщие, разряды счетного регистра. Таким образом, нредель-, ная частота следования импульсов по каждому входу достигается новым сочетанием, и. воздействием известных элементов, что позволяет достичь поставленной цели.

Предмет изобретения

Многовходовой счетчик импульсов, содержащий счетный регистр на триггерах и запоминающие ячейки с параллельным выводом информации, отличающийся тем, что, с целью повыщения предельной частоты следования

импульсов по каждому входу, он содержит одноразрядные двоичные сумматоры, разделенные на ступени, причем выходы сумматоров низщей ступени подключены ко входам сумматоров высщей ступени, выходы сумматоров последней ступени связаны со счетнь ми входами триггеров счетного регистра, а входы сумматоров младщей ступени соединены с вылодами запо.лпшающих ячеек.

Опрос М

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| УСТРОЙСТВО для УСРЕДНЕНИЯ ВЫЗВАННЫХ ОТКЛИКОВ!,:k.-. | 1973 |

|

SU361461A1 |

| Многоканальное устройство для форми-РОВАНия ВРЕМЕННыХ иНТЕРВАлОВ | 1979 |

|

SU815875A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ОПЕРАТИВНЫХ НАКОПИТЕЛЕЙ | 1972 |

|

SU341087A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| ПАТЕНТНО- ^ft '^ Т[.ХпИЧ!:ГиЛЙ ^^ш.голизидйБИБЛИОТЕКА | 1966 |

|

SU185569A1 |

Даты

1970-01-01—Публикация