Изобретение относится к вычислительной технике и может быть исполь- .эонано в цифровых системах обработки случайных процессов.

Цель изобретения - повышение быстродействия путем сокращения операций обращения к памяти.

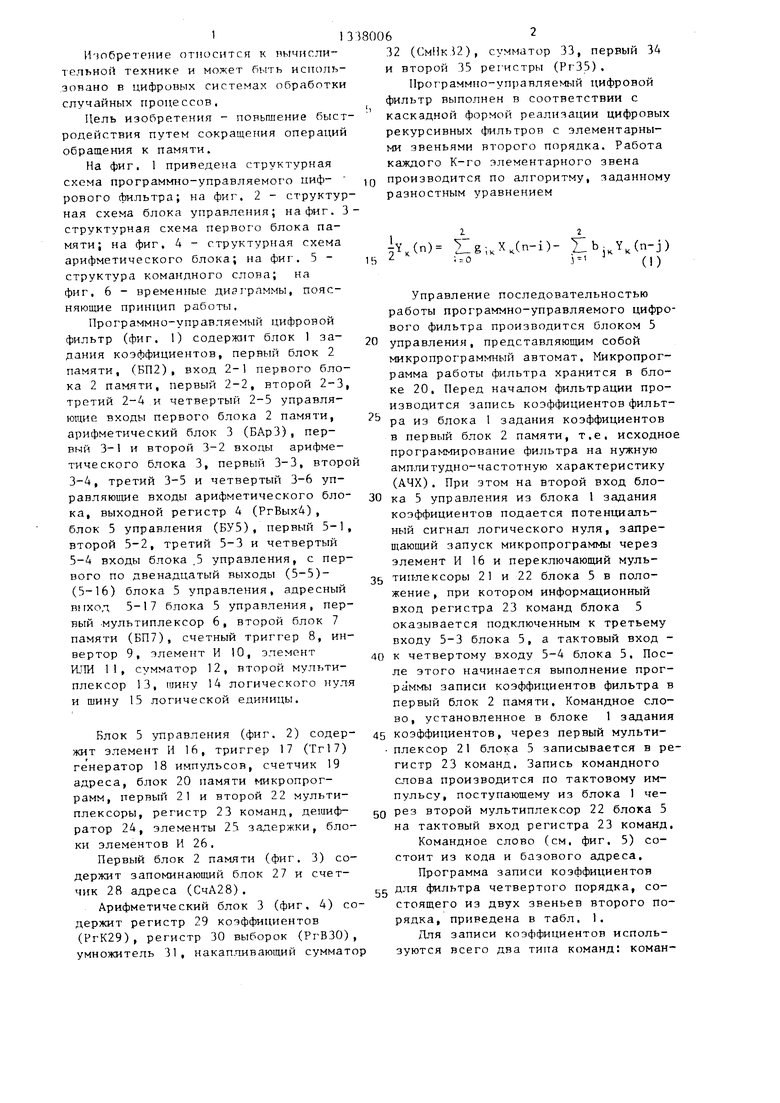

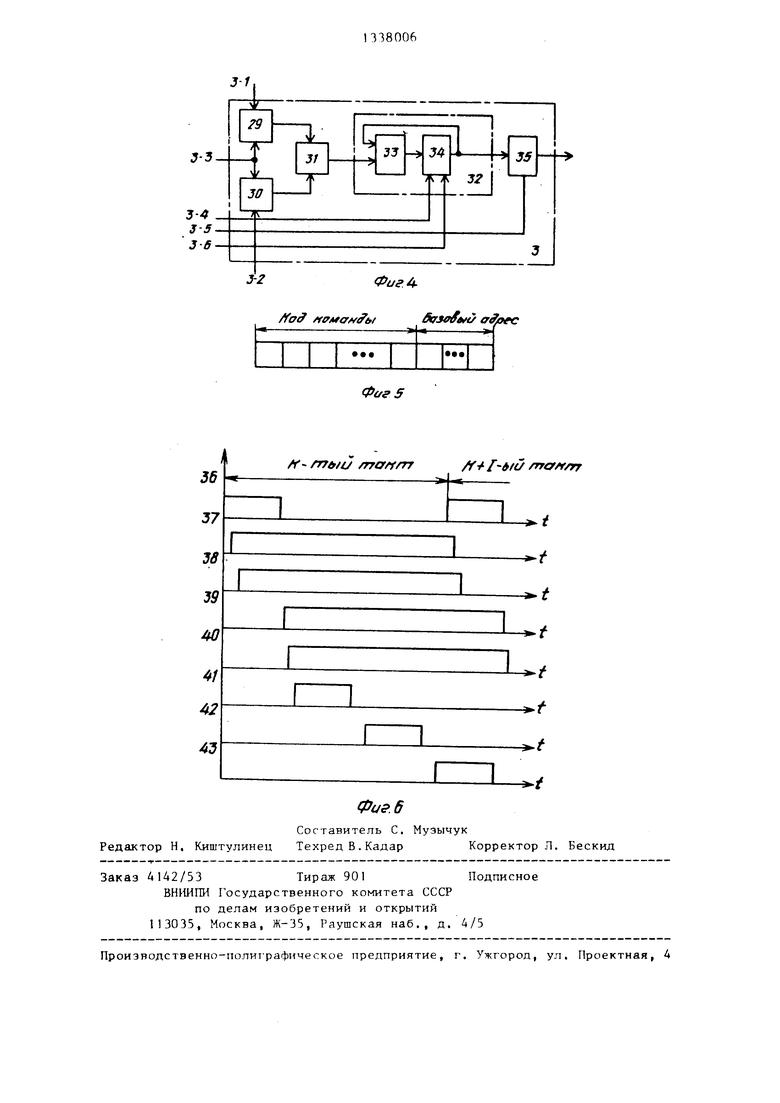

На фиг, 1 приведена структурная схема программно-управляемого циф- рового фильтра; на фиг. 2 - структурная схема блока управления; на фиг. 3 структурная схема первого блока памяти; на фиг, 4 - структурная схема арифметического блока; на фиг. 5 - структура командного слова; на фиг, 6 - временные диаг-раммы, поясняющие принцип работы.

Программно-управляемый цифровой фильтр (фиг, 1) содержит блок 1 задания коэффициентов, первый блок 2 памяти, (БП2), вход 2-1 первого блока 2 памяти, первый 2-2, второй 2-3, третий 2-4 и четвертый 2-5 управляющие входы первого блока 2 памяти, арифметический блок 3 (БАрЗ), первый 3-1 и второй 3-2 входы арифметического блока 3, первый 3-3, второ 3-4, третий 3-5 и четвертый 3-6 управляющие входы арифметического блока, выходной регистр 4 (РгВых4), блок 5 управления (БУ5), первый 5-1, второй 5-2, третий 5-3 и четвертый 5-4 входы блока .5 управления, с первого по двенадцатый выходы (5-5)- (5-16) блока 5 управления, адресный выход 5-17 блока 5 управления, первый -мультиплексор 6, второй блок 7 памяти (БП7), счетный триггер 8, инвертор 9, элемент И 10, элемент ИЛИ 11, сумматор 12, второй мультиплексор 13, шину 14 логического нуля и шину 15 логической единицы.

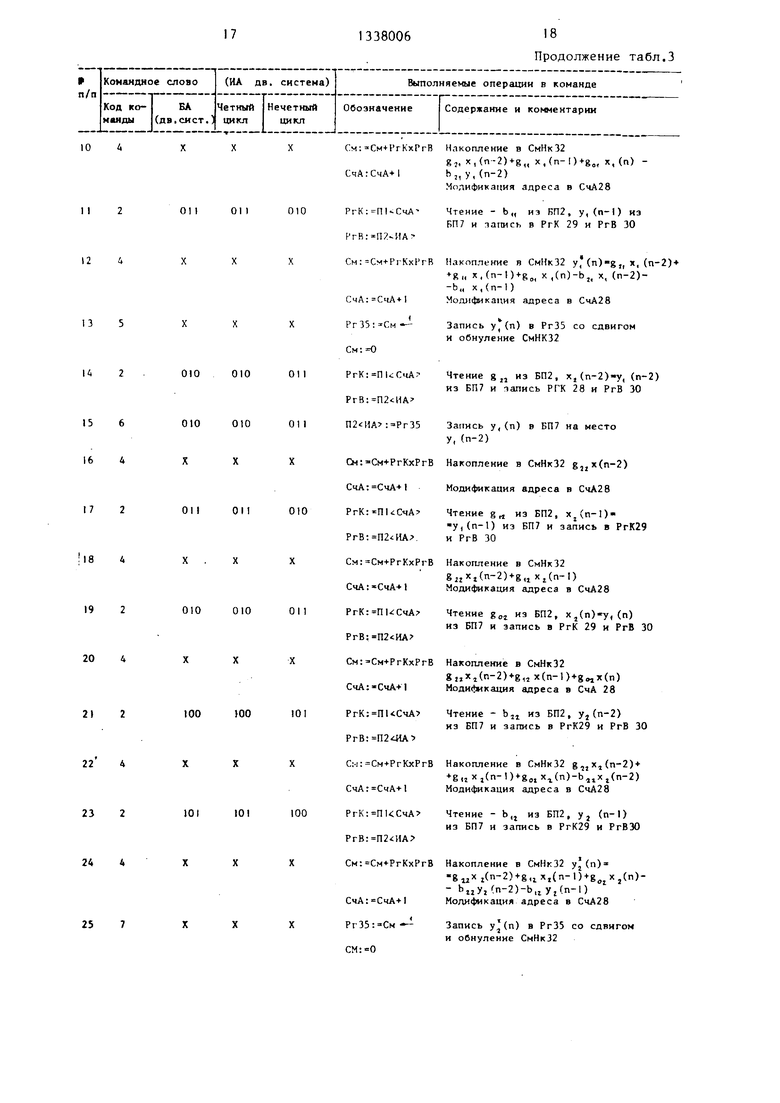

Блок 5 управления (фиг. 2) содержит элемент И 16, триггер 17 (Тг17) генератор 18 импульсов, счетчик 19 адреса, блок 20 памяти микропрограмм, первый 21 и второй 22 мультиплексоры, регистр 23 команд, дешифратор 24, элементы 25 задержки, блоки элементов И 26,

Первый блок 2 памяти (фиг. 3) содержит зaпoминaюш й блок 27 и счетчик 28 адреса (СчА28).

Арифметический блок 3 (фиг, 4) содержит регистр 29 коэффициентов (РгК29), регистр 30 выборок (РгВЗО), умножитель 31, накапливающий суммато

32 (СмНк32), сумматор 33, первый 34 и второй 35 регистры (Рг35),

Программно-управляемый цифровой фильтр выполнен в соответствии с каскадной формой реализации цифровых рекурсивных фильтров с элементарными звеньями второго порядка. Работа каждого К-го элементарного звена производится по алгоритму, заданному разностным уравнением

YJn) g;,X,(n-i)- ГЬ

; 0j 1

JK к

(n-j)

(1)

Управление последовательностью работы программно-управляемого цифрового фильтра производится блоком 5

управления, представляющим собой

микропрограммный автомат. Микропрограмма работы фильтра хранится в блоке 20, Перед началом фильтрации производится запись коэффициентов фильтра из блока 1 задания коэффициентов в первый блок 2 памяти, т,е, исходное программирование фильтра на нужную амплитудно-частотную характеристику (АЧХ), При зтом на второй вход блока 5 управления из блока I задания коэффициентов подается потенциальный сигнал логического нуля, запрещающий запуск микропрограммы через элемент И 16 и переключающий мультип-лексоры 21 и 22 блока 5 в положение , при котором информационный вход регистра 23 команд блока 5 оказывается подключенным к третьему входу 5-3 блока 5, а тактовый вход к четвертому входу 5-4 блока 5, После этого начинается выполнение программы записи коэффициентов фильтра в первый блок 2 памяти. Командное слово, установленное в блоке 1 задания

коэффициентов, через первый мульти- плексор 21 блока 5 записывается в регистр 23 команд. Запись командного слова производится по тактовому импульсу, поступающему из блока 1 через второй мультиплексор 22 блока 5 на тактовый вход регистра 23 команд.

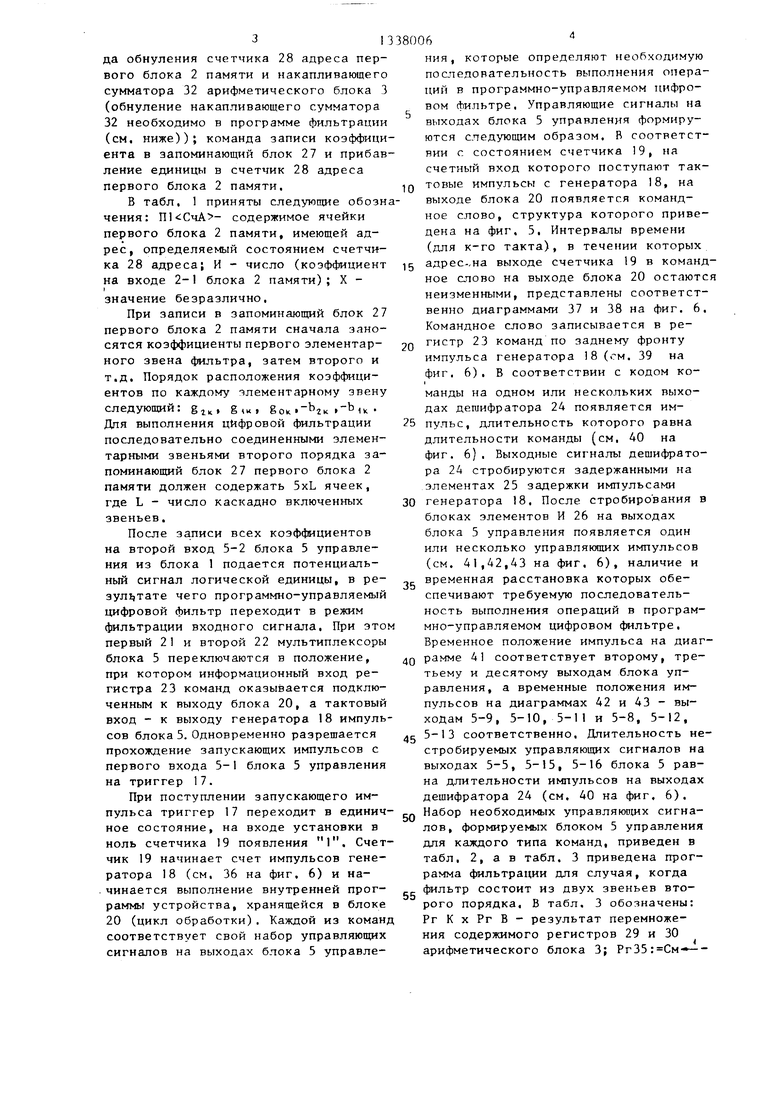

Командное слово (см, фиг, 5) состоит из кода и базового адреса. Программа записи коэффициентов

для фильтра четвертого порядка, состоящего из двух звеньев второго порядка, приведена в табл, 1.

Для записи коэффициентов используются всего два типа команд: коман31

да обнуления счетчика 28 адреса первого блока 2 памяти и накапливающего сумматора 32 арифметического блока 3 (обнуление накапливающего сумматора 32 необходимо в программе фильтрации (см. ниже)); команда записи коэффициента в запоминающий блок 27 и прибавление единицы в счетчик 28 адреса первого блока 2 памяти,

В табл. 1 приняты следующие обознчения: содержимое ячейки первого блока 2 памяти, имеющей адрес, определяемый состоянием счетчика 28 адреса; И - число (коэффициент на входе 2-1 блока 2 памяти); X - значение безразлично.

При записи в запоминающий блок 27 первого блока 2 памяти сначала заносятся коэффициенты первого элементарного звена фильтра, затем второго и т.д. Порядок расположения коэффициентов по каждому элементарному звену следующий: g, g ,,, go.-b ,-Ъ . Для выполнения цифровой фильтрации последовательно соединенными элементарными звеньями второго порядка запоминающий блок 27 первого блока 2 памяти должен содержать 5xL ячеек, где L - число каскадно включенных звеньев.

После записи всех коэффициентов на второй вход 5-2 блока 5 управления из блока 1 подается потенциальный сигнал логической единицы, в ре- зул1}Тате чего программно-управляемый цифровой фильтр переходит в режим фильтрации входного сигнала. При этом первый 21 и второй 22 мультиплексоры блока 5 переключаются в положение, при котором информационный вход регистра 23 команд оказывается подключенным к выходу блока 20, а тактовый вход - к выходу генератора 18 импульсов блока 5.Одновременно разрешается прохождение запускающих импульсов с первого входа 5-1 блока 5 управления на триггер 17.

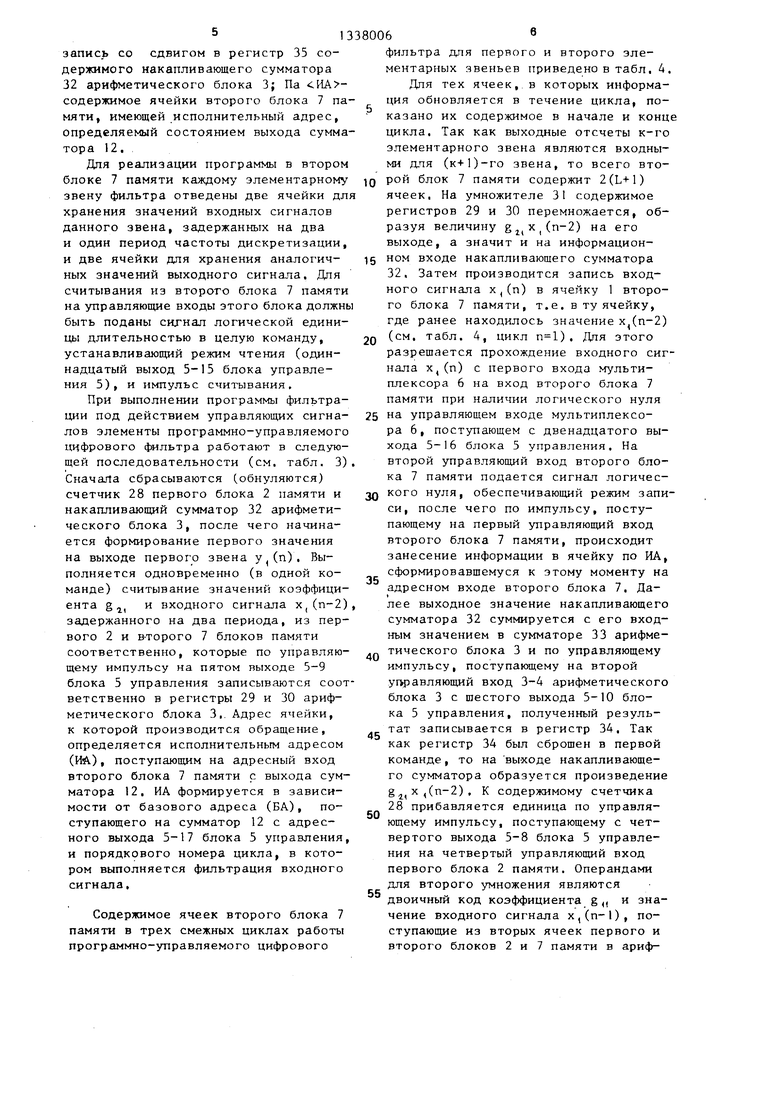

При поступлении запускающего импульса триггер 17 переходит в единичное состояние, на входе установки в ноль счетчика 19 появления 1. Счетчик 19 начинает счет импульсов генератора 18 (см. 36 на фиг. 6) и начинается выполнение внутренней программы устройства, хранящейся в блоке 20 (цикл обработки), Каждой из команд соответствует свой набор управляющих сигналов на выходах блока 5 управле6

НИН, которые определяют необходимую последовательность выполнения операций в программно-управляемом цифровом фильтре, Управляющие сигналы на выходах блока 5 управления формируются следующим образом, В соответствии с состоянием счетчика 19, на счетный вход которого поступают тактовые импульсы с генератора 18, на выходе блока 20 появляется командное слово, структура которого приведена на фиг. 5. Интервалы времени (для к-го такта), в течении которых

адрес-,на выходе счетчика 19 в командное слово на выходе блока 20 остаются неизменными, представлены соответственно диаграммами 37 и 38 на фиг, 6, Командное слово записывается в регистр 23 команд по заднему фронту импульса генератора 18 (см, 39 на фиг, 6). В соответствии с кодом команды на одном или нескольких выходах дешифратора 24 появляется импульс, длительность которого равна длительности команды (см. 40 на фиг, 6), Выходные сигналы дешифратора 24 стробируются задержанными на элементах 25 задержки импульсами

генератора 18, После стробиро вания в блоках элементов И 26 на выходах блока 5 управления появляется один или несколько управляющих импульсов (см, 41,42,43 на фиг. 6), наличие и

временная расстановка которых обеспечивают требуемую последовательность выполнения операций в программно-управляемом цифровом фильтре. Временное положение импульса на диаграмме 41 соответствует второму, третьему и десятому выходам блока управления, а временные положения импульсов на диагра мах 42 и 43 - выходам 5-9, 5-10, 5-11 и 5-8, 5-12,

5-13 соответственно. Длительность не- стробируемых управляющих сигналов на выходах 5-5, 5-15, 5-16 блока 5 равна длительности импульсов на выходах дешифратора 24 (см. 40 на фиг, 6),

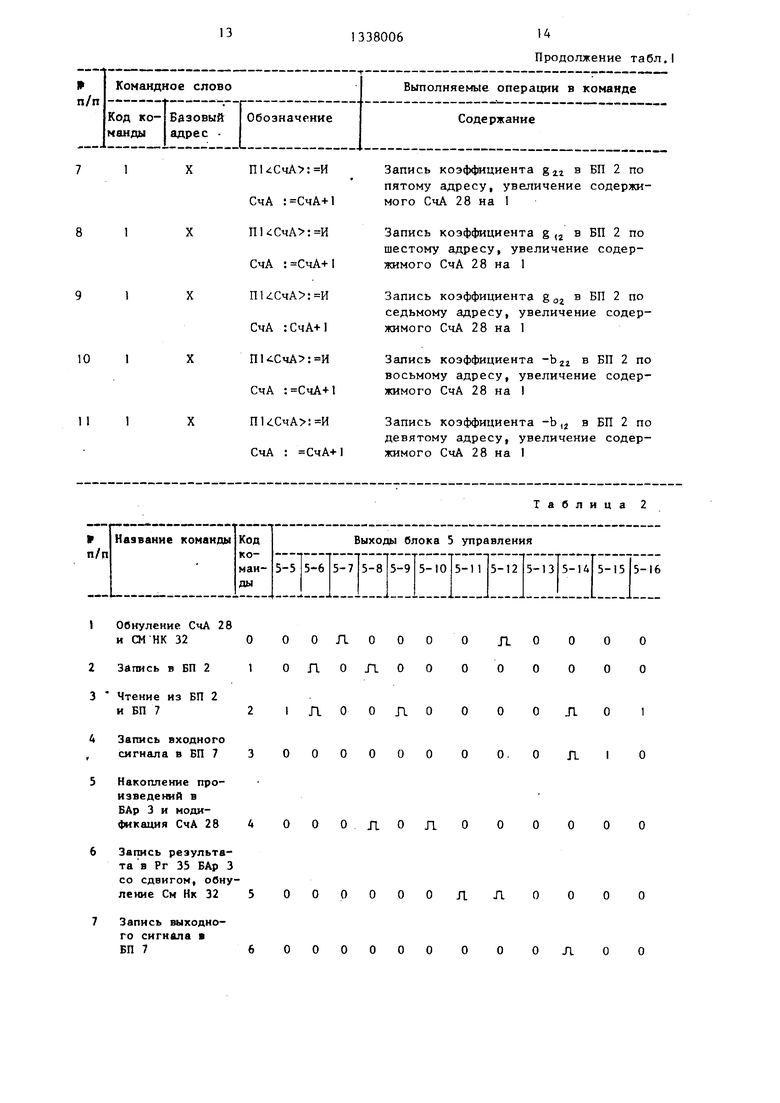

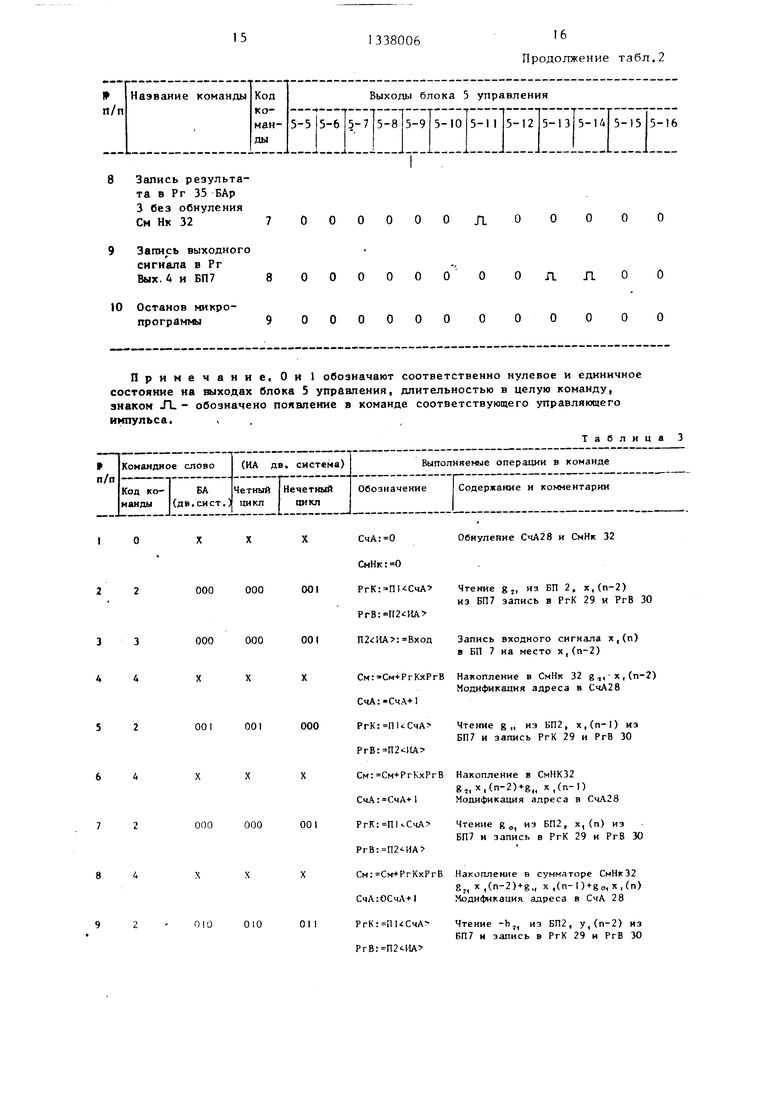

Набор необходимых управляюпшх сигналов, формируемых блоком 5 управления для каждого типа команд, приведен в табл. 2, а в табл. 3 приведена программа фильтрации для случая, когда фильтр состоит из двух звеньев второго порядка. В табл. 3 обозначены: г К X Рг В - результат перемножеия содержимого регистров 29 и 30

арифметического блока 3; Рг35: См-

запись со сдвигом в регистр 35 содержимого накапливающего сумматора 32 арифметического блока 3; Па содержимое ячейки второго блока 7 памяти, имеющей исполнительный адрес, определяемый состоянием выхода сумматора 12.

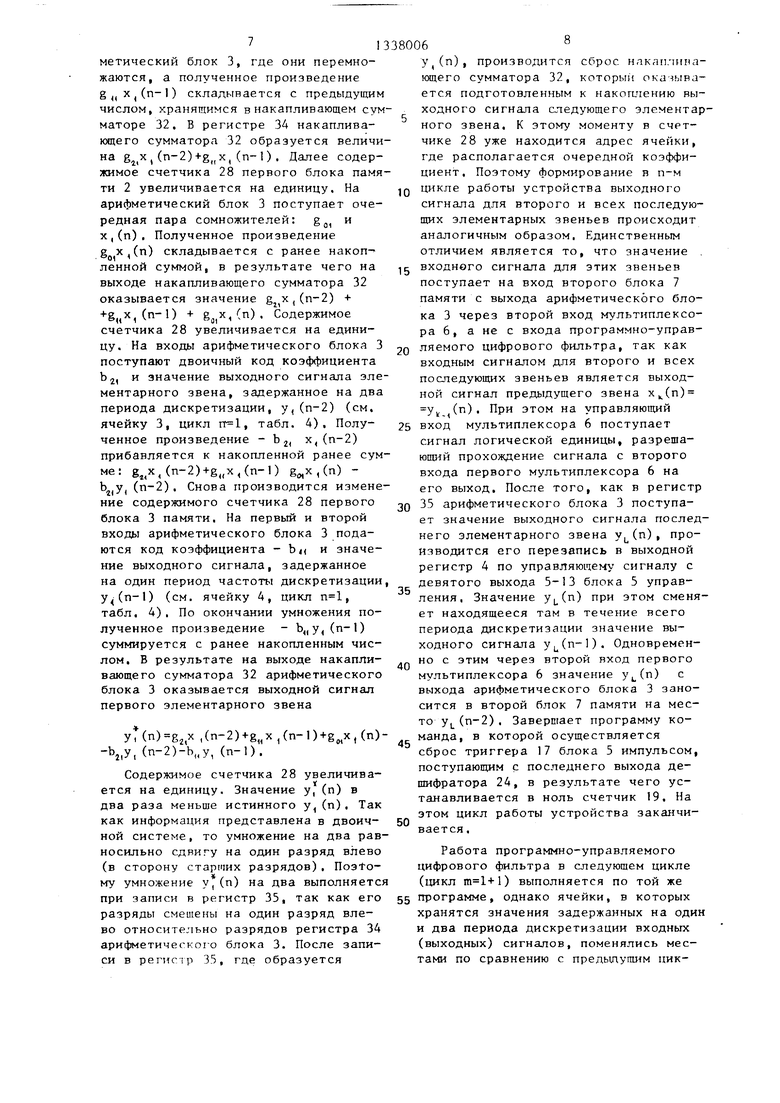

Для реализации программы в втором блоке 7 памяти каждому элементарному звену фильтра отведены две ячейки дл хранения значений входных сигналов данного звена, задержанных на два и один период частоты дискретизации, и две ячейки для хранения аналогичных значений выходного сигнала. Для считывания из второго блока 7 памяти на управляющие входы этого блока должны быть поданы сигнал логической единицы длительностью в целую команду, устанавливающий режим чтения (одиннадцатый выход 5-15 блока управления 5), и импульс считывания.

При выполнении программы фильтрации под действием управляющих сигналов элементы программно-управляемого цифрового фильтра работают в следующей последовательности (см, табл. 3) Сначала сбрасываются (обнуляются) счетчик 28 первого блока 2 памяти и накапливающий сумматор 32 арифметического блока 3, после чего начинается формирование первого значения на выходе первого звена у(п). Выполняется одновременно (в одной команде) считывание значений коэффициента g , и входного сигнала Х|(п-2) задержанного на два периода, из первого 2 и второго 7 блоков памяти соответственно, которые по управляющему импульсу на пятом выходе 5-9 блока 5 управления записываются соответственно в регистры 29 и 30 арифметического блока 3,. Адрес ячейки, к которой производится обращение, определяется исполнительным адресом (ИА), поступающим на адресный вход второго блока 7 памяти с выхода сумматора 12. ИА формируется в зависимости от базового адреса (БА), поступающего на сумматор 12 с адресного выхода 5-17 блока 5 управления, и порядкового номера цикла, в котором выполняется фильтрация входного сигнала.

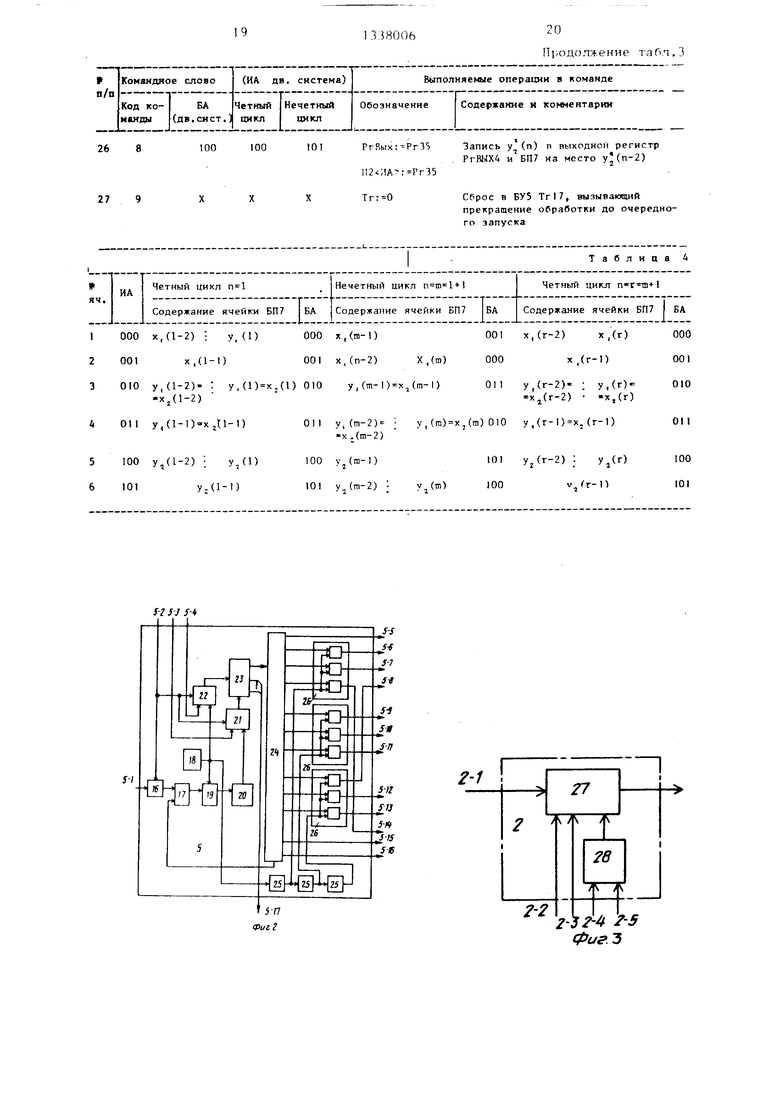

Содержимое ячеек второго блока 7 памяти в трех смежных циклах работы программно-управляемого цифрового

5

0

5

0

5

0

5

0

5

фильтра для первого и второго элементарных звеньев приведено в табл. А, Для тех ячеек, в которых информация обновляется в течение цикла, показано их содержимое в начале и конце цикла. Так как выходные отсчеты к-го элементарного звена являются входными для (к+О-го звена, то всего второй блок 7 памяти содержит 2(L+1) ячеек, На умножителе 31 содержимое регистров 29 и 30 перемножается, образуя величину (n-2) на его выходе, а значит и на информационном входе накапливающего сумматора 32, Затем производится запись входного сигнала х, (п) в ячейку 1 второго блока 7 памяти, т.е, в ту ячейку, где ранее находилось значение х(п-2) (см. табл, 4, цикл ). Дпя этого разрещается прохождение входного сигнала X,(п) с первого входа мультиплексора 6 на вход второго блока 7 памяти при наличии логического нуля на управляющем входе мультиплексора 6, поступающем с двенадцатого выхода 5-16 блока 5 управления. На второй управляющий вход второго блока 7 памяти подается сигнал логического нуля, обеспечивающий режим записи, после чего по импульсу, поступающему на первый управляющий вход второго блока 7 памяти, происходит занесение информации в ячейку по ИА, сформировавщемуся к этому моменту на адресном входе второго блока 7. Далее выходное значение накапливающего сумматора 32 суммируется с его входным значением в сумматоре 33 арифметического блока 3 и по управляющему импульсу, поступающему на второй упгравляющий вход 3-4 арифметического блока 3 с шестого выхода 5-10 блока 5 управления, полученный результат записывается в регистр 34. Так как регистр 34 был сброщен в первой команде, то на выходе накапливающего сумматора образуется произведение g .j X ,(п-2) , К содержимому счетчика 28 прибавляется единица по управляющему импульсу, поступающему с четвертого выхода 5-8 блока 5 управления на четвертый управляющий вход первого блока 2 памяти. Операндами для второго умножения являются двоичный код коэффициента g,, и значение входного сигнала х,(п-1), поступающие из вторых ячеек первого и второго блоков 2 и 7 памяти в арифметический блок 3, где они перемножаются, а полученное произведение i (, X J (п-1) складывается с предыдущим числом, хранящимся в накапливающем сумматоре 32, В регистре ЗА накапливающего сумматора 32 образуется величина g,x, (n-2)+g,,x, (п-1) . Далее содержимое счетчика 28 первого блока памяти 2 увеличивается на единицу. На арифметический блок 3 поступает очередная пара сомножителей: g,, и X , (п), Полученное произведение g X , (п) складывается с ранее накоп- ленной суммой, в результате чего на выходе накапливающего сумматора 32 оказывается значение ,(n-2) + +g,jX,(n-l) + ,(n). Содержимое счетчика 28 увеличивается на единицу. На входы арифметического блока 3 поступают двоичный код коэффициента b 2, и значение выходного сигнала элементарного звена, задержанное на два периода дискретизации, у,(п-2) (см. ячейку 3, цикл , табл. 4), Полученное произведение - b 2, х, (п-2) прибавляется к накопленной ранее сумме: , (n-2)+g,,x Дп-1) ,(n) - Ч|У( (п-2). Снова производится изменение содержимого счетчика 28 первого блока 3 памяти. На первый и второй входы арифметического блока 3 подаются код коэффициента - Ь( и значение выходного сигнала, задержанное на один период частоты дискретизации ) (см. ячейку 4, цикл , табл. 4). По окончании умножения полученное произведение - (п-1) суммируется с ранее накопленным числом, В результате на выходе накапливающего сумматора 32 арифметического блока 3 оказывается выходной сигнал первого элементарного звена

У (п)82,х ,(n-2)+g,,x /n-l)-bg,x, (п)- -b,,y,(n-2)-b,y, (п-1).

Содержимое счетчика 28 увеличивается на единицу. Значение у, (п) в два раза меньше истинного у,(п). Так как информация представлена в двоичной системе, то умножение на два равносильно сдвигу на один разряд влево (в сторону старших разрядов), noato- му умножение у,(п) на два выполняется при записи в регистр 35, так как его разряды смешены на один разряд влево относительно разрядов регистра 34 арифметическо1 о блока 3. После записи в регислр 35, где образуется

0

У,(п), производится сброс накапливающего сумматора 32, который оказывается подготовленным к накогигению выходного сигнала следующего элементарного звена. К этому моменту в счетчике 28 уже находится адрес ячейки, где располагается очередной коэффициент. Поэтому формирование в п-м цикле работы устройства выходного сигнала для второго и всех последующих элементарных звеньев происходит аналогичным образом. Единственным отличием является то, что значение . g входного сигнала для этих звеньев поступает на вход второго блока 7 памяти с выхода арифметического блока 3 через второй вход мультиплексора 6, а не с входа программно-управ- 0 ляемого цифрового фильтра, так как входным сигналом для второго и всех последующих звеньев является выходной сигнал предыдущего звена Х|(п) У| (п) . При этом на управляющий 5 вход мультиплексора 6 поступает сигнал логической единицы, разрешающий прохождение сигнала с второго входа первого мультиплексора 6 на его выход. После того, как в регистр 35 арифметического блока 3 поступает значение выходного сигнала последнего элементарного звена у (п) , производится его перезапись в выходной регистр 4 по управляющему сигналу с девятого выхода 5-13 блока 5 управления. Значение Уц(п) при этом сменяет находящееся там в течение всего периода дискретизации значение выходного сигнала yj(n-l). Одновременно с этим через второй вход первого мультиплексора 6 значение у(п) с выхода арифметического блока 3 заносится в второй блок 7 памяти на место у (п-2) . Завершает программу команда, в которой осуществляется сброс триггера 17 блока 5 импульсом, поступающим с последнего выхода дешифратора 24, в результате чего устанавливается в ноль счетчик 19, На этом цикл работы устройства заканчивается.

Работа программно-управляемого цифрового фильтра в следующем цикле (цикл m l-i-l) выполняется по той же 5 программе, однако ячейки, в которых хранятся значения задержанных на один и два периода дискретизации входных (выходных) сигналов, поменялись местами по сравнению с предыдущим цик0

5

0

лом (см, циклы m и 1, табл. 4). В последующем цикле вновь происходит смена смежных четных и нечетных ячеек (см. табл. 4) так, что адресация совпадает с 1-м циклом и т.д. При работе программно-управляемого цифрового фильтра происходит смена информации в ячейках второго блока 7 памяти так, что в четные цик лы работы адреса должны формиройать- ся иначе, чем в нечетные циклы, причем правило смены адресов должно соответствовать табл, 4, чтобы исключить потери времени на перезапись информации.

Формирование исполнительного адреса ИА второго блока 7 памяти, поступающего на его адресный вход с выход сумматора 12, производится с помощью базового адреса БА, подаваемого с адресного выхода 5-17 блока 5 управления, т.е. с адресных разрядов регистра 23 команд (см. фиг. 5).

Дпя получения требуемого ИА в устройстве производится преобразование БА по следующему правилу:

-1, если счетный триггер 8 находится в состоянии 1, а младший разряд БА равен нулю, что соответствует нечетным циклам работы и четным номерам ячеек второго блока 7 памяти; , если счетный триггер 8 находится в состоянии 1 и младший разряд БА равен единице, что соответствует нечетным циклам работы и нечетным номерам ячеек второго блока 7 памяти; , если счетный триггер 8 находится в состоянии О, что соответствует четным циклам работы.

Счетный триггер 8 меняет свое состояние на противоположное по запускающему сигналу на входе запуска, т.е. при переходе с одного цикла работы к следующему. Если счетный тоиг- rffp 8 находится в состоянии 1 (нечетный цикл работы), а младщий разряд БА и, соответственно, вход элемента 9 равны нулю, то выходы элементов И 10 и ИЛИ 11 авны единице. Сигнал с выхода элемента И 10 поступает на вход переноса в младший разряд сумматора 12, на первый вход которого поступает БА, а к второму

через второй мультиплексор 13 под действием управляющего сигнала, рав ного 1 и поступающего на второй вход второго мультиплексора 13 с вы хода элемента ИЛИ 11. В итоге на вы ходе сумматора 12 формируется резул тат cyм иpoвaния, равный БА+1 . Если счетный триггер 8 находится в состо нии 1 и младший разряд БА равен единице, то выходы элементов И 10 и ИЛИ I1 равны нулю. В этом случае на выходе переноса в младщий разряд су матора 12 действует О, а к его вт рому входу подключается щина 15 логической единицы 15, т.е. код 1,1,. ...,1 в то время, как на первом вхо де сумматора 12 по-прежнему БА. Сум мирование БА с содержимым щины 15 логической единицы равносильно вычи танию из БА единицы, так как -1 в дополнительном коде представляется единицами во всех разрядах. В том случае, когда счетный триггер 8 на- 25 ходится в состоянии О (четный цик работы), то независимо от того, чем равен младший разряд БА, на выходе элемента И 10 действует О, а выхо элемента ИЛИ 11 равен 1. При этом на входе переноса в младший ра ряд сумматора 12 действует О, а к второму входу подключается щина 14 логического нуля. Суммирование БА, поступающего на первый вход суммато ра 12 с нулевым кодом при отсутстви переноса на входе, дает на его выходе результат, равный БА.

Таким образом, обеспечивается не обходимый порядок смены адресов сме ных ячеек второго блока 7 памяти в четных и нечетных циклах работы программно-управляемого цифрового фильтра, позволяющий полностью исключить дополнительные операции перезаписи информации.

30

35

40

45

50

Формула изобретени

. Программно-управляемый цифров фильтр, содержащий первый мультипле сор, первый вход которого является входом программно-управляемого цифрового фильтра, блок задания коэффи циентов, первый блок памяти, выход которого соединен с первым входом

ее

этом случае оказывается под- арифметического блока, второй блок

входу в

ключенной щина 14 логического нуля, т.е. код 0,0,0...,О. Подключение щины 14 логического нуля осуществляется

памяти, выходной регистр, вход кото рого объединен с вторым входом муль типлексора, а выход является выходо

5

0

через второй мультиплексор 13 под действием управляющего сигнала, равного 1 и поступающего на второй вход второго мультиплексора 13 с выхода элемента ИЛИ 11. В итоге на выходе сумматора 12 формируется результат cyм иpoвaния, равный БА+1 . Если счетный триггер 8 находится в состоянии 1 и младший разряд БА равен единице, то выходы элементов И 10 и ИЛИ I1 равны нулю. В этом случае на выходе переноса в младщий разряд сумматора 12 действует О, а к его второму входу подключается щина 15 логической единицы 15, т.е. код 1,1,... ...,1 в то время, как на первом входе сумматора 12 по-прежнему БА. Суммирование БА с содержимым щины 15 логической единицы равносильно вычитанию из БА единицы, так как -1 в дополнительном коде представляется единицами во всех разрядах. В том случае, когда счетный триггер 8 на- 5 ходится в состоянии О (четный цикл работы), то независимо от того, чему равен младший разряд БА, на выходе элемента И 10 действует О, а выход элемента ИЛИ 11 равен 1. При этом на входе переноса в младший разряд сумматора 12 действует О, а к второму входу подключается щина 14 логического нуля. Суммирование БА, поступающего на первый вход сумматора 12 с нулевым кодом при отсутствии переноса на входе, дает на его выходе результат, равный БА.

Таким образом, обеспечивается необходимый порядок смены адресов смежных ячеек второго блока 7 памяти в четных и нечетных циклах работы программно-управляемого цифрового фильтра, позволяющий полностью исключить дополнительные операции перезаписи информации.

0

5

0

5

Формула изобретения

. Программно-управляемый цифровой фильтр, содержащий первый мультиплексор, первый вход которого является входом программно-управляемого цифрового фильтра, блок задания коэффициентов, первый блок памяти, выход которого соединен с первым входом

памяти, выходной регистр, вход которого объединен с вторым входом мультиплексора, а выход является выходом

программно-управляемого цифрового фильтра, и блок управления, первый вход которого является входом запуска программно-управляемого цифрового фильтра, причем первый, второй, третий и четвертый выходы блока управления соединены соответствующими управляющими входами первого блока памяти, пятый, шестой, седьмой и восьмой выходы блока управления - соответственно с первым, вторым, третьим и четвертым управляющими входами арифметического блока, девятый выход блока управления - с входом записи выходного регистра, десятый и одиннадцатый выходы блока управления - соответственно с первым и вторым управляющими входами второго блока памяти, а двенадцатый выход блока управления соединен с управляющим входом первого мультиплексора, отличающийся тем, что, с целью повьщ1ения быстродействия путем сокращения количества операций обращения к памяти, введены сумматор, второй мультиплексор, счетный триггер, инвертор и элементы И и ИЛИ, причем второй, третий и четвертый входы

См

ПиСчА : И

Сч А: СчА-И

пиСчА : И

П1 СчА7: И

СчА: СчА+I

СчА: СчА+1

ПиСчА : И

СчА: СчА-И

10

38006

блока управления соединены с соот- ветствуюпшми выходами блока задания коэффициентов, четвертый выход которого соединен с входом первого блока памяти, адресный выход блока управления соединен через сумматор с адресным входом второго блока памяти, вход которого подключен к выходу первого мультиплексора, а выход - к второму входу арифметического блока, выхгд которого соединен с входом выходного регистра, вход счетного триггера подключен к первому входу блока.,управления , инверсный выход счетного триггера соединен через элемент ИЛИ с управляющим входом второго мультиплексора, лервый и второй входы которого подключены к щинам логического нуля и логической единицы соответственно, а выход соединен с вторым входом сумматора, прямой выход счетного триггера соединен через элемент И с объединенныт и вторым 25 входом элемента ИЛИ и входом переноса сумматора, а второй вход элемента И соединен через инвертор с младшим разрядом адресного выхода блока

управления, I

Таблица 1

15

20

Обнуление СчА 28 и СмНк 32

Запись коэффициента g j( в БП 2 по нулевому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента g ,, в БП 2 по первому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента go, в БП 2 по рому адресу, увеличение содержимог СчА 28 на 1

Запись коэффициента -Ь, в БП 2 по третьему адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента -Ь,( в БП 2 по четвертому адресу, увеличение содержимого СчА 28 на 1

13

ПиСчА : И СчА : СчА-И ПиСчА : И СчА : СчА+1 пиСчА : И СчА :СчА-И ПиСчА : И СчА : СчА+1 ПиСчА : И СчА : СчА-И

1Овнуление СчА 28

и СМ НК 32 О

2Запись в БП 2 1

3 Чтение из БП 2

и БП 72

4Запись входного

, сигнала в БП 7 3

5Накопление произведений в БАр 3 и модификация СчА 28 4

6Запись результата в Рг 35 БАр 3 со сдвигом, обнуление См Нк 32 5

7Запись выходного сигнала в

БП 76

ООЛООООЯО ОО

ОПОЛОО ООО ОО

1ЛООЯО ОООЛО

000000 о0.о яI

ооояолооо оо

оооооояло оо

000000 ооОЛо

1338006

14

Продолжение табл.I

Запись коэффициеита в БП 2 по пятому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента g ,2 в БП 2 по шестому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента g в БП 2 по седьмому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента в БП 2 по восьмому адресу, увеличение содержимого СчА 28 на 1

Запись коэффициента -Ь , в БП 2 по девятому адресу, увеличение содержимого СчА 28 на 1

Таблица 2

о о

15

8 Запись результата в Рг 35 БАр 3 без обнуления См Нк 327

ооооооя о о о о о

9 Запись выходного сигнала в Рг Вых.А и БП7 8

0000000 оя л. о о

10 Останов 01кропрсграм «ы9

000000 О О О О О О

Примечание, Ои 1 обозначают соответственно нулевое и единичное состояние на выходах блока 5 упрйвления, длительностью в целую команду, знаком TL - обозначено появление в команде соответствующего управляющего импульса.

Таблиц

000

000

001

000

000

001

001

001

000

000

000

001

010

010

01 I

338006

16 Продолжение табл.2

Обнуление СчА28 и СмНк 32

Чтение g,, из БП 2, х,(п-2)

из БП7 запись в РгК 29 и РгВ 30

Запись входиого сигнала х,(п) в БП 7 на место х,(п-2)

Смг См+РгКхРгВ Накопление в СмНк 32 g,,-x,(n-2)

Модификация адреса в СчА28 СчА:-СчА-М

РгК: ПиСчА

Чтение g,, из БП2, х,(п-1) из БП7 и запись РгК 29 и РгВ 30

Накопление в СмНК32

g,, x,(n-2)+g,, x,(n-I) Модификация адреса в СчА28

Чтение g из БП2, х, (п) из

БП7 и запись в РгК 29 и РгВ 30

См: См+РгКхРгВ Накопление в сумматоре СмНк32

8j, X ,(n-2) + g,, X ,(п-l) + go, X ,(n) СчА:ОСчА+1Модификация адреса в СчА 28

РгК: ПиСчА- (и

Чтение -Ь,, из БП2, у, (п-2) из БП7 и запись в РгК 29 и РгВ 30

17

4

2

4

5

2

6

4

2

4

2

4

2

4

2

4

7

011011010

010010oil

010010oil

onСИ010

010010oil

100ЮО101

101101100

См: См+РгКхРгВ СчАгСчА I

РгК: П1-СчА

РгВ.- ПЙ ИА:См: См+РгКх1 гВ

СчА: СчА+1 Рг35:-См -

РгК: ПиСчА

См: См+РгКхРгВ

СчА: СчА+1

РгКг ПиСчА

.

См: См+РгКхРгВ

СчА:«СчА+1

РгК: ПиСчЛ

См: См+РгКхРгВ

СчА:-СчА+1

РгК: ПиСчА

См: См+РгКхРгВ

СчА: СчА+1

См: См+РгКхРгВ

СчА: СчА+1 Рг35: -См -

1338006

18 Продолжение табл.3

Накопление в СмНк32

g,, x,(n-2)+g,, x,(n-l)+g,, jc, (n) h,,y.(n-2)

Модификация адреса в СчА28

Чтение - Ь„ из ВП2, у, (п-1) из БП7 и яатшсь в РгК 29 и РгВ 30

Накопление в СмНк32 у, (n)g,, х, (п-2) + f,i, 1,(п-1)+е„, X ,(п)-Ь„ X, (п-2)- -Ь„ х,(п-1) Модификация адреса в СчА28

Запись у, (п) в РгЗЗ со сдвигом и обнуление СмНК32

Чтение g ,, из БП2, х, (п-2)-у, (п-2) из БП7 и запись РГК 28 и РгВ 30

Запись у,(п) в БП7 на место У, (п-2)

Накопление в СмНк32 gjjX(n-2) Модификация адреса в СчА28

Чтение g Э БП2, х(п-1),(п-1) из БП7 и запись в РгК29

и РгВ 30

Накопление в СмНк32 gjjXj(n-2)+g,i Xj(n-I) Модификация адреса в СчА28

Чтение g из БП2, х(п)-у, (п) из БП7 и запись в РгК 29 и РгВ 30

Накопление в СмНк32

g j,x.j(n-2)g,, x(n-l) + go,x(n)

Модификация адреса в СчА 28

Чтение - Ь, из БП2, у,(п-2)

из БП7 и запись в РгК29 и РгВ 30

Накопление в СмНк32 g х (п-2) + g4Xj(n-l) + go,x(n)(n-2) Модификация адреса в СчА28

Чтение - b ,j из БП2, у, (п-1) из БП7 и запись в РгК29 и РгВЗО

Накопление в СмНк32 yj(n) gjjX i(n-2)+g,iX,(n-l) j(n)- - Ь„у, (п-2)-Ь,Уг(п-1) Модификация адреса в СчА28

Запись у (п) в Рг35 со сдвигом и обнуление СмНк32

26 8

100

100101РгЯых: Рг35Запись (п) п выходнои регистр

РгВЫХ4 н БП7 на место у(п-2)

27

.(--- ----

000 х,(1-2) ; у, (1) 000 ),(п1-1)001 х,(г-2) х,(г)

001 х,(п-2) Х,(т) 000 х,(г-1)

001

:,(-)

010 у,(1-2)- : у,(1)х,(1) 010 y,(m-l)x,(m-l) Oil y,(r-2)- ; y,(r)- n-2 -x-(r-2) -x,(r)

4 Oil y.d-O-XjU-l)

on y,(m-2)- y,(m)x,(m) 010 у , (r-I) x, (r-1) «x.(ni-2)

s-г}} /-

Сброс в БУ5 Тг17, вызывающий прекращение обработки до очередного запуска

Таблица 4

000 001 010

01 I

12

г-2

-т2-3 г-4 -s

фиг. 5

3-ZФиг 4

/fod /УЛ4/о Л/АглчЛие;

Фаг 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для преобразования изображения | 1990 |

|

SU1770745A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для моделирования конечных автоматов | 1988 |

|

SU1520534A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия путем сокращения количества операций обращения к памяти. Фильтр содержит блок задания 1 коэффициентов, блоки памяти (БП) 2 и 7, арифметический блок 3, выходной регистр 4, блок управления (БУ) 5, мультиплексоры 6 и 13, счетный триггер 8, инвертор 9, эл-тИ 10, зл-т ИЛИ 11 и сумматор 12. Работа (фильтра осуществляется по циклам. При этом обеспечивается необходимый порядок смены адресов смежных ячеек БП 7 в четных и нечетных циклах работы фильтра. Это позволяет полностью исключить дополнительные операции перезаписи информации. Цель достигается введением триггера 8, инвертора 9, эл-та И 10, эл-та ИЛИ 11, сумматора 12 и мультиплексора 13, с помощью которых производится преобразование базового адреса с БУ 5 для получения требуемого исполнительного адреса для БП 7. 6 ил., 4 табл. с (Л Л/ят СА: со 00

| Программно-управляемый цифровой фильтр | 1979 |

|

SU877787A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1985-07-22—Подача