Предлагаемое устройство относится к специализированным вычислительным устройствам, может быть иопользовано в системах синхронного статистического анализа откликов биологических объектов. Известны устройства для усреднения, вызванных откликов биологических объектов, содержащие преобразователь исследуемых сигналов в цифровую форму, суммирующее и запоминающее устройства, устройства управления и вывода. Такие устройства не могут вырабатывать стимулирующие воздействия со стохастическим характером следования, что не позволяет добиться значительного уменьше«ия мощкости фоновой активности из-за адаптации биологических объектов. Предлагаемое устройство отличается тем, что выходная шина одного разряда ячеек запоминающего устройства соединена со входом сумматора по модулю два, управляемого дешифратором состояний адресного регистра запоминающего устройства, и через ключевую схему - со входом ячейки кратковременной памяти, выход которого присоединен ко входу записи упомянутого разряда запоминающего устройства, причем второй вход ключевой схемы присоединен к выходу сумматора по модулю два, а сигнал запуска внешнего источника стимулирующего воздействия образуется на выходе схемы совпадения, на один вход которой подается сигнал разряда запоминающего устройства, а на другой - выходной сигнал дешифратора состояний адресного регистра этого запоминающего устройства. Сигнал запуска .источника стимулирующего воздействия снимается с выхода вспомогательного триггера через схему совпадения, на второй -вход которой подается сигнал индикации нулевого состояния адресного регистра, причем разрещение на прием выходного сигнала разряда запоминающего устройства во вспомогательный триггер поступает с выхода дешифратора состояний адресного регистра. Усреднитель содержит управляющий триггер, устанавл.иваемый в единичное состояние импульсом, поступающи.м на з-апуск внешнего источника стимулирующего воздействия, нулевой выход управляющего триггера присоединен ко входу схемы совпадения, на второй вход которой поступает сигнал с выхода дешифратора двух состояний адресного регистра запоминающего устройства, соответствующего большому номеру адреса запоминающего устройства, а выход схемы совпадения присоединен к ш.нне сброса в ноль этого адресного регистра, причем сигнал индикации нулевого состояния адресного регистра сбрасывает в ноль управляющий триггер.

Единичный выход управляющего триггера присоединен к разрешающему входу суммирующего устройства.

Это позволяет задавать не только равномерный, но и случайный характер следова ния стимулирующих воздействий и ускорить усреднение вызванных откликов.

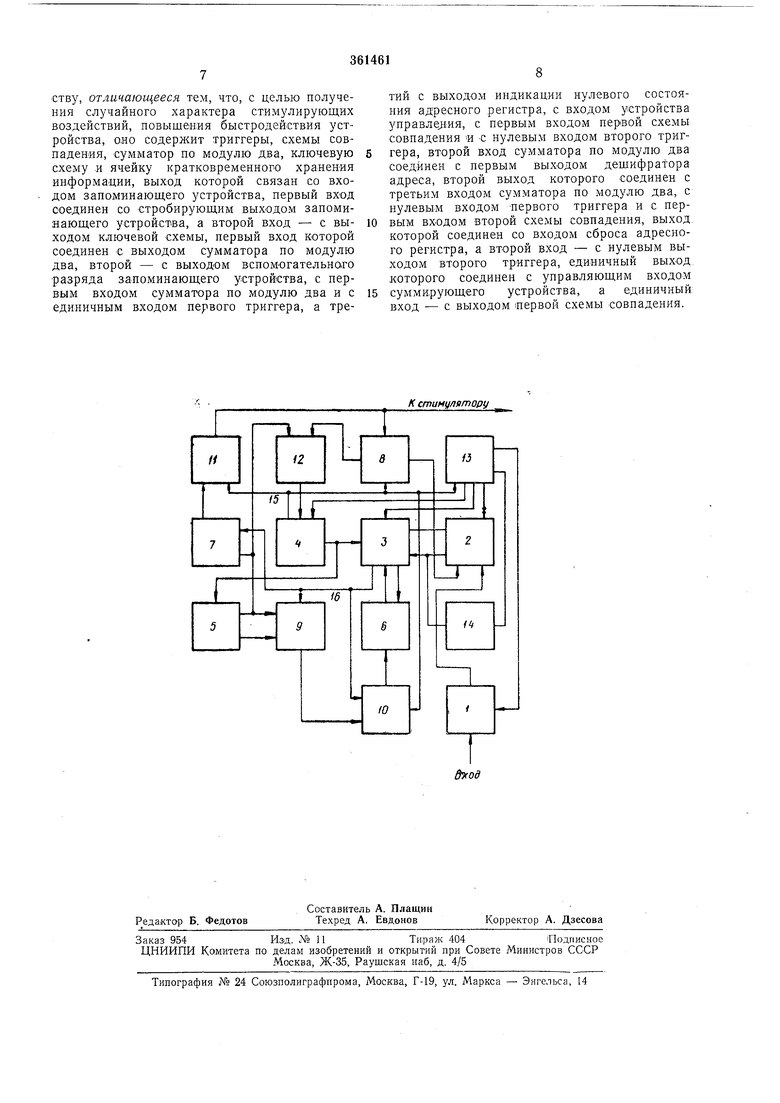

Блок-схема предлагаемого устройства изображена на чертеже.

Усреднитель вызванных откликов состоит из аналого-цифрового преобразователя , сумматора 2, цифрового запоминающего устройства 3, адресного регистра 4 этого запоминающего устройства, дещи.фратора 5 состояний адресного регистра, ячейка 6 кратковременного хранения информации, триггеров 7 и S, одноразрядного сумматора по модулю два 9, ключевой схемы 10 и схем совпадения // н 12. В состав усреднителя вх(дят также устройства упр авления 13 и вывода 14.

Исследуемый процесс поступает на аналого-цифровой преобразователь 1. Выход последнего присоединен ко входу сумматора 2, второй вход которого присоединен к выходу цифрового запоминающего устройства 3. Выходные шины сумматора присоединены ко входным ЩИнам запоминающего устройства. Цифровое запоминающее устройство представляет собой обычное ЗЗпоминающее устройство, например, на ферромагнитных элементах. Разряды каждой его ячейки условно разбивают «а две части. Один разряд (назовем его вспомогательным) каждой ячейки предназначен для выработки псевдослучайной последовательности импульсов. Выход этого разряда присоединен ко входу первого триггера 7, ко входу сумматора по модулю два 9 и ко входу ключевой схемы Ю.

Вход вспомогательного разряда запоминающего устройства присоединен к выходу ячейки 6 кратковременного хранения информации (таким устройством может быть, например, обычный триггер). Остальные разряды (например, 15 /г разрядов) предназНачены для хранения накапливаемых значений вызванных откликов. Эти разряды обмениваются информацией только с суммато-ром 2. Адресный регистр 4, представляющий собой обычный счетчик импульсов, соединен с соответствующими входами запоминающего устройства Лис дешифратором 5, выполненным по обычной схеме. Дешифратор устанавливает соответствие состояния адресного регистра двум выбранным числам (например, трем и двадцати). Один из двух выходов дешифратора, соответствующий меньщему числу, присоединен к стробирующему входу сумматора 9. Другой его выход соединен со стробирующим входом триггера 7, с управляющим ВХОДОМ сумматора 5 и со входом второй схемы совпадений 12. Одноразрядный сумматор 9 представляет собой простейшую схему для выполнения этой логической операции. Он может быть выполнен, например, в виде счетного триггера со схемой совпадений на входе, разрешающей или запрещающей

суммирование по модулю два. Выход сумматора 9 соединен со вторым входом ключевой схемы 10, выход которой присоединен ко входу триггера 6. Ключевая схема представляет собой простую логическую схему, передающую на выход сигналы первого или второго входов в зависимости от управляющего сигнала. Ее управляющий вход присоединен к шине 15 индикации нулевого состояния адресного регистра 4. Эта щина присоединена также ко входу сброса триггера 8, ко входу схемы совпадения /7 и к устройству управления 13. Выход ключевой схемы присоединен ко входу ячейки 6, стробирующий вход которой соединен с управляющим выходом запоминающего устройства 3. Сигнал на стробирующем входе ячейки 6 появляется по окончании цикла записи в любую ячейку устройства 3. Выход триггера 7 подсоединен ко второ.му входу схемы совпадения 11, выход которой соединен с установочным входом триггера 5 и с выходной щиной, подающей сигнал запуска на внешний источник стимулирующего воздействия. Единичный выход триггера 8 присоединен к управляющему входу сумматора Р, а.нулевой - ко второму входу схемы совпадений 12. Выход схемы совпадений 12 присоединен к шине сброса в нуль адресного регистра 4.

Устройство упр-авления 13, соединенное с аналого-дифровым преобразователем 1, сумматором 2, запоминающим устройством 3, адресным регистром 4, устройством вывода 14, управляет работой этих устройств. Устройство вывода, соединенное с сумматором 2, выводит результаты усреднения по окончании анализа исследуемых данных. В простейщем случае устройство вывода представляет собой осциллоскоп.

Устройство управления 13, периодически вызывающее прибавление единицы к содержимому адресного регистра 4, по каждому импульсу увеличения адреса выдает команду запуска аналого-цифрового преобразователя /, команду считывания содержимого данного адреса запоминающего устройства 3, команду суммирования этого содержимого с результатом аналого-цифрового преобразования и команду записи результата суммирования по тому же адресу запоминающего устройства. Полный проход по всем ячейкам (адресам) запоминающего устройства, составляет цикл работы усреднителя. Конец цикла отмечается появлением сигнала на шине 15 индикации нулевого состояния адресного регистра.

Сумматор 2 складывает выборки входного процесса с содержимым ячеек запоминающего устройства только в том случае, если триггер 8 находится в единичном состоянии. В противном случае содержимое ячеек запоминающего устройства не изменяется. Триггер 8 устанавливается в единичное состояние выходным сигналом схемы совпадений //. Одновр-еменно этот сигна т запускает источник стимулирующего воздействия; при этом усреднитель выполняет один цикл накопления. По окончании цикла сигналом индикации нулевого состояния адресного регистра 4 триггер 5 устанавливается в нуль, запрещая складывание входных данных с содержимым ячеек запоминающего устройства 3 и разрещая прохождение сигнала € выхода дещифратора 5 на шину сброса адресного регистра 4 через схему совпадений 12. В остальном работа устройств усреднителя в этом случае не отличается от описанной ранее. Псевдослучайная последовательность импульсов, появляющаяся на выходе схемы совпадений 11, о:бразуется во вспомогательном разряде запоминающего устройства 3 одновременно с выполнением основных операций, описанных выше. За один проход по ячейкам запоминающего устройства выполняется один такт работы генератора псевдослучайной последовательности. Результатом любого такта может оказаться появление на выходе схемы совпадений 11 не более одного импульса запуска источника стимулирующего воздействия.

Устройства, связанные со вспомогательным разрядом запоминающего устройства 3, работают в каждом элементарном цикле следующим образом. При опросе любой яч-ейки запоминающего устройства число, считанное из данной ячейки, остается в числовом регистре, а в ячейку записывается цифра, находящаяся в ячейке 6. По окончании записи в любую ячейку запоминающего устройства

СТрОбируЮЩИЙ сигнал из этого устройства

устанавливает триггер В состояние, определяемое выходным сигналом ключевой схемы }Q. Состояние ячейки 6 при этом определяется содержимым вспомогательного разряда предыдущей по номеру ячейки устройства 3, кроме того элементарного цикла, в котором на втором выходе деш-ифратора адреса 5 появляется сигнал. Тогда ячейка 6 устанавливается через ключевую схему 10 в состояние, соответствующее выходному сигналу сумматора по модулю два 9. Выходной сигнал сумматора 9 зависит от содержимого ячеек, номера которых соответствуют появлению сигналов на первом и втором выходах дешифратора 5. При появлении сигнала на строб-ирующем входе сумматора 9 последний принимает первое слагаемое из устройства 3. Появление сигнала на втором выходе дешифратора 5, т. е. на управляющем входе сумматора 9, вызывает проведение операции суммирования по модулю 12 на сброс адресного регистра 4. В это.м случае усреднитель выполняет укороченный цикл работы, начиная сразу же новый цикл; iB укороченном цикле входная информация не накапливается. Когда из впомогательного разряда последней ячейки укороченного цикла по шине 16 вспомогательного р азряда запоминающего устройства 3 считывается единица, она устанавливает триггер 7 Б единичное состояние. По

сигналу индика.циИ нуля адресного регистра 4 эта единица из триггера 7 поступает через схему совпадений // на запуск источника стимулирующего воздействия и на установку триггера 9 в единичное состояние. Таким образом в сумматоре 2 накапливается очередной отклик. До окончания полного цикла триггер 8 блокирует схему совпадений 12, препятствуя сбросу адресного регистра 4 в середине цикла. Сигнал индикации нулевого состояния адресного регистра, появляющийся в конце цикла на щине 15, сбрасывает в ноль трнггер 8 и устанавливает ячейку 6 через ключевую схему 10 в состояние, соответствующее выходному сигналу сумматора по модулю два 9. В начале нового цикла это состояние ячейки 6 записывается в первую по номеру ячейку запоминающего устройства 3. Таким образом, в дополнительный разряд первой ячейки устройства 3 всегда записывается выходной сигнал сумматора, а в остальных ячейках происходит перезапись в каждом цикле содержимого ячеек в следующие по номеру ячейки. Это обеспечивает рециркуляцию информации в данном разряде ячеек устройства 3 и выработку псевдослучайной последовательности запускающих стимуляторов импульсов. Как было описано, генерирование последовательности не прекращается и в тех циклах, в которых накапливаются отклнки, поэтому вероятностный закон следования импульсов запуска не нарушается и ни один нмпульс не пропадает. Для обеспечения правильной работы усреднителя в исходном состоянии сумматор 2, адресный регистр 4, триггеры 7, S и сумматор по модулю два 9 устанавливаются в нулевое состояние, содержимое всех ячеек запо.минающего устройства 3 равно нулю, а ячейка 6 устанавливается в единицу. После пуска в работу по выполнении нужного числа накоплений откликов, количество которых может быть подсчитано по количеству импульсов запуска источника стимулирующего воздействия, в ячейках запоминающего устройства накапливается результирующая кривая усредненного отклика исследуемого объекта на раздражитель. Результат выводится из ячеек устройства 3 на устройство 14 по командам из устройства управления 13.

Предмет изо,бретення

Устройство для усреднения вызванных откликов, содержаул,ее аналого-цифровой преобразователь, суммирующее устройство, запоминающее устройство, соединенное с адресным регистром и дешифратором адреса, устройство вывода и устройство управления, соединенное с адресным регистролг, запоминающим устройством, суммирующим устройством, устройством вывода и аналого-цифровым преобразователем, соединенным с суммирующим устройством, подключенным к устройству вывода и запоминающему устройству, отличающееся тем, что, с целью получения случайного характера стимулирующих воздействий, повышения быстродействия устройства, оно содержит триггеры, схемы совпадения, сумматор по модулю два, ключевую схему .и ячейку кратковременного хранения информации, выход которой связан со входом запоминающего устройства, первый вход соединен со стробирующим выходом запоминающего устройства, а второй вход - с выходом ключевой схемы, первый вход которой соединен с выходом сумматора по модулю два, второй - с выходом вспомогательного разряда запоминающего устройства, с первым входом сумматора по модулю два и с единичным входом первого триггера, а третий с выходом индикации нулевого состояния адресного регистра, с входом устройства yпpaвлeJ ия, с первым входом перовой схемы совпадения и -с нулевым входом второго триггера, второй вход сумматора по модулю два соединен с первым выходом дешифратора адреса, второй выход которого соединен с третьим входом сумматора по модулю два, с нулевым входом -первого триггера и с первым входом второй схемы совпадения, выход, которой соединен со входом сброса адресного регистра, а второй вход - с нулевым выходом второго триггера, единичный выход которого соединен с управляющим входом

суммирующего устройства, а единичный: вход - с выходом первой схемы совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| ВСЕСОЮЗНАЯ I | 1973 |

|

SU370601A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1361624A2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ Л1ЕЖДУ АБОНЕНТАМИ И ЦВМ | 1973 |

|

SU368607A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

к стищ1пяторд

Авторы

Даты

1973-01-01—Публикация