лей, второй дешифратор, второй -блок контроля, контрольные регистры, группа регистров адреса, третья, четвертая, -пятая и шестая группы элементов И, второй и третий элементы И, третья четвертая, пятая и шестая группы элементов ИЛИ и элемент НЕ, причем нулевые входы первого контрольного регистра соединены с выходами первого блока контроля, единичные входы первого и второго контрольных регистров подключены к выходу генератора одиноч ных импульсов и установочному входу второго счетчика импульсов, счетный вход которого соединен с выходом переноса первого счетчика импульсов, а выход - с входом второго дешифратора первые входы и выходы одноразрядных накопителей второй группы подключены соответственно к шестому выходу блока управления и к одним из входов второго блока контроля, другие входы которого соединены соответственно с . третьим и с седьмым выходами блока управления, восьмой выход которого подключен к нулевым входам регистров адреса группы, единичные выходы которых соединены с первыми входами элементов И третьей и четвертой групп, а одни из единичных входов - соответственно с выходами элементов ИЛИ третьей, и четвертой групп, входы которых подключены к выходам одних из элементов И пятой группы, другие единичные входы регистров адреса группы соединены с выходами других элементов И пятой группы, а нулевые выходы - с входами элементов И шестой группы, первые входы элементов И пятой группы подключены к единичным выходам контрольных регистров, вторые и третьи входы - соответственно к выходам первого и второго дешифраторов.

четвертые входы элементов И пятой группы соединены с выходами элементов И шестой группы, вторые входы элементов ИЛИ третьей и четвертой групп подключены соответственно к девятому и к десятому выходам блока управления, выходы элементов ИЛИ первой группы соединены с вторыми входами элементов И третьей группы выходы одних из которых подключены к вторым входам одноразрядных накопителей -первой группы, выходы которых соединены с вторыми входами одних из элементов И четвертой группы, выходы других элементов И третьей группы подключены к входам элементов. ИЛИ пятой группы, выходы которых соединены, с вторыми входами одноразрядных накопителей второй группы, выходы которых подключены к вторым входам других элементов И четвертой группы, выходы элементов И четвертой группы соединены с входами элементов ИЛИ второй группы, выходы второго блока контроля подключены к одним из входов элементов И шестой труппы, другие входы которых соединены с единичными выходами регистров адреса группы, а выходы - с нулевыми входами второго контрольного регистра, первый и второй входы второго элемента И подключень соответственно к одному из выходов первого дешифратора и к одному из выходов второго дешифратора, выход второго элемента соединен с единичным входом первого триггера, вторым входом элемента ИЛИ и первым входом третьего элемента И, выход которого подключен к единичному входу третьего триггера, а второй вход - к выходу элемента НЕ, вход которого соединен с выходом одного из элементов И шестой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU903973A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство | 1979 |

|

SU842955A1 |

| Запоминающее устройство | 1980 |

|

SU858095A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в качествеоперативного запоминающего устройства (ОЗУ) в автоматизированных системах управления, доступ ремонтного персонала к которым: затруднен или практически невозможен .

Известно оперативное запоминающее устройство с самоконтролем, которое содержит накопитель, выходы которого подключены к одним входам элементов ИЛИ, а входы - к адресным формирователям токов выборки,.соединенным с регистром адреса, выход которого под; ключен к счетным входам счетчика. блок-контроля, первый вход которого соединен с выходом регистра числа, блок формирования контрольного кода выходы которого подключены к другим входам элементов ИЛИ и входам регист ра числа, дешифратор, вход которого соединен с выходом счетчика, элементы И, соединенные с регистром адреса, элементами ИЛИ и регистром чис ла, блок управления и блоки Индикации iQ Недостатком этого устройства является низкая точность контроля. Наиболее близким техническим решением к изобретению является оперативное запоминающее устройство с самоконтролем, содержащее накопител выходы которого подключены к одним входам элементов И|1И, а входы - к ад ресным формирователям токов выборки соединенным с регистром адреса, выход которого подключен к счетному входу счетчика, блок контроля, первый вход которого соединен с выходо регистра числаi блок формирования контрольного кода, .выходы которого подключены к другим входам элементов ИЛИ и входам регистра числа, де шифратор, вход которого соединен с выходом счетчика, элементы И, соединенные с регистром адреса, элементами ИЛИ и регистром числа, блок управления, блоки индикации, генераторы одиночных импульсов, триггеры, дополнительные элементы И и ИЛИ блок местного управления и дополнительный блок контроля, выход первого генератора одиночных импульсов n ключен ко входам регистра адреса и счетчика, одним из входов первого, второго и третьего триггеров, одному из выходов дополнительного элемента ИЛИ, другой вход которого сое нен с выходом второго генератора одиночных импульсов, а выход подключен к одному из входов четвертого триггера, другие входы триггеров соединены соответственно с выходом, дополнительного элемента И, первым входом дешифратора и первым входом дополнительного элемента И, выходом блока контроля, выходы триггеров по ключены соответственно ко входам бл ков индикации, первым входбм блока местного управления, блока управления, дополнительного блока контроля и блока формирования контрольного кода, вторым входам блока управления, блока формирования контрольног кода и дополнительного элемента И и одним из входов элементов И, второй и третий входы блока местного управления соединены соответственно с выходом блока управления и вторим выходом дешифратора, а выход блекла местного управления подключен к второму входу блока контроля и третьим входам блока управления и блока Формирования контрольного кода, третий вход дополнительного блока контроля соединен с одним из входов регистра адреса 2 , Однако для известного устройства характерна невозможность автоматического устранения неисправностей, обнаруженных в результате автономного контроля, что снижает надежность . устройства. Цель изобретения - повышение надежности устройства. . Поставленная цель достигается тем, что в оперативное запоминающее устройство с самоконтролем, содержащеё генератор тактовых импульсов, i триггеры, регистр адреса, первый счетчик импульсов, группы элементов И, блок управления, первый блок контроля, группы элементов ИЛИ, первую группу одноразрядных накопителей, первый дешифратор, элементы индикации, первый элемент И , элемент ИЛИ и генератор одиночных импульсов, выход которого соединен с нулевыми входами первого триггера и регистра адреса, установочным входом первого счетчика импульсов, первым входом блока управления и первым входом элемента ИЛИ, выход которого подключен к нулевому входу второго триггера, причем выход генератора тактовых импульсов соединен с вторым входом блока управления и первым входом первого элемента Н, второй вход которого подключен к единичному выходу втором триггера, а выход - к счетному входу первого счетчика импульсов, выход которого соединен с входом первого дешифратора, нулевой выход первого триггера подключен к третьему входу блока управления, единичный выход первого триггера соединен с первыми входами элементов И первой и второй групп, четвёртым входом блока управления и входом первого элемента ин дикации, выходы элементов И первой группы подключены к единичным аходам регистра адреса, счетный вход которого соединен с первым выходом блока

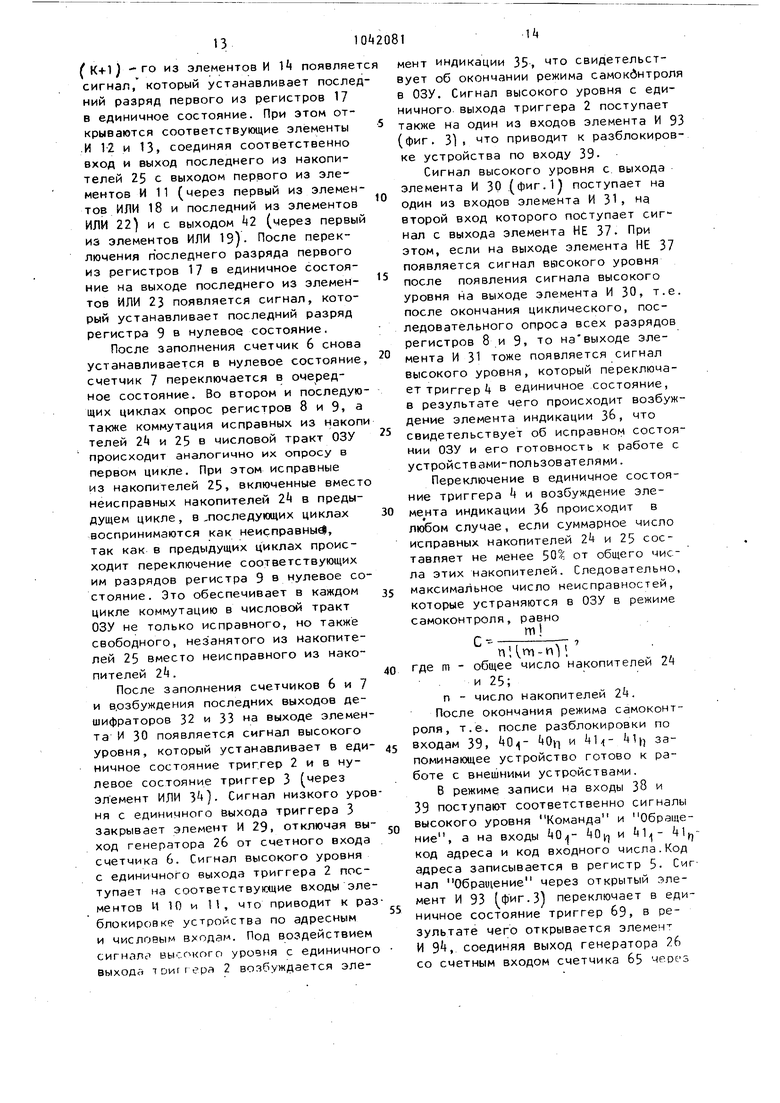

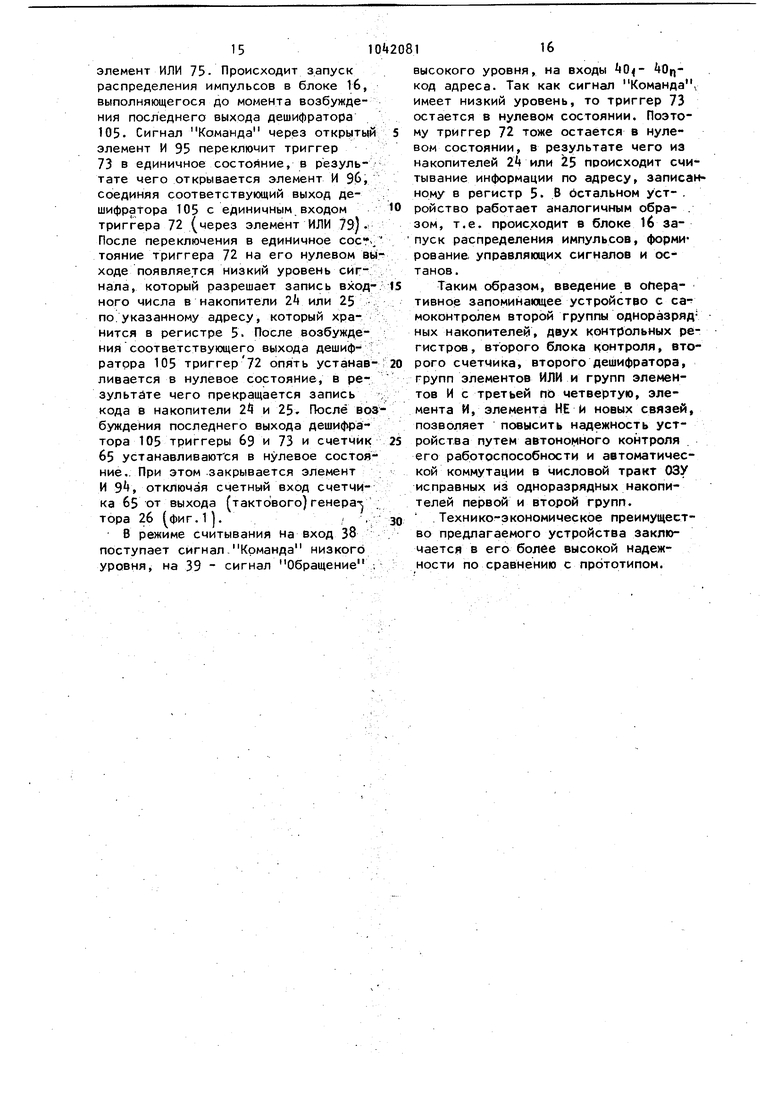

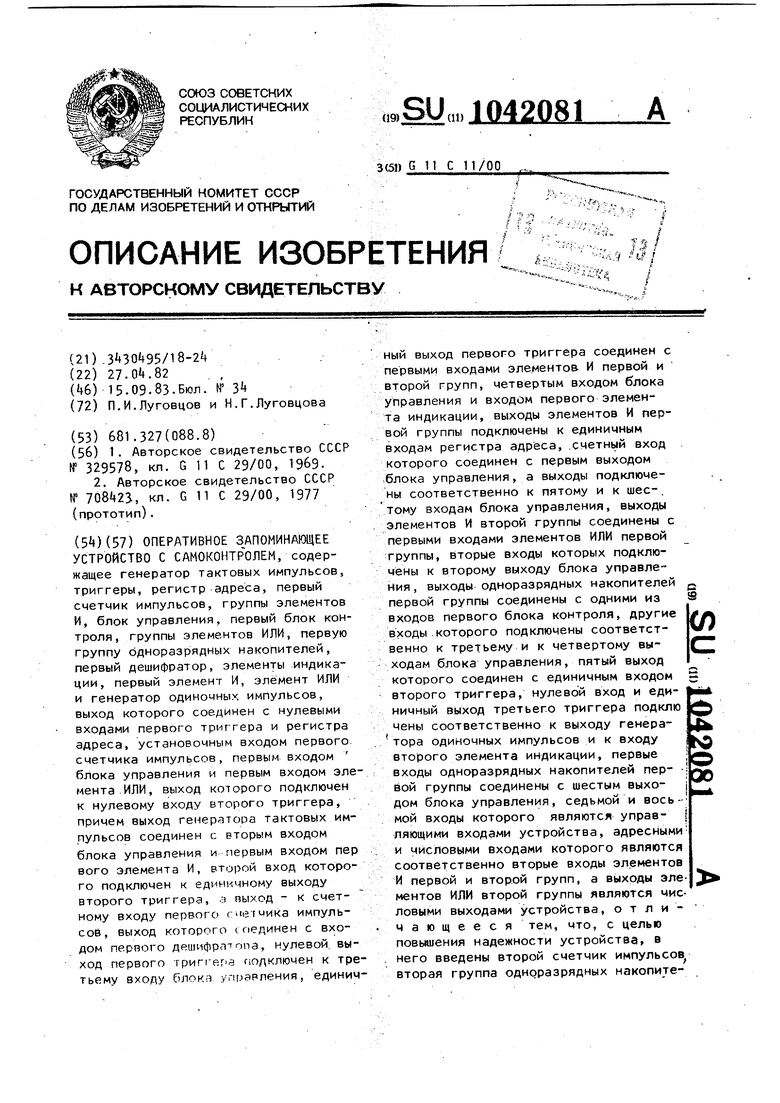

управления, a выходы подключены соответственно к пятому и к шестому входам блока управления, выходы элементов И второй группы соединены с первыми входами элементов ИЛИ первой группы,, вторые входы которых подключены к второму выходу блока управления , выходы одноразрязных накопителей первой группы соединены с одними из входов первого блока контроля, другие входы которого подключены соответственно к третьему и четвертомувыходам блока управления, пятый выход которого соединен с единичным входом второго триггера, нулевой вход и единичный выход третьего триггера подключены соответственно к выходу генератора одиночных импульсов и к входу Btoporo элемента индикации, первые входы одноразрядных накопителей первой группы соединены с шестым выходом блока управления, седьмой и восьмой входы которого являются управляющими входами устройства, адресными и числовыми входами которого являются соответственно вторые входы э 1ементов И лервой и второй групп, а выходы элементов ИЛИ второй группы являются числовыми выходами устройства, введены второй счетчик импульсов, втойая группа одноразрядных накопителей, второй дешифратор, второй блок контроля, контрольные регистры, группа регистров адреса, третья, четвертая пяtaя и шестая группы элементов И, второй и третий элементы И, третья четвертая, пятая и шестая группы элементов ИЛИ и элемент НЕ, причем нулевые входы первого контрольного регистра соединены с выходами первого блока контроля, единичные входы первого и второго контрольных регистров подключены к выходу генератора одиночных импульсов и установочному входу второго счетчика импульсов, счетный вход которого соединен с выходом переноса первого счетчика импульсов, а выход - с входом второго дешифратора,первые входы и выходы одноразрядных накопителей второй группы подключены соответственно к шестому выходу блока управления и к одним из входов второго блока контроля, другие входы которого соединены соответственно с третьим и с седьмым выходами блока управления, восьмой выход которого подключен к нулевым входам регистров адреса группы, единичные выходы которых соединены с первыми входами элементов И Третьей и четвертой групп,-а одни из единичных входов - соответственно с выходами элементов ИЛИ третьей и четвертой групп, входы которых подключены к выходам одних из элементов И пятой группы, другие единичные входы регистров адреса группы соединены с выходами других элементов И пятой группы, а нулевые выходы - с входами элементов И шестой группы, первые входы элементов И пятой группы подключены к единич5 ным выходам контрольных регистров, вторые и третьи входы - соответственно к выходам первого и второго дешифраторов, четвертые входы элементов И пятой группы соединены с выходами элементов И шестой группы, вторые входы элементов ИЛИ третьей и четвертой групп подключены соответственно к девятому и к десятому выходам блока управления, выходы элемен5 |тов ИЛИ, первой группы соединены с Вторыми входами элементов И третьей группы, выходы одних из которых подключены к вторым входам одноразрядных накопителей первой группь, выходы которых соединены с вторыми входами одних из элементов И четвертой Группы, выходы других элементов И третьей группы подключены к входам элементов ИЛИ пятой группы, выходы которых соединены с вторыми входами одноразрядных накопителей второй группы, выходы которых подключены к вторым входам других элементов И четвертой группы, выходы элементов И четвертой группы соединены с входами элементов ИЛИ второй группы, выходы второго блока контроля подключены к одним из входов элементов И шестой группы, другие входы которых соединены с единичными выходами регистров адреса группы, а выходы с нулевыми входами второго контрольного регистра, первый и второй входы второго элемента И подключены соответственно к одному из выходов первого дешифратора и к одному из выходов второго дешифратора, выход второго элемента И соединен с единичным входом первого триггера, вторым входом элемента ИЛИ и первым входом 5 третьего элемента И, выход которого подключен к единичному входу третье-го триггера, а второй вход - к выходу элемента НЕ, вход которого гоединен с выходом одного из элементов И шестой группы. На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема второго блока контроля; на фиг. 3 функциональная схема блока управления . Устройство содержит (фиг.1 генератор 1 одиночных импульсов, первый 2, второй 3 и третий t триггеры, регистр 5 адреса, первый 6 и второй 7 счетчики импульсов, первый 8 и второй 9 контрольные регистры, пер вую 10, вторую 11, третью 12, четвертую 13, пятую И и шестую 15 rpyq пы элементов И, блок 16 управления., группу регистров адреса 17, первую 18, вторую 19, трет|)Ю 20, четвертую 21, пятую 22 и шестую 23 группы элементов ИЛИ, первую 2k и вторую 25 группы одноразрядных накопителей, генератор 26 тактовых импульсов, пер вый 27 и второй 28 блоки контроля. первый 29, второй 30 и третий 31 эле менты И, первый 32 и второй 33 дешифраторы, элемент ИЛИ 3, первый 35 и второй 36 элементы индикации и. элемент НЕ 37. Устройство также содержит первый 38 и второй 39 управляющие входы, адресные влоды и числовые входы tlr и выходы k2 устройства (где п 1 - число одноразрядных накопителей первой группы).. Второй блок контроля содержит (фиг.2) первую 3 и вторую kk группы элементов НЕ, элемент НЕ 5, группы элементов И , группу элементов ИЛИ . Устройство содержит также (фиг-. 1) первый вход 50 и выходы с первого . по десятый 51-60 блока управления, единичный выход 61 первого триггере, выход 62 одного из элементов И шеетой группы, выходы 63 и однораз рядных накопителей второй группы. Блок управления содержит (фиг.З) счетчики б5-б7 импульсов, триггеры 68-73, элементы ИЛИ , формирователи сигналов, элементы И 88 Qk и дешифраторы 105-112. Устройство содержит также выход 113 переноса регистра адреса (фиг.1 и 3). Устройство работает следующим образом.; Подготовка устройства к работе , выполняется в два этапа. На первом этапе производится автономный кон1l8 троль работоспособности ОЗУ, для чего отводится отрезок времени, в течение которого в ОЗУ формируется контрольный тест, производится его запись, считывание, проверка правипьности считанной информации и запись результатов этой проверки в спе циальные регистры. В основу проверки работоспособности может быть положен шахматный код. На втором этапе производится автоматическая коммутация исправных разрядов накопителей 2 и 25 (фиг.1) в числовой тракт ОЗУ. Для автоматической коммутации отводится отрезок времени, в течение которого производится последовательное включение исправных разрядов накопителей и 25 в числовой тракт ОЗУ и формирование сигнала исправности ОЗУ в конце самоконтроля. Сигнал вызова автономного контроля с выхода генератора 1(например, после подачи на вход ОЗУ питающих напряжений устанавливает в нуле вое состояние триггеры 2-, регистр 5, счетчики 6 и 7 и в единичное состояние регистры 8 и 9. Низкий уровень сигнала с единичного выхода триггера 2 поступает на соответствующие входы элементов И 10 и 11 и блокирует устройство по адресным lOf-fOyj и числовым 41 входам от внешних устройств-пользователей. Сигнал вызова автономного контроля устанавливает в нулевое состояние счетчики б5 и 66, триггеры 68 и б9 и в единичное состояние триггер 70 (фиг.З). Сигнал вызова автономного контроля через элемент ИЛИ 7 блока 16 устанавливает в нулевое состояние регистры 17, после чего по заднему фронту сигнала вызова автономного контроля на выходе формирователя блока 16 формируется сиг- , нал, который переключает в единичное состояние триггер 68 блока 1б и первые разряды регистров 17 (через соответствующие элементы ИЛИ 20). При этом открываются соответствующие элементы И 12, соединяя через элементы ИЛИ 18 генерирующий контрольный тест выход элемента И 88 блока 16 со входами накопителей2 4. Сигнал высокого уровня с единичного выхода триггера 68 открывает элемент И 89, соединяя выход генератора 2б со счетным входом счетчика б5, в результате чего запускаются 9 счетчик 65, элемент ИЛИ 76, дешифра тор 15, выполняющие функцию распределителя импульсов. Нулевому состоянию счетчика 66 соответствует возбуждение первого вы хода дешифратора 10б, в результате чего блок 16 формирует команду Запись прямого шахматного кода , в соответствии с которой производится запись прямого шахматного кода в накопители Z фиг.1). Запись тяжелого кода начинается с первой ячейки каждого накопителя 2, при этом во все нечетные ячейки накопителей 2 записываются О, а во все четные ячейки - 1. Регистр 5 последовательно перебирает все адреса, а бло 16, реагируя на состояние младшего разряда регистра 5, формирует на нулевом выходе триггера 71 (фиг.3)контрольный тест, которьТй через открытый элемент И 88, элементы ИЛИ 1В и элементы И 12 поступает на входы накопителей 2. Запись Контрольного теста в накопители производится под действием сигнала, который форми руется на выходе триггера 72. Последовательное переключение регистра 5 в очередное состояние проис ходит под воздействием сигнала, поступающего с последнего выхода (дешифратора 105 через открытый элемент И 90 на счетный вход регистра 5. После первого обхода всех адресов регистр 5 снова оказывается в ну левом состоянии, при этом счетчик 66 переключается в очередное состояние сигналом переноса с выхода регистра 5,которому соответствует возбуждение второго выхода дешифратора 106, в результате чего блок 16 формирует команду Чтение. Чтение тяжелого кода, записанного при первом обходе адресов, начинается с первой ячейки каждого накопител 2k. Информация с накопителей 2k поступает в блок 27, в котором производится поразрядное сравнение считанной с накопителей 2k информации с эталонным сигналом, который формируется на выходе элемента ИЛИ 77 с учетом состояния младшего разряда ре гистра 5 и выполняемой команды. Результат контроля после стробирования сигналом с выхода элемента И 91 фиксируется регистром 8. После вторичного обхода всех адресов, т.е. после сиитывдния информа ции из йсрх ячеек накопителей 2Ч, Si разряды регистра 8, соответствующие исправным накопителям 2k, останутся в единичном состоянии, а разряды, соответствующие неисправным накопителям 2, переключаются в нулевое состояние. Переключение разрядов регистра 8 в нулевое состояние происходит при наличии хотя бы одного сбоя fошибки) в считанной информации во время вторичного обхода всех адресов накопителей 2. После вторичного обхода адресов регистр 5 оказывается в нулевом состоянии, а счетчик- 66 переключается в- новое состояние, которому соответствует возбуждение третьего выхода дешифратора 106, в результате чего блок 16 формирует команду Запись обратного шахматного -кода внакопители . Запись этого кода начинается с первой ячейкикаждого накопителя 2k, при этом во все нечетные ячейки накопителей записываются 1, а во все четные ячейки . После.третьего обхода всех адресов регистр 5 снова оказывается в нулевом состоянии, а счетчик 66 переключается в очередное состояние, которому соответствует возбуждение последнего выхода дешифратора 106, в результате чего блок 16 повторно формирует команду Чтение. Чтение кода, записанного при третьем обходе адресов, начинается с первой ячейки каждого накопителя 2k. Информация с накопителей поступает в блок 2 в котором производится поразрядное сравнение считанной с накопителей информации с эталонным сигналом, который формируется на выходе элемента ИЛИ 77 с учетом состояния младшего разряда регистра 5 и выполняемой команды. Результат контроля после стробирования сигналом с выхода элемента И. 91 фиксируется регистром 8. После четвертого обхода всех адресов, т.е. после считывания информации из всех ячеек накопителей 2k, раз ряды регистра 8, соответствующие исправным накопителям 2k, остаются в единичном состоянии, а разряды, соответствующие неисправным накопителям , переключаются в нулевое состояние. Таким образом, после двухкратного считывания контрольной информации из всех ячеек накопителей в регистре 8 будет зафиксирован код, отражающий данные о исправности накопителей 2. После четвертого обхода всех адресов регистр 5 снова оказывается в нулевом состоянии, при этом счетчик 66 тоже переключается в нулевое состояние, которому.соответствует возбуждение первого выхода дешифратора 106, а очередному состоянию счетчика 67 соответствует возбуждение второго выхода дешифратора 107. В момент возбуждения второго выхода де шифратора 107 на выходе формировател 85 формируется сигнал, который через элемент ИЛИ 7 устанавливает в нулевое состояние регистры 17, после чего по заднему фронту этого сигнала на выходе формирователя 86 вырабатывается сигнал, который через соответ ствующие элементы ИЛИ 21 (фиг.1) переключает в единичное состояние разряды зёгистра 17. При этом открываются соответствующие элементы И12, соединяя через элементы ИЛИ 22 и 18, генерирующий контрольный тест выход элемента И 88 фиг.З) со входами накопителей 25. Проверка работоспособности накопителей 25 (фиг.1) производится аналогично проверке работоспособности накопителей путем последовательной записи в ячейки накопителей 25 прямого шахматного кода, считывани контрольной информации, записи обрат ного шахматного кода и повторного считывания контрольной информации. При этом Считанная контрольная информация поступает в блок 28, с выхода которого результат контроля пос ле стробирования сигналом с выхода 57 блока 16 фиксируется регистром 9. После четвертого обхода всех адресов накопителей 25 регистр 5 снова оказывается в нулевом состоянии, при этом счетчик (фиг. 3) переключается в нулевое состояние, а счетчик б7 в очередное состояние, которому со ветствует возбуждение третьего выхода дешифратора 107, в результате чего триггер 68 переключается в нулевое состояние. Низкий уровень сигнала с единичного выхода триггера 6 закрывает элемент И 89, отключая выход генератора 26 фиг.1 от входа блока 16, что приводит к останову распределения импульсов в блоке 16. В оиент возбуждения третьего выхода дешифратора 107 иа выходе формирователя 87 формио гся сигнал. который устанавливает в нулевое состояние регистры 17 и переключает в единичное состояние триггер 3. Сигнал высокого уровня с единичного выхода триггера 3 открывает элемент И 29, соединяя счетный вход счетчика 6 с ВЫХОДОМ генератора 2б. Состояние счетчика 6 дешифрируется дешифратором 3.2. Выход переноса счетцика 6 соединен со счетным входом счетчика 7, состояние которого дешифрируется дешифратором 33. Дешифраторы 32 и 33 служат для опроса состояния разрядов регистров 8 и 9. Опрос производится циклически в следующейпоследовательности. В течение первого цикла опрашиваются, первый разряд регистра 8 и все разряды регистра 9- Во втором цикле - второй разряд регистра В и все разряды регистдз циклов равно числу разрядов регист.ра, т.е. числу накопителей 2. ОпIpoc регистров 8 и 9 производится с Целью автоматической коммутации исправных накопителей 2 или 25 в числовой тракт ОЗУ. Опрос начинается с первого разряда регистра 8. Если этот разряд находится в единичном состоянии, что свидетельствует об исправном состоянии первого из накопителей 2k, то на выходе первого из элементов И появляется сигнал, который устанавливает первый разряд первого из регистров 17 в единичное состояние. При этом открываются первые из элементов И 12 и 13, соединяя вход и выход первого из накопителей .Ц соответственно с выходом первого из элементов И 11 и с выходом Z (через первый из элементов ИЛИ 19). Если,например,, первый разряд регистра 8 находится в нулевом состоянии,, что свидетельствует о неисправном состоянии первого из накопителей 2k, то в результате послег довательного опроса производится с поиск любого первого исправного на-i копителя 23 для замещения им неис-, правного накопителя 2k. Пусть, например, все разряды регистра 9 за исключением последнего находятся в нулевом состоянии, что свидетельствует о неисправном состоянии всех накопителей 25, за исключением последнего. Тогда при последовательном опросе разрядов регистра Э на выходе ( K+1 } - ГО из элементов И Т появляется сигнал, который устанавливает после ний разряд первого из регистров 17 в единичное состояние. При этом открываются соответствующие элементы .И 1-2 и 13, соединяя соответственно вход и выход последнего из накопителей 25 с выходом первого из элементов И 11 (через первый из элемен тов ИЛИ 18 и последний из элементов ИЛИ 22) и с выходом 42 (через первы из элементов ИЛИ 18)- После переключения последнего разряда первого из регистров 17 в единичное состояние на выходе последнего из элементов ИЛИ 23 появляется сигнал, который устанавливает последний разряд регистра 9 в нулевое состояние. После заполнения счетчик 6 снова устанавливается в нулевое состояние счетчик 7 переключается в очередное состояние. Во втором и последую щих циклах опрос регистров 8 и 9, а также коммутация исправных из накоп телей и 25 в числовой тракт ОЗУ происходит аналогично их опросу в первом цикле. При этом исправные из накопителей 25, включенные вмест неисправных накопителей в предыдущем цикле , в ,последую1цих циклах воспринимаются как неисправный, так как в предыдущих циклах происходит переключение соответствующих им разрядов регистра 9 в нулевое со стояние. Это обеспечивает в каждом цикле коммутацию в числовой тракт ОЗУ не только исправного, но также свободного, незанятого из накопителей 25 вместо неисправного из накопителей 2k. После заполнения счетчиков 6 и 7 и в.озбуждения последних выходов дешифраторов 32 и 33 на выходе элемен та И 30 появляется сигнал высокого уровня, который устанавливает в еди ничное состояние триггер 2 и в нулевое состояние триггер 3 (через элемент ИЛИ З). Сигнал низкого уро ня с единичного выхода триггера 3 закрывает элемент И 29, отключая выход генератора 26 от счетного входа счетчика 6. Сигнал высокого уровня с единичного выхода триггера 2 поступает на соответствующие входы элементов И 10 и П, что приводит к раз блокировке устройства по адресным и числовым входам. Под воздействием сигналсч высокого уровня с единичного выхода тоиггерл 2 возбуждается элемент индикации 35, что свидетельствует об окончании режима самоконтроля в ОЗУ. Сигнал высокого уровня с единичного выхода триггера 2 поступает также на один из входов элемента И 93 (фиг. 31, что приводит к разблокировке устройства по входу 39Сигнал высокого уровня с выхода элемента И 30 .(фиг.1) поступает на один из входов элемента И 31, на второй вход которого поступает сигнал с выхода элемента НЕ 37. При этом, если на выходе элемента НЕ 37 появляется сигнал вйсокого уровня после появления сигнала высокого уровня на выходе элемента И 30, т.е. после окончания циклического, последовательного опроса всех разрядов регистров 8 и 9, то навыходе элемента И 31 тоже появляется сигнал высокого уровня, который переключает триггер t в единичное состояние, в результате чего происходит возбуждение элемента индикации 36, что свидетельствует об исправном состоянии ОЗУ и его готовность к работе с устройствами-пользователями. Переключение в единичное состояние триггера k и возбуждение элеме ита индикации 36 происходит в случае, если суммарное число исправных накопителей 2 и 25 составляет не менее от общего числа этих накопителей. Следовательно, максимальное число неисправностей, которые устраняются в ОЗУ в режиме самоконтроля, nAnri-nV, где m - общее число накопителей 24 - и 25; п - число накопителей 2k. После окончания режима самоконтроля, т.е. после разблокировки по входам 39, и k запоминающее устройство готово к работе с внешними устройствами. В режиме записи на входы 38 и 39 поступают соответственно сигналы высокого уровня Команда и Обращение, а на входы 40; и адреса и код входного числа.Код адреса записывается в регистр 5- Сиг нал Обращение через открытый элемент И 93 (фиг.З) переключает в единичное состояние триггер 69, в результате чего открывается элеменИ 9, соединяя выход генератора 26 со счетным входом счетчика 65 через элемент ИЛИ 75- Происходит запуск распределения импульсов в блоке 16, выполняющегося до момента возбуждения последнего выхода дешифратора 105. Сигнал Команда через открыты элемент И 95 переключит триггер 73 в единичное состояние, в результате чего открывается элемент И 96, соединяя соответствующий выход дешифратора 105 с единичным входом триггера 72 (через элемент ИЛИ 79). После переключения в единичное сост тояние триггера 72 на его нулевом в ходе появляется низкий уровень сигнала, который разрешает запись вход ного числа в накопители 2 или 25 по/указанному адресу, который хранится в регистре 5, После возбуждения соответствующего выхода деши1фратора 105 триггер72 опять устанав ливается в нулевое состояние, в результйте чего прекращается запись кода в накопители 2 и 25. После во буждения последнего выхода дешифратора 105 триггеры б9 и 73 и счетчик б5 устанавливаются в нулевое состоя ние. При этом закрывается элемент И 9, отключая счетный вход счетчика 65 от выхода (тактового)генерал тора 26 (фиг. 1 . В режиме считывания на вход 38 поступает сигнал.Команда низкого уровня, на 39 - сигнал Обращение 1 l16 высокого уровня, на входы Оцкод адреса. Так как сигнал Команда имеет низкий уровень, то триггер 73 остается в нулевом состоянии. Поэтому триггер 72 тоже остается в нулевом состоянии, в результате чего из накопителей Z или 25 происходит считывание информации по адресу, записанному в регистр 5. В остальном уст- . ройство работает аналогичным обра- . зом, т.е. происходит в блоке 1б запуск распределения импульсов, формирование управляющих сигналов и останов. Таким образом, введение в ohepgтивное запоминающее устройство с самоконтролем второй труппы одноразрядных накопителей, двух контрольных регистров, второго блока контроля, аторого счетчика, второго дешифратора, групп элементов ИЛИ и групп элементов И с третьей пи четвертую, элемента И, элемента НЕ и новых связей, позволяет повысить надежность устройства путем автономного контроля его работоспособности и автоматической коммутации в числовой тракт ОЗУ исправных из одноразрядных накопителей первой и второй групп. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности по сравнению с прототипом.

х; S

ШЬ

W

//

W

««

S3

Art

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МАГНИТНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU329578A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1983-09-15—Публикация

1982-04-27—Подача