Предлагаемое устройство может быть нспользовано в радиотехнических установках, в частности в ядерно-физической аппаратуре различного назначения, в том числе и полевых портативных приборах, где ставится задача регистрации разности в числе импульсов, проходящих в течение двух или нескольких последовательных отрезков времени (например, автоматическое вычитание фоновой радиации, выполнение анализатора для рентгенорадно.метрического анализа и т. д.). Аналогичные задачи возникают часто и при предварительной обработке накопленной информации.

Известны разностные счетные устройства ка четырех симметричных триггерах с перекрестной связью, разделенных ключевыми каскадами, которые управляют режимами суммирования и вычитания, с введением обратной связи. Вывод данных о числе накопленных импульсов обеспечивается с помощью привода на люминесцентный знаковый индикатор.

Так как в больщинстве случаев объем памяти счетных схем составляет не менее 10 импульсов, основны.ми недостатками известных устройств является сложность (по числу используемых элементов) и значительная потребляемая мощность, что практически исключает применение их в портативной аппаратуре.

Данное устройство для упрощения схемы разностного счета двух или нескольких последовательностей импульсов, поступающих на один и тот же вход схемы памяти, упрощения вывода информации и сокращения потребляемой мощности содержпт переключатель разрядов, входы которого соединены с программным переключателем и выходо.м индицированного декадного счетчика, а выходы - со схемой пропускания, ключом связи между входом устройства и декадными счетчиками схемы памятн, а также с ключами связи между декадными счетчиками. Схема знака разности подключена к выходу схемы памят11 и ключам связи между декадными счетчиками схемы намяти, а также к схеме пропускания управляющих импульсов и к программному переключателю, связанному с ключами блока преобразования.

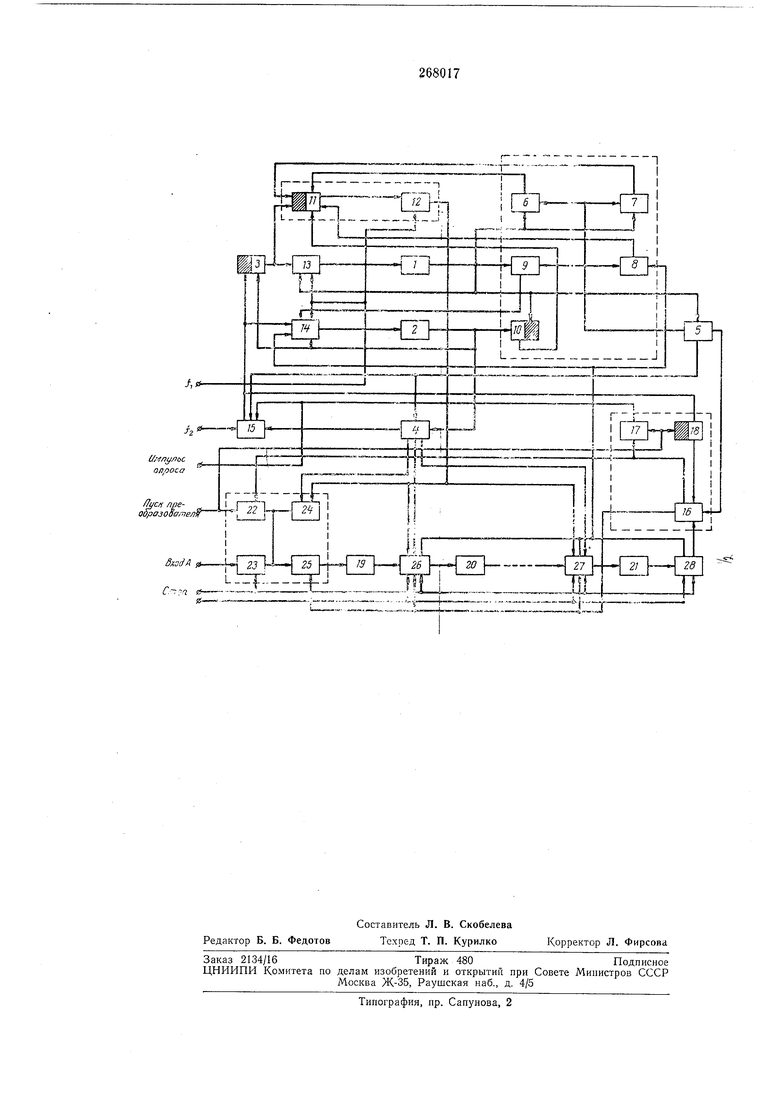

Блок-схема устройства изображена на чертеже.

Устройство состоит из двух функциональных частей - блока преобразования и регистрирующей схемы памяти. Блок преобразования включает в себя буферный декадный счетчик /, индицированный декадный счетчик 2, управляющий симметричный триггер 3 с раздельным запуском, пepeключaтev ь разрядов 4, представляющий собой пересчетную схему, программный переключатель 5. Ключи 6-9 и симметричный триггер 10 с раздельным запуском образуют ключевую схему связи. Симметричный триггер //с несколькими входами и ключ 12 составляют проиускатель унравлкющих имнульсов, аиалогцчиый иронускателям 13-16. Пронускатель 16, ключ 17 и симметричный триггер 18 с раздельным запуском образуют схему знака разности. Регистрирующая счетная схема состоит из п последовательно включенных декадных счетчиков 19- 21. Ключи Z2-24 и имнульсный согласующий усилитель 25 составляют каскад связи между первым десятичным счетчиком и входом устройства. Аналогичные каскады связи 26-28 соединяют соответствующие десятичные счетчики. На вход А устройства подают две последовательности импульсов NI т . . . Ьа и //2 tn ,-,- bifli, при регистрации которых должна быть получена их разность Л:-N,, где flifr ... miai&i... ml - значения разрядов данных последовательностей импульсов. Для простоты рассмотрим процесс (порядок операций) получения разности двух последовательностей имнульсов G 10 и Ло а при их регистрации счетной схемой памяти, состоящей из одного декадного счетчика. Могут быть два варианта очередности иоступления на вход схемы памяти числа импульсов и . Вариант .,. После регистрации числа импульсов N a состояние декадного счетчика схемы памяти преобразуется сначала в результате добавления единицы в (a+l), а затем путем вычитания из десяти в состояние 10-(a-f I). исло импульсов N2 a суммируется с преобразованным состоянием 10-(а+1). По окончании регистрации N-2 декадиый счетчик схемы иамяти оказывается в состоянии 10- (а + 1) + о , которое иутем добавления единицы и последующего вычитания из десяти иреобразуетс.ч в состояние, соответствующее разности двух последовательностей импульсов. В случае многозначных последовательностей импульсов число декадных счетчиков счетной схемы выбирают из условия 10, где п - число декадных счетчиков. После регистрации операции а-}-1 и 10-(о+1) происходят в каждом разряде числа без переноса единицы в соседний старший разряд. Вариант jVi c/V2Операции после регистрации NZ те же, что и ири варианте . После регистрации Л2 как при одноразрядном, так и при многоразрядном числах проводится лищь операция добавления единицы в младщий разряд с последующим переносом импульса наполнения разрядов в соседний старший разряд. Операция «а проводится в момент прихода импульсов, при этом все декадные счетч ки включены последовательно. ча 12, и аналогичные ему пропускатели 13- 15 закрыты, а пропускатель 16 схемы знака разности открыт. Программный переключатель 5 устанавливает ключ 6 закрытым, а ключ 7 н S - открытыми. Переключатель разрядов 4 иаходится в положении, при котором подключен декадпый счетчик 21 схемы памяти. Добавление единицы во все разряды происходит по скоичании регистрации последовательности импульсов (срабатывание таймера). В этот момент последовательные связи .между декадными счетчиками схемы памяти разорваны вследствие запирания внешним сигналом «стоп ключа 23 входного каскада связи и аналогичных ему в каскадах связи 26 - 28. Одновременно с приходом сигнала «стон внешний импульс «пуск преобразования нодготавливает триггер 18 к приему импульса частотой /2 и через ключ 17 открывает пропускатель 15. С приходом импульса частотой /2 триггер 18 через пропускатель 16 добавляет единицу во все разряды счетной схемы через согласующий усилитель 25 входного каскада связи и аналогичных ему усилителей каскадов связи 26 и 27. Операция 10- (a+l). Одновременпо с приходом импульса частотой /2 управляющий триггер 8 подготавливается к приему импульса цикла преобразования состояния разряда схемы памяти, пропускатель 14 открывается, и импульсы частотой /, дополняют до десяти индицированный декадный счетчик 2, выходпой импульс которого закрывает пропускатель 14 и перебрасывает управляющий триггер. Импульсом последнего триггер // перебрасывается в положение, при котором ключ 12 открывается. Пропускатель 13, в котором происходят аналогичные преобразования, также открывается. Таким образо.м, импульсы частотой fi поступают одновременно на декадные счетчики / и 21. После прихода в декадный счетчик 21 старшего разряда схемы памяти числа и.мпульсов 10-(а+1) ои заполняется до десяти и выдает имиульс, который открывает пропускатель М и через ключ 8 перебрасывает триггер 11, закрывающий ключ 12, что обеспечивает поступление импульсов частотой /i в декадиые счетчики / и 2. При заполнении буферного декадного счетчика 1 до десяти его выходной импулье перебрасывает триггер // в положепие, при котором открывается ключ 12, закрывает пропускатель 13 и подготавливает к приему выходного импульса индицированного декадного счетчика 2 триггер 10. С приходом импульса со счетчика / счетчик 2 регистрирует (a-f-l) импульсов. В этот момент счетчик 21 схемы намяти готов к приему импульсов дополнения с частотой fi. После заполнения счетчика 2 до десяти счетчик 21 регистрирует 10-(а+1) импульсов. Импульсо.м счетчика 2 перебрасывается триггер 10, который в свою очередь Одновременно закрывается пропускатель 14, а переключатель 4 подключает декадный счетчик схемы памяти разряда п-/. Время Т преобразования схемы памяти ЗОп бирают из условия Т -- , где п - число /1 декадных счетчиков. С приходом следующего импульса частотой /2 - преобразуется состояние декадного счетчика следующего разряда счетной схемы и т. д. После преобразования младшего разряда выходным импульсом переключателя разрядов пропускатель /5 закрывается. Счетная схема готова к регистрации последовательности импульсов А/2. Переключатель разрядов находится в положении, при котором подключен старший разряд. Операция «+1 в младший разряд. После заполнения счетной схемы при регистрации последовательности импульсов N выходной импульс декадного счетчика 21 старшего разряда через ключевой каскад 28 закрывает пропускатель 16 и ключ 17, а ключ 22 открывается. По окончании регистрации .импульсов jVo (срабатывание таймера) на данное устройство подаются и.мпульс «пуск преобразования и сигнал «стоп. Импульс «пуск преобразования опережает сигнал «стоп на время, достаточное для переноса единицы во всех разрядах схемы памяти. Импульс «пуск преобразования через ключ 22 добавляет к состоянию счетной схемы единицу. Состояние декадных счетчиков схемы памяти не изменяется, так как ключ 17 закрыт, и пропускатель 15 становится неуправляемым. Режим вывода информации из схемы памяти определяется положением программного переключателя 5, при котором ключи 7 и S закрыты, ключи 6 и 9 открыты и пропускатель 16 закрыт. Состояние остальных узлов устройства аналогично режиму преобразования после регистрации последовательности импульсов . Опрос декадных счетчиков начинается со старшего разряда схемы памяти (срабатывание таймера) после получения разности или зарегистрированной последовательности импульсов. В этом случае программный переключатель 5 блокирует схему преобразования. С подачей разового импульса опроса пропускатель 15 открывает пропускатель 14 и подготавливает к приему импульса цикла управляющий триггер 3. Импульсы частотой /j через пропускатель наполняют индицированный декадный счетчик 2, и он сбрасывается в нуль. Выходной импульс с него закрывает пропускатель 14 и перебрасывает триггер 3. Выходной импульс управляющего триггера перебрасывает триггер 11, открывает ключ 12 и пропускатель 13. Таким образом, на входы опрашиваемого разряда и буферного декадного счетчика / поступают импульсы частотой /i. Пусть опрашиваемый декадный счетчик 21 на.чодится в состоянии «т. С регистрацией им числа импульсов 10-т его выходной импульс открывает пропускатель 14. В этот момент счетчик / регистрирует 10-т импульсов, а счетчики 2 и 21 находятся в состоянии «нуль. Для дополнения счетчика / до десяти на его вход, а, следовательно, и на счетчики 2 и 2/ должно поступить т импульсов. По заполнении счетчика / его выходной импульс перебрасывает триггер //, закрывает ключ 12 и пропускатели 13-15 и одновременно подключает следующий разряд за счет автоматического перехода в новое состояние переключателя разрядов 4. С приходом следующего импульса опроса начинается аналогичный процесс вывода информации. Вывод инфор.мации проходит без разрушения памяти счетной схемы. Возможна индикация номера опрашиваемого разряда с помощью переключателя 4. Предмет изобретения Разностное счетное устройство, содержащее схему памяти из п последовательно включенных через ключи декадных счетчиков и блок преобразования, выполненный из буферного и индицированного декадных счетчиков, триггеров, ключей, схем пропускания, схемы знака разности и программного переключателя, отличающееся тем, что, с целью обеспечения возможности работы по одному счетному входу, упрощения как разностного устройства, так и схемы вывода информации, уменьщения потребляемой мощности, оно содержит переключатель разрядов, соединенный входами с программным переключателем и с выходом индицированного декадного счетчика, а выходами - со схемой пропускания, ключом связи между входолг устройства и декадными счетчиками схемы памяти, а также с ключами связи между декадными счетчиками; схема знака разности подключена к выходу схемы памяти и ключам связи между декадными счетчиками схемы памяти, а также к схеме пропускания управляющих импульсов и к программному переключателю, связанному с ключами блока преобразования. Лус/i ппе-.. oSpojoSoi eM .br::L.J I

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Адаптивный цифровой частометр с нормированием динамической погрешности | 1972 |

|

SU447636A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТОМЕР С НОРМИРОВАНИЕМ ДИНАМИЧЕСКОЙ ПОГРЕШНОСТИ | 1973 |

|

SU409148A1 |

| Устройство преобразования последовательного двоичного кода в код десятичный | 1978 |

|

SU782155A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| Вторичные цифровые часы с секундомером | 1987 |

|

SU1478187A2 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Устройство для цифровой индикации | 1972 |

|

SU445053A1 |

| СТЕНД ДЛЯ ДИНАМИЧЕСКОЙ БАЛАНСИРОВКИ КОЛЕС | 1991 |

|

RU2036449C1 |

Даты

1970-01-01—Публикация