1

Изобретение относится к импульсной технике, может быть использовано в цифровом синтезаторе частот.

Известны делители частоты с дробным переменным коэффициентом деления, содержащие управляемый делитель целых с вентилем на входе, логические элементы «ИЛИ, причем в каждом дробном разряде - управляемый делитель с вентилем на входе, первый вход которого соединен с входной шиной, пересчетную схему, вход «отарой в младшем разряде соединен через второй вентиль со входом управляемого делителя, триггер, нулевой вход которого соединен с выходом управляемого делителя, а единичный выход - со вторым входом вентиля на входе управляемого делителя.

Цель изобретения - расширение функциональных возможностей.

В предлагаемом делителе в каждом дробном разряде выход управляемого делителя .соединен с единичным входом триггера соседнего старшего дробного разряда, второй вход второго вентиля - со входом управляемого делителя своего разряда, выход пересчетной схемы - со входом пересчетной схемы соседнего старшего дробного разряда через вентиль «ИЛИ, выход управляемого делителя целых - с единичным входом триггера младшего дробного разряда, первый вход вентиля

на входе управляемого делителя целых - с единичным выходом дополнительного триггера, нулевой вход которого связан с выходом пересчетной схемы старшего дробного разряда, а единичный -со входной шиной и вторым входом вентиля на входе управляемого делителя целых.

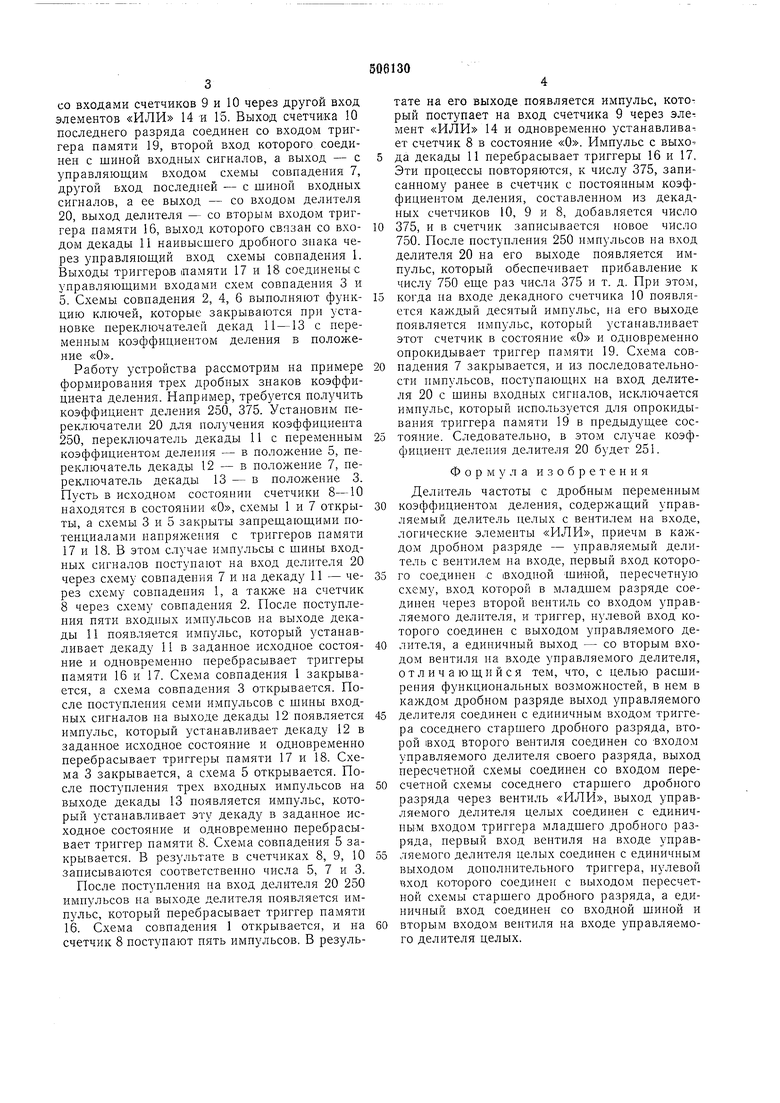

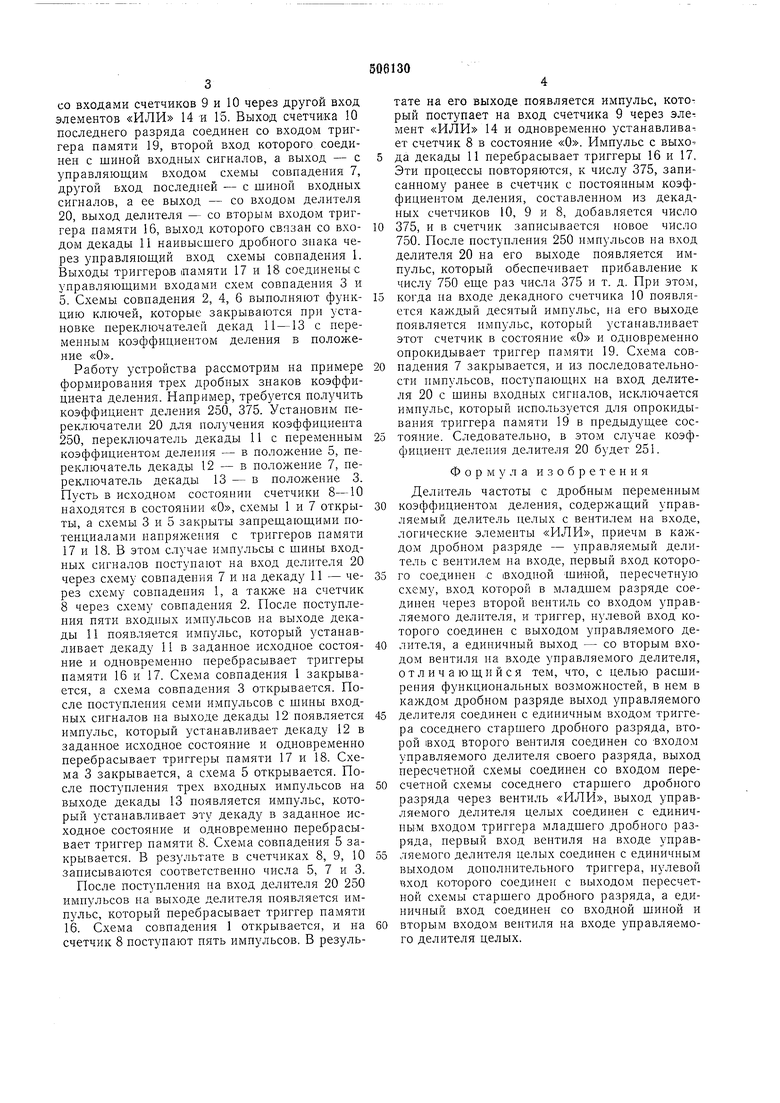

На чертеже представлена 6vTOK-cxeMa устройства.

Делитель содержит схемы совпадения 1-7, декадные счетчики 8-10, дополнительные декады 11 -13 с переменным коэффициентом деления, в которых происходит установка числа от О до 9 в разряде тысячных, сотых и десятых долей набираемого коэффициента деления; элементы «ИЛИ 14 и 15, триггеры памяти 16-19 и делитель 20, составленный из трех декад с переменным коэффиицентом деления. Входы декад 11 -13 связаны с шиной входных

сигналов через схемы совпадения 1, 3, 5, а выходы присоединены к соответствующим входам триггеров 16-18. Вход декадного счетчика 8 наинизшего разряда соединен со входом дополнительной декады 11 наивысшего дробного знака через схему совпадения 2, а входы счетчиков 9 и 10 соединены с соответствующими дополнительными декадами 12 и 13 при помощи последовательно включенных схем совпадения 4 и 6 и элементов «ИЛИ 14 и 15. Выходы счетчиков 8 и 9 связаны соответственно

со входами счетчиков 9 и 10 через другой вход элементов «ИЛИ 14 и 15. Выход счетчика 10 последнего разряда соединен со входом триггера памяти 19, второй вход которого соединен с шиной входных сигналов, а выход - с управляющим входом схемы совпадения 7, другой вход последней - с шиной входных сигналов, а ее выход - со входом делителя 20, выход делителя - со вторым входом триггера памяти 16, выход которого связан со входом декады И наивысшего дробного знака через уиравляюш,ий вход схемы совпадения 1. Выходы триггер01В памяти 17 и 18 соединены с управляющими входами схем совпадения 3 и 5. Схемы совпадения 2, 4, 6 выполняют функцию ключей, которые закрываются при устаповке переключателей декад 11 -13 с переменным коэффициентом деления в положение «О.

Работу устройства рассмотрим на примере формирования трех дробных знаков коэффициента деления. Например, требуется получить коэффициент деления 250, 375. Установим переключатели 20 для получения коэффициента 250, переключатель декады 11 с переменным коэффициентом деления - в положение 5, переключатель декады 12 - в полол ;ение 7, переключатель декады 13 - в положение 3. Пусть в исходном состоянии счетчики 8-10 находятся в состоянии «О, схемы 1 и 7 открыты, а схемы 3 и 5 закрыты запрещающими потеициалами иапряжения с триггеров памяти 17 и 18. В этом случае импульсы с шины входных сигналов поступают на вход делителя 20 через схему совпадения 7 и на декаду 11 - через схему совпадения 1, а также на счетчик 8 через схему совиадения 2. После поступления пяти входных импульсов на выходе декады 11 появляется импульс, который устанавливает декаду 11 в задаииое исходное состояние и одновременно перебрасывает триггеры памяти 16 и 17. Схема совпадения 1 закрывается, а схема совпадения 3 открывается. После поступления семи импульсов с шины входных сигналов иа выходе декады 12 появляется имиульс, который устанавливает декаду 12 в заданное исходное состояние и одновременно перебрасывает триггеры памяти 17 и 18. Схема 3 закрывается, а схема 5 открывается. После поступления трех входных импульсов на выходе декады 13 появляется импульс, который устанавливает эту декаду в заданное исходное состояние и одновременно перебрасывает триггер памяти 8. Схема совпадеиия 5 закрывается. В результате в счетчиках 8, 9, 10 записываются соответствеиио числа 5, 7 и 3.

После поступлепия на вход делителя 20 250 импульсов на выходе делителя появляется импульс, который перебрасывает триггер памяти 16. Схема совпадеиия 1 открывается, и иа счетчик 8 постуиают пять импульсов. В результате на его выходе появляется импульс, который поступает на вход счетчика 9 через элемент «ИЛИ 14 и одновременно устанавливав ет счетчик 8 в состояние «О. Импульс с выхо

да декады 11 перебрасывает триггеры 16 и 17, Эти процессы повторяются, к числу 375, записанному ранее в счетчик с постоянным коэффициентом деления, составленном из декадных счетчиков 10, 9 и 8, добавляется число

375, и в счетчик записывается новое число 750. После поступлепия 250 имиульсов на вход делителя 20 на его выходе появляется импульс, который обеспечивает прибавление к числу 750 еще раз числа 375 и т. д. При этом,

когда иа входе декадного счетчика 10 появляется каждый десятый импульс, на его выходе появляется импульс, который устанавливает этот счетчик в состояние «О и одиовременно опрокидывает триггер памяти 19. Схема совпадепия 7 закрывается, и из последовательности импульсов, поступающих иа вход делителя 20 с шины входных сигналов, исключается импульс, который используется для опрокидывания триггера памяти 19 в предыдущее состояиие. Следовательио, в этом случае коэффициент деления делителя 20 будет 251.

Формула изобретения

Делитель частоты с дробным переменным

коэффициеитом деления, содержащий управляемый делитель целых с вентилем па входе, логические элемеиты «ИЛИ, приечм в каждом дробиом разряде - уиравляемый делитель с веитилем иа входе, первый вход которого соединен с входной шиной, нересчетную схему, вход которой в младшем разряде соединен через второй вентиль со входом управляемого делителя, и триггер, нулевой вход которого соединен с выходом управляемого делителя, а едииичиый выход - со вторым входом вентиля иа входе управляемого делителя, отличающийся тем, что, с целью расширения функциональных возможностей, в нем в каждом дробиом разряде выход уиравляемого

делителя соединен с единичным входом триггера соседиего старшего дробиого разряда, второй вход второго вентиля соединен со входом управляемого делителя своего разряда, выход пересчетной схемы соединен со входом иересчетной схемы соседнего старшего дробиого разряда через веитиль «ИЛИ, выход управляемого делителя целых соедииен с единичным входом триггера младшего дробиого разряда, первый вход вептиля на входе управляемого делителя целых соедипен с единичным выходом дополнительного триггера, иулевой чход которого соединен с выходом пересчетиой схемы старшего дробного разряда, а единичный вход соединен со входной шиной и

вторым входом веитиля на входе управляемого делителя целых.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| Цифровой синтезатор частот | 1976 |

|

SU799100A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1972 |

|

SU344590A1 |

| Электронно-счетный частотомер | 1974 |

|

SU488161A1 |

| Одноканальное устройство для управленияВЕНТильНыМ пРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU839007A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1973 |

|

SU365029A1 |

пьПуП г з; Г7 jsiiiiiiii

Авторы

Даты

1976-03-05—Публикация

1974-01-17—Подача