(54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В КОД ДЕСЯТИЧНЫЙ

12

Изобретение относится к автоматике и электронно-вычислительной технике, технике регистрации и может быть использовано при построении преобразователей кодов в аппаратуре 5 обработки телеметрической информации.

Известно устройство преобразования последовательного двоичного кода в код десятичный по авт. св. Ю № 403058, содержащее переключатель, элементы И, элементы ИЛИ, декадный счетчик импульса, генератор фиксированного числа импульсов, при этом первые входы элементов И подключены 5 к переключателю, вторые через элементы ИЛИ .- к генератору фиксированного числа импульсов, а выходы элементов И соединены с декадным счетчиком импульсов i .20

Недостатком описанного устройства является замедленное время npiao6paэования, обусловленное количеством разрядов в слове и его длительностью, временем счёта импульсов декгщным 25 счетчиком импульсов, формируемых по кгикдому разряду входного последовательного кода.

Цель изобретения - повышение быст.родействия устройства.30

Указанная цель достигается тем, что в устройство преобразованияпоследовательного ДВО1ИЧНОГО кода в код десятичный, содержащее переключатель, элементы И, элементы ИЛИ, декадный счетчик импульсов, генератор фиксированного числа импульсов, при этом первые входы элементов И подключены к переключателю, вторые через элементы ИЛИ - к генератору фиксированного числа импульсов, причем выходы элементов И соединены с Декадным счетчиком импульсов,введены регистр, формирователь последовательного кода, последовательно соединенные формирователи импульсов, вход первого из KOTop dx соединен с первым выходсм переключателя, а выход - со счетньв входом декадного счетчика импульсов, выход второго формирователя импульсов - с управляющим входом регистра, третьего с управляющим входом формирователя последовательного кода и входом установки в нуль декадного счетчика импульсов, выходы которого соединены со входгши регистра, выходы которого являются выходами параллельного кода и соединены со входами . формирователя последовательного кода/ ;выход которого является выходом послёдовательного кода, и элемент за держки, вход которого соединен с информационной шиной, а выход - со входом линии задержки.

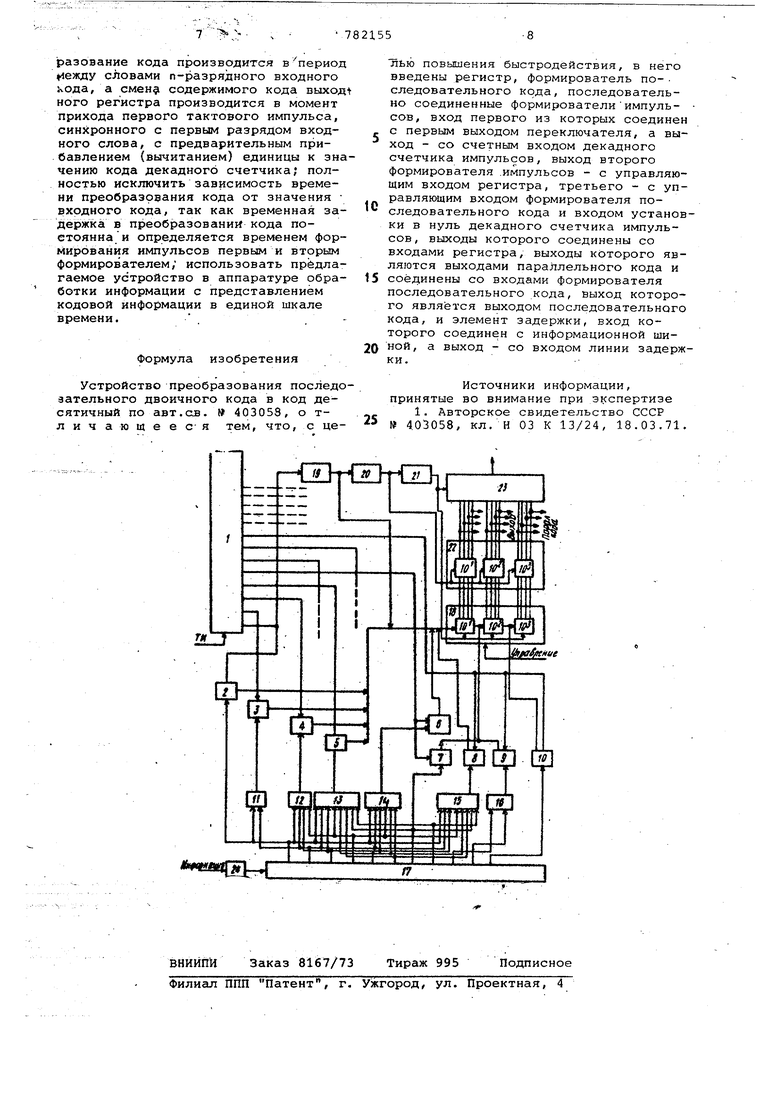

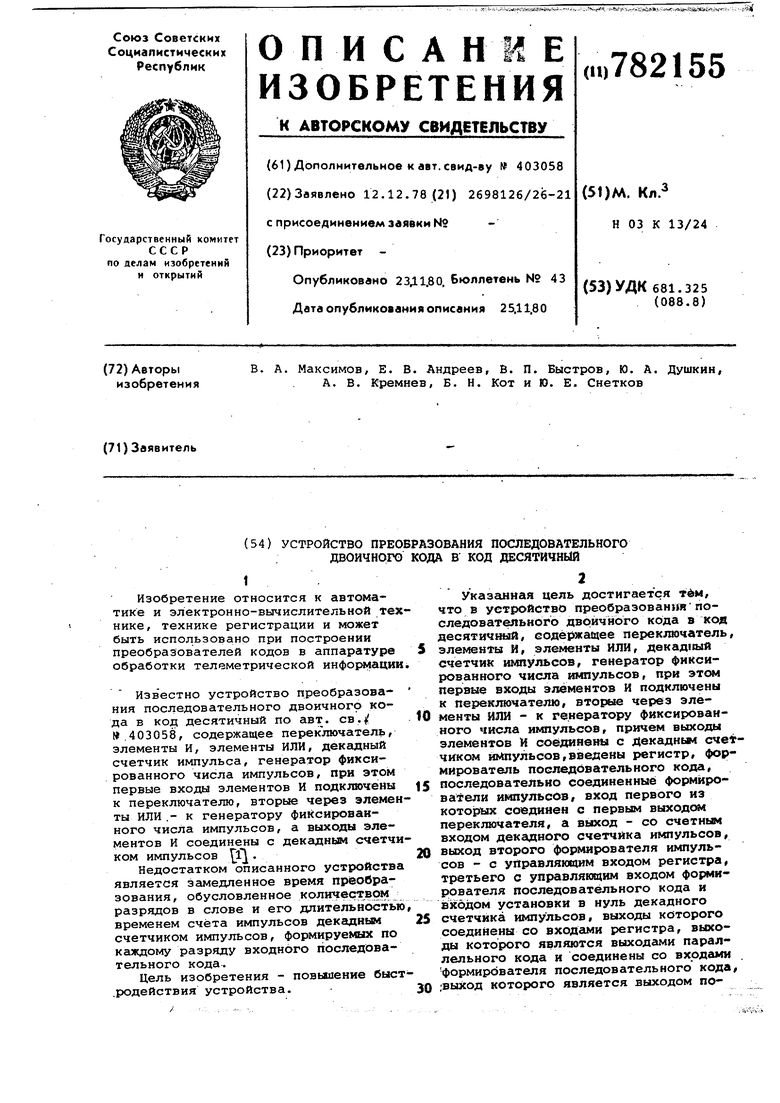

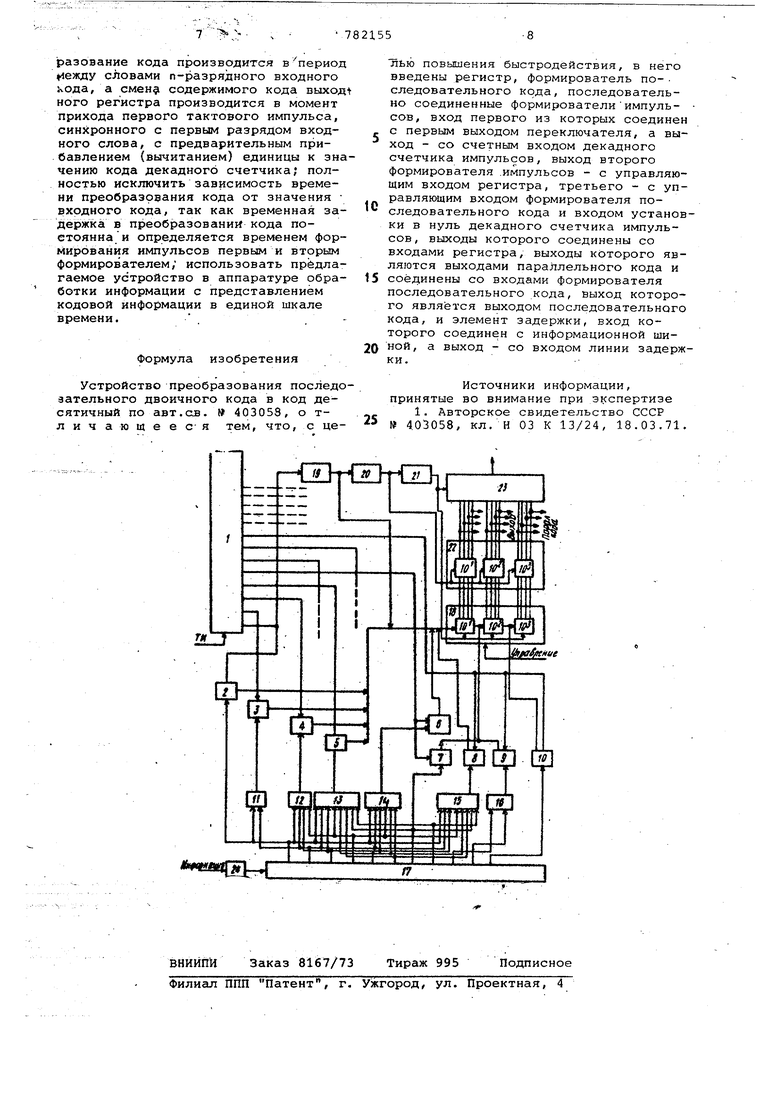

На чертежеизображена структурная электрическая схема устройства.

Устройство содержит переключатель 1, элементы 2-10 И, элементы 11-16 ИЛИ, линию 17 задержки, счетчик 18 декадных импульсов, формирователи 19-21 импульсов , регистр 22, формирователь 23 последовательного кода, элемент 24 задержки.

Устройство работает следующим образом.

В исходном состоянии содержимое счетчика 18 и регистра 22 соответствует предьвдущему значению входного кода (предыдущему значений п разрядного слова двоичного входного кода, преобразованного в десятичный код), находится в нулевом положении и выдает на все элементы 2-10 запрет. На вход линии 17 задержки через элемент 24 поступают импульсы последовательного двоичного входного кода.

На вход переключателя 1 поступают тактовые входные импульсы (ТИ), синхронно следующие с разрядами по ЪЛёйЬватель ногЬ вХоднбГо кода и переводящие переключатель 1 последовательно в положения 1, 2 ... п, где п - число двоичных разрядов в преобразуемом входном слоее.

После прихода первого тактового импульса, синхронного с первым разрядом входного кода, переключатель 1 перебрасывается с нулевого в первое положение.

С первого выхода переключателя 1 подается напряжение разрешения (первый стробирующиЗ импульс) на элемент 2. На элементы 3-10 вьщается запрет. Попереднему фронту первого ст|ЕЗобйрующего импульса на входе формирователя 19 с выходов последова-, тельно соединенной цепочки формирователей 19-21 выдаются сдвинутые относительно друг друга импульсы управления.

С выхода формирователя 19 сформированный импульс поступает на счетный вход счетчика 18, хранящего в сеёе предыдущее значение преобразованного входного кода, и изменяет его значение на единицу (увеличивает при работе с монотонно возрастающим, или уменьшает при работе с монотонно убывающим входным кодом). При этом значение счетчика 18 принимает значение эквивалентное значению Тходнбгбкода.

Выходной импульс с формирователя

20поступает на управляемый вход регистра 22, осуществляя запись в регистр 22.значения кода счетчика 18,

Выходной импульс с формйрова:теля

21поступает одновременно на сбро782155

совый вход счетчика 18, устанавливая его в нулевое состояние, и на вход формирователя 23 в качестве сигнала на разрешение формирования выходной структуры последовательного десятичного кода.

Одновременно с первым тактовым импульсом через элемент 24 на вход линии 17 задержки, представляющей собой генератор фиксированного числа импульсов, поступает первый разряд последовательного двоичного кода.

С первого отвода линии 17 задержки при значении первого разряда входного кода 1 через . элемент 2 на сче-тный вход счетчика 18 поступает один импульс для заполнения первой декады счетчика 18.

При этом суммарное время задержки tt f формирователя , формирователя формирователя 21, должно

быть меньше или равно времени задержки элемента 24. .

второй тактовый импульс перебрасывает переключатель 1 с Первого положекия во второе. Со второго отвода переключателя 1 подается напряжение разрешения (второй стробирующий импульс) на элемейт 3. На элементы И вьадается запрет.

Одновременно со сторым тактовым импульсом на входе переключателя 1 импульс второго разряда последовательного двоичного кода через элемент 24 поступает на вход линии 17

задержки, с первых двух отводов которой сниМаЬтся два параллельно-последовательных импульса и поступают на элемент 11, с выхода которого два последовательных импульса через элемента 3 поступают на счетный вход

счетчика 18 для заполнения первой декады счетчика 18.

Третий тактовый импульс перебрасывает переключатель 1 со второго положения на третье. С третьего вывода

переключателя 1 снимается напряжение с разрешения на элемент 4. На остальные элементы И выдается запрет. Одновременно с третьим тактовым импульсов на входе переключателя 1 импульс третьего разряда последовательного двоичного кода через элемент 24 поступает на вход линии 17 задержки, с первых четырех отводов которойсни.маются четыре параллельно-последовательных импульса и поступают на элемент 12, с выхода koTOpbro четыре последовательных импульса через элемент 4 поступают на счетный вход счетчика 18 для заполнения первой декады счетчика 18.

Четвертый тактовый импульс перебрасывает пер еключатёль 1 с третьего положения в четвертое. С четвертого выхода переключателя 1 снимается напряжение разрешения на элемент 5. На

остальные элементы И выдается запрет. Одновременно с четвертью такто вым импульсом импульс четвертого раз ряда последовательного двоичного код иереэ элемент 24 поступает на вход линии 17 задержки, с первых восьми отводов которой подаются восемь параллельно-последовательных импульсов на входы элемента 13. С выхода элемента 13 восемь последовательных импульсов через элемент 5 поступают на счетный вход первой декады счетчика 18 для ее заполнения. Пятый тактовый импульс перебрасывает переключатель 1 с четвертого по ложения на пятое. С пятого вывода пе реключателя 1 снимается напряжение разрешения на элементы б и 7. На остальные элементы выдается запрет. Одновременно с пятым тактовым импуль сов импульсы пятого разряда последовательного двоичного кода через элемент 24 поступают на вход линии 17 задержки. Сначала с первых шести отводов линии 17 задержки шесть параллельнопоследовательных импульсов через эле мент б подаются на счетный вход первой декады счетчика 18 для ее заполнения, затем с седьмого отвода линии 17 задержки через элемент 7 один импульс поступает на счетный вход вт рой декады с сетчика 18 для его заполнения. Преобразование шестого и седьмого разрядов последовательного двоичного кода в код десятичный аналогично пре образованию пятого разряда кода. Восьмой тактовый импульс перебрасывает переключатель 1 с седьмого положения на восьмое. С восьмого выхода переключателя 1 снимается напряжение разрешения на элементы 8, 9и 10. На остальные элементы И выдается запрет. Одновременно с восьмым тактовым импульсом импульс восьмого разряда через элемент 24 поступает на вход линии 17 задержки. С первых восьми отводов линии 17 задержки восемь параллельно-последовательных импульсов подаются на входы элемента 15, с выхода которого восемь последовательных импульсов чв рез элемент 8 подаются на счетный вход первой декады счетчика 18 для ее заполнения, затем с девятого и десятого отводов линии 17 задержки два параллельно-последовательных импульса поступают на входы элемента 1 с выхода которого два последова- тельнь1х импульса через элемент 9 подаются на счетный вход второй декад счетчика 18 для ее заполнения. В последнюю очередь с одиннадцатого отвода линии 17 задержки через элемент 10один импульс поступает на счетный вход третьей декащы счетчика 18 для ее заполнения. J Девятый, десятый и т.д. разряды оследовательного двоичного кода пре- бразуются в код десятичный аналогично преобразованию восьмого разряа кода. После преобразования последнего разряда (п-разрядного входного слова) последовательного двоичного кода в код десятичный, переключатель 1 переходит в нулевое (исходное) положение, на все элементы И вьщается запрет и содержимое счетчика 18 принимает значение в десятичном виде, соответствующее значению преобразованного входного двоичного кода (значение п-разрядного входного слова). При приходе первого тактового имПульса, синхронного с первым разрядом монотонно изменяющегося последо- /вательного входного двоичного кода (последующего п-разрядного слова), описанный вьше процесс повторяется. Ограниче.нием для линии задержки при формировании фиксированного числа параллельно-последовательных импульсов является то, что время формирования указанных импульсов с учетом задержки вспомогательного элемента задержки tg должно быть меньше или равно периоду следования тактовых импульсов. T-i, 6 Т нТаким образом, преобразование монотонно изменякмцегося последовательного двоичного кода в код десятичный осуществляется в период между п-разрядными словами входного двоичного кода, а добавление единицы при монотонно воэрастающем коде (или уменьшение на единицу при монотонно убывающем коде) к значению счетчика 18 и запись в регистр 22 эквивалентного кода осуществляется в момент прихода первого тактового импульса, синхронного с первым разрядом последующего п-разрядного входного слова. Таким образом исключается временная задержки в преобразовании монотонно изменяющегося последовательного двоичного кода в код десятичный, возникающая за счет времени преобразован.ия всей последовательности кодовых импульсов п-разрядного слова. Управление декадным ьчетчиком для работы с монотонно возрастающим или монотонно убываХ)Щим входным кодом осуществляется внешним сигналом Управление, поступающим на вход счетчика 18. Использование предлагаемого устройства преобразования последоват льного двоичного кода в код десятичный позволяет полностью исключить временную задержку в преобразовании монотонно изменяющегося последовательного двоичногокода в код десятичный, определяемую количеством разрядов в слове и тактовой частотой следования кодовых импульсов, так как преобразование кода производится впериод словами п-разрядного входного хода, а смен содержимого кода выход ного регистра производится в момент прихода первого тактового импульса, синхронного с первым разрядом входного слова, с предварительным прибавлением (вычитанием) единицы к значению кода декадного счетчика; полностью исключить зависимость времени преобразования кода от значения входного кода, так как временная задержка в преобразований кода постоянна и определяется временем формирования импульсов первым и вторым формирователем; использовать предлагаемое устройство в аппаратуре обработки информации с представлением кодовой информации в единой шкале времени.

Формула изобретения

Устройство преобразования последозательного двоичного кода в код десятичный по авт.св. 403058, о т

личающеесЯ тем, что, с це

лью повышения быстродействия, в него введены регистр, формирователь по- следовательного кода, последовательно соединенные формирователиимпульсов, вход первого из которых соединен с первым выходом переключателя, а выход - со счетным входом декадного счетчика импульсов, выход второго формирователя .импульсов - с управляющим входом регистра, третьего - с управляющим входом формирователя последовательного кода и входом установки в нуль декадного счетчика импульсов, выходы которого соединены со входами регистра, выходы которого являются выходами параллельного кода и

5 соединены со входами формирователя последовательного кода, выход которого является выходом последовательного кода, и элемент задержки, вход которого соединен с информационной шиной, а выход - со входом линии задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 403058, кл. Н 03 К 13/24, 18.03.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ | 1971 |

|

SU432486A1 |

| Преобразователь перемещения в код | 1982 |

|

SU1043701A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых величин | 1987 |

|

SU1476616A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Устройство для декодирования кодов представленных в системе остаточных классов | 1973 |

|

SU506850A1 |

| Цифровая система индикации времени | 1979 |

|

SU792210A1 |

Авторы

Даты

1980-11-23—Публикация

1978-12-12—Подача