Изобретение относится к контрольно-измерительной технике, в частности к контролю параметров цифровых интегральных схем.

Известен способ контроля нагрузочной способности пороговых логических схем и их классификации путем подачи входных воздействий и измерения выходных параметров. При иодаче на выход контролируемой схемы напряжения, заданного для данного типа схем уровня, и измерении установившегося при этом нагрузочного тока возникает опасность выхода из строя проверяемых схем за счет возможной токовой перегрузки.

Цель изобретения - повысить эффективность контроля.

Это достигается тем, что в выходную цепь контролируемой схемы задают линейно возрастающий нагрузочный ГОК и фиксируют его величину при достижении выходным напряжением заданного норогового уровня.

При определении нагрузочной снособности схем предлагаемым способом нагрузочный ток не может превысить уровня, реально донустимого для каждой нроверяемой схемы, так как рост тока прекращается при достижении выходным напряжением заданного уровня, что исключает возможность токовых перегрузок для лучщих экземпляров проверяемых схем. Описываемый способ позволяет также с большей точностью классифицировать проверяемые с.хемы на группы по нагрузочной снособности, а таже упрощает реализацию устройств контроля за счет того, что технически измерение одного потепниала с высокой

точностью значительно прош,е, чем задание нескольких контрольных наирял еиий также с высокой точностью при значительном токе нагрузкн.

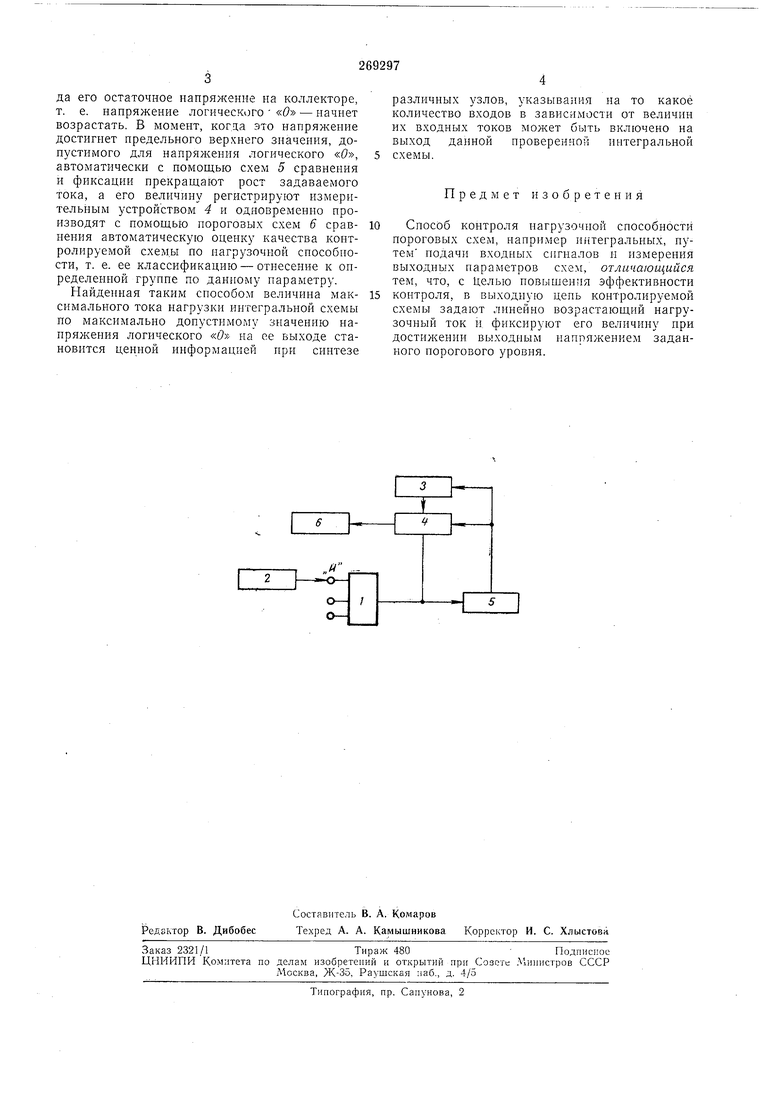

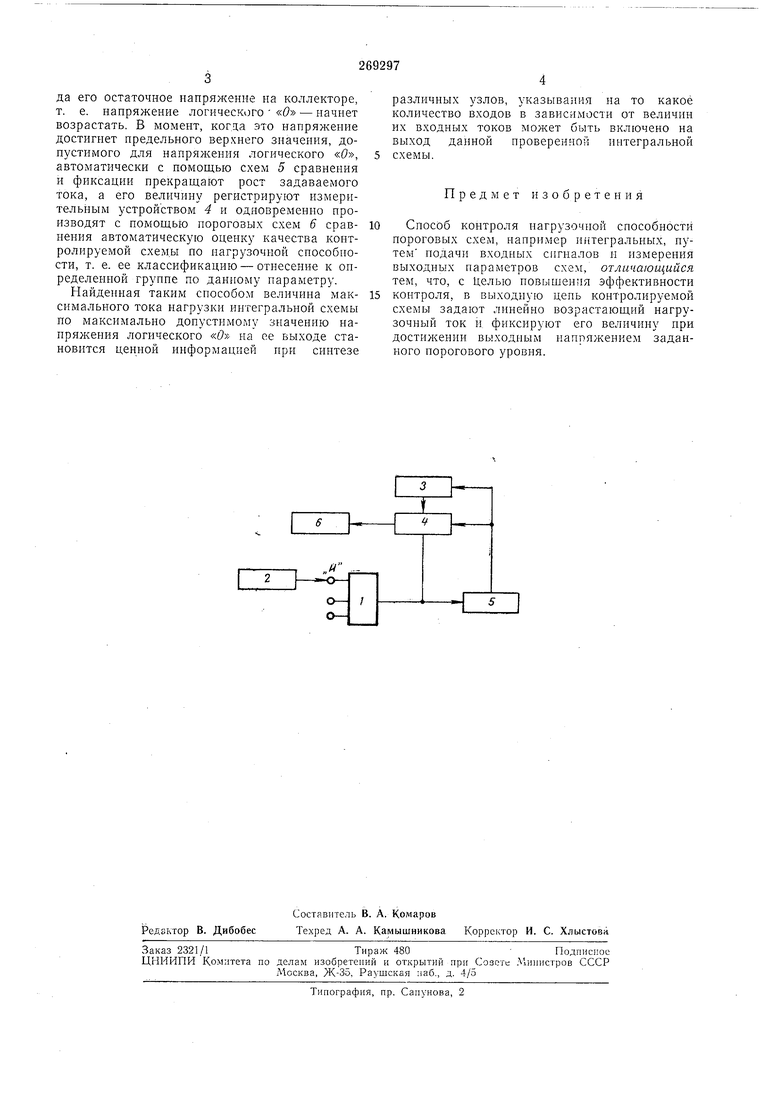

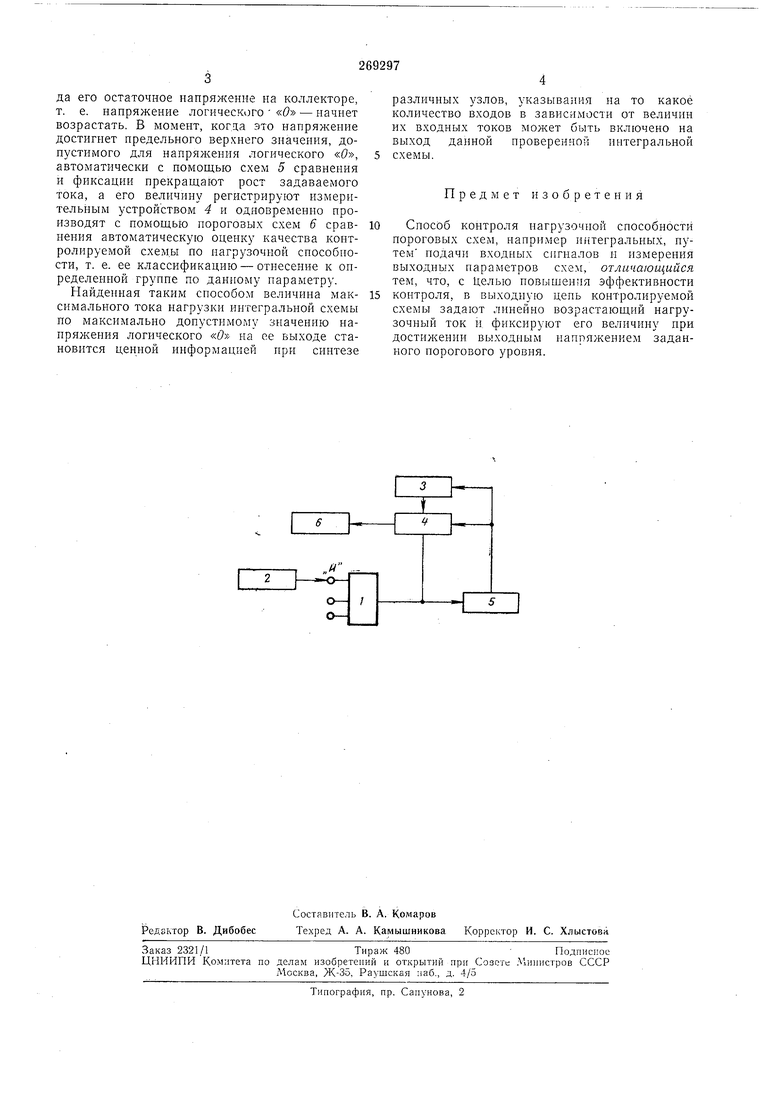

На чертеже дана схема реализации нредлагаемого способа проверки пороговых схем, например цнфровых интегральных микросхем «И-НЕ типов ДТЛ и ТТЛ.

На вход «Я интегральной схемы / из задатчика входных сигналов 2 подают снгнал

логической «, при этом на выходе проверяемой схемы будет сигнал логического «О, определяемый остаточным напрял ением участка коллектор-эмиттер выходного транзистора. Если теперь в коллекторную цепь открытого транзистора от отдельного источника 3 через измерительное устройство 4 задавать возрастающий ток (аналогично тому, как через этот транзистор протекают входные токн других интегральных схем, при включеннн их

входов на выход данной интегральной схемы), то базовый ток выходного транзистора нрн имеющемся у него коэффициенте усиления и при определенной величине выходного тока, окажется недостаточным для удержания

да его остаточное напряжение на коллекторе, т. е. напряжение логического «О - начнет возрастать. В момент, когда это напряженне достигнет предельного верхнего значения, допустимого для напряжения логического «О, автоматически с помощью схем 5 сравнения и фиксации прекращают рост задаваемого тока, а его величину регистрируют измерительным устройством 4 и одновременно производят с помощью пороговых схем 6 сравнения автоматическую оценку качества контролируемой схемь но нагрузочной способности, т. е. ее классификацию - отнесение к онределенной грунне по данному параметру.

Найденная таким способом величина максимального тока нагрузки интегральной схемы по максимально допустимо1му значению напряжения логического «б на ее выходе становится ценной информацией при синтезе

различных узлов, указЕЯвания на то какое количество входов в зависимости от величин их входных токов может быть включено на выход данной проверенной интегральной схемы.

Предмет изобретения

Способ контроля нагрузочной способности пороговых схем, например интегральных, путем подачи входных сигналов и измерения выходных параметров схем, отличающийся тем, что, с Целью повышения эффективности контроля, в выходную цепь контролируемой схемы задают линейно возрастающий нагрузочный ток и фиксируют его величину при достижении выходным напряжением заданного норогового уровня.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для КОНТРОЛЯ НАГРУЗОЧНОЙ СНОСОБНОСТИ ПОРОГОВЫХ СХЕМ | 1970 |

|

SU266945A1 |

| УСТРОЙСТВО Д,ЛЯ КОНТРОЛЯ ПОРОГОВЫХ-^УРбВНЁЙ ПОЛУПРОВОДНИКОВЫХ ЛОГИЧЕСКИХ СХЕМ | 1970 |

|

SU266943A1 |

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1605238A1 |

| Способ контроля ТТЛ итегральных схем | 1989 |

|

SU1675804A1 |

| ВСЕСОЮЗНАЯ ;П::Тг:гп10-1Ехн';-п^пр!'^'- 'ib;!:'!V.J . L i'i АI | 1971 |

|

SU293296A1 |

| СПОСОБ КОНТРОЛЯ КАЧЕСТВА СОЕДИНЕНИЙ ЦИФРОВЫХ КМОП-УСТРОЙСТВ | 2000 |

|

RU2199129C2 |

| Токовое пороговое устройство | 1983 |

|

SU1251018A1 |

| ИНТЕГРАЛЬНЫЙ ГРАДИЕНТНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ДАТЧИК | 2010 |

|

RU2453947C2 |

| Устройство для контроля параметровиНТЕгРАльНыХ CXEM | 1972 |

|

SU802965A1 |

Даты

1970-01-01—Публикация