:д

N5

X)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ С ЗАЩИТОЙ | 1990 |

|

RU2011258C1 |

| Управляемый формирователь импульсов | 1988 |

|

SU1596441A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| УСТРОЙСТВО ВИБРАЦИОННОГО КОНТРОЛЯ (ВАРИАНТЫ) | 2008 |

|

RU2375692C1 |

| УСТРОЙСТВО ДЛЯ ВИБРАЦИОННОГО КОНТРОЛЯ (ВАРИАНТЫ) | 2008 |

|

RU2376564C1 |

| Устройство для контроля напряжения электропитания | 1991 |

|

SU1784982A1 |

| Устройство для контроля сопротивления изоляции сети постоянного тока | 1990 |

|

SU1774284A1 |

| Устройство автоматического контроля и отбраковки резисторов | 1987 |

|

SU1531026A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля цифровых блоков. Цель изобретения - повышение достоверности контроля цифровых блоков. Устройство содержит генератор тестов, блок нагрузок, формирователь граничных уровней, два пороговых элемента, элемент И-НЕ, мультиплексор результата, аналоговый мультиплексор, формирователь граничных импульсных воздействий, элемент НЕ. С помощью устройства проверяется динамическая устойчивость контролируемого цифрового блока на помехоустойчивость за счет того, что входные сигналы на контролируемый блок со средним значением уровней лог."0" и лог."1" промодулированы импульсами с граничными значениями уровней лог."0" и лог."1". В условиях реальной эксплуатации цифровых блоков уровни входных сигналов, как правило, соответствуют средним значениям, поэтому, если в результате контроля входные элементы проверяемого блока оказываются работоспособными при импульсных помехах, соответствующих наихудшим уровням входных сигналов, это гарантирует их работоспособность во всем диапазоне уровней входных сигналов. Производится также измерение уровней выходных сигналов проверяемого блока и отображение их на экране осциллографа совместно с их допусками, граничными уровнями и состоянием сбоя, что позволяет быстро отыскать место неисправности. 1 з.п.ф-лы, 1 табл., 5 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля цифровых блоков.

Цель изобретения - повьппение достоверности контроля цифровых блоков за счет обеспечения контроля входными сигналами с дополнительными им- пульса -га, имеющими граничное значение амплитуды на входных контактах.

и проверки соответствия логических

уровней.

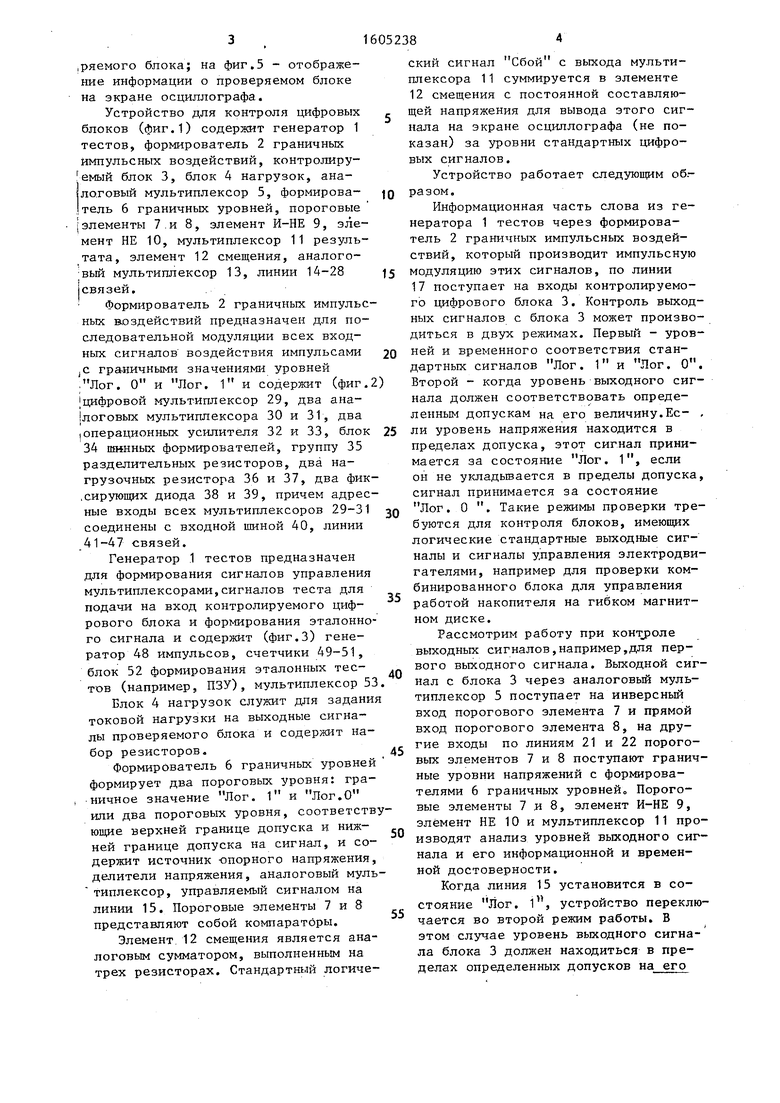

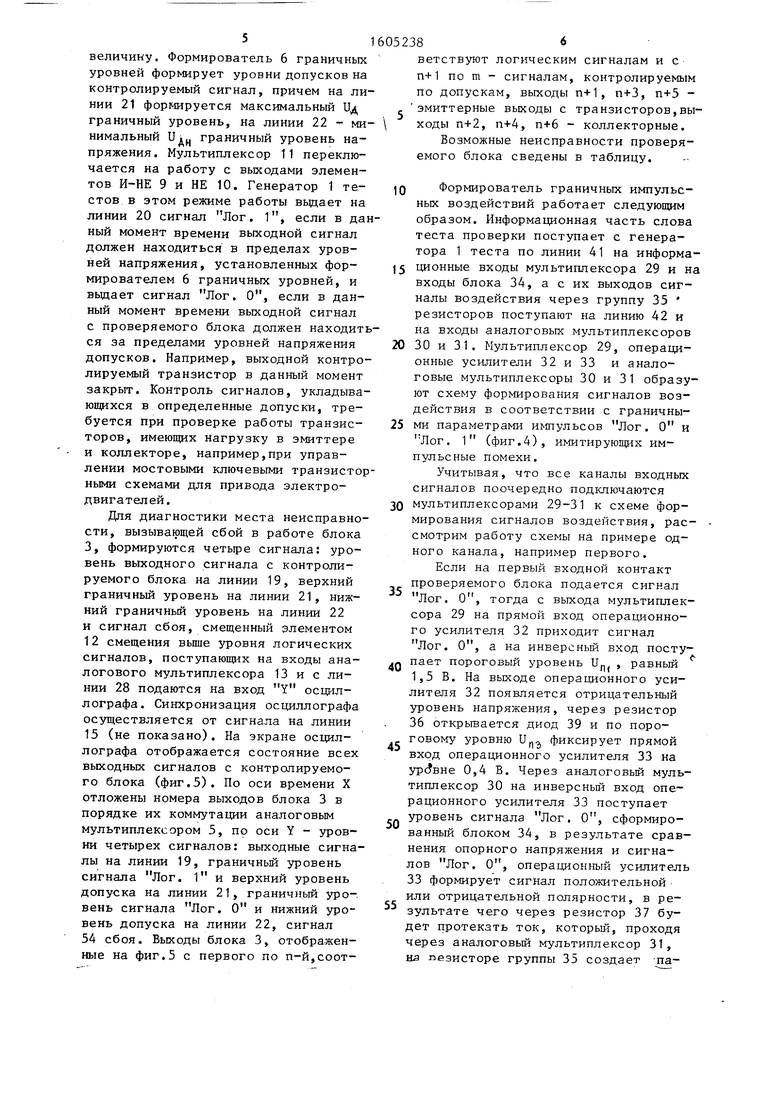

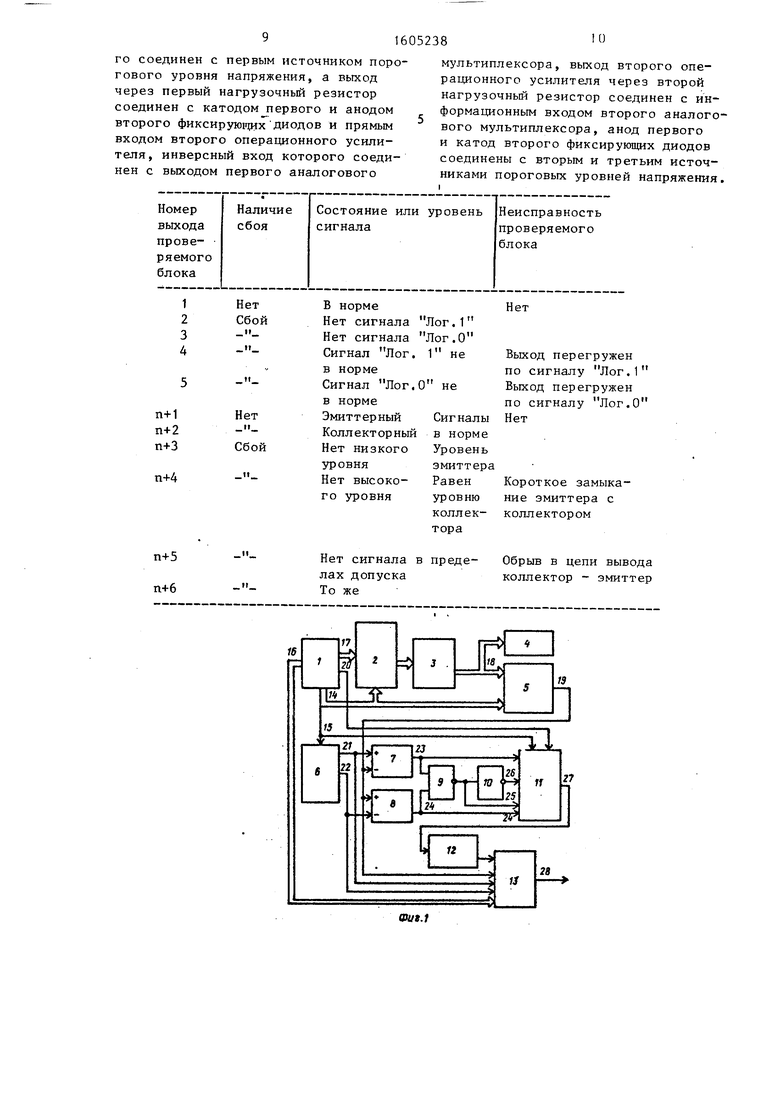

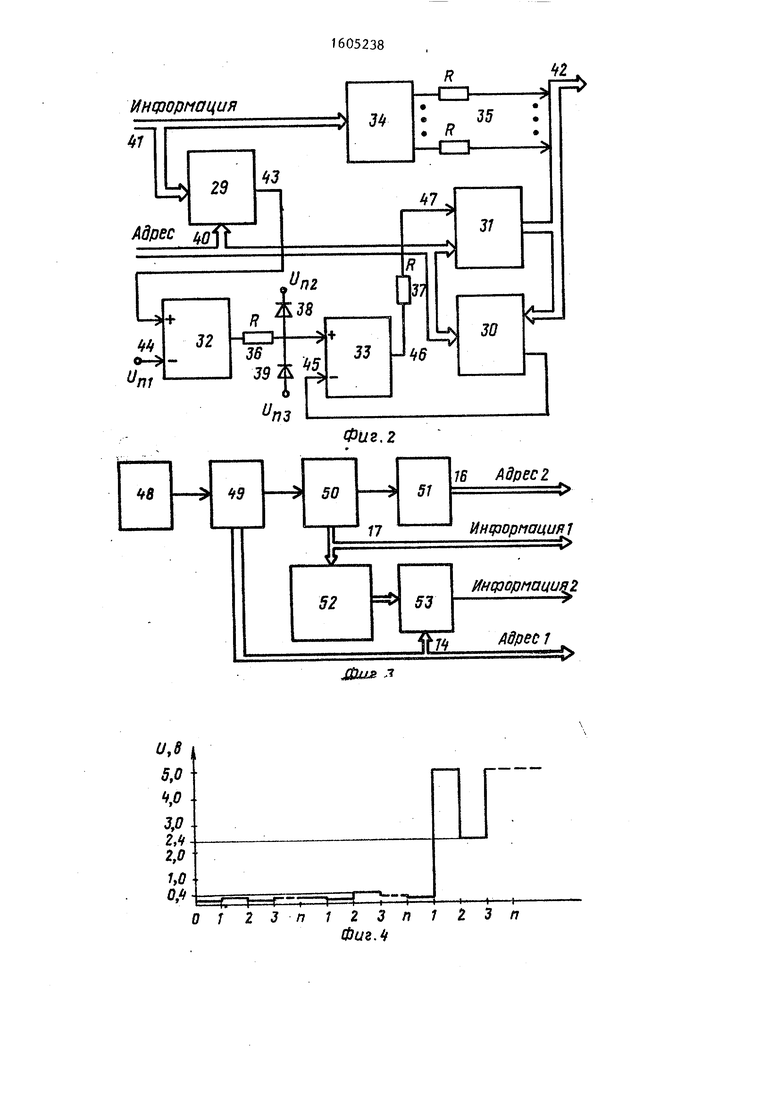

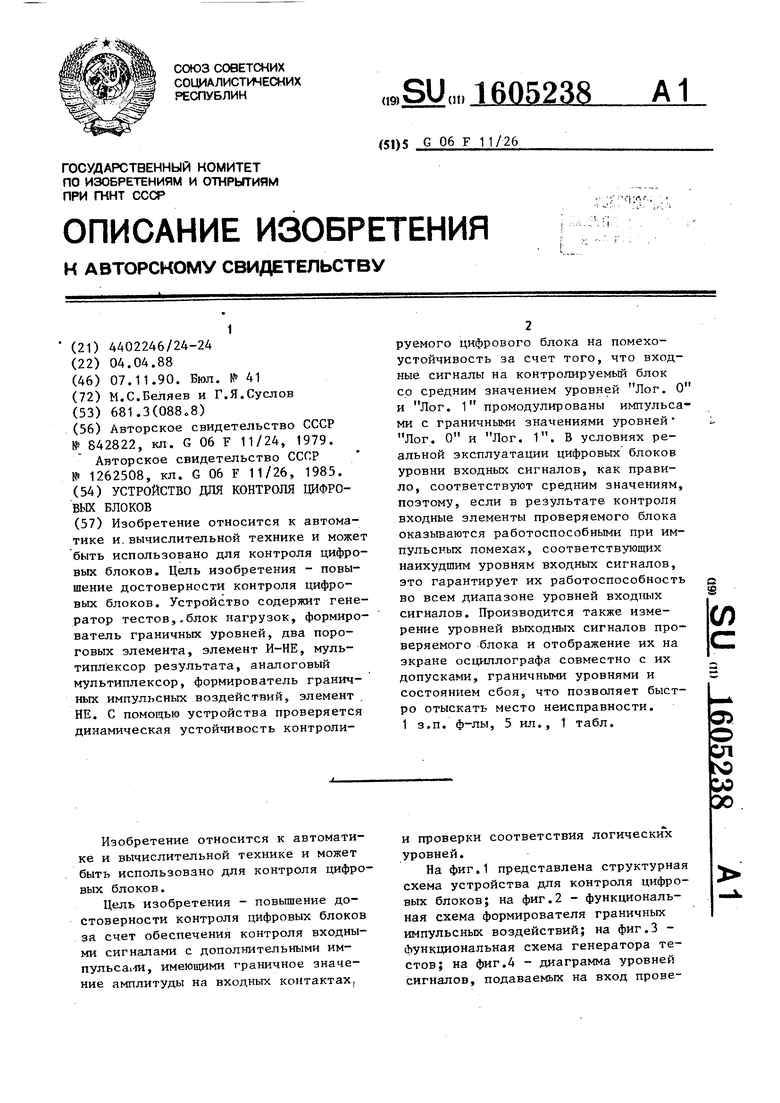

На фиг.1 представлена структурная схема устройства для контроля цифровых блоков; на фиг.2 - функциональная схема формирователя граничных импульсных воздействий; на фиг.З - функциональная схема генератора тестов; на фиг.4 - диаграмма уровней сигналов, подаваемых на вход прове10

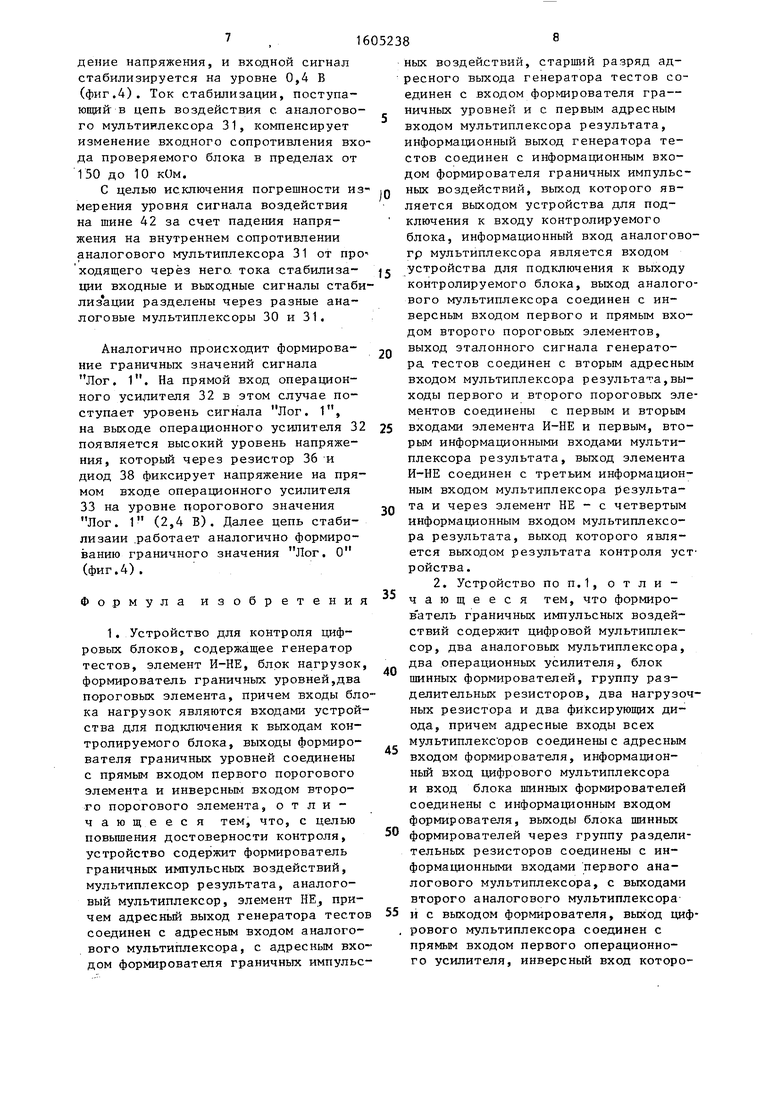

ряемого блока; на фиг.5 - отображение информации о проверяемом блоке на экране осциллографа.

Устройство для контроля цифровых блоков (фиг.1) содержит генератор 1 тестов, формирователь 2 граничных импульсных воздействий, контролируемый блок 3, блок 4 нагрузок, аналоговый мультиплексор 5, формирователь 6 граничных уровней, пороговые

элементы 7.и 8, элемент И-НЕ 9, элемент НЕ 10, мультиплексор 11 результата, элемент 12 смещения, аналоговьш мультиплексор 13, линии 14-28

связей.

Формирователь 2 граничных импульсных тоздействий предназначен для последовательной модуляции всех входных сигналов воздействия импульсами 20

с градичными значениями уровней

25

30

Лог. О и Лог. 1 и содержит (фиг.2) цифровой мультиплексор 29, два ана- логовых мультиплексора 30 и 31, два операционных усилителя 32 и 33, блок 34 шинных формирователей, группу 35 разделительных резисторов, два нагрузочных резистора 36 и 37, два фик- .сирующих диода 38 и 39, причем адресные входы всех мультиплексоров 29-31 соединены с входной шиной 40, линии 41-47 связей.

Генератор 1 тестов предназначен для формирования сигналов управления мультиплексорами,сигналов теста для подачи на вход контролируемого цифрового блока и формирования эталонного сигнала и содержит (фиг.З) генератор 48 импульсов, счетчики 49-51, блок 52 формирования эталонных тестов (например, ПЗУ), мультиплексор 53, Блок 4 нагрузок служит для задания токовой нагрузки на выходные сигналы проверяемого блока и содержит набор резисторов.

Формирователь 6 граничных уровней формирует два пороговых уровня: гра- ничное значение Лог. 1 и Лог.О или два пороговых уровня, соответствующие верхней границе допуска и ниж- ней границе допуска на сигнал, и содержит источник -опорного напряжения, делители напряжения, аналоговый муль- типлексор, управляемый сигналом на линии 15. Пороговые элементы 7 и 8 представляют собой компараторы.

Элемент 12 смещения является аналоговым сумматором, выполненньм на трех резисторах. Стандартшлй логиче15

35

40

45

55

10

20

25

30

2) -

3, я й- ву, ь-

6052384

ский сигнал Сбой с выхода мультиплексора 11 суммируется в элементе 12 смещения с постоянной составляющей напряжения для вывода этого сигнала на экране осциллографа (не показан) за уровни стандартных цифровых сигналов.

Устройство работает следующим образом.

Информационная часть слова из генератора 1 тестов через формирователь 2 граничных импульсных воздействий, который производит импульсную модуляцию этих сигналов, по линии 17 поступает на входы контролируемого цифрового блока 3. Контроль выходных сигналов с блока 3 может производиться в двух режимах. Первый - уровней и временного соответствия стандартных сигналов Лог. 1 и Лог. О. Второй - когда уровень выходного сигнала должен соответствовать определенным допускам на его величину.Ее- , ли уровень напряжения находится в пределах допуска, этот сигнал прини15

35

40

45

55

мается за состояние Лог. 1, если он не укладьшается в пределы допуска, сигнал принимается за состояние Лог. О . Такие режимы проверки требуются для контроля блоков, имеющих логические стандартные выходные сигналы и сигналы управления электродвигателями, например для проверки комбинированного блока для управления работой накопителя на гибком магнитном диске.

Рассмотрим работу при контроле выходных сигналов,например,для первого выходного сигнала. Выходной сигнал с блока 3 через аналоговьй мультиплексор 5 поступает на инверсный вход порогового элемента 7 и прямой вход порогового элемента 8, на другие входы по линиям 21 и 22 пороговых элементов 7 и 8 поступают граничные уровни напряжений с формирователями 6 граничных уровней. Пороговые элементы 7 и 8, элемент И-НЕ 9, элемент НЕ 10 и мультиплексор 11 производят анализ уровней выходного сигнала и его информационной и временной достоверности.

Когда линия 15 установится в состояние Jior. 1, устройство переключается во второй режим работы. В этом случае уровень выходного сигнала блока 3 должен находиться в пределах определенных допусков на его

5

величину. Формирователь 6 граничных уровней формирует уровни допусков на контролируемый сигнал, причем на линии 21 формируется максимальный Цд граничный уровень, на линии 22 - минимальный Цд граничный уровень напряжения. Мультиплексор 11 переключается на работу с выходами элементов И-НЕ 9 и НЕ 10. Генератор 1 тестов в этом режиме работы вьщает на линии 20 сигнал Лог. 1, если в даный момент времени выходной сигнал должен находиться в пределах уровней напряжения, установленных формирователем 6 граничных уровней, и выдает сигнал Лог. О, если в данный момент времени выходной сигнал с проверяемого блока должен находится за пределами уровней напряжения допусков. Например, выходной контролируемый транзистор в данный момент закрыт. Контроль сигналов, укладывающихся в определенные допуски, требуется при проверке работы транзисторов, имеющих нагрузку в эмиттере и коллекторе, например,при управлении мостовыми ключевыми транзисторными схемами для привода электродвигателей.

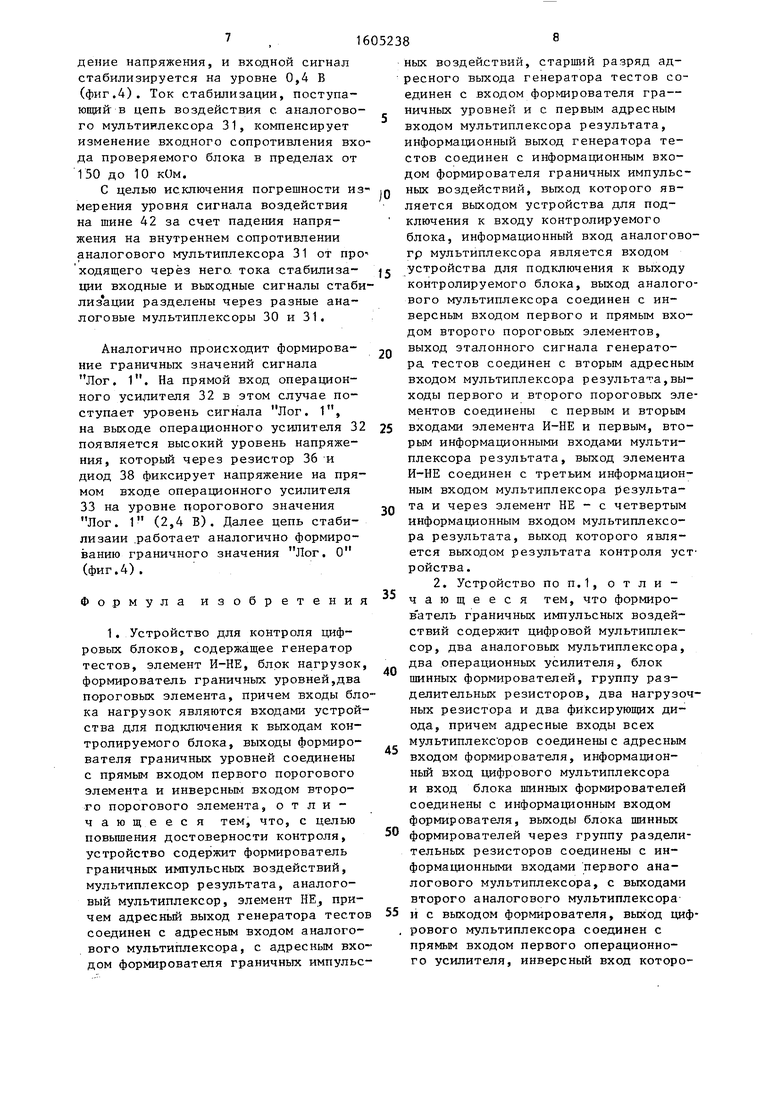

Для диагностики места неисправности, вызывающей сбой в работе блока 3, формируются четыре сигнала: уровень выходного сигнала с контролируемого блока на линии 19, верхний граничный уровень на линии 21, нижний граничный уровень на линии 22 и сигнал сбоя, смещенный элементом 12 смещения вьше уровня логических сигналов, поступающих на входы аналогового мультиплексора 13 и с линии 28 подаются на вход Y осциллографа. Синхронизация осциллографа осуществляется от сигнала на линии 15 (не показано). На экране осциллографа отображается состояние всех выходных сигналов с контролируемого блока (фиг.5). По оси времени X отложены номера выходов блока 3 в порядке их коммутации аналоговым мультиплексором 5, по оси Y - уровни четырех сигналов: выходные сигналы на линии 19, граничньй зфовень сигнала Лог. 1 и верхний уровень допуска на линии 21, граничный уровень сигнала Лог. О и нижний уровень допуска на линии 22, сигнал 54 сбоя. Выходы блока 3, отображенные на фиг.5 с первого по п-й,соот052386

ветствуют логическим сигналам и с п+1 по m - сигналам, контролируемым по допускам, выходы п+1, п+3, п+5 - с эмиттерные выходы с транзисторов,вы- ходы п+2, п+4, п+6 - коллекторные.

Возможные неисправности проверяемого блока сведены в таблицу.

10 Формирователь граничных импульсных воздействий работает следующим образом. Информационная часть слова теста проверки поступает с генератора 1 теста по линии 41 на информа 5 ционные входы мультиплексора 29 и на входы блока 34, а с их выходов сигналы воздействия через группу 35 резисторов поступают на линию 42 и на входы аналоговых мультиплексоров

20 30 и 31. Мультиплексор 29, операционные усилители 32 и 33 и аналоговые мультиплексоры 30 и 31 образуют схему формирования сигналов воздействия в соответствии с граничны25 ми параметрами и myльcoв Лог. О и Лог. 1 (фиг.4), имитирующ11х импульсные помехи.

Учитывая, что все каналы входных сигналов поочередно подключаются

30 мультиплексорами 29-31 к схеме формирования сигналов воздействия, рассмотрим работу схемы на примере одного канала, например первого.

Если на первый входной контакт проверяемого блока подается сигнал Лог. О, тогда с выхода мультиплексора 29 на прямой вход операционного усилителя 32 приходит сигнал

40

Лог. О, а на инверсньй вход поступает пороговый уровень U., , равный

1,5 В. На выходе операционного усилителя 32 появляется отрицательный Зфовень напряжения, через резистор 36 открьгоается диод 39 и по поро- - говому уровню , фиксирует прямой вход операционного усилителя 33 на 0,4 В. Через аналоговьм мультиплексор 30 на инверсный вход операционного усилителя 33 поступает уровень сигнала Лог. О, сформированный блоком 34, в результате сравнения опорного напряжения и сигналов Лог. О, операционный усилитель 33 формирует сигнал положительной . или отрицательной полярности, в результате чего через резистор 37 будет протекать ток, который, проходя через аналоговый мультиплексор 31, на пезисторе группы 35 создает -па50

дение напряжения, и входной сигнал стабилизируется на уровне 0,4 В (фиг.4). Ток стабилизации, поступающий в цепь воздействия с аналогового мультиплексора 31, компенсирует изменение входного сопротивления входа проверяемого блока в пределах от 150 до 10 кОм.

С целью исключения погрешности измерения уровня сигнала воздействия на шине 42 за счет падения напряжения на внутреннем сопротивлении аналогового мультиплексора 31 от про ходящего через него, тока стабилизации входные и выходные сигналы стаби лиз ации разделены через разные аналоговые мультиплексоры 30 и 31.

Аналогично происходит формирование граничных значений сигнала Лог. 1. На прямой вход операционного усилителя 32 в этом случае поступает уровень сигнала Лог. 1, на выходе операционного усилителя 32 появляется высокий уровень напряжения, которьй через резистор 36 и диод 38 фиксирует напряжение на прямом входе операционного усилителя 33 на уровне порогового значения Лог. 1 (2,4 В). Далее цепь стаби- лизаии .работает аналогично формированию граничного значения Лог. О (фиг.4).

Формула изобретения

0

15

605238

ных воздействий, старший разряд ад- ресного выхода генератора тестов соединен с входом формирователя гра- ничных уровней и с первым адресным входом мультиплексора результата, информационный выход генератора тестов соединен с информационным входом формирователя граничных импульсных воздействий, выход которого является выходом устройства для подключения к входу контролируемого блока, информационный вход аналогово- гр мультиплексора является входом устройства для подключения к выходу контролируемого блока, выход аналогового мультиплексора соединен с инверсным входом первого и прямым входом второго пороговых элементов, выход эталонного сигнала генератора тестов соединен с вторым адресным входом мультиплексора результата,выходы первого и второго пороговых элементов соединены с первым и вторым входами элемента И-НЕ и первым, вторым информационными входами мультиплексора результата, выход элемента И-НЕ соединен с третьим информационным входом мультиплексора результата и через элемент НЕ - с четвертым информационным входом мультиплексора результата, выход которого является выходом результата контроля устройства.

25

30

, в35

40

45

50

55

чающееся тем, что формиро- в атель граничных импульсных воздействий содержит цифровой мультиплексор, два аналоговых мультиплексора, два операционных усилителя, блок шинных формирователей, группу разделительных резисторов, два нагрузочных резистора и два фиксирующих диода, причем адресные входы всех мультиплекс оров соединены с адресным входом формирователя, информацион- ньй вход цифрового мультиплексора и вход блока шинных формирователей соединены с информационным входом формирователя, выходы блока шинных формирователей через группу разделительных резисторов соединены с информационными входами первого аналогового мультиплексора, с выходами второго аналогового мультиплексора и с выходом формирователя, выход цифрового мультиплексора соединен с прямым входом первого операционного усилителя, инверсный вход которого соединен с первым источником порогового уровня напряжения, а выход через первый нагрузочный резистор соединен с катодом первого и анодом второго фиксирую1цих диодов и прямым входом второго операционного усилителя, инверсный вход которого соединен с выходом первого аналогового

мультиплексора, выход второго операционного усилителя через второй нагрузочный резистор соединен с информационным входом второго аналогового мультиплексора, анод первого и катод второго фиксирующих диодов соединены с вторым и третьим источниками пороговых уровней напряжения.

и

Т Г

;7J L

Фиг,2

л

ОГ23п123п123п

Фиг.

R

Фаг. 5

| Устройство для контроля цифровыхузлОВ | 1979 |

|

SU842822A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для контроля цифровых узлов | 1985 |

|

SU1262508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-04-04—Подача