Предложение относится к области вычислительной техиики.

Известны синхронизаторы на ферротранзисторных элементах, в которых используется принцип работы, основанный на преобладании или превышении уровня записи над уровнем считывания, строящиеся на специальных ячейках с увеличенными витковыми данными, которые накладывают жесткие требования на параметры перемагничивающих импульсов, что значительно усложняет генераторы продвигающих (тактовых) импульсов.

Подобные схемы необходимы для систем с одновременным запретом, но их применение в системах с разновременным запретом неоправданно.

Цель предложения - упростить схему синхронизатора, выполнив ее на типовых ферротранзисторных элемента.х системы с разновременным запретом, и тем самым повысить надежность всего устройства в целом.

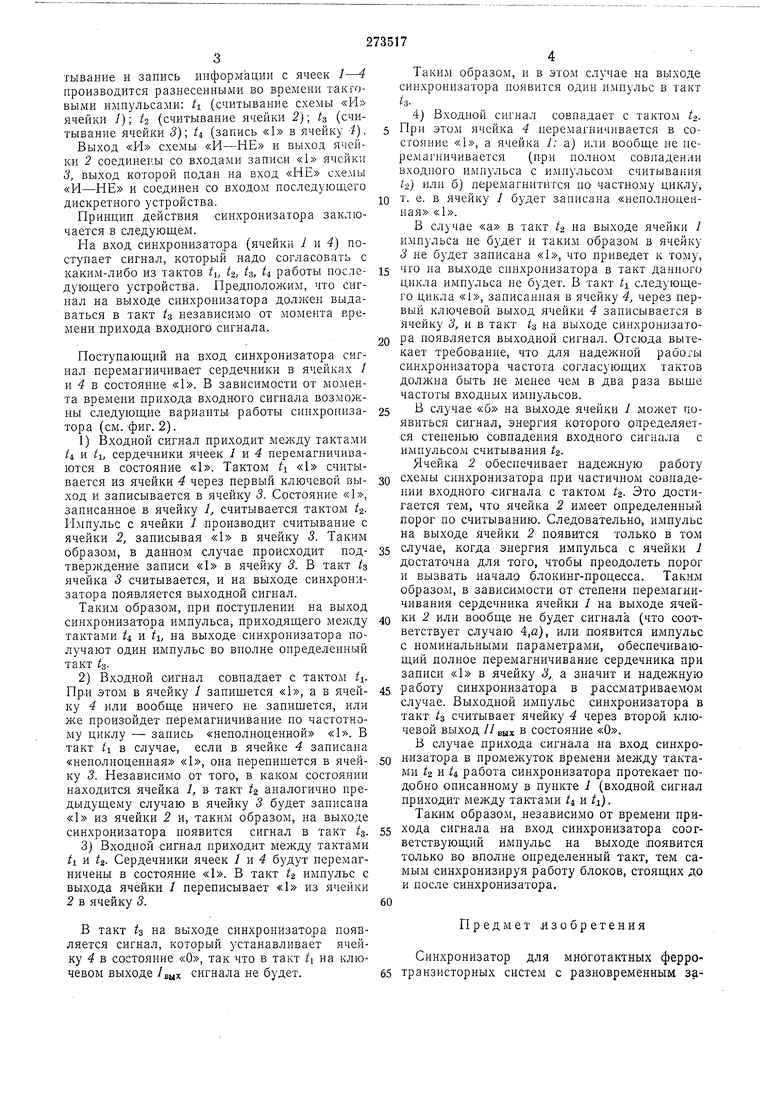

Предлагаемый синхронизатор построен, как и известные, на трех типовых ячейках памяти с положительной обратной связью и схеме «И-НЕ, причем в отличие от известных входы схемы «И-НЕ, первой и третьей ячеек памяти и вход записи второй ячейки памяти подключены к источникам синхронизирующих тактовых импульсов, выход «И схемы «И- НЕ соединен со входом записи третьей ячей-- . , 2- ,/

ки памяти, выход первой яч-ещу г/одключеи ко входу считывания второй ячешчи. выход второй ячейки соединен со вторым входом ла писи третьей ячейки, а выход третьей ячейки подключен ко входу «НЕ схемы «II-НН и входу многотактиой системы.

Отличительным свойством предложенного синхронизатора является принцип построения схемы с нспользование.м порога срабатывания

ло считыванию ферротранзисторных ячеек с положительной обратной связью и сопротивление.м в цени эмиттера, у которых имихльс ia выходе ячейки будет иметь место лишь в гом случае, еслн энергия импульса считывания достаточна для преодоления порога срабатыв;;ння, параметры же нмпульса на выходе лче|Ь ки не зависят от пара.метров имнульга счпт.лвания.

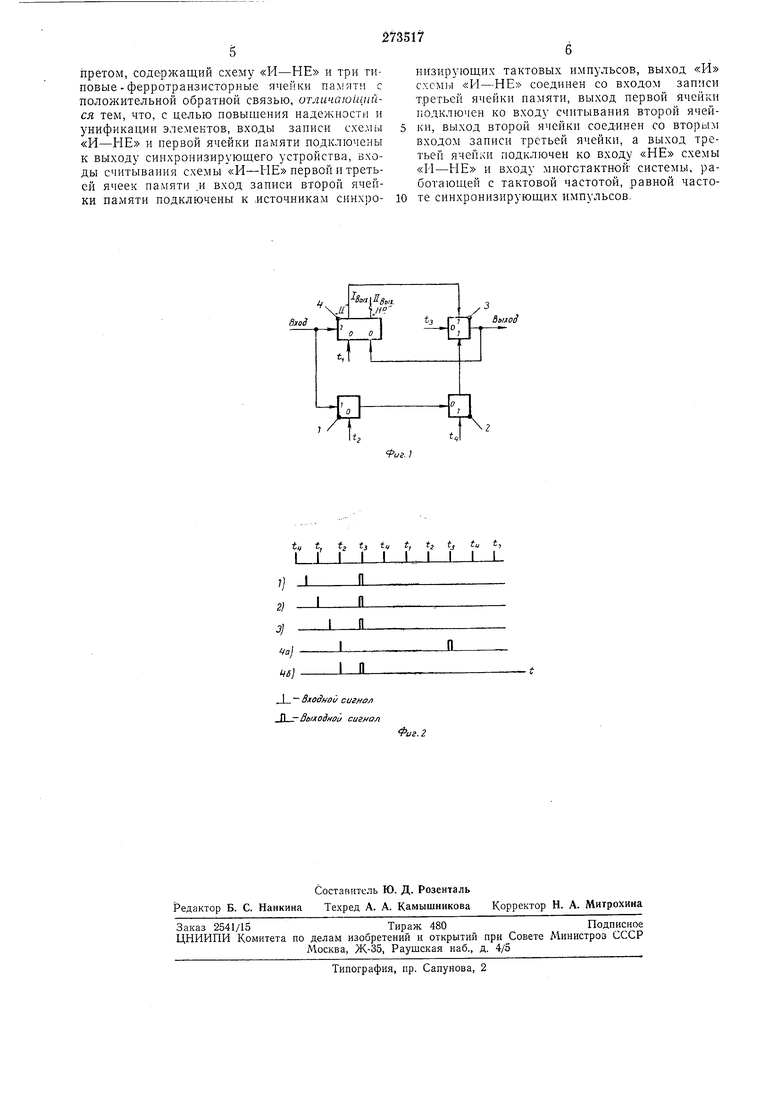

Схема синхронизатора нрелставлена

фиг. 1 и содержит ферротраизисторные памяти /; 2 и 3 с положительной обрат Г)ч связью и сопротивлением в цепи эмиттера., п схему «И-НЕ (ячейка 4).

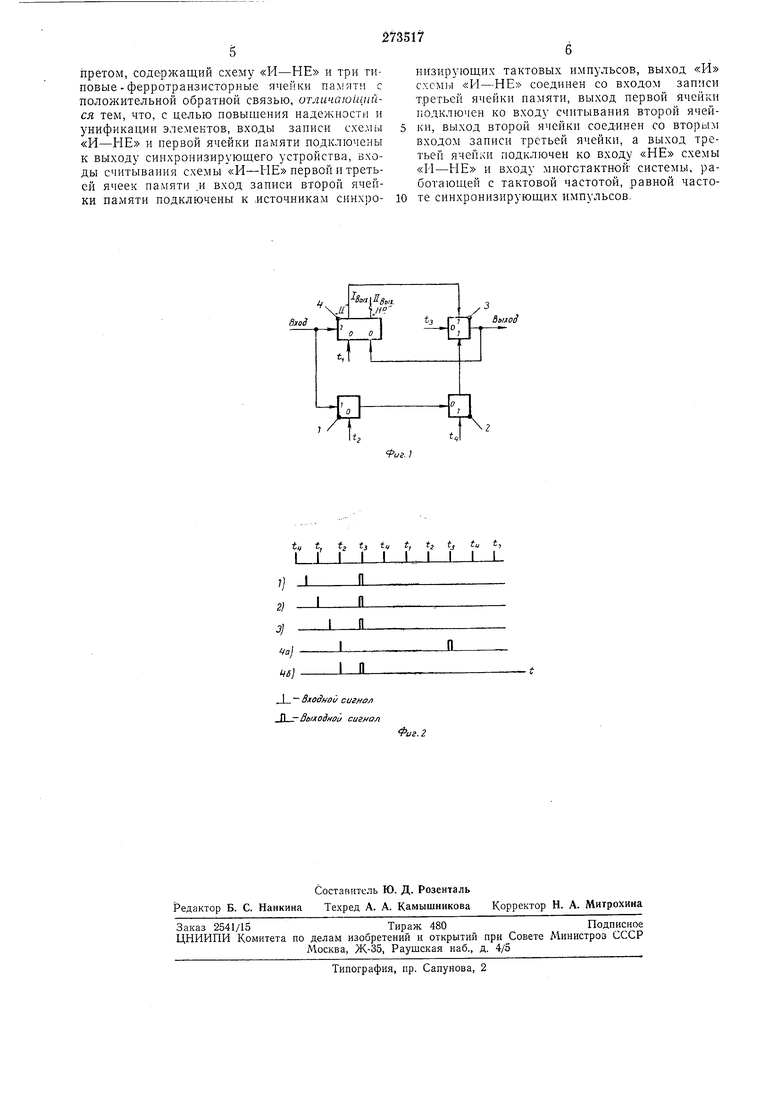

На фиг. 2 представлена диаграм.ма тактовых

нмпульсов.

На вход синхронизатора обмотки заиисм ячейки памяти / и схемы «И-НЕ 4 поступает информация, которую необходимо согласовать с тактами последующего дискретного

тывание и запись информации с ячеек 1-4 производится разнесенными во времени тактовыми имнульсами: t (считывание схемы «И ячейки /); /2 (считывание ячейки 2); з (считывание ячейки 3); t (запись «1 в ячейку 4).

Выход «И схемы «И-НЕ и выход ячейки 2 соединены со входами записи «1 ячейки 3, выход которой подан на вход «НЕ схемы «И-НЕ и соединен со входом последующего дискретного устройства.

Принцип действия синхронизатора заключается в следующем.

На вход синхронизатора {ячейки У и 4) поетуиает сигнал, который надо согласовать с каким-либо из тактов t, tz, ts, ti работы последующего устройства. Нредноложим, что сигнал на выходе синхронизатора должен выдаваться в такт и независимо от момента времени прихода входного сигнала.

Поступающий на вход синхронизатора сигнал перемагничивает сердечники в ячейках / и 4 в состояние «1. В зависимости от момента времени црихода входного сигнала возможны следующие варианты работы синхронизатора (см. фиг. 2).

1)Входной сигнал приходит между тактами /4 и ti, сердечники ячеек 1 к 4 перемагничиваются в состояние «Ь. Тактом ti «1 считывается из ячейки 4 через первый ключевой выход и записывается в ячейку 3. Состояние «1, записанное в ячейку 1, считывается тактом t. Нмпульс с ячейки / производит считывание с ячейки 2, записывая «1 в ячейку 5. Таким образом, в данном случае происходит подтверждение записи «1 в ячейку 3. В такт /з ячейка 3 считывается, и на выходе синхронизатора появляется выходной сигнал.

Таким образом, при поступлении на выход синхронизатора импульса, приходящего между тактами t, и /ь на выходе синхронизатора получают один импульс во внолне определенный такт is2)Входной сигнал совпадает с тактом /i. Пр,и этом в ячейку / запищется «1, а в ячейку 4 или вообще ничего не запищется, или же произойдет перемагничивание по частотному циклу - запись «неполноцеиной «1. В такт /1 в случае, если в ячейке 4 записана «неполноценная «1, она перепищется в ячейку 5. Независимо от того, в каком состоянии находится ячейка 1, в такт 4 аналогично предыдущему случаю в ячейку 3 будет записана «1 из ячейки 2 и, таким образом, на выходе синхронизатора появится сигнал в такт ts.

3)Входной сигнал приходит между тактами ti и t-i. Сердечники ячеек 1 и 4 будут перемагничены в состояние «1. В такт 2 импульс с выхода ячейки 1 переписывает «1 из ячейки 2 в ячейку 3.

В такт гз на выходе синхронизатора появляется сигнал, который устанавливает ячейку 4 в состояние «О, так что в такт ti на ключевом выходе /едх сигнала не будет.

Таким образом, и в этом случае на выходе синхронизатора появится один импульс в такт

/3.

4) Входной сигнал совпадает с тактом /g. При этом ячейка 4 иеремагничивается в состояние «1, а ячейка 1: а) или вообще не неремагничивается (при полном совпадении входпого импульса с импульсом считывания tz) или б) перематнитится по частному циклу,

т. е. в ячейку 1 будет записана «неполноценная «1.

В случае «а в такт 4 на выходе ячейки / импульса не будет и таким образом в ячейку 3 ие будет записана «1, что приведет к тому,

iTO на выходе синхронизатора в такт данного цикла импульса не будет. В такт i следующего цикла «1, записанная в ячейку 4, через первый ключевой выход ячейки 4 записывается в ячейку 5, и в такт /з на выходе синхронизатора появляется выходной сигнал. Отсюда вытекает требование, что для надежной работы синхронизатора частота согласующих тактов должна быть не менее чем в два раза выще частоты входных импульсов.

В случае «б на выходе ячейки / может появиться сигнал, энергия которого определяется степенью совпадения входного сигнала с импульсом считывания /2. Ячейка 2 обеспечивает наделшую работу

схемы синхронизатора при частичном совпадении входного сигнала с тактом t. Это достигается тем, что ячейка 2 имеет определенный порог по считыванию. Следовательно, импульс на выходе ячейки 2 появится только в том

случае, когда энергия импульса с ячейки 1 достаточна для того, чтобы преодолеть порог и вызвать начало блокинг-процесса. Таким образом, в зависимости от степени перемагничивания сердечника ячейки 1 на выходе ячейкн 2 или вообще не будет сигнала (что соответствует случаю 4,а), или появится импульс с номинальными параметрами, обеспечивающий полное перемагничивание сердечника при записи «Ь в ячейку 3, а значит и надежную

работу синхронизатора в рассматриваемом случае. Выходной импульс синхронизатора в такт /3 считывает ячейку 4 через второй ключевой выход //вых в состояние «О. В случае прихода сигнала на вход синхропизатора в промежуток времени между тактами /2 и /4 работа синхронизатора протекает подобно описанному в пункте 1 (входной сигнал приходит между тактами /4 и /i). Таким образом, независимо от времени прихода сигнала на вход синхронизатора соответствующий импульс на выходе появится только во вполне определенный такт, тем самым синхронизируя работу блоков, стоящих до и после синхронизатора.

Предмет изобретения

iipeiOM, содержащий схему «И-НЕ и три типовые-ферротранзисторные ячейки с положительной обратной связью, отличающийся тем, что, с целью повышения надежности и унификации элементов, входы записи схе.мы «И-НЕ и первой ячейки памяти подключены к выходу синхронизирующего устройства, входы считывания схемы «И-НЕ первой и третьей ячеек намяти .и вход записи второй ячейки памяти подключены к источникам синхоопизирующих тактовых импульсов, выход «И схемы «И-НЕ соединен со входом записи третьей ячейки памяти, выход первой ячейки подключен ко входу считывания второй ячейки, выход второй ячейки соединен со вторым входом записи третьей ячейки, а выход третьей ячейки подключен ко входу «НЕ схемы «Н-НЕ и входу многстактной системы, работающей с тактовой частотой, равной частоте синхронизирующих импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU311403A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| ГИСТЕРЕЗИСНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1969 |

|

SU257889A1 |

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1970 |

|

SU270804A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 1967 |

|

SU197281A1 |

| НАКОПИТЕЛЬ КОДА МОРЗЕ | 1971 |

|

SU306576A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU306570A1 |

| Дешифратор | 1978 |

|

SU809564A1 |

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU308517A1 |

t-jt ij Vtj S 7

I I I I I I I ILJ

J - Входной сигнал гВыходнои сиг но A

,

Даты

1970-01-01—Публикация