Известны одноразрядные двоичные сумматоры на феррит-транзисторных ячейках с компенсационным сердечником и без него.

Предложенный сумматор отличается от известных тем, что его одна ячейка без комнеисационного сердечника и другая с компенсационным сердечником соединены по схеме кольцевого регистра сдвига, причем выход первой ячейки подключен к обмотке записи третьей ячейки с компенсационным сердечником для образования в ней суммы, а выход второй ячейки - к шине переноса в следующий разряд и к обмотке считывания без выдачи информации третьей ячейки. Продвигающие обмотки регистра сдвига подсоединены к источникам сигналов слагаемых и переноса из предыдущего разряда.

Это позволяет упростить схему н повысить надежность устройства.

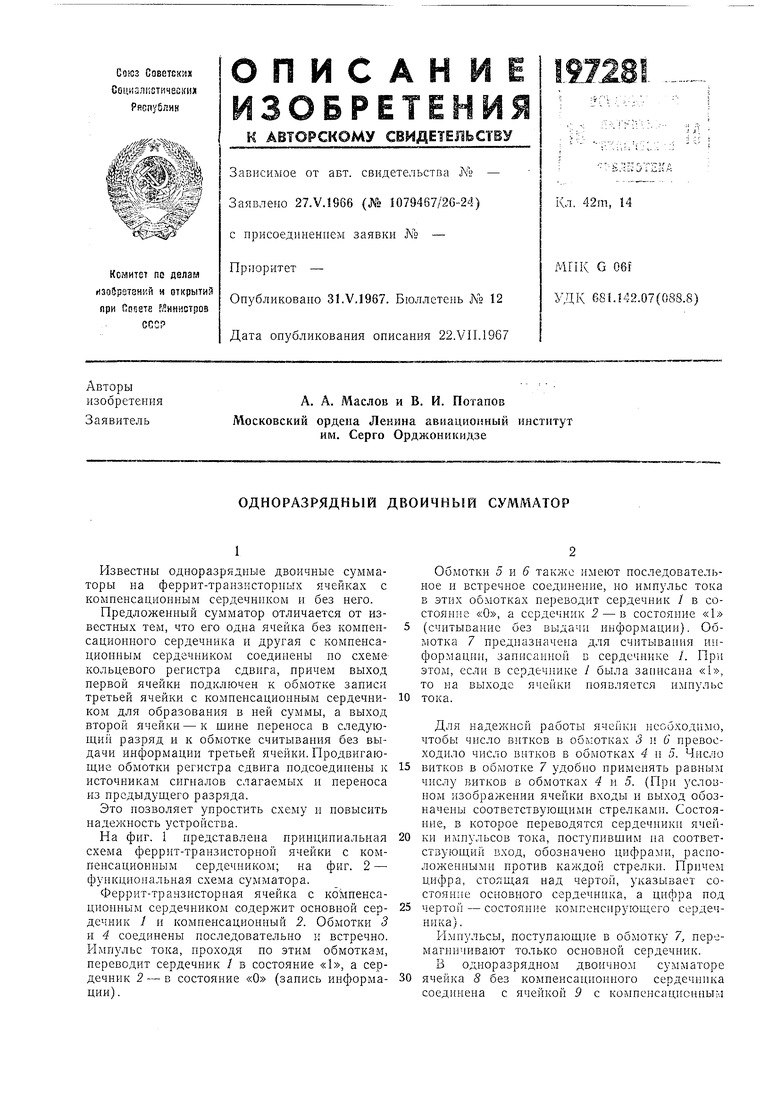

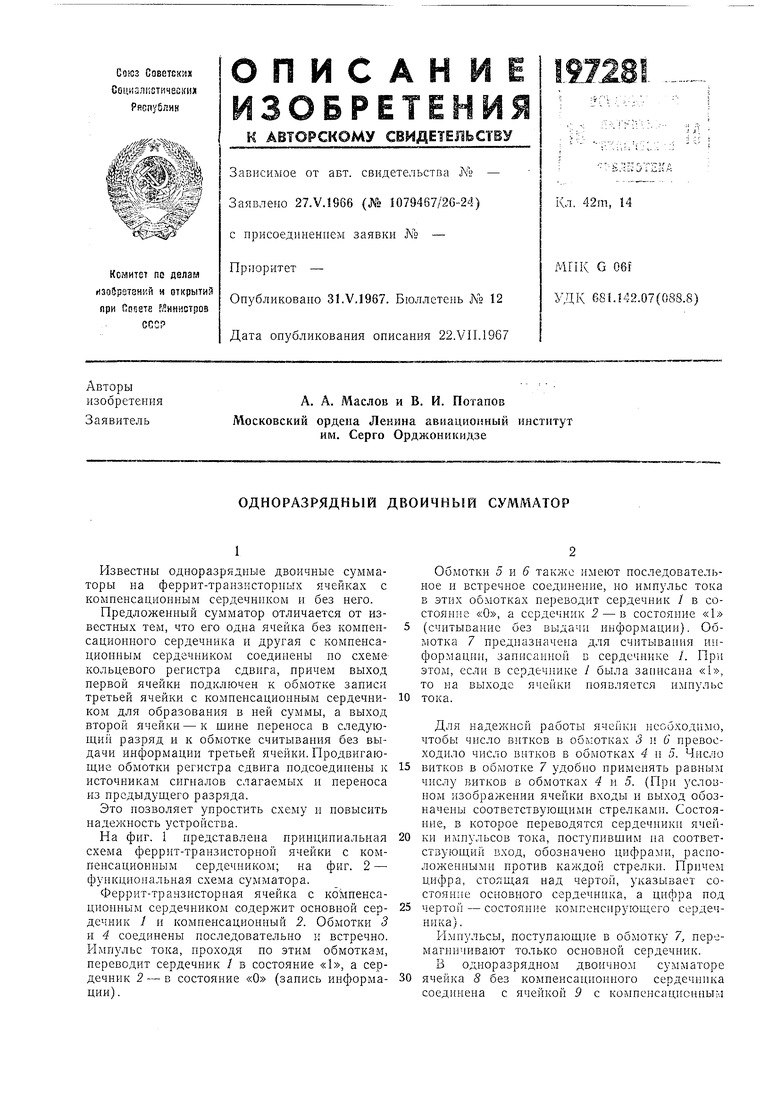

На фиг. 1 представлена принципиальная схема феррит-транзисторной ячейки с компенсационным сердечником; на фиг. 2 - функциональная схема сумматора.

Феррит-транзисторная ячейка с комненсациоиным сердечником содержит основной сердечник 1 н компенсационный 2. Обмотки 3 н 4 соединены последовательно и встречно. Импульс тока, проходя по этим обмоткам, переводит сердечник / в состояние «1, а сердечник 2 - в состояние «О (запись информации) .

Обмотки 5 и 6 также имеют последовательное и встречное соединение, но импульс тока в этих обмотках переводит сердечник / в еоетояине «О, а сердечник 2 - в состояние «1 (считывание без выдачи информации). Обмотка 7 предназначена для считывания информации, записанной в сердечнике /. При этом, если в сердечнике / была записана «1, то на выходе ячейки появляетея импульс тока.

Для надежной работы ячейки необходимо, чтобы число витков в обмотках 3 н 6 превосходило число витков в обмотках 4 п 5. Число

витков в обмотке 7 удобно применять равным числу витков Б обмотках 4 и 5. (При условном изображении ячейки входы и выход обозначены соответствующими стрелками. Состояние, в которое переводятся сердечники ячейки импульсов тока, поступившим на соответствующий вход, обозначено цифрами, располол енными против каждой стрелки. Причем цифра, стоящая над чертой, указывает состояние основного сердечника, а цифра под

чертой - еостояние компенсирующего сердечника).

Импульсы, поступающие в обмотку 7, перемагничивают только основной сердечник. В одноразрядном двоичном сумматоре

сердечником по схеме кольцевого регистра сдвига.

На входную шину 10 сумматора подаются импульсы соответствующих разрядов слагаемых AI , BI и переноса пз предыдущего разряда Pi-i, разпесепные по тактам t, is ) Последовательность поступления в сумматор слагаемых п переноса в течение цикла вычисления одного разряда может быть произвольной.

1чейка // с компенсационным сердечником служит для образования суммы 5 . Импульс нерепоса в следующий разряд Р снимается с щины 12. На шины 13 и 14 по такту ti по.дводятся соответственно импульсы установки начального состояиия и имнульсы считывания суммы.

Работу сумматора уа,обно рассмотреть при

Л,- B,WJ, I.

По такту fi происходит установка начального состояния сумматора, т. е. по шине 13 Б ячейку 8 записывается «1, а в ячейку 9 - «О. При этом, если в результате предыдущих вычислений в ячейке 9 была записана «1, то благодаря компенсационному сердечнику произойдет стирание «1 без выдачи имиульса с выхода ячейки 9. Одповремеи 0 по шине 14 производится опрос ячейки 11, где образуется сумма, и ее основпой сердечник перемагиичивается в состояние «О. Состояние компенсационного сердечника ячейки 11 определяет комбинация состояний сумматора в предыдущем цикле вычислений и может быть либо «О, либо «1.

Пусть для определепности по такту U на вход сумматора поступает слагаемое Л,. , по такту 3 - слагаемое В; , а по такту /4 - перенос из предыдущего разряда Pi-i. Таким образом, после подачи на шину 10 первого слагаемого импульс с выхода ячейки 5 переводит в состояние «1 основные сердечники ячейки 9 и 11, а компенсационные сердечники этих ячеек перемагничивает в состояние «О. В результате взаимной компенсации а.д.с., наводимой на базовых обмотках ячеек 9 и //, и преобладания э.д.с. положительпой полярности, триоды обеих ячеек будут надежно закрыты.

При поступлении на шину 10 второго слагаемого основной сердечник ячейки 9 перемагиичивается из состояиия «1 в состояипе «О. На выходе ячейки 9 появляется и: пульс

тока, который по обмотке с преобладанием записывает «1 в 8, производит, благодаря компенсационному сердечнику, стирание информации без выдачи в ячейке // и подводится к шиие 12 переноса в следующий разряд.

Импульс переноса из предыдущего разряда, поступнвшнй на вход сумматора, перемагничиваег ячейку 8 из состояния «1 в состояние «О. Импульс с выхода ячейки 8 перемагннчивает в состояние «1 основной сердечник и подтверждает состояние «О компенсационного сердечника ячейки 9. Одновременно «1 записывается в основной, а «О в

компенсационный сердечник ячейки 11. По такту ti происходит ечитываиие суммы из ячейки // п установка сумматора в исходное состояние. Последующие циклы суммирования аналогичны. Если сумматор используется

в качестве сумматора накапливающего типа и в нем осуществляется суммироваиие п слагаемых (), импульсы установки начального состояния подаются на щину 13 только перед началом суммирования и после окончаПИЯ суммирования слагаемых п всех переносов из предыдущего разряда. Результат любых промежуточных вычислений можно получить, подавая по такту t импульсы считывапия на шипу 14 ячейки 11.

Предмет изобретения

Одноразрядный двоичный сумматор иа

феррит-транзисторных ячейках, одна из которых вьшолпена без компенсационного сердечника, а две другие - с компенсационными сердечниками, отличающийся тем, что, с целью упрощения схемы и повышения надежностн, первая ячейка без компенсационного сердечника и вторая с компепсационным сердечником соединены по схеме кольцевого регистра сдвига, причем выход первой ячейки подключен к обмотке записи третьей ячейки

с компеисационным сердечником для образования в ней суммы, выход второй ячейки соединен с шиной переноса в следующий разряд и с обмоткой считывания без выдачи информапии третьей ячейки, а продвигающие обмотки регистра сдвига подключены к источникам сигналов слагаемых и переноса из предыдущего разряда.

- . ..;s-

(I

,.4

е /%- - - -:;ir

| название | год | авторы | номер документа |

|---|---|---|---|

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU268008A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ К | 1972 |

|

SU341034A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| К-значный фазоимпульсатор сумматор | 1977 |

|

SU657435A1 |

| Двоичный параллельный сумматор со сквозным переносом | 1960 |

|

SU142818A1 |

| ФЕРРИТО-ТРАНЗИСТОРНЫЙ ДВОИЧНЫЙ ДИНАМИЧЕСКИЙСЧЕТЧИК | 1972 |

|

SU337950A1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU311403A1 |

|

L/

игягв

N Г

1

(/

-„J ff /..

Т

f2

Si Фиг.2

Даты

1967-01-01—Публикация