держит синхронизатор 1. квантователь 2 по амплитуде, квантователь 3 по длительности, первый 4 и второй 5 формирователи, триггер 6, элемент И 7, адресный счетчик 8, первый

9 и второй 10 регистры, мультиплексор 11, блок 12 памяти, блок 13 обработки сигналов, тактовый вход 14, первый 15 и второй 16 входы и выход 17. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1990 |

|

SU1750036A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения вычислительной машины с объектами управления | 1979 |

|

SU1040482A1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

Изобретение относится к автоматике, вычислительной технике, радиотехнике, связи, а именно к устройствам декодирования импульсных кодовых последовательностей, и может быть использовано в устройствах обработки информации. Целью изобретения является расширение области применения дешифратора за счет осуществления декодирования времяимпульсных кодов по критерию k из т. Дешифратор со

Изобретение относится к автоматике, вычислительной технике, радиотехнике, связи, а именно к устройствам декодирования импульсных кодовых последовательностей, и может быть использовано в устройствах обработки информации.

Целью изобретения является расширение области применения дешифратором за счет осуществления декодирования время- импульсных кодов по критерию к/м.

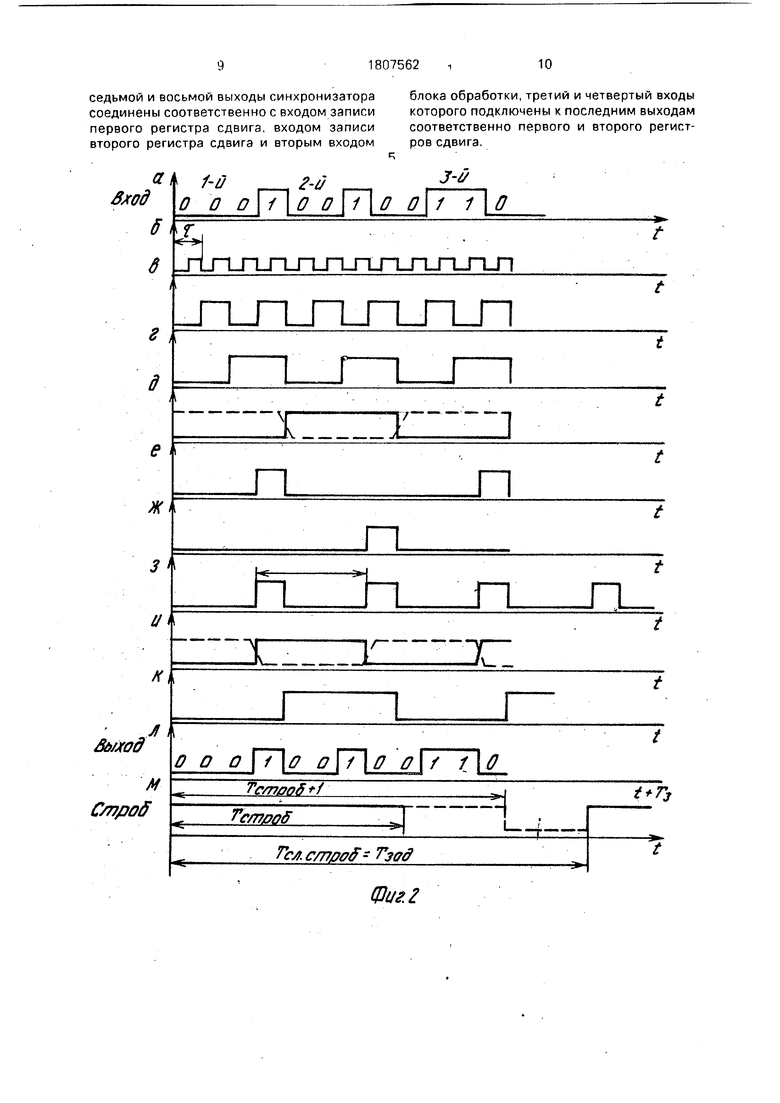

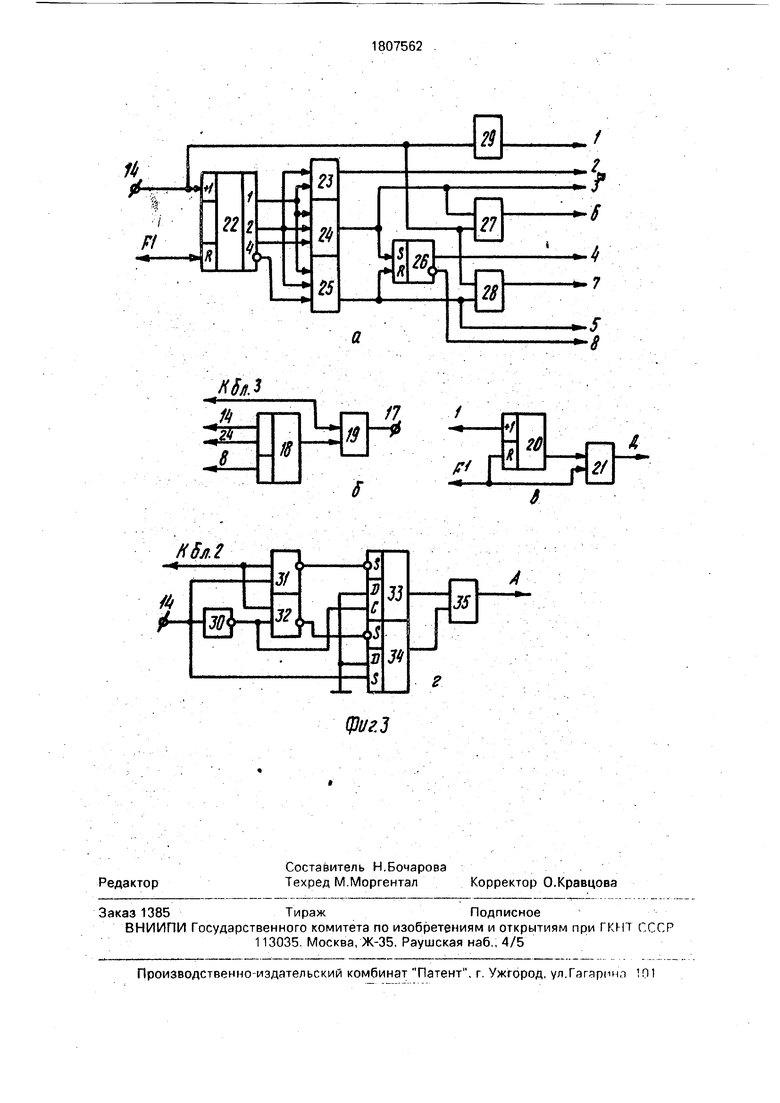

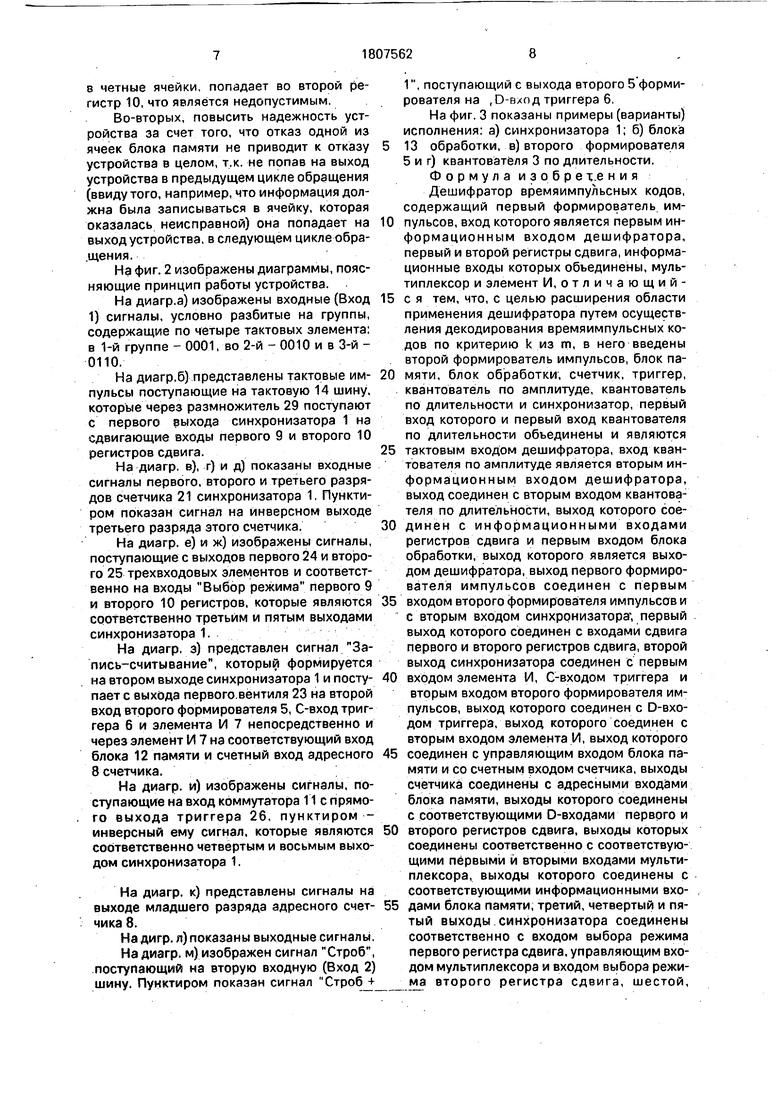

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - переменные диаграммы, поясняющие принцип работы дешифратора; на фиг. 3 - примеры (варианты) исполнения блоков: а) синхронизатор, б) блок обработки, в) второй формирователь, г) квантователь по длительности.

Дешифратор времяимпульсных кодов содержит синхронизатор 1, квантователь 2 по амплитуде, квантователь 3 по длительности, первый 4 и второй 5 формирователи, триггер 6, элемент И 7, адресный счетчик 8, первый 9 и второй 10 регистры, мультиплексор 11, блок 12 памяти, блок 13 обработки сигналов, тактовый вход 14, первый 15 и второй 16 информационные входы и

ВЫХОДИТ.

Работу дешифратора рассмотрим на примере при п 4, где п - число разрядов регистров.

Дешифратор работает следующим образом.

В исходном состоянии первый 22 и адресный 8 счетчики находятся в произвольном состоянии, триггер 21 второго формирователя 5 - в нулевом состоянии. При этом первый 24 и второй 25 трехвходо- вые элементы И, первый 23, второй 27 и третий 28 вентили, первый 9 и второй 10 регистры, мультиплексор 11 и блок 13 обработки сигналов работают в обычном режиме. Адресный 3 счетчик не считает импульсы, т.к. элемент И 7 закрыт и на его выход не поступают сигналы с второго выхода синхронизатора 1. Блок 12 памяти находится в одном из режимов, при этом информация в него записывается, а из него не считывается. Информация на входе и выходе устройства отсутствует.

С приходом импульса Строб на вторую входную шину 16, которая соединена с входом первого формирователя 4, последний по переднему фронту этого импульса вырабатывает сигнал установки первого счетчика 22 в нулевое состояние, Одновременно этим сигналом устанавливается в нулевое состояние счетчик 20 и в единичное состояние триггер 21 второго 5„формирова- теля, который соединен последовательно с первым формирователем 4, Триггер 6 устанавливается в единичное состояние и

разрешает прохождение тактовых сигналов с второго выхода синхронизатора 1 через второй вход элемента И 7 на счетный вход адресного счетчика 8, под действием которых адресный 8 счетчик производит перебор ячеек блока 12 памяти. Первый счетчик 22 считает импульсы, поступающие на его счетный вход с тактовой шины, при этом на выходах синхронизатора 1 формируются синхронизированные началом сигнала

Строб следующие сигналы: первый выход - сигналы, соответствующие тактовым сигналам, поступающим на тактовую шину, второй выход - Считывание - Запись - тактовые сигналы, которыми осуществляется считывание (запись) из/в блок 12 памяти, формируется первым вентилем 23, эти же сигналы используются в качестве счетных импульсов адресного счетчика 3; третий выход - Выбор режима РП - выбор режима

первого регистра 9 - первым трехвходовым элементом И 24; четвертый выход - Считывание их РП /РГ2 - считывание информации из первого/второго регистра и запись ее в блок 12 памяти - триггером 26; пятый

выход - Выбор режима РГ2 - выбор режима работы второго регистра 10 - вторым трехвходовым элементом И 25; шестой выход- Запись РП - запись информации из блока 12 памяти в первый 9 регистр - первым вентилем 27; седьмой выход - Запись РГ2 - запись информации из блока 12 памяти во второй регистр 10 - вторым вентилем 28; восьмой - подключение выходов регистров 9 и 10 к элементу И 19 в блоке 13

обработки.

Сигналы, поступающие на первый вход 15, квантуются по амплитуде и длительности при помощи квантователей 2 и 3 и поступают на объединенные информационные

входы первого 9 и второго 10 регистра сдвига, а также на первый вход блока 13 обработки, Под действием сигналов типа

меандр, поступающих на тактовую шину, производится сдвиг входной информации в первом 9 и втором 10 регистрах сдвига. При этом первые (нечетные) п элементов этой информации записываются во второй регистр 10, а из него параллельным кодом - в первую (нечетную ячейку) блока 12 памяти, из которой предварительно была считана в первый регистр 9 информация, записанная туда ранее в предыдущем цикле обращения. Последующие (четные) п элементов этой информации записываются в первый регистр 9, а из него параллельным кодом - во вторую (четную) ячейку блока 12 памяти, из которой предварительно была считана во второй регистр 10 информация, записанная туда ранее в предыдущем цикле обращения, Запись и считывание информации из первого 9 и второго 10 регистров в блок 12 памяти и обратно осуществляется путем изменения режимов работы регистров (Сдвиг или Запись) под действием сигналов, поступающих с выходов первого 24 и второго 25 трехвходовых элементов И на соответствующие входы этих регистров, а также сигнала Считывание-Запись, поступающего с выхода первого вентиля 23 на соответствующий вход блока 12 памяти. Коммутация выходов.первого 9 и второго 10 регистров с информационными входами блока 12 памяти осуществляется сигналами с выходов триггера посредством мультиплексора 11. В блоке 12 памяти перебирается определенное Число ячеек, которое определяется длительностью сигналов Строб Т и тактовых сигналов t, поступающих на управляющий вход блока 12 памяти. Число ячеек N можно определить по следующей формуле N T/t.

Процесс обмена информацией Между регистрами 9 и 10 и блоком памяти 12 осуществляется до появления сигнала на выходе второго формирователя 5. Последний совместно с триггером 6 осуществляет формирование сигнала Строб + 1, длительность которого по отношению к исходному сигналу Строб больше на один такт длительности импульсов, вырабатываемых на втором выходе синхронизатора 1. По окончании формирования сигнала Строб + производится установка триггера 6 в состояние, которым запрещается прохождение сигналов на счетный вход счетчика 8 и управляющий (Запись-Считывание) вход блока 12 памяти. После этого дешифратор возвращается в исходное состояние.

Таким образом, осуществив квантование входных сигналов по амплитуде и по длительности при помощи квантователей 2 и 3, разбив входную информацию на группы, содержащие по п тактовых элементов, и

разделив при помощи первого 9 и второго 10 регистров эту информацию на два потока (нечетный и четный), преобразовав ее из последовательного кода в параллельный при помощи этих регистров и осуществив задержку полученного кода путем запоминания в блоке 12 памяти с последующим считыванием из него, через время, определяемое периодом следования сигнала

0 Строб, поступающего на вторую входную шину 16, произведя обратное преобразование этой информации из параллельного кода в последовательный путем считывания ее из блока 12 памяти и записи ее в первый 9

5 и второй 10 регистры и объединив эти потоки на выходе устройства при помощи блока обработки сигналов, производится дешифрация входных сигналов.

При этом перебор ячеек 12 памяти осу0 ществляется при помощи адресного счетчика 8 со сдвигом на одну ячейку начального адреса при каждом новом цикле обращения к блоку 12 памяти (т.е. при каждом очередном появлении сигнала Строб).

5 Сдвиг ячейки начального адреса осуществляется вторым формирователем 5, при этом содержимое счетчика 8 каждый раз с приходом импульса Строб увеличивается на единицу.

Таким образом, нечетные п элементов.

0 записываются через второй регистр 10 в нечетные ячейки блока 12 памяти и из них должны считываться во второй регистр при следующем цикле обращения, Это возможно лишь в том случае, если производить

5 считывание из блока памяти со сдвигом на одну ячейку при каждом новом цикле обращения. Аналогично для четных элементов,

Сдвиг ячейки начального адреса адресного счетчика 8 позволяет, во-первых, обес0 печить работоспособность устройства, так как, например, в 1 цикле обращения запись нечетных п элементов информации (п - число разрядов регистра) записывается последовательным кодом во второй регистр 10, а

5 из него параллельным кодом в нечетную ячейку блока 12 памяти, при этом ранее записанная в эту ячейку информация предварительно считывается в первый регистр 9. (Одновременно осуществить считывание в

0 первый 9 регистр, сдвиг информации в нем и запись новой информации в эту же ячейку .блока 12 памяти невозможно). В противном случае, так как считывание ранее записанной информации из ячейки блока 12 памяти

5 должно предшествовать записи в нее, получается в следующем цикле обращения к блоку 12 памяти информации, записанная в нечетные ячейки, попадает в первый регистр 9 и наоборот информация, записанная

в четные ячейки, попадает во второй регистр 10, что является недопустимым,

Во-вторых, повысить надежность устройства за счет того, что отказ одной из ячеек блока памяти не приводит к отказу устройства в целом, т.к. не попав на выход устройства в предыдущем цикле обращения (ввиду того, например, что информация должна была записываться в ячейку, которая оказалась неисправной) она попадает на выход устройства, в следующем цикле обра- .щения.

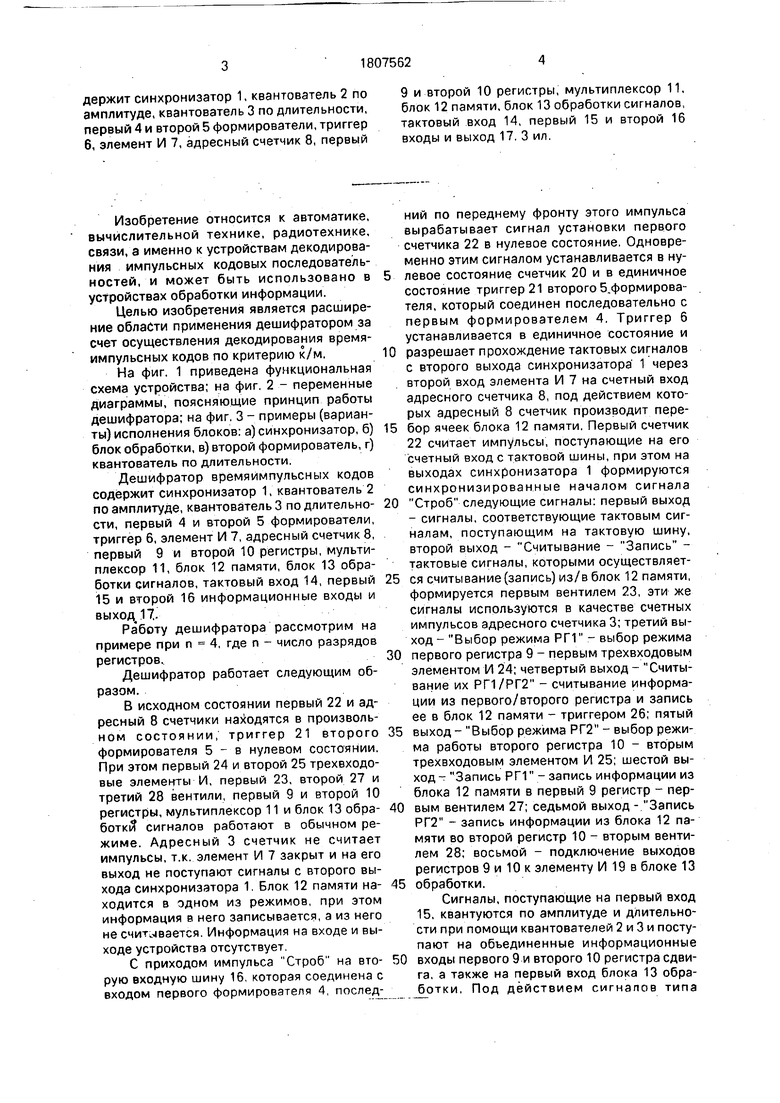

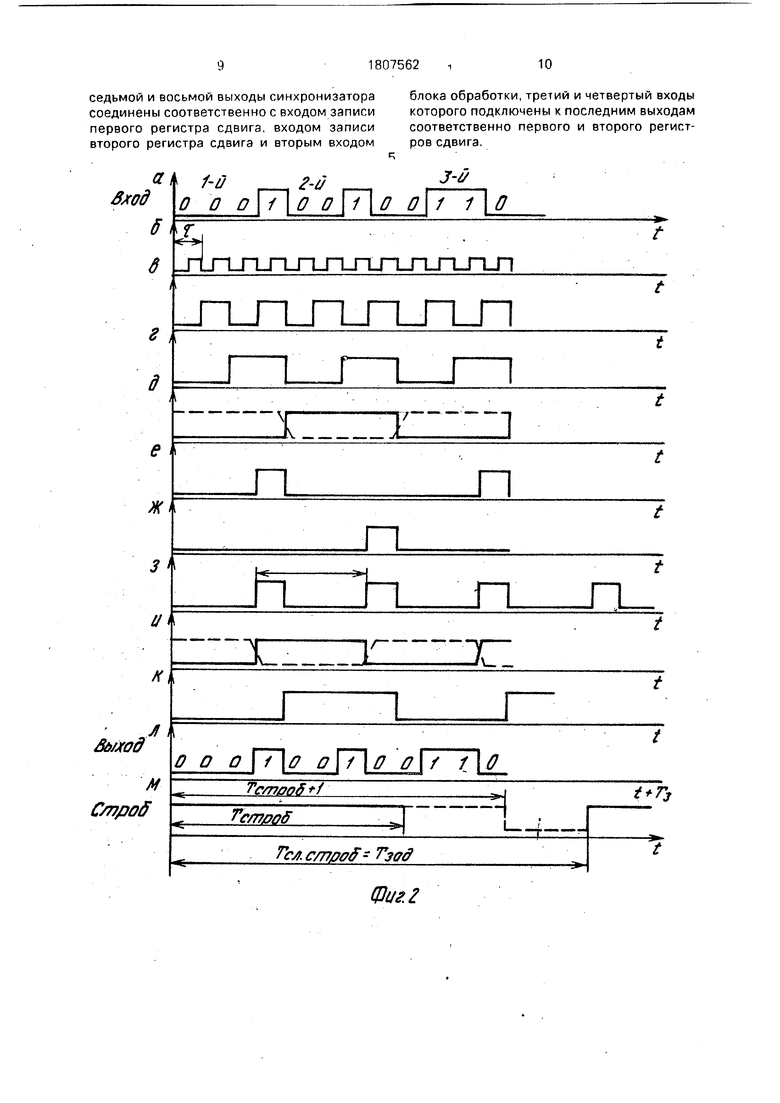

На фиг. 2 изображены диаграммы, поясняющие принцип работы устройства.

На диагр.а) изображены входные (Вход 1) сигналы, условно разбитые на группы, содержащие по четыре тактовых элемента: в 1-й группе - 0001, во 2-й -0010 и в 3-й - 0110.

На диагр.б) представлены тактовые им- пульсы поступающие на тактовую 14 шину, которые через размножитель 29 поступают с первого выхода синхронизатора 1 на сдвигающие входы первого 9 и второго 10 регистров сдвига.

На диагр. в), г) и д) показаны входные сигналы первого, второго и третьего разрядов счетчика 21 синхронизатора 1. Пунктиром показан сигнал на инверсном выходе третьего разряда этого счетчика.

На диагр. е) и ж) изображены сигналы, поступающие с выходов первого 24 и второго 25 трехвходовых элементов и соответственно на входы Выбор режима первого 9 и второго 10 регистров, которые являются соответственно третьим и пятым выходами синхронизатора 1.

На диагр. з) представлен сигнал Запись-считывание, который формируется на втором выходе синхронизатора 1 и посту- пает с выхода первого.вёнтиля 23 на второй вход второго формирователя 5, С-вход триггера 6 и элемента И 7 непосредственно и через элемент И 7 на соответствующий вход блока 12 памяти и счетный вход адресного 8 счетчика.

На диагр. и) изображены сигналы, поступающие на вход коммутатора 11 с прямого выхода триггера 26, пунктиром - инверсный ему сигнал, которые являются соответственно четвертым и восьмым выходом синхронизатора 1.

На диагр, к) представлены сигналы на выходе младшего разряда адресного счет- чика 8.

На дигр. л) показаны выходные сигналы,

На диагр, м)изображен сигнал Строб,

поступающий на вторую входную (Вход 2)

шину. Пунктиром показан сигнал Строб +

1, поступающий е выхода второго 5 формирователя на , D-вход триггера 6,

На фиг. 3 показаны примеры (варианты) исполнения: а) синхронизатора 1; б) блока 13 обработки, в) второго формирователя 5 и г) квантователя 3 по длительности. Формула из обрет.ения Дешифратор времяимпульсных кодов, содержащий первый формирователь импульсов, вход которого является первым ин- формационным входом дешифратора, первый и второй регистры сдвига, информационные входы которых объединены, мультиплексор и элемент И, отличающий- с я тем, что, с целью расширения области применения дешифратора путем осуществления декодирования времяимпульсных кодов по критерию k из т, в него введены второй формирователь импульсов, блок памяти, блок обработки, счетчик, триггер, квантователь по амплитуде, квантователь по длительности и синхронизатор, первый вход которого и первый вход квантователя по длительности объединены и являются тактовым входом дешифратора, вход квантователя по амплитуде является вторым информационным входом дешифратора, выход соединен с вторым входом квантователя по длительности, выход которого сое- динен с информационными входами регистров сдвига и первым входом блока обработки, выход которого является выходом дешифратора, выход первого формирователя импульсов соединен с первым входом второго формирователя импульсов и с вторым входом синхронизатора , первый выход которого соединен с входами сдвига первого и второго регистров сдвига, второй выход синхронизатора соединен с первым входом элемента И, С-входом триггера и вторым входом второго формирователя импульсов, выход которого соединен с D-вхо- дом триггера, выход которого соединен с вторым входом элемента И, выход которого соединен с управляющим входом блока памяти и со счетным входом счетчика, выходы счетчика соединены с адресными входами блока памяти, выходы которого соединены с соответствующими D-входами первого и второго регистров сдвига, выходы которых соединены соответственно с соответствующими первыми и вторыми входами мультиплексора, выходы которого соединены с соответствующими информационными входами блока памяти, третий, четвертый и пятый выходы.синхронизатора соединены соответственно с входом выбора режима первого регистра сдвига, управляющим входом мультиплексора и входом выбора режима второго регистра сдвига, шестой,

седьмой и восьмой выходы синхронизатораблока обработки, третий и четвертый входы

соединены соответственно с входом записикоторого подключены к последним выходам

первого регистра сдвига, входом записисоответственно первого и второго региствторого регистра сдвига и вторым входомров сдвига.

Фи г. 2

Кбл.2

фиг.3

| Устройство декодирования импульсных кодовых последовательностей | 1981 |

|

SU995357A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство декодирования импульсных кодовых последовательностей | 1976 |

|

SU582573A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Дешифратор время-импульсных кодов | 1988 |

|

SU1545326A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1993-04-07—Публикация

1991-03-11—Подача